## Toward dynamically reconfigurable high throughput multiprocessor Turbo decoder in a multimode and multi-standard context

Vianney Lapotre

#### ► To cite this version:

Vianney Lapotre. Toward dynamically reconfigurable high throughput multiprocessor Turbo decoder in a multimode and multi-standard context. Electronics. Université de Bretagne-Sud, 2013. English. NNT: . tel-01096975

## HAL Id: tel-01096975 https://hal.science/tel-01096975

Submitted on 18 Dec 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

#### THÈSE / UNIVERSITÉ DE BRETAGNE SUD

sous le sceau de l'Université européenne de Bretagne pour obtenir le titre de DOCTEUR DE L'UNIVERSITÉ DE BRETAGNE SUD Mention : STIC

École Doctorale SICMA

Toward dynamically reconfigurable high throughput multiprocessor Turbo decoder in a multimode and multi-standard context présentée par

## Vianney Lapôtre

Préparée au Laboratoire Lab-STICC, Lorient, France

Thèse soutenue le 20 Novembre 2013 devant le jury composé de :

Christophe JEGO Professeur, IMS, IPB / Rapporteur

Guido MASERA Professeur, Politecnico di Turino / Rapporteur

Jean-Didier LEGAT Professeur, Université Catholique de Louvain / Rapporteur

Édith BEIGNÉ Docteur, ingénieur de recherche, CEA - LETI / Examinateur

Michael HÜBNER Professeur, Ruhr-Universität Bochum / Examinateur

Amer BAGHDADI Professeur, Telecom Bretagne / Co-directeur de thèse

Jean-Philippe DIGUET Directeur de Recherche, CNRS / Co-directeur de thèse

Guy GOGNIAT Professeur, Université de Bretagne Suf / Directeur de thèse

Plus on connaît, plus on aime. Léonard de Vinci

### Remerciements

Je n'imagine pas pouvoir rédiger ces remerciements sans commencer par remercier vivement Guy GOGNIAT qui m'a accompagné et conseillé tout au long de ces trois années de thèse. Nos nombreux échanges allant bien souvent audelà des questions purement scientifiques entourant ma thèse, m'ont permis de découvrir et d'apprécier aussi bien le Professeur que l'homme.

Je remercie Amer BAGHDADI pour son aide et ses conseils précieux qui m'ont permis d'avancer tout au long de mes travaux de thèse. Je tiens également à le remercier pour l'accueil chaleureux lors de mes différents séjours à Brest. Je remercie également Jean-Philippe DIGUET pour son soutien et nombreux apports lors de la rédaction de ce manuscrit. Je remercie Michael HÜBNER pour son investissement dans mes travaux de thèse ainsi que pour le superbe accueil qui m'a été réservé lors de mon séjour à Bochum.

Je remercie également le Professeur Christophe JEGO d'avoir accepté la charge de rapporteur ainsi que le rôle de président du jury de soutenance de cette thèse. Je remercie également les Professeurs Guido MASERA et Jean-Didier LEGAT d'avoir accepté la charge de rapporteur de cette thèse. Je tiens également à remercier dith BEIGNE d'avoir accepté de participer au jury de la soutenance de thèse.

Ces remerciements sont également le bon moment pour faire une pause, se retourner, regarder ces trois années qui ont défilé si vite, et prendre le temps de vous remercier. Cédric, six années ensemble à l'UBS, emplies de superbes souvenirs, ça ne s'oublie pas. Florence, Virginie, après trois ans de pauses, de missions, et de formulaires administratifs en tout genre, je ne peux que vous dire un grand merci pour votre bonne humeur et votre soutien sans faille. J'ai également à cœur de remercier tous les autres membres du Lab-STICC avec qui nous avons partagé de très bons moments et que je ne cite pas explicitement ici car la liste est bien trop longue. Enfin, j'aimerais remercier les différentes personnes que j'ai rencontrées à Brest et à Bochum pour m'avoir accueillies chaleureusement lors de mes différentes visites.

# Contents

#### Introduction

#### 1

| 1        | Tur | bo coc  | les and state of the art in channel decoder design       | 7  |

|----------|-----|---------|----------------------------------------------------------|----|

|          | 1.1 | Conte   | xt of channel coding                                     | 8  |

|          |     | 1.1.1   | Communication system                                     | 8  |

|          |     | 1.1.2   | Channel code performance                                 | 9  |

|          |     | 1.1.3   | Turbo encoding                                           | 9  |

|          |     |         | 1.1.3.1 Recursive Systematic Convolutional encoders      | 10 |

|          |     |         | 1.1.3.2 Turbo codes interleavers                         | 13 |

|          |     | 1.1.4   | Turbo decoding                                           | 14 |

|          |     |         | 1.1.4.1 The MAP Algorithm                                | 16 |

|          |     |         | 1.1.4.2 Parallelism in Turbo decoding                    | 17 |

|          | 1.2 | Dynar   | nic configuration of flexible Turbo Decoders             | 20 |

|          |     | 1.2.1   | Dynamic configuration in embedded systems                | 20 |

|          |     | 1.2.2   | Dynamic configuration in multi-mode and multi-standard   |    |

|          |     |         | scenario                                                 | 23 |

|          | 1.3 | State   | of the art in flexible Turbo decoding architectures      | 24 |

|          | 1.4 | Initial | multi-ASIP architecture for turbo decoding               | 30 |

|          |     | 1.4.1   | Overiew of the DecASIP processor                         | 32 |

|          |     | 1.4.2   | Interleaved/deinterleaved address generator              | 34 |

|          |     | 1.4.3   | NoC messages                                             | 35 |

|          |     | 1.4.4   | ASIC synthesis results                                   | 36 |

|          | 1.5 | Summ    | ary                                                      | 38 |

| <b>2</b> | RD  | ecASI   | P: optimized DecASIP for an efficient reconfiguration    | 39 |

|          | 2.1 | Initial | DecASIP configuration                                    | 40 |

|          |     | 2.1.1   | Configuration memory                                     | 40 |

|          |     | 2.1.2   | Program memory                                           | 42 |

|          | 2.2 | Propo   | sed optimizations for an efficient dynamic configuration | 45 |

|          |     | 2.2.1   | Configuration parameters storage                         | 45 |

|          |     | 2.2.2   | Configuration memory organization                        | 47 |

|          |     | 2.2.3   | Unified program                                          | 50 |

|          |     | 2.2.4   | Multi-configuration storage                              | 53 |

|          | 2.3 | RDec    | ASIP Implementation                                      | 54 |

|          |     | 2.3.1   | ASIC synthesis results                                   | 54 |

|          |     | 2.3.2   | Dynamic reconfiguration performance                      | 56 |

|          | 2.4 | Summ    | ary                                                      | 58 |

| 3  | Rec   | onfigu  | rable multi-ASIP UDec architecture                                                   | 61  |

|----|-------|---------|--------------------------------------------------------------------------------------|-----|

|    | 3.1   | Flexib  | ble UDec architecture                                                                | 62  |

|    |       | 3.1.1   | ASIP number and location                                                             | 63  |

|    |       |         | 3.1.1.1 Ring buses adaptation                                                        | 63  |

|    |       |         | 3.1.1.2 Butterfly topology NoCs adaptation                                           | 64  |

|    |       | 3.1.2   | Platform controller                                                                  | 68  |

|    | 3.2   | UDec    | configuration infrastructure                                                         | 72  |

|    |       | 3.2.1   | Main challenges for an efficient configuration infrastructure                        | 73  |

|    |       |         | $3.2.1.1$ Low complexity $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$       | 73  |

|    |       |         | 3.2.1.2 Multicast, broadcast and selection mechanisms .                              |     |

|    |       |         | 3.2.1.3 Incremental data burst transfer                                              | 74  |

|    |       | 3.2.2   | Configuration infrastructure                                                         | 74  |

|    |       |         | 3.2.2.1 Architecture overview                                                        | 75  |

|    |       |         | 3.2.2.2 Addressing                                                                   | 77  |

|    |       |         | 3.2.2.3 Transfer protocol                                                            | 78  |

|    |       |         | 3.2.2.4 Selection                                                                    | 80  |

|    |       | 3.2.3   | SystemC/VHDL mixed Validation                                                        | 81  |

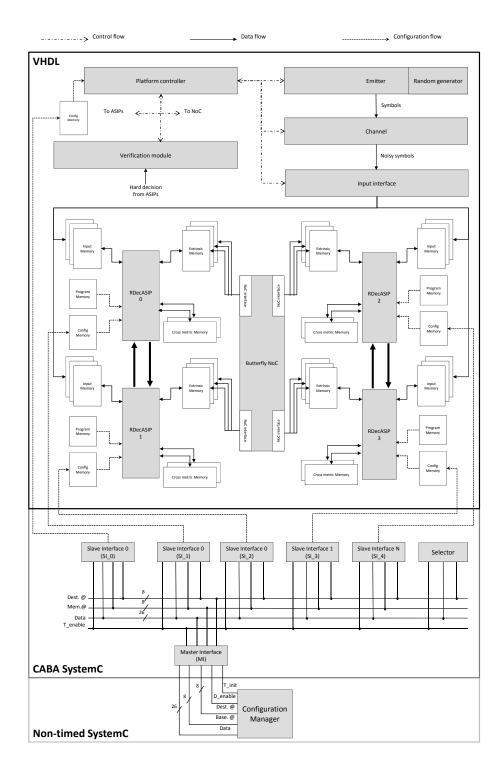

|    |       |         | 3.2.3.1 Platform model                                                               | 81  |

|    |       |         | 3.2.3.2 Model evaluation                                                             | 81  |

|    |       | 3.2.4   | FPGA prototype                                                                       | 83  |

|    | 3.3   |         | ary                                                                                  | 88  |

|    |       |         | ·                                                                                    |     |

| 4  |       | -       | tion management for the UDec architecture                                            | 89  |

|    | 4.1   |         | elism impact on decoding performance                                                 | 90  |

|    |       | 4.1.1   | Sub-block parallelism                                                                | 90  |

|    |       | 4.1.2   | Shuffled decoding                                                                    | 93  |

|    | 4.2   |         | omputed configuration management                                                     | 94  |

|    | 4.3   | Run-t   | ime configuration generation management                                              | 96  |

|    |       | 4.3.1   | Restricted configuration management                                                  |     |

|    |       | 4.3.2   | Oversized configuration management                                                   | 100 |

|    |       |         | 4.3.2.1 Oversized configuration principle                                            | 100 |

|    |       |         | 4.3.2.2 Oversized configuration generation                                           | 101 |

|    |       | 4.3.3   | Oversized Configuration management scenario                                          | 106 |

|    |       |         | $4.3.3.1  1 \text{ frame - 1 configuration}  \dots  \dots  \dots  \dots  \dots$      |     |

|    |       |         | 4.3.3.2 Decoding of multiple frames                                                  | 107 |

|    | 4.4   | Config  | guration management discussion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 109 |

|    | 4.5   | Summ    | nary                                                                                 | 111 |

| Co | onclu | ision a | and perspectives                                                                     | 113 |

| G  | lossa | ry      |                                                                                      | 119 |

| Contents             | iii |

|----------------------|-----|

| Bibliography         | 121 |

| List of publications | 127 |

| Appendix             | 129 |

# List of Figures

| 1    | Communication standards evolution in mobile telephone networks        | 1        |

|------|-----------------------------------------------------------------------|----------|

| 2    | Usage scenario example of a considered multiprocessor platform .      | 2        |

| 1.1  | Elements of a digital communication system                            | 8        |

| 1.2  | Turbo encoder: Parallel concatenation of two RSC encoders             | 10       |

| 1.3  | Non-recursive non-systematic and Non-recursive systematic encoders    | 10       |

| 1.4  | Recursive systematic convolutional encoders                           | 11       |

| 1.5  | Trellis diagram of the RSC encoder of Figure 1.4(b)                   | 12       |

| 1.6  | Typical Turbo decoder structure                                       | 15       |

| 1.7  | Sub-block parallelism with message passing for metric initialization  | 18       |

| 1.8  | Sub-blocking and windowing with message passing for metric ini-       |          |

| 1.0  | tialization                                                           | 19       |

| 1.9  | Shuffled decoding scheme, where $D_x = MAP$ -SISO decoder x=1,2,      | 20       |

| 1.10 | 8                                                                     | 21       |

| 1.11 | Reconfiguration of Instruction-set based processor and flexible hard- | 00       |

| 1 10 | ware                                                                  | 22       |

|      | Worst case configuration scenario                                     | 23       |

|      | Decoding latency of a 2048 bits frame                                 | 24       |

|      | FlexiTreP general architecture                                        | 27       |

|      | Memory reconfiguration process presented in [44]                      | 28<br>31 |

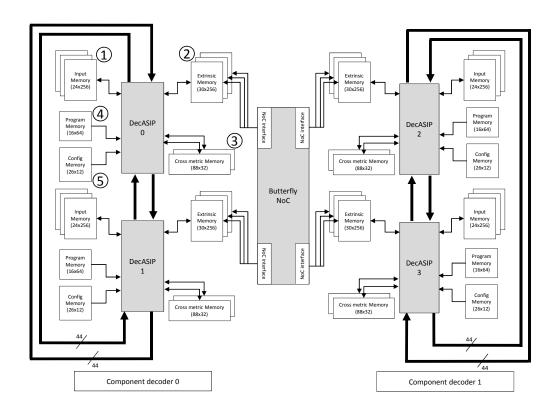

|      | UDec system architecture example with 2x2 ASIPs                       | 31<br>32 |

|      | Overview of the DecASIP pipeline stages with its register file and    | 32       |

|      | memory banks                                                          | 34       |

| 1.19 | ARP and QPP interleaved/deinterleaved address generator               | 35       |

| 1.20 | Butterfly NoC structure as used in the UDec architecture              | 37       |

| 1.21 | NoC packets format using Butterfly NoC                                | 37       |

| 2.1  | Flexible parameters transfer to configuration memory                  | 46       |

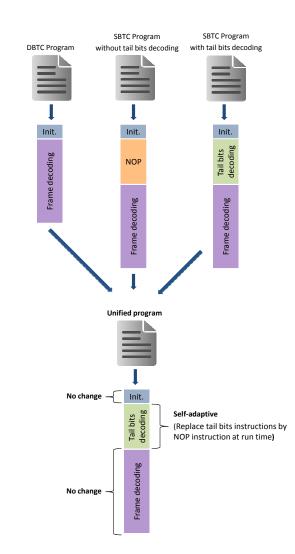

| 2.2  | Unified program for SBTC and DBTC modes                               | 51       |

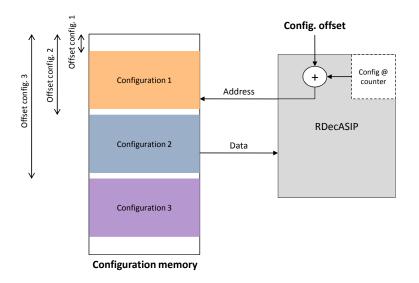

| 2.3  | Configuration memory address offset                                   | 54       |

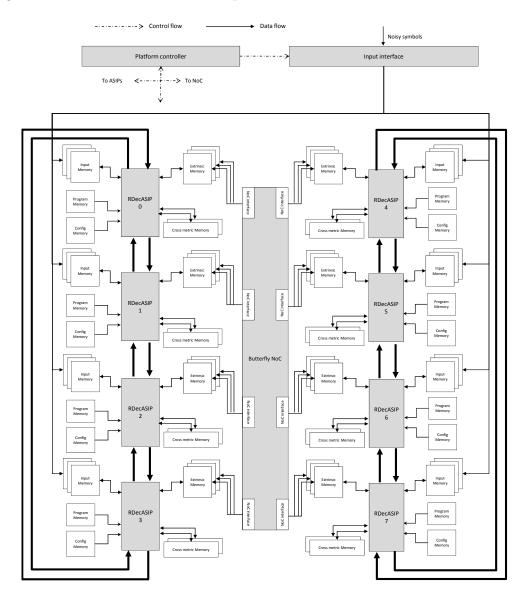

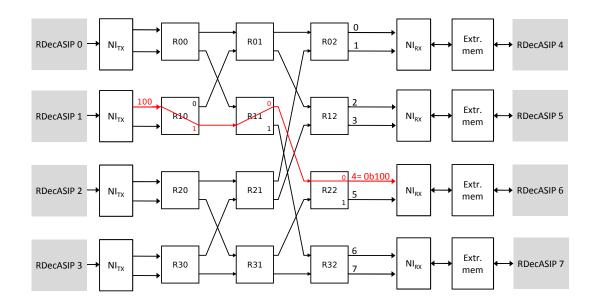

| 3.1  | UDec architecture implementing 8 RDecASIPs associated to a            |          |

|      | platform controller and an input interface                            | 62       |

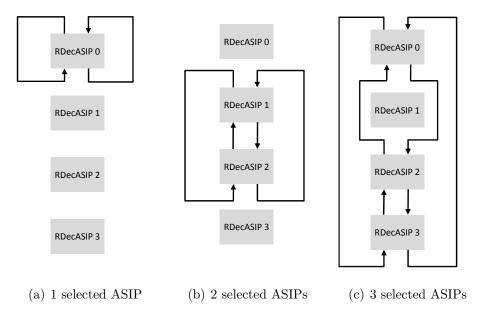

| 3.2  | Ring buses dynamic adaptation examples                                | 64       |

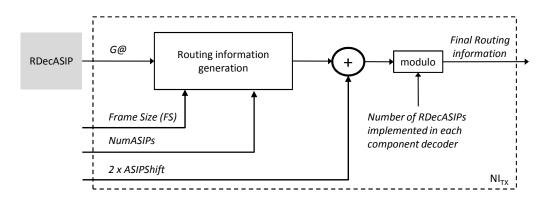

| 3.3  | Butterfly topology routing principle                                  | 65       |

| 3.4  | Complete routing information generator                                | 68       |

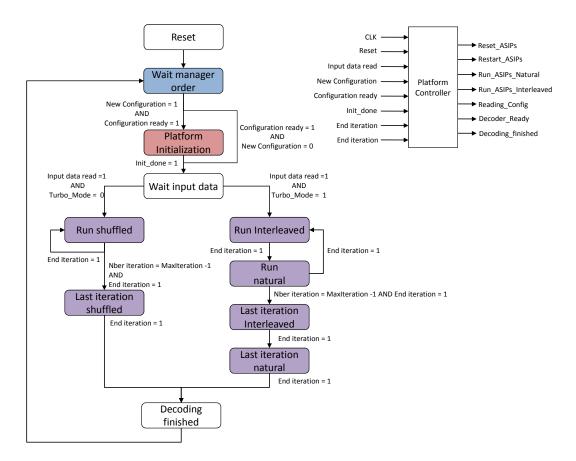

| 3.5  | Flexible UDec platform controller FSM                                 | 69       |

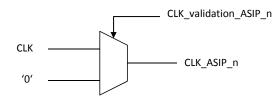

| 3.6  | Initial and new ASIP clock validation                                 | 72       |

| 3.7  | Architecture of the proposed bus interconnect                         | 75       |

| 3.8  | Master interface architecture overview                                    | 76  |

|------|---------------------------------------------------------------------------|-----|

| 3.9  | Slave interface architecture overview                                     | 77  |

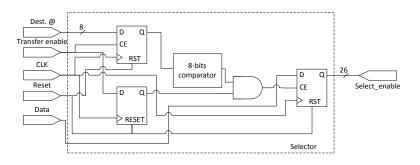

| 3.10 | Selector architecture overview                                            | 77  |

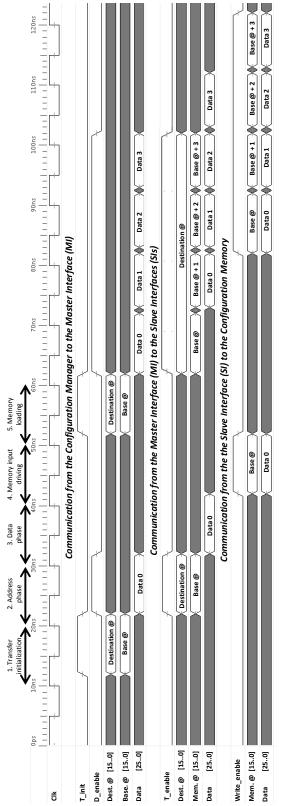

| 3.11 | Communication from the configuration manager to the configura-            |     |

|      | tion memory through the communication infrastructure                      | 79  |

| 3.12 | Architecture model for SystemC/VHDL mixed simulation                      | 82  |

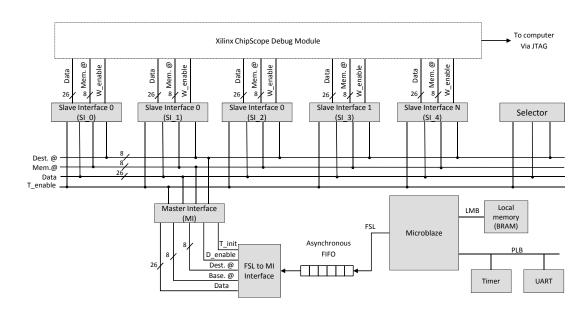

| 3.13 | Architecture of the prototype                                             | 84  |

| 3.14 | FSL to MI protocol adaptation                                             | 85  |

| 4.1  | Convergence of message passing method example of DVB-RCS,                 |     |

|      | code rate=6/7, 188 bytes frame, SNR=4.2dB, 5 bit quantification,          |     |

|      | Log-MAP algorithm                                                         | 90  |

| 4.2  | Number of iterations with message passing method, DVB-RCS,                |     |

|      | code rate=6/7, 188 bytes frame, SNR=4.2dB, 5 bit quantification,          |     |

|      | Log-MAP algorithm                                                         | 91  |

| 4.3  | Pre-computed configuration principle                                      | 94  |

| 4.4  | Configuration steps of the UDec platform                                  | 97  |

| 4.5  | Oversized configuration principle                                         | 100 |

| 4.6  | Oversized configuration search example. $1^{st}$ frame: size = 4800       |     |

|      | bits, throughput = 400 Mbps. $2^{nd}$ frame: size = 1920 bits, through-   |     |

|      | put = 280 Mbps. $N_{iterP=1} = 8, T = 10 \text{ and } P_{max} = 32 \dots$ | 104 |

| 4.7  | Stable configuration scenario                                             | 106 |

| 4.8  | Multi-frame configuration scenario                                        | 108 |

|      |                                                                           |     |

# List of Tables

| 1.1          | Dynamic configuration methods                                                                                                | 22       |

|--------------|------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2          | Configuration overview of the most relevant SoA works                                                                        | 30       |

| 1.3          | Interleaved/deinterleaved address generation step and seed values                                                            | 36       |

| 2.1          | Config memory contents of the DecASIP                                                                                        | 40       |

| 2.2          | Configuration parameters of the DecASIP for the Turbo decoding                                                               |          |

|              | mode                                                                                                                         | 41       |

| 2.3          | DecASIP program flexible parameters                                                                                          | 46       |

| 2.4          | Configuration memory architecture alternatives                                                                               | 48       |

| 2.5          | New proposed organization of the configuration memory                                                                        | 49       |

| 2.6          | ASIC synthesis results for the initial DecASIP and optimized Rde-<br>cASIP                                                   | 56       |

| 2.7          | Configuration and program bit load comparison in bits                                                                        | 50<br>57 |

| 3.1          | Routing information for a 2 selected ASIPs configuration                                                                     | 66       |

| 3.2          | Routing information for a 4 selected ASIPs configuration                                                                     | 66       |

| 3.3          | UDec platform controller configuration memory                                                                                | 71       |

| 3.4          | SoA Buses comparison                                                                                                         | 75       |

| 3.5          | Configuration loading impact for 4 active ASIPs                                                                              | 83       |

| 3.6          | Configuration transfer time in $ns$                                                                                          | 86       |

| 3.7          | FPGA synthesis results comparison                                                                                            | 86       |

| $3.8 \\ 3.9$ | Area of the proposed configuration architecture $\ldots$<br>Estimated Configuration transfer time in $ns$ for an ASIC imple- | 87       |

|              | mentation                                                                                                                    | 87       |

| 4.1          | Threshold values for DVB-RCS                                                                                                 | 92       |

| 4.2          | Comparison of necessary number of decoding iterations regarding                                                              |          |

|              | the level of sub-block parallelism for 53 bytes DVB-RCS interleav-                                                           |          |

|              | ing code rate= $6/7$ , SNR= $4.0$ dB, Log-MAP algorithm, FER= $1.6e^{03}$                                                    | 93       |

| 4.3          | Comparison of necessary number of decoding iterations regarding                                                              |          |

|              | the level of sub-block parallelism for 188 bytes DVB-RCS interleav-                                                          |          |

|              | ing code rate= $6/7$ , SNR= $4.0$ dB, Log-MAP algorithm, FER= $1.6e^{03}$                                                    | 93       |

| 4.4          | Estimated maximum throughput supporting the considered multi-                                                                |          |

|              | mode and multi-standard scenario with $N_{iterP=1}=8$ , $T=10$ and                                                           |          |

|              | $P_{max}=32$                                                                                                                 | 99       |

| 4.5          | Multi-frame scenario examples: $N_{iterP=1} = 8$ , $T = 10$ and $P_{max} = 321$                                              | 109      |

| 4.6          | Estimated maximum throughput comparison with $N_{iterP=1}=8$ , $T=10$                                                        |          |

| 4 🗁          | 110000                                                                                                                       | L09      |

| 4.7          | Configuration management comparison                                                                                          | 111      |

# Introduction

$T^{\rm HE}$  need of mobile connectivity has hugely increased in the first decade of the 21st century. Homes, schools, businesses and people are now connected together for sharing information as soon as that information is produced. This permanent connectivity has lead to a growing number of connected mobile devices such as laptops, tablets, mobile phones, watches and plenty of other portable devices. This multiplication of connected devices goes along with a large variety of applications and traffic types needing diverse requirements.

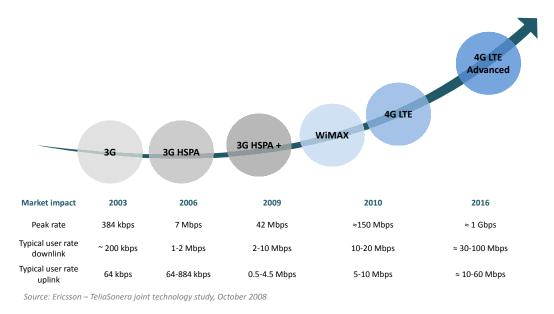

Figure 1: Communication standards evolution in mobile telephone networks

Accompanying this mobile connectivity evolution, the last years have seen considerable evolutions of wireless communication standards in the domain of mobile telephone networks, local/wide wireless area networks, and Digital Video Broadcasting (DVB). Figure 1 shows the evolution of standards for mobile since 2003 in terms of throughput requirements. Besides the increasing requirements in terms of throughput and robustness against destructive channel effects, the convergence of services in single smart terminal becomes a crucial and challenging feature. As an example, the fourth generation (4G) of cellular wireless standards aims at providing mobile broadband solution to laptop computer wireless modems, smartphones, and other mobile devices. Diverse features such as ultrabroadband Internet access, IP telephony, gaming services, and streamed multimedia are provided. In order to enable such advanced services at the algorithmic level, new state of the art data processing techniques have been developed and adopted in the emerging wireless communication standards.

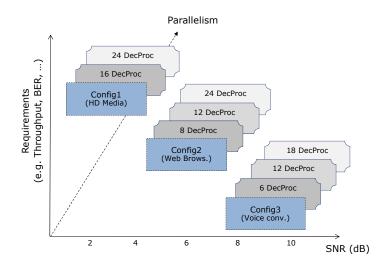

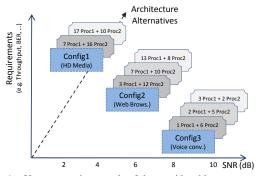

Figure 2: Usage scenario example of a considered multiprocessor platform

Channel decoding is a key feature of a wireless communication standard. It allows reliable data transfer targeting high throughput over unreliable communication channels. However, a channel coding technique is typically associated to a variety of parameters and configuration options (frame size, communication channel, signal-to-noise ratio, etc). Among channel decoding techniques, Turbo codes are frequently adopted in the recent wireless standards to reach a very low bit error rate (BER). Furthermore, the high throughput requirement of emerging services imposes the efficient exploitation of different parallelism levels of the underlying algorithms. In this context, multiprocessor architecture is a promising approach to reach high flexibility and high throughput. In fact, flexible multiprocessor architectures are generally designed to support a set of communication standards which correspond to some specific application needs and usage scenarios. Each usage scenario corresponds to particular requirements for example in terms of throughput, latency, error rates, and/or others. Figure 2 gives an example of such usage scenario which corresponds to a mobile terminal supporting different services (High Definition Multimedia, Web Browsing, Voice Conversation) at different channel conditions. At design-time, the multiprocessor architecture must be dimensioned to support the highest requirements while, at run-time, the number of processors can be chosen depending of the current level of requirements. Considering the emerging multi-mode and multi-standard applications, as well as the increasing interest for Software Defined Radio and Cognitive Radio applications, Turbo decoder architectures have to be able to be dynamically adapted to face emerging requirements.

#### **Problematic and contributions**

In this context, intensive research has been conducted to provide flexible Turbo decoder targeting high throughput, multi-mode, multi-standard and power consumption efficiency. However, flexible Turbo decoder implementations are not often designed regarding dynamic reconfiguration issues in the context of high throughput, multi-mode and multi-standard scenario requiring high speed configuration switching. In fact, most of the existing related works have proposed flexible hardware platforms while trying to optimize their efficiency in terms of area, throughput, and energy consumption. Very few contributions have considered the crucial requirement of rapid dynamic configuration and the related implementations and costs. Starting from this assessment, this thesis work aims to propose novel contributions in order to reach efficient and high speed configuration of a flexible multiprocessor Turbo decoder. As a base architecture, we consider an ASIP<sup>1</sup>-based flexible Turbo decoder developed at the Electronics Department of Telecom Bretagne in Brest. The considered ASIP, namely DecASIP, supports several wireless communication standards and is integrated in a scalable and flexible multiprocessor platform, namely  $UDec^2$ .

Toward the above mentioned objective, the following contributions are detailed in this thesis:

- Configuration optimization of the flexible DecASIP processor

- Proposal of an efficient configuration parameters storage.

- Optimization of the configuration memory organization in order to provide a low latency configuration information transfer.

- Proposal of the support of multi-configuration storage and high speed reinitialization of the ASIP.

- Proposal of a generic program in order to reduce the configuration load.

These contributions have been presented as a poster at GRETSI national conference and as regular presentations at ISCAS'13 and ISVLSI'13 international conferences.

• Design of a configuration infrastructure for the UDec multi-ASIP architecture

- Optimizations of the platform controller and the interconnection structure of the UDec architecture in order to increase its flexibility.

- Implementation of a complete configuration infrastructure for high speed

<sup>&</sup>lt;sup>1</sup>Application Specic Instruction-set Processor

<sup>&</sup>lt;sup>2</sup>Universal channel Decoder

configuration of the multi-ASIP UDec architecture.

These contributions have been realized during a collaboration with Pr. Michael Hübner in the context of a researcher mobility of six months at the University of Bochum, Germany and have been presented as regular presentations at ReCoSoC'13 and DSD'13 international conferences.

#### • Configuration management of the UDec architecture

- Definition of a configuration management where configuration information is stored in a global configuration memory.

- Proposal of two configuration management techniques where configuration information is generated at run-time.

These last contributions have not been yet published. Several papers are currently under revision and will be submitted soon.

#### Thesis outline

This thesis manuscript is composed of four chapters as described below:

**Chapter 1** firstly introduces the basic concepts related to Turbo codes and Turbo decoding techniques. An overview of the fundamental concepts of channel coding and the basics for error-correcting codes are introduced. Then, the Turbo codes and their basic components are presented. Next, The Maximum Aposteriori Probability algorithm for Turbo decoding and its different levels of parallelism are described. The second section introduces the dynamic configuration problematic for multi-mode and multi-standard Turbo decoders. This is followed by the State of the Art in flexible channel Turbo decoder design. The final part of this chapter presents the initial UDec architecture which constitutes the starting point of this thesis work.

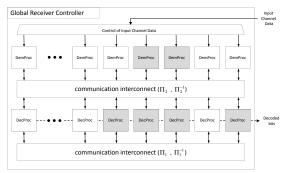

Chapter 2 proposes to tackle the optimization of the initial DecASIP processor for Turbo decoding in order to offer an efficient dynamic configuration of the multi-ASIP UDec architecture for Turbo decoding. An analysis of the configuration lacks of the initial DecASIP architecture is proposed. Based on these observations, optimizations to reach an efficient dynamic reconfiguration are described. These optimizations lead to the implementation of a new processor called RDecASIP. The final part of this chapter provides implementations results in terms of area overhead and configuration load. Finally, the architectural choices are discussed. **Chapter 3** addresses the dynamic configuration of the UDec multi-ASIP architecture for Turbo decoding. The chapter proposes to study the lacks of flexibility of the UDec architecture and points out needs to support the dynamic configuration of the platform. A complete reconfigurable platform implementing eight RDecASIPs is presented and detailed. In order to transfer the configuration to each component of the architecture, the second part of this chapter addresses the definition and the implementation of a dedicated configuration infrastructure providing an efficient and low complexity solution for configuration data transfer to each configuration memory of the implemented RDecASIPs. The proposed configuration infrastructure is evaluated and validated through a SystemC/VHDL mixed simulation model. Finally, implementation results and configuration timing performance are discussed targeting both FPGA and ASIC implementation.

**Chapter 4** studies the configuration management of the UDec architecture in order to offer high throughput and high decoding performance. An analysis of the dynamic evolution of the number of decoding iterations regarding the level of sub-block parallelism is provided in order to be integrated in the configuration management of the UDec architecture. Then, this chapter presents two configuration managements. The first one proposes to store the configuration information for all possible configurations in a global memory while the second one proposes the run-time configuration generation respecting the hard constraints in terms of throughput and error rate in a multi-mode and multi-standard scenario. Turbo codes and state of the art in channel decoder design

$T^{\rm HIS}$  first chapter starts with an overview of a typical communication system and an introduction of the main concepts of error correcting codes. As this thesis work targets the dynamic configuration of Turbo decoders, the Turbo coding and the Turbo decoding principles are introduced. Afterwards, the state of the art in flexible channel Turbo decoder design is presented. One of these contributions has been developed at the Electronics department of Telecom Bretagne in Brest using a flexible multi-ASIP approach called UDec. The final part of this chapter presents the initial UDec architecture which constitutes the starting point of this thesis work.

### 1.1 Context of channel coding

In the context of digital wireless communication systems, information is transmitted over a noisy channel that may cause errors on the received message. Channel coding techniques are used in order to reduce the noise disturbances effects by introducing redundant information to the original message. These coding techniques seek to increase as much as possible the correction capabilities of the communication system to reach the theoretical limits defined by Shannon [1].

Figure 1.1: Elements of a digital communication system

#### 1.1.1 Communication system

A simplified block diagram of a communication system is presented in Figure 1.1. It consists of a *source* that generates a flow of bits representing a particular digital message to be transmitted. This message can be related for example to a video or audio signal, to digital data or be the samples of an analog signal. At the receiver, an estimated message is provided to the *destination*. In an ideal case, the estimated message is identical to the original message generated by the source. Due to noise disturbances introduced by the channel, a *channel encoder* has to be used at the transmitter such as the additional redundant bits can be used by the *channel decoder* for error correction at the receiver. Then, the modulator maps the encoded message into signal waveforms to be transmitted over the channel. Modulation is performed by varying the amplitude, the phase, the frequency or a combination of the three signal parameters of a sinusoidal waveform called a *carrier*. The *channel* reflects the communication medium over which the

message is transmitted (e.g. air, wire-line, optic fiber, etc.). At the receiver, the *demodulator* extracts the information-bearing signal from the modulated carrier. Finally, the *channel decoder* estimates the most probable transmitted message based on the coding rules and the characteristics of the channel.

When a set of data has to be encoded, it is generally admitted that a step of segmentation has to be performed before the encoding process. Indeed, this step prevents excessive complexity and memory requirement of the decoding algorithm at the receiver. The segmentation process consists in dividing the set of data in several parts called *frame* in this document. This process is driven by the application requirements (i.e. throughput, latency, etc...). The maximal size of a frame and the segmentation rules are defined by the targeted standard. For instance, the LTE standard [2] supports frame size from 40 to 6144 bits for Turbo codes. Following the segmentation step, each frame is then encoded and mapped to be transmitted.

#### 1.1.2 Channel code performance

The channel code performance represents the ability of a code to correct transmissions errors. It depends on the Signal-to-noise ratio (SNR) value and the decoding technique used. It is presented in terms of the Frame Error Rate (FER) or Bit Error Rate (BER) values. The benefit that a code associated to a specific decoding technique provides is quantized in terms of the coding gain which is defined as the SNR difference between the coded and uncoded curves for a given error rate value. The coding gain is usually expressed in decibels (dB).

Past years have seen the emergence of two main coding techniques providing excellent error corrections properties: LDPC codes and Turbo codes. The next section introduces the Turbo coding concept which is the channel coding technique focused of this thesis work.

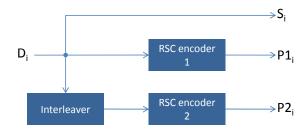

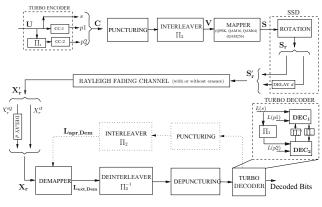

#### 1.1.3 Turbo encoding

The advent of Turbo codes [3] marks a major turning point for digital telecommunication. Indeed, Turbo decoding technique was the first practical solution to closely approach the Shannon's theoretical limits. For the recent and emerging wireless communication standards supporting Turbo codes, a Turbo encoder is usually built from the parallel concatenation of two Recursive Systematic Convolutional (RSC) encoders separated by an interleaver as shown in Figure 1.2. The first RSC encoder receives the input data bits stream  $D_i$  in a natural order while the second RSC encoder receives the data in an interleaved one. Three output streams are generated: the systematic  $S_i$ , which is identical to the input stream and two parities  $P1_i$  and  $P2_i$  generated by the encoders in natural and

Figure 1.2: Turbo encoder: Parallel concatenation of two RSC encoders

Figure 1.3: Non-recursive non-systematic and Non-recursive systematic encoders

interleaved domain respectively. In recent standards, we observe two types of RSC encoders: the Double Binary Turbo Code (DBTC) encoder and the Single Binary Turbo Code (SBTC) encoder. The DBTC encoder generates double binary symbols by encoding bit pairs of the incoming data bits stream while the SBTC encoder encodes bitwise the incoming data bits stream.

The rest of this section shows the concepts of the RSC encoders and interleaving rules introduced in recent standards such as WiMax, DVB-RCS and LTE.

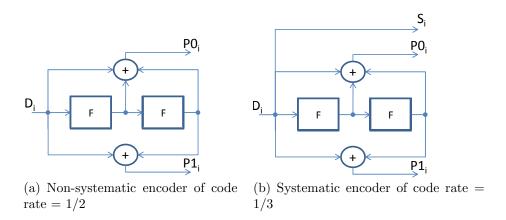

#### 1.1.3.1 Recursive Systematic Convolutional encoders

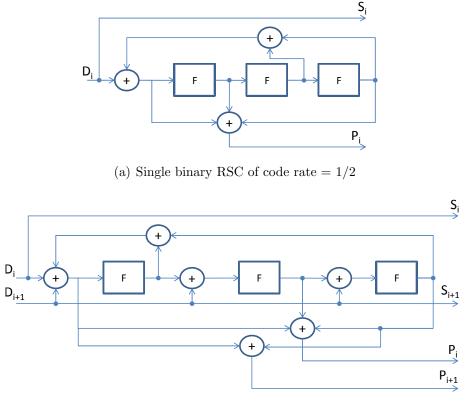

Convolutional codes have been widely used in wireless telecommunication standards due to their low complexity. The most common form of convolutional encoder is the non-recursive and non-systematic convolutional encoder presented in Figure 1.3(a). This type of encoder can not be used for Turbo encoding since it is not systematic. A second form of non-recursive encoder (Figure 1.3(b)) introduces a systematic output but it is not suitable for Turbo decoding because of

(b) Double binary RSC of code rate = 1/2

Figure 1.4: Recursive systematic convolutional encoders

the poor distance properties of the resulting code. Finally, RSC encoders shown in Figure 1.4 introduce the feedback of one of the output. The encoders shown in Figure 1.4(a) presents a single binary RSC encoder. It encodes, at each instant i, one bit of the input data stream. Figure 1.4(b) presents a double binary RSC encoder in which two bits of the input stream are encoded at each instant i.

These encoders have very simple structure that can be implemented with a set of flip-flops and XOR operators. The number of states of the encoder is  $2^p$  when p flip flops are implemented. Moreover, the value p + 1 is known as the constraint length of the code. The code rate of a convolutional code is defined by the ratio n/l where n is the number of bits that composes the input symbol  $D_i$  and l represents the number of bits of the coded symbol with l > n. In the example of Figure 1.3(a), the code rate is 1/2 since at each instant i, the input bit  $D_i$  is encoded to a two bits coded symbol that consists of  $P0_i$  and  $P1_i$ . In the example of Figure 1.3(b), the code rate is 1/3 since at each instant i, the input bit  $D_i$  is encoded to a three bits coded symbol that consists of  $P0_i$  and  $P1_i$ .

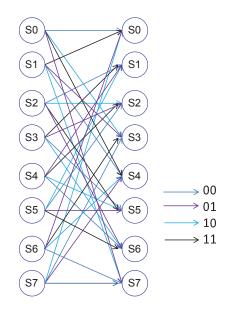

**Figure 1.5:** Trellis diagram of the RSC encoder of Figure 1.4(b)

$P1_i$  and  $S_i$ . The code rate of both RCS encoders presented in Figure 1.4 is 1/2. In order to adapt the code rate, the puncturing technique [2, 4] can be used. It consist in removing some of the parity bits after encoding in order to increase the code rate. Another commonly used representation of convolutional encoding is the trellis diagram [5] which consists of nodes and branches. A node represents the state S of the code while a branch represents a transition from one state to another state due to an input bit or bit pair in case of double binary convolutional code. An example of a trellis diagram corresponding to the Double binary RSC encoder presented in Figure 1.4(b) is given in Figure 1.5. In this example, the constraint length of the code is 4, i.e. p = 3. Thus, the number of states of the encoder is  $2^p = 8$ . It can be noted that each state has  $2^b = 4$  possible transitions, where b = 2 is the number of bits per symbol at the input of the encoder.

For the first frame which has to be encoded, the initial state of the encoder is typically the all-zero state. In order to reinitialize the encoder at the end of the encoding process, tail bits are encoded in order to force the encoder back to the all-zero state and then start to encode the next frame. This technique called *zero padding* in the literature ensures that the encoder starts and finishes in the same state. However, extra parity bits are generated and added to the encoded message that leads to a minor loss of transmission bandwidth. Standards as WiMAX and DVB-RCS adopt the *Tail biting* scheme. It uses a circular RSC encoder, which allows the initialization with a particular state for each frame. This state, called circulation state, ensures that the encoder returns to the same state at the end

of the encoding process. The existence of such a state is guaranteed when the size of the encoded frame is not a multiple of the period of the encoding recursive generator [6]. The value of the circulation state depends on the frame to encode and is determined by a pre-ending step. Following the initialization of the encoder to the all-zero state, the frame is encoded once. From the final state reached at the end of the encoding process, the circulation state is computed using simple combinational operators or a lookup table as described in [6].

#### 1.1.3.2 Turbo codes interleavers

Interleavers provide an efficient solution to enhance the protection of data against destructive channel effects. For that purpose, the data is temporally dispersed. In the context of Turbo codes, the parallel concatenation of two RSC encoders provides two copies of the same symbol at different intervals of time thanks to the interleaver that separates the two encoders. This solution allows retrieving at least one copy of the symbol if the second one has been distorted during the transmission. An interleaver ( $\Pi$ ) satisfying this property can be verified by studying the dispersion factor S given by the minimum distance between two symbols i and j in natural order and interleaved order:

$$S = \min_{i,j} (|i-j| + |\Pi(i) - \Pi(j)|)$$

(1.1)

The design of interleavers respecting a dispersion factor can be reasonably achieved through the S-random algorithm proposed in [7]. However, even if this kind of interleaver can be sufficient to validate the performance in the convergence zone of a code, it does not achieve a good asymptotic performance. Therefore to improve the latter, the design of the interleaver must also take into account the nature of component encoders. Complexity of the hardware implementation should, in addition, be taken into account. In fact, the recent wireless standards specify performance and hardware aware interleaving laws for each supported frame length.

In following paragraphs, the interleaving laws associated to Turbo codes for WiMAX and LTE standards are described.

WiMAX: For this standard, using double binary Turbo code, two levels of interleaving are proposed.

1. The first one is the bit swapping in the alternate couple i.e.  $(a_j, b_j) = (b_j, a_j)$  if  $j \mod 2 = 0$  where  $j = 0, 1, \dots N-1$  and N is the number of couples in the frame.

2. The second one is given by the following expression:

$$\Pi(j) = (P_0 \times j + P + 1) \mod N \tag{1.2}$$

where

$$P = 0 \qquad \text{if } j \mod 4 = 0$$

$$P = \frac{N}{2} + P_1 \qquad \text{if } j \mod 4 = 1$$

$$P = P_2 \qquad \text{if } j \mod 4 = 2$$

$$P = \frac{N}{2} + P_3 \qquad \text{if } j \mod 4 = 3$$

where the values of parameters  $P_0$ ,  $P_1$ ,  $P_2$  and  $P_3$  depend on the frame size and are defined in the corresponding standard specification [4].

**LTE:** For this standard, using single binary Turbo code, the interleaver is called quadratic polynomial permutation (QPP). It is given by the following expression:

$$\Pi(j) = (f_1 j + f_2 j) \mod N \tag{1.3}$$

where  $f_1$  and  $f_2$  are integers parameters defined in the standard [2] and depend of the frame size N.

The previous sections have introduced the basic concepts of Turbo coding. The next section presents the Turbo decoding principle which is the considered application of this thesis work.

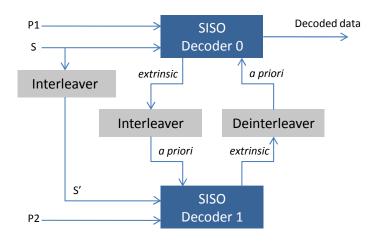

#### 1.1.4 Turbo decoding

Turbo decoding principle is based on an exchange of probabilistic information, called *extrinsic information* between two (or more) component decoders dealing with the same received set of data. As shown in Figure 1.6, a typical Turbo decoder consists of two decoders operating iteratively on the received frame. The first component (SISO decoder 0 in Figure 1.6) works in natural domain while the second (SISO decoder 1 in Figure 1.6) works in interleaved domain. The Soft-Input Soft-Output (SISO) decoders operate on soft information to improve the decoding performance. Thus, besides its own channel input data, each SISO decoder in order to improve its estimation over the iterations. Usually, but not necessary, the computations are done in the logarithmic domain. Each decoder calculates the Log-Likelihood Ratio (LLR) for the  $i^{th}$  data bit  $d_i$  as

Figure 1.6: Typical Turbo decoder structure

$$L(d_i) = ln \frac{Pr(d_i = 1|y)}{Pr(d_i = 0|y)}$$

(1.4)

Input LLRs causing trellis transition can be decomposed into 3 independent terms as

$$L(d_i) = L^{ap}(d_i) + L^{sys}(d_i) + L^{par}(d_i)$$

(1.5)

where  $L^{ap}(d_i)$  is the a-priori information of  $d_i$ ,  $L^{sys}(d_i)$  and  $L^{par}(d_i)$  are the channel measurement of the systematic and parity parts respectively. Each SISO decoder generates extrinsic information that is sent to the other decoder. Extrinsic information becomes the a-priori information  $L^{ap}(d_i)$  for the other decoder as shown in Figure 1.6.

Several algorithms for this SISO decoding have been proposed in the literature. The Soft Output Viterbi Algorithm (SOVA) and the Maximum Aposteriori Probability (MAP) algorithms are the most frequently used. The SOVA algorithm [8] is a soft output variant of the Viterbi algorithm targeting the minimization of the FER while the MAP algorithm [9] targets to minimize the BER. This last algorithm has been simplified in [10] to propose the Max-Log-MAP algorithm that is most often adopted because of the efficient hardware implementation possibility. For a better understanding of the architectural and configuration issues highlighted in the rest of this thesis work, the next section provides a short introduction to the MAP decoding.

#### 1.1.4.1 The MAP Algorithm

A MAP decoder provides, for each coded symbol  $d_i^{symb}$  consisting in m bits of a frame of N coded symbols,  $2^m$  a posteriori probabilities given the channel output y received by the decoder. The hard decision on the corresponding value j, i.e.  $d_i^{symb} = j$ , that maximizes the *a posteriori* probability is expressed in terms of joint probabilities as:

$$Pr(d_i^{symb} = j|y) = \frac{P(d_i^{symb} = j, y)}{\sum_{k=0}^{2^m - 1} P(d_i^{symb} = k, y)}$$

(1.6)

The trellis structure of the code enables us to decompose the calculation of joint probabilities between past and future observations. This decomposition defined by Equation (1.7) uses a Forward recursion metric  $\alpha_i(S)$ , which gives the probability of the state S at instant i computed from the past values received from the channel. It also uses a Backward recursion metric  $\beta_i(S)$ , which gives the probability of the state S at instant i computed from the future values received from the channel and a Branch metric  $\gamma(S', S)$ , which gives the state transition probability from state S' to state S of the trellis at instant i.

$$Pr(d_i^{symb} = j|y) = \sum_{(S',S)/d_i^{symb} = j} \alpha_i(S')\gamma_i(S',S)\beta_{i+1}(S)$$

(1.7)

The Forward recursion metric and Backward recursion metric are expressed by Equation (1.8) and Equation (1.9) respectively.

$$\alpha_{i+1}(S) = \sum_{S'=0}^{2^m - 1} \alpha_i(S') \gamma_i(S', S), i \in 0...N - 1$$

(1.8)

$$\beta_i(S) = \sum_{S'=0}^{2^m - 1} \beta_{i+1}(S')\gamma_i(S', S), i \in N - 1...0$$

(1.9)

The initialization of these metrics depends of the initial and final state of the trellis. The Branch metric is given by Equation (1.10).

$$\gamma_i(S', S) = p(y_i|x_i) \cdot Pr^a(d_i^{symb} = d_i^{symb}(S', S))$$

(1.10)

where  $p(y_i|x_i)$  is the channel transition probability.  $x_i$  and  $y_i$  are the  $i^{th}$  transmitted modulated symbol and received symbol respectively. Assuming an equiprobable source, the *apriori* probability  $Pr^a(d_i^{symb} = d_i^{symb}(S', S)) = \frac{1}{2^m}$ . The

generated extrinsic information corresponds to the aposteriori probability (Equation (1.6)) in which the branch metric is modified in order to remove the symbol channel input since the other decoder knows this information.

The next section introduces the different levels of parallelism that can be exploited considering a MAP-SISO decoder. It particularly highlights the SISO decoder level parallelism.

#### 1.1.4.2 Parallelism in Turbo decoding

Turbo decoding provides an efficient solution to reach very low error rate performance at the cost of high processing time for data retrieval. Researches targeting the exploitation of parallelism have been conduced in order to achieve high throughput. These parallelism levels that can be categorized in three groups: Metric level, SISO decoder level, Turbo decoder level.

The Metric level parallelism concerns the processing of all metrics involved in the decoding of each received symbol inside a MAP-SISO decoder. For that purpose, the inherent parallelism of the trellis structure [11, 12] and the parallelism of the MAP computation can be exploited [11, 12, 13]. The MAP-SISO decoder level parallelism consists in duplication of the SISO decoders in natural and interleaved domain, each executing the MAP algorithm on a sub-block of the frame to decode. Finally, the Turbo decoder level parallelism proposes to duplicate whole Turbo decoders to process iterations and/or frames in parallel. However, this level of parallelism is not relevant due to the huge area overhead of such an approach (all memories and computation resources are duplicated). Moreover, this solution presents no gain in frame decoding latency.

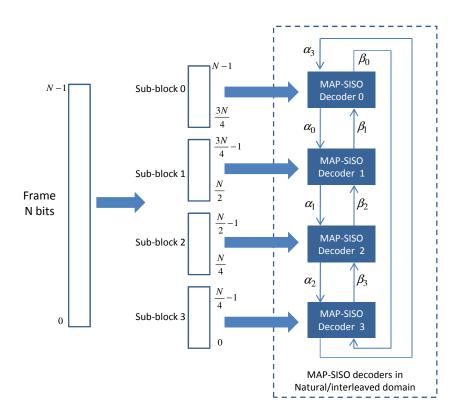

The SISO decoder level parallelism hugely impacts the configuration process of a multiprocessor Turbo decoder. Indeed, the number of SISO-decoders that have to be configured and the configuration parameters associated with each SISO-decoder are both dependent of this parallelism level. At this level, three techniques are available: Frame sub-blocking, Windowing, and Shuffled decoding.

**Frame sub-blocking:** In sub-block parallelism, each frame is divided into M sub-blocks and then each sub-block is processed on a MAP-SISO decoder (Figure 1.7) using adequate initializations. Besides duplication of MAP-SISO decoders, this parallelism imposes two other constraints. On the one hand, interleaving has to be parallelized in order to scale proportionally the communication bandwidth. Due to the scramble property of interleaving, this parallelism can induce communication conflicts except for interleavers of emerging standards that are conflict-free for certain parallelism degrees. In case of conflicts an appropriate

Figure 1.7: Sub-block parallelism with message passing for metric initialization

communication structure, e.g. Network on Chip (NoC), should be implemented for conflict management [14]. On the other hand, MAP-SISO decoders have to be initialized adequately either by acquisition or by message passing. In [15] a detailed analysis of the parallelism efficiency of these two methods is presented which gives favor to the use of message passing technique. The message passing, which initializes a sub-block with recursion metrics ( $\alpha$  and  $\beta$ ) computed during the previous iteration in the neighboring sub-blocks (Figure 1.7), needs not to store the recursion metric and time overhead is negligible compared to the acquisition method.

Sliding window: In addition to the sub-block parallelism, the sliding window technique is commonly used at the SISO decoder level. It allows to reduce the memory size required to store the state metric values by splitting each sub-block into a number of small windows, where the MAP decoding is applied to each window independently [16, 17]. To illustrate this technique, let us assume that a backward-forward schedule is adopted for the state metric recursions of the MAP-SISO decoder (Figure 1.8). In this schedule,  $\beta$  recursion metrics are computed

Figure 1.8: Sub-blocking and windowing with message passing for metric initialization

before  $\alpha$  recursion metrics. Thus, using only sub-block parallelism would require storing the intermediate recursion metrics calculated in the backward recursion in an internal memory, called *cross metric memory*. Therefore, this memory has to have a memory depth equals to the sub-block length. In order to increase the area efficiency of the design, sub-blocks are further divided into L windows [16, 17]. This implies cross metric memory depth reduction to the size of a window (with an additional requirement of storage state metric boundaries values of all windows to be used in the next iteration). Consequently, each MAP-SISO decoder processes the sub-block, window by window as shown in Figure 1.8. In the example of Figure 1.8, the level of sub-block parallelism is 2. Each MAP-SISO decoder uses two recursion units and employs backward-forward schedule for window processing. The first recursion unit (processing in the backward direction of the trellis) executes on window j while the second recursion unit (processing in the forward direction of the trellis) executes on window j-1 at the same time (as shown in Figure 1.8). Boundary state metrics are then exchanged between windows either immediately within the same iterations or stored and used in the subsequent iteration as illustrated in Figure 1.8.

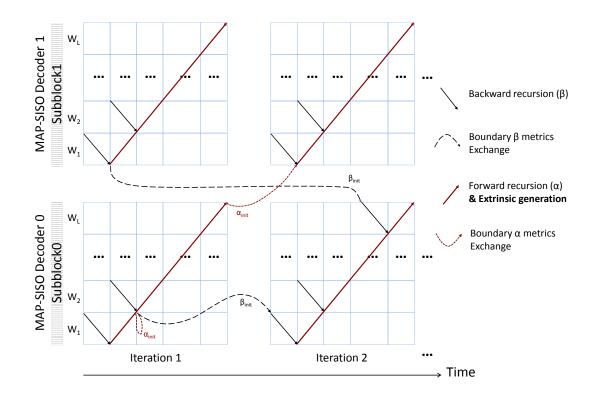

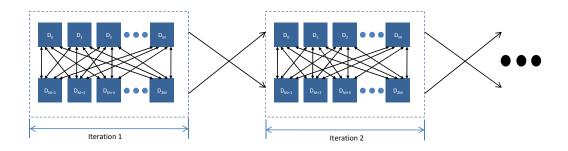

**Figure 1.9:** Shuffled decoding scheme, where  $D_x = MAP$ -SISO decoder x=1,2,...

**Shuffled Turbo decoding:** The principle of the shuffled decoding technique has been introduced in [18]. In this mode, all component decoders work in parallel and exchange extrinsic information as soon as it is created. Thus the shuffled decoding technique performs decoding (computation time) and interleaving (communication time) fully concurrently while serial decoding implies waiting for the update of all extrinsic information before starting the next half iteration (Figure 1.9). Thus, by doubling the number of MAP-SISO decoders, component-decoder parallelism halves the iteration period in comparison with originally proposed serial Turbo decoding. Nevertheless, to preserve error-rate performance with shuffled Turbo decoding, an overhead of iteration between 5 and 50 percent is required depending on the MAP computation scheme, on the degree of sub-block parallelism, on propagation time, and on interleaving rules [15].

The previous sections provided the basic background on Turbo codes and on the different levels of parallelism which can be exploited in order to reach high throughput requirement imposes by emerging communication standards. The next section introduces configuration methods in embedded system and tackles the specific dynamic configuration scenario of a Turbo decoder in a multi-mode, multi-standard and mobility context.

### 1.2 Dynamic configuration of flexible Turbo Decoders

#### 1.2.1 Dynamic configuration in embedded systems

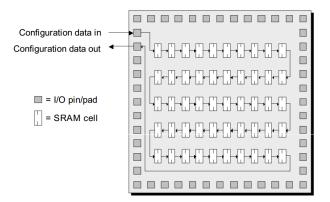

In the context of telecommunication, the multiplication of wireless standards is introducing the need of flexible and dynamically reconfigurable multi-mode and multi-standard baseband receivers. The methods to reconfigure an architecture are multiple and can be organized in three main categories. The first one corresponds to architectures that are configured through a stream of configuration bits that are spread over the architecture components to configure the data and control path. For instance, the configured components can be multiplexers, Lookup Tables (LUTs), Arithmetic Logic Unit (ALU), etc. This configuration method is typically applied to Field-Programmable Gate Array (FPGA) in which LUTs, multiplexers and programmable routing switches are configured through a bitstream load at power-up. Recent FPGA technology also proposes dynamic configuration techniques allowing hardware reconfiguration at run-time. The configuration load of recent FPGAs represents several Mega Bytes of information that can be loaded from various sources as an external memory, a host PC, a microcontroller, etc. Figure 1.10 shows bitstream chain in a FPGA which is sent from outside and is then spread inside the component. The configuration of the SRAM points of the FPGA can be seen as a huge shift register (in practice, the configuration chain is divided into frames and latches are used).

Figure 1.10: FPGA reconfiguration chain

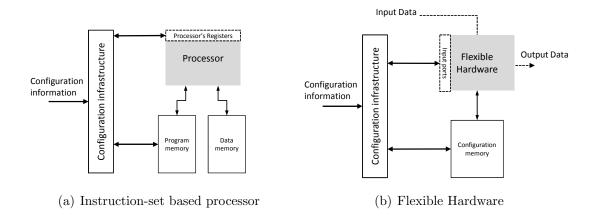

The second category corresponds to instruction-set based processors that provide inherently high flexibility in terms of control logic design. The reconfiguration of these architectures is done by context switching. A context switch is the switching of a processor from one task to another. For that purpose, the program instructions/counter and processor's registers have to be initialized for the new task. As shown in Figure 1.11(a), depending on the system architecture, a configuration infrastructure could be needed to load new instructions in the program memory of the processor and modify processor's registers values before the execution of a new task.

The third category corresponds to traditional parametrized hardware architectures. The flexibility of these designs is incorporated by the designer through the use of initialization parameters loaded from a configuration memory or input ports of the architecture. Figure 1.11(b) shows a parametrized hardware

Figure 1.11: Reconfiguration of Instruction-set based processor and flexible hardware

| Category           | Configuration<br>data | Configuration<br>load   | Configuration<br>granularity |

|--------------------|-----------------------|-------------------------|------------------------------|

| Stream of          | bitstream             | From $\approx 10$ to    | Low                          |

| configuration bits | Ditstream             | $\approx 100$ of Mbytes | (LUTs, switches)             |

| Instruction-set    | Registers             | from $\approx 10$ to    | High                         |

| based processor    | and Program           | $\approx 1000$ Mbytes   | (Software)                   |

| Parametrized       | Ports and             | $\leq 1$                | Medium                       |

| hardware           | config. memory        | Kbytes                  | (Control/data                |

|                    |                       |                         | paths, operands)             |

Table 1.1: Dynamic configuration methods

design which is configured through a configuration memory and configuration information from input ports. The configuration infrastructure associated to the architecture allows the configuration memory loading with configuration parameters and drives the configuration input ports. This solution provides the lowest configuration load since the number and size of each configuration parameter are optimized at design time.

Table 1.1 summaries the main features of the three configuration methods described in previous paragraphs. It can be notice than the ASIP technology can be classed in both second and third categories. Indeed, an ASIP is an instruction-set based processor that can incorporate configuration memories and configuration pins if it is necessary.

The next section highlights the configuration issue of a Turbo decoder in a multi-mode and multi-standard context.

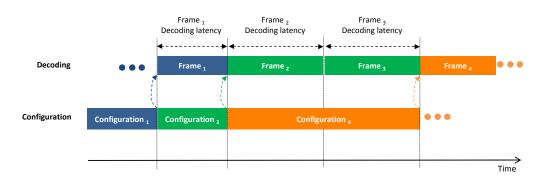

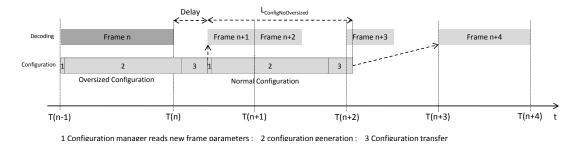

Figure 1.12: Worst case configuration scenario

#### 1.2.2 Dynamic configuration in multi-mode and multistandard scenario

When a Turbo decoder is designed to support several communication standards, the decoder behavior has to be adapted in order to respect the application requirements and to take into account the communication channel quality. In this thesis work, the scenario presented in Figure 1.12 is considered as the worst case configuration scenario that should be met by a multi-mode and multi-standard Turbo decoder in mobility.

In this scenario, the Turbo decoder deals with input frames that have to be decoded for multiple applications that use different communication standards or modes. Each application is associated with throughput and BER objectives. Moreover, considering a mobile terminal, the configuration associated to an application has to be adapted temporally depending on the communication channel quality evolution. Consequently, as shown in Figure 1.12, each frame received by the Turbo decoder is associated to a specific configuration which takes into account the application requirements and the channel quality. In order to avoid extra delays between two frames associated with different configurations, the configuration process for a frame (i.e. computing and loading the new configuration) can be performed during the processing on the current frame. Thus, the Maximum Configuration Latency (MCL) for a frame k ensuring a null extra delay between two frames is evaluated using Equation (1.11).

$$MCL(k) = N_{PrevFrame}(k) \cdot \frac{FrameSize(k-1)}{Throughput(k-1)}$$

(1.11)

where k is the  $k^{th}$  received frame,  $N_{PrevFrame}$  is the number of consecutive frames decoded with the same configuration that precede the frame k, FrameSize(k-1)is the  $k-1^{th}$  frame size in bits and Throughput(k-1) is the throughput requirement associated with the  $k-1^{th}$  data frame. In the example presented in Figure 1.12,  $N_{PrevFrame}(2) = 1$  since one frame is decoded with the  $Configuration_1$

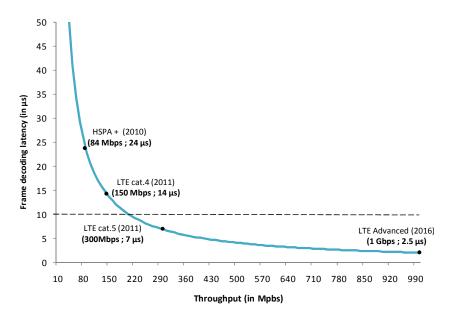

Figure 1.13: Decoding latency of a 2048 bits frame

while  $N_{PrevFrame}(3) = 2$  since two frames are decoded with the Configuration<sub>2</sub>. MCL, FrameSize and Throughput are expressed in seconds, bits and bits/s respectively. Assuming the worst case when  $N_{PrevFrame}(k) = 1$ , the maximum configuration latency critically decreases with high throughput targeted by emerging and future wireless communication standards as shown in Figure 1.13. This figure presents the decoding latency of a 2048-bit data frame for different current and emerging wireless communication standards. Regarding the throughput requirement evolution, the decoding latency of a frame decreases and will reach latencies around few microseconds in LTE-advanced standard. Thus, considering the dynamic configuration scenario presented in this section, emerging and future high throughput multi-mode and multi-standard architectures would have to deal with configuration latencies lower that 10  $\mu s$ . That is why, in order to face this challenge, this thesis work aims to bring contributions providing an efficient and high speed dynamic configuration of a multi-mode and multi-standard Turbo decoder.

# **1.3** State of the art in flexible Turbo decoding architectures

Since the invention of Turbo codes in 1993 [3], a considerable amount of contributions targeting the VLSI implementation of Turbo decoders have been proposed. These implementations target diverse design objectives in terms of area efficiency, energy efficiency, scalability, flexibility and high throughput. Among the initial efforts in this context, the work described in [19] has investigated sub-block parallelism in order to increase the throughput. In [13], the authors have explored different computational schemes for the MAP algorithm. Quantization optimizations for input and extrinsic information have been studied in [20]. Algorithmic and architecture joint optimizations have been explored and proposed in [21]. [22] presents one of the first ASIC implementation achieving a throughput of 50 Mbps with 10 decoding iterations and an operating frequency of 1 GHz.

Turbo codes have been widely adopted in wireless communication standards like CDMA2000, UMTS, LTE, WiMAX, DVB-RCS, etc. Several architecture approaches have been investigated in order to build high throughput and flexible Turbo decoders. Many implementations have succeeded to meet the low throughput requirements of the early standards (e.g. CDMA2000 and UMTS) using advanced DSP architectures [23, 24, 25], customizable processors [26]. However, the scalability of such implementations is limited by the block interleavers specified in these standards which cause memory access contentions when targeting higher sub-block parallelism degree. In [27], the authors present an implementation of a turbo decoder in the Coarse-Grained Montium Architecture. The implementation offers a low reconfiguration latency of  $6.36 \ \mu s$  but the architecture reaching 100 MHz supports the low UMTS throughput requirement (1.92 Mbps) only. FPGA implementations have been investigated but this technology suffers from a prohibitive reconfiguration latency. In [28], results show that the reconfiguration process of the FPGA is 35 ms.

The introduction of contention-free interleavers, like ARP in WiMAX and QPP in LTE, alleviated this limitation enabling high throughput implementations [29, 30, 31, 32, 33, 34]. The work presented in [29] targeting LTE, allows multiple SISO decoders (1, 2, 4, or 8) to concurrently process frame subblocks and integrates a three stage network to connect the multiple memory and SISO decoder modules. Implemented in 90nm CMOS technology, the design achieves a throughput of 129 Mbps with 8 iterations and occupies an area of 2.1 mm2 while exhibiting a power consumption of 219 mW and supporting the maximum specified frame size of 6144 bits. Another example of flexible architecture is the parameterized architecture of [30] which supports both Turbo modes (DBTC and SBTC) and achieves a high throughput of 187 Mbps with 8 parallel MAP decoders. Targeting Gbps throughputs, a recent work [35] has proposed an LTE-Advanced compliant Turbo decoder architecture with 32 parallel SISO decoders using Radix-4 trellis compression and butterfly schedule of forward backward calculations. A throughput of 2.15 Gbps is achieved with an on chip area of 7.1 mm2 using 65nm CMOS technology. The architectures previously presented propose to use multiple SISO decoders to reach high throughput of emerging and future standards. However, even if these turbo decoders offer certain degrees of flexibility to adapt for instance the number of SISO decoders, the turbo code mode (i.e. SBTC or DBTC), or the frame size, the authors do not present any configuration infrastructures associated to their architecture in order to support dynamic configuration switches.

In order to support dynamic configuration, the authors of [36] present an FPGA implementation of a High Speed MAP Decoder Architecture for Turbo Decoding achieving 346 Mbps. However, the configuration latency cost of such an implementation is not evaluated. The recent FPGA dynamic reconfiguration mechanisms provide very high flexibility. The configuration latency of Xilinx FPGA [37] depends on the targeted FPGA technology, the bitstream size and the medium (ICAP, JTAG, etc.) used to transfer the configuration bitstream. However, the configuration latency overhead is still important (from around 100  $\mu s$  to 100 ms). Recent works investigated General Purpose Processor (GPP) implementations using high performance multi-cores architectures taking advantage of the Intel SSE (Streaming SIMD Extensions) instructions. In [38], a 418 Mbps turbo decoder for LTE is implemented on an Intel Xeon processor X5670 with a 12 threads level of parallelism. The 150 Mbps LTE throughput requirement is reached with a 4 threads implementation. In [39], an adaptive turbo decoder implementation on an Intel I7-960 core is investigated. The authors propose to adapt the decoding algorithm depending on the communication channel quality. However, for both [39] and [38] works, no discussion is provided about the context switching cost when the turbo decoder configuration has to be changed. Moreover, these GPP implementations have been initially developed for base station. Thus, they are not suitable for mobile terminals due to the high power consumption of such processors.

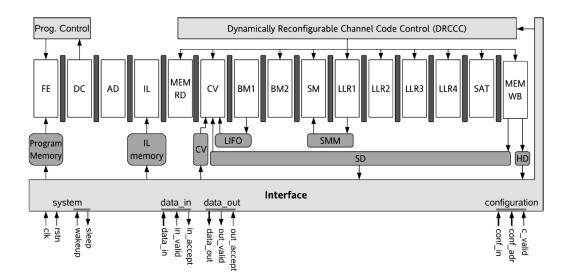

Recently, Application Specific Instruction-set Processor (ASIP) designs solutions have been investigated in order to offer architectures providing good compromises in terms of flexibility, throughput and power dissipation. In [40] a flexible and high performance ASIP model for Turbo decoding was proposed which can be configured to support all simple and double binary Turbo codes up to eight states. The architecture uses shuffled decoding with frame sub-blocking. The extrinsic information is iteratively and concurrently exchanged between multiple component decoders via an on-chip communication network presented in [41]. Afterwards, optimizations on the proposed ASIP have been added in [42]. Moreover, LDPC decoding modes is proposed as well as new LDPC decoding schedule adapted to a multi-ASIP architecture. In [43], the authors introduce the FlexiTreP ASIP presented in [44] in a multi-ASIP architecture for turbo decoding consisting of two ASIPs and dedicated accelerator to reach the 150 Mbps throughput requirement of LTE. This ASIP, whose general architecture is illus-

Figure 1.14: FlexiTreP general architecture

trated in Figure 1.14, supports both SBTC and DBTC for various standards and it is configured through an interleaver memory (IL), a program memory and the Dynamically Reconfigurable Channel Code Control (DRCCC). The DRCCC is a look-up table based unit which allows the configuration of the structure of the convolutional code, the internal data-path, and the configuration memory. Two configurations are stored in this unit, a working and a shadow configuration. The working configuration holds the parameters that are actually used while the shadow configuration is used to prepare the next configuration. One cycle switching can be performed between these two configurations thanks to a special instruction. However, using a specific instruction in the program to switch between two configurations limits the flexibility because the reconfiguration scenario is defined statically. Moreover, even if the DRCCC allows to prepare the next configuration parameters in parallel of the current decoding process, the program and interleaver memories can not be modified during the processing. A configuration delay, which is not detailed in the presented works, between two consecutive frames is necessary to load these two memories for each ASIP implemented on a platform.

Previous works provide an efficient way to reach the high performance requirement of emerging standards. However, the dynamic reconfiguration aspect of these platforms is superficially addressed. All these platforms can be reconfigured through program and configuration memories of each core, but the configuration mechanisms are not optimized for an efficient implementation in a multi-core system. Furthermore, these platforms are not coupled with a configuration infrastructure that allows configuration broadcasting to the cores. As explained in

Figure 1.15: Memory reconfiguration process presented in [44]

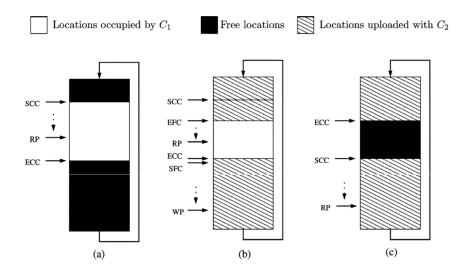

Section 1.2.2, the perpetual increase of throughput of wireless standards reduces the reconfiguration time available between two data frames while the number of cores increases to reach high throughput. This point is particularly challenging as in many standards decoding parameters can be changed as early as one data frame ahead [45]. Among the few works which considered this issue, we can cite the recent architecture presented in [46] where the authors propose solutions for the reconfiguration management of the NoC-based multiprocessor Turbo/LDPC decoder architecture presented in [47]. Up to 35 processing elements (PEs) and up to 8 configuration buses have been implemented. Each PE is configured through a configuration memory which is organized as a circular buffer. The set of pointers used to manage reading and writing operations are shown in Figure 1.15. The start of current configuration (SCC) pointer and the end of current configuration (ECC) pointer delimit the memory blocks that are currently being used. A read pointer (RP) is used to retrieve the data during the decoding process, as shown in Figure 1.15(a). The start of future configuration (SFC) and end of future configuration (EFC) pointers, shown in Figure 1.15(b) are instead used concurrently with the write pointer (WP) to delimit the locations that are going to be used to store the new configuration data. The reconfiguration process to switch from a configuration  $C_1$  to a configuration  $C_2$  can be masked by the current decoding task (Figure 1.15(c)) if the configuration memory provides enough free space and if a high speed configuration infrastructure is provided.

For that purpose, groups of four PEs are connected to a dedicated configuration bus. The remaining PEs are shared among the buses when the number of PEs is not divisible by four. Dynamic reconfiguration during one frame duration is possible when the current configuration is small enough to load a new configuration in the memory. If not, authors provide management solutions to deal with this issue, such as erasing the current configuration during the last decoding iteration and continue the reconfiguration process during the first iteration of the new configuration, but it is not always sufficient. Then, stopping the current processing to configure the new configuration is unavoidable and leads to a decoding quality loss in terms of BER. Moreover, the cost of the proposed multi-bus configuration infrastructure becomes too high with the increasing number of PEs and leads to a complex configuration transfer management.

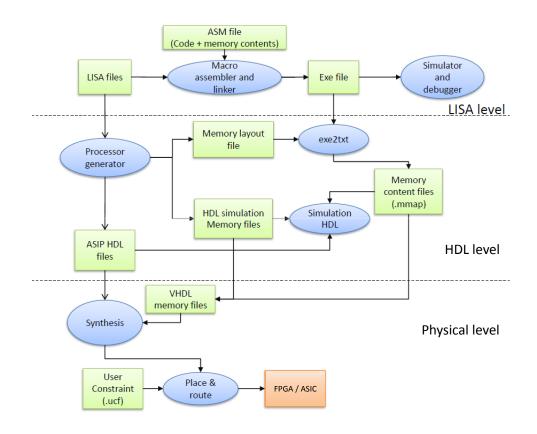

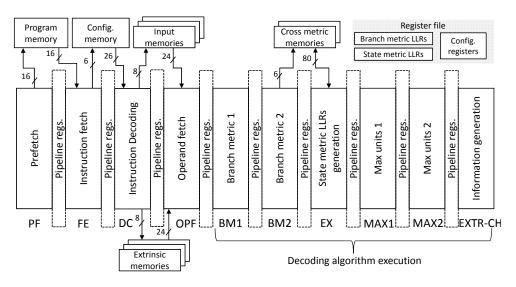

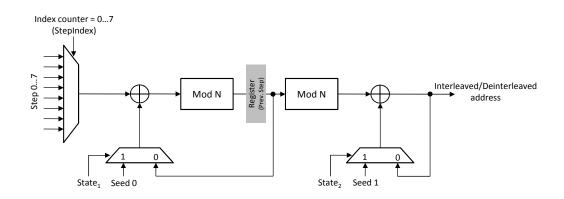

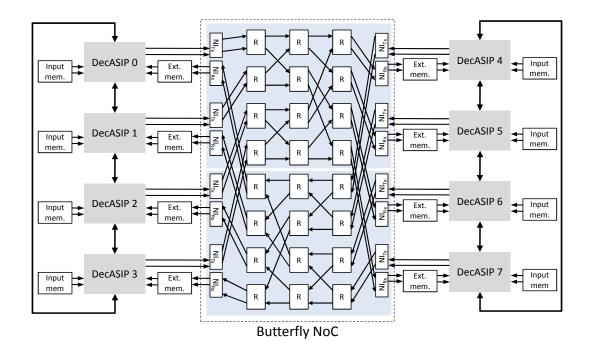

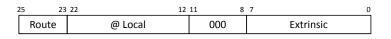

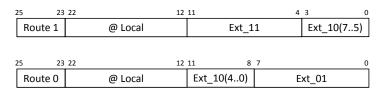

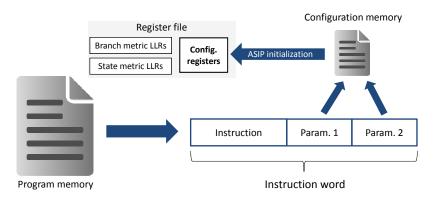

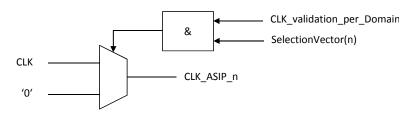

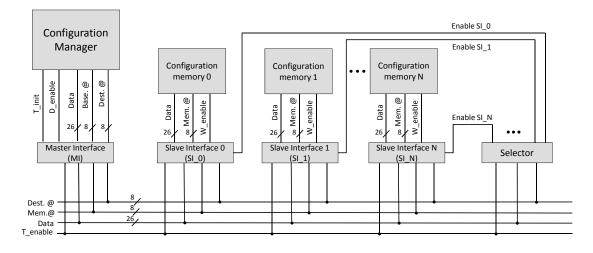

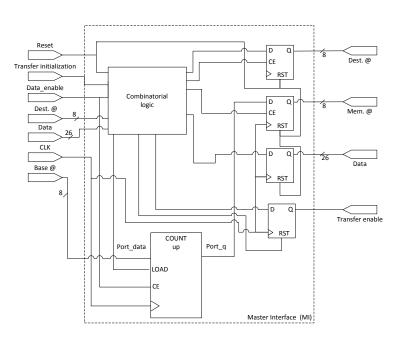

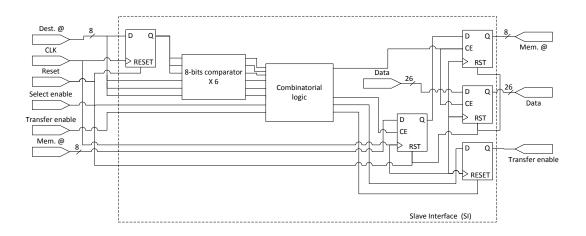

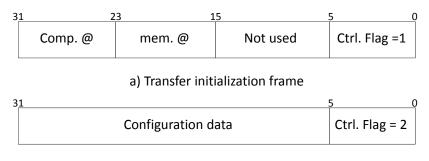

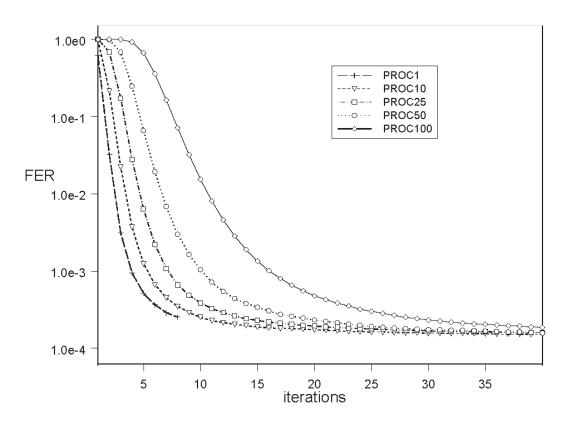

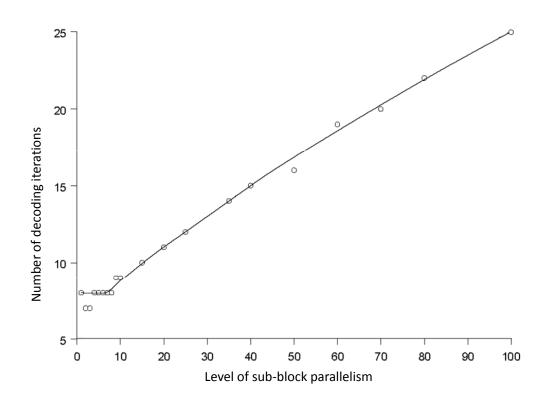

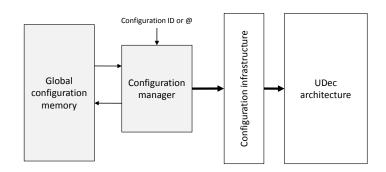

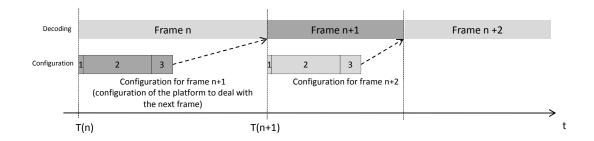

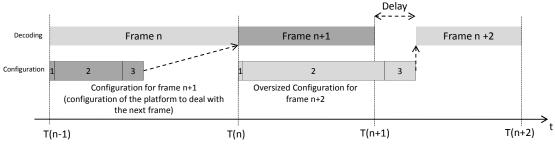

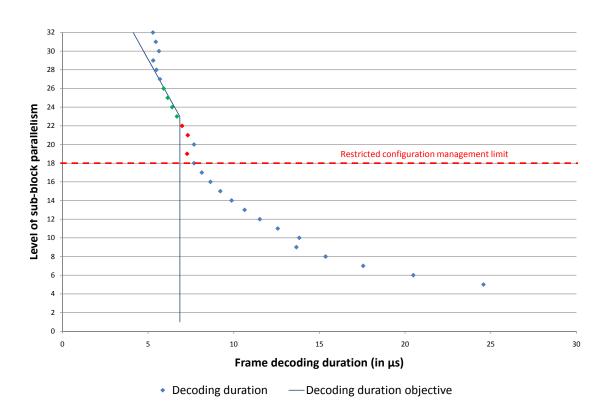

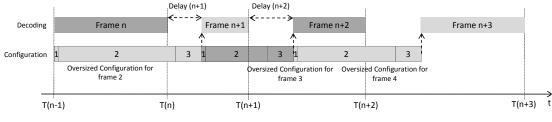

To leverage these issues, it becomes essential to propose original solutions for a low complexity and stopping-free configuration of multiprocessor Turbo decoders. Previous works targeting reconfigurable Turbo decoder architectures tackled one or two specific aspects of the reconfiguration process leading to inefficient global reconfiguration mechanisms. Indeed, as summarized in Table 1.2, [44, 43] proposes an efficient dynamically reconfigurable channel code control (DRCCC) unit allowing a one cycle reconfiguration of the processor's pipeline but the rest of the configuration information (program and interleaver configuration) is not optimized for a high speed configuration. In [46], the configuration memory of each processing element has been designed to support configuration overlapping but the configuration load is not optimized so a complex multi-bus configuration has to be implemented to support high speed configuration. In this context, this thesis work, starting from the works presented in [40, 41, 42], aims to further investigate and optimize the dynamic reconfiguration process in order to support stoppingfree dynamic reconfiguration for high throughput requirements and high level of parallelism in the context of multi-mode and multi-standard scenarios presented in Section 1.2.2. Configuration latency below 10  $\mu s$ , including run-time configuration generation which is not implemented in previous work, must be proposed to reach this objective for emerging and future communication standards.