# Métaheuristiques pour la synthèse de haut niveau

Kods Trabelsi

#### ▶ To cite this version:

Kods Trabelsi. Métaheuristiques pour la synthèse de haut niveau. Recherche opérationnelle [math.OC]. Université Européenne de Bretagne; Université de Bretagne-Sud, 2009. Français. NNT: . tel-01096399

#### HAL Id: tel-01096399 https://hal.science/tel-01096399

Submitted on 18 Dec 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THESE / UNIVERSITE DE BRETAGNE-SUD

sous le sceau de l'Université européenne de Bretagne

pour obtenir le titre de

DOCTEUR DE L'UNIVERSITE DE BRETAGNE-SUD

Mention: STIC

Ecole doctorale SICMA

présentée par

#### **Kods TRABELSI**

Laboratoire des sciences et technologies de l'information, de la communication et de la connaissance (Lab-STICC) CNRS UMR 6285

# Métaheuristiques pour la synthèse de haut niveau

#### Thèse soutenue le 1er décembre 2009

devant le jury composé de :

Mme Alix MUNIER KORDON

Professeur, Université Paris 6 / Rapporteur

M. Emmanuel CASSEAU

Professeur, ENSSAT, Université de Rennes 1 / Rapporteur

M. Kenneth SÖRENSEN

Professeur, Université d'Anvers, Belgique / Président du jury

M. André ROSSI

Dr. Université de Bretagne-Sud / Examinateur

M. Marc SEVAUX

Professeur, Université de Bretagne-Sud / Directeur de thèse

M. Philippe COUSSY

Dr. Université de Bretagne-Sud / Directeur de thèse

# Table des matières

| Chapit | re 1    |                                            |      |

|--------|---------|--------------------------------------------|------|

| Conte  | xte     |                                            |      |

| 1.1    | Introd  | luction                                    | . 2  |

| 1.2    |         | eption des circuits intégrés               |      |

|        | 1.2.1   | Évolution des besoins et des applications  |      |

|        | 1.2.2   | Évolution technologique et architecturale  |      |

|        | 1.2.3   | Évolution des méthodologies de conception  |      |

| 1.3    |         | cherche opérationnelle                     |      |

| 1.3    |         |                                            |      |

|        | 1.3.1   | Les méthodes exactes                       |      |

|        | 1.3.2   | Les méthodes approchées                    | . 12 |

| 1.4    | Conte   | exte de ces travaux                        | . 12 |

|        | 1.4.1   | Le challenge de la réduction de la surface | . 13 |

|        | 1.4.2   | Plan de la thèse                           | . 13 |

| Chapit | re 2    |                                            |      |

| Etat d | e l'Art | t                                          |      |

| 2.1    | La syı  | nthèse de haut niveau                      | . 16 |

|        | 2.1.1   | L'élévation du niveau d'abstraction        | . 16 |

|        | 2.1.2   | Le flot de synthèse                        | . 17 |

|        | 2.1.3   | Les modèles formels                        |      |

|        | 2.1.4   | Complexité de la synthèse de haut niveau   |      |

| 2.2    |         |                                            |      |

| 2.2    | 2.2.1   | Les méthodes exactes pour la HLS           |      |

|        |         | •                                          |      |

|        | 2.2.2   | Les méthodes approchées pour la HLS        |      |

| 2.3    | Insuffi | isances actuelles et proposition           | . 41 |

| Chapitre 3                                                     |                                                      |  |  |  |

|----------------------------------------------------------------|------------------------------------------------------|--|--|--|

| Estimation et recherche locale pour la synthèse de haut niveau |                                                      |  |  |  |

| 3.1                                                            | Introduction                                         |  |  |  |

| 3.2                                                            | Représentation d'une architecture                    |  |  |  |

|                                                                | 3.2.1 Un estimateur de surface d'architecture        |  |  |  |

|                                                                | 3.2.2 Validation de l'estimateur                     |  |  |  |

| 3.3                                                            | Méthode de descente                                  |  |  |  |

|                                                                | 3.3.1 Présentation de la méthode                     |  |  |  |

|                                                                | 3.3.2 Application de la méthode de descente à la HLS |  |  |  |

| 3.4                                                            | Résultats                                            |  |  |  |

|                                                                | 3.4.1 Applications et technologie cible              |  |  |  |

|                                                                | 3.4.2 Résultats et interprétations                   |  |  |  |

|                                                                | 3.4.3 Conclusion                                     |  |  |  |

| Chapit                                                         | re 4                                                 |  |  |  |

|                                                                | thmes avancés pour la synthèse de haut niveau        |  |  |  |

| 4.1                                                            | Introduction                                         |  |  |  |

| 4.2                                                            | La descente Multi-start                              |  |  |  |

|                                                                | 4.2.1 Description de la méthode                      |  |  |  |

|                                                                | 4.2.2 Implémentation                                 |  |  |  |

|                                                                | 4.2.3 Résultats                                      |  |  |  |

| 4.3                                                            |                                                      |  |  |  |

|                                                                | 4.3.1 Description de la méthode                      |  |  |  |

|                                                                | 4.3.2 Implémentation                                 |  |  |  |

|                                                                | 4.3.3 Résultats                                      |  |  |  |

| 4.4                                                            | Le GRASP                                             |  |  |  |

|                                                                | 4.4.1 Description de la méthode                      |  |  |  |

|                                                                | 4.4.2 Implémentation                                 |  |  |  |

|                                                                | 4.4.3 Résultats                                      |  |  |  |

| 4.5                                                            | Bilan                                                |  |  |  |

| Chapit                                                         | Chapitre 5                                           |  |  |  |

| Conclu                                                         | sions et Perspectives                                |  |  |  |

|                                                                |                                                      |  |  |  |

93

Bibliographie

# Table des figures

| 1.1  | Complexité algorithmique $vs$ . performance des processeurs                      |

|------|----------------------------------------------------------------------------------|

| 1.2  | Différentes solutions architecturales                                            |

| 1.3  | Schéma d'un système mono-puce                                                    |

| 1.4  | Performance vs. Fléxibilité                                                      |

| 1.5  | Cycle de développement d'un circuit intégré                                      |

| 1.6  | Productivité vs. Capacité d'intégration                                          |

| 1.7  | Le flot de la conception matérielle logicielle                                   |

| 2.1  | Exploration de l'espace des solutions aux différents niveaux d'abstraction 1     |

| 2.2  | Flot de synthèse de haut niveau                                                  |

| 2.3  | Graphe Flot de Données                                                           |

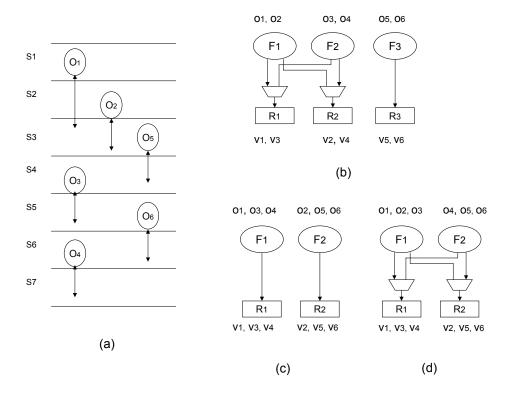

| 2.4  | Exemple                                                                          |

| 2.5  | Deux solutions d'un même problème                                                |

| 2.6  | (a) DFG (b) Expression des contraintes                                           |

| 2.7  | Arbre de recherche et séparation                                                 |

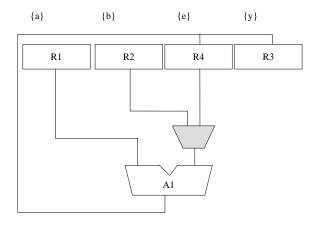

| 2.8  | Données d'entrée à l'assignation des registres                                   |

| 2.9  | Assignation des registres en utilisant le LEA                                    |

| 2.10 | Assignation des registres en utilisant le MLEA                                   |

| 2.11 | Application de l'algorithme de l'assignation simultanée                          |

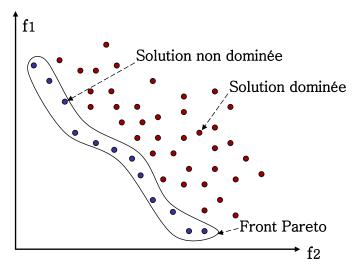

| 2.12 | Identification des solutions optimales au sens de Pareto optimal en cas de mini- |

|      | misation                                                                         |

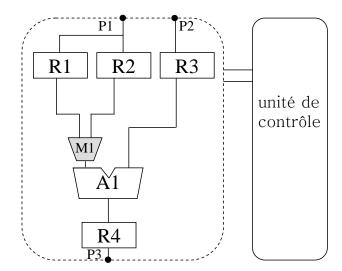

| 3.1  | Exemple d'un circuit                                                             |

| 3.2  | Exemple d'un circuit                                                             |

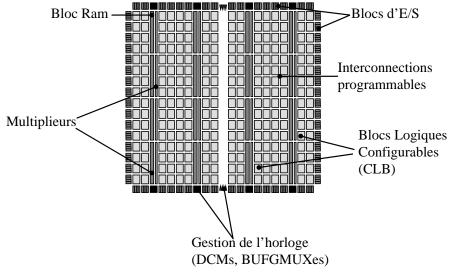

| 3.3  | FPGA 4                                                                           |

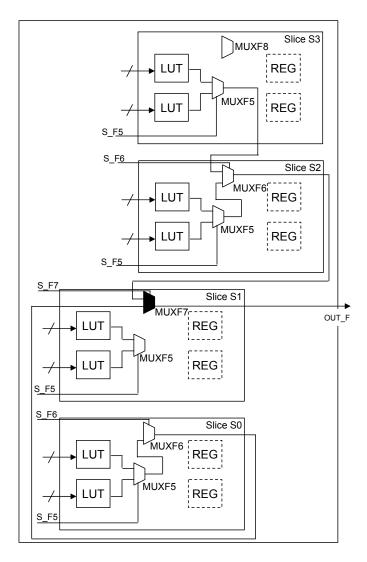

| 3.4  | Un CLB                                                                           |

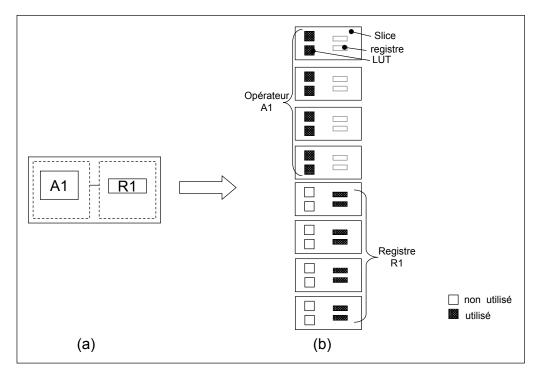

| 3.5  | Implémentation avec l'option hiérarchique                                        |

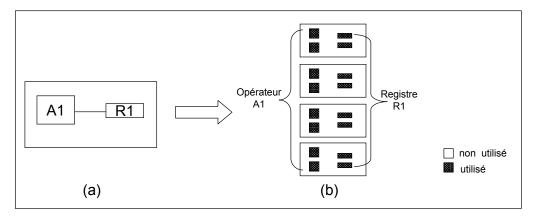

| 3.6  | Implémentation avec l'option à plat                                              |

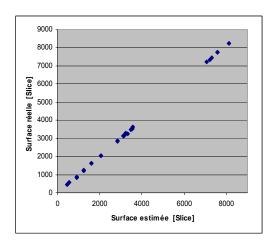

| 3.7  | Validation du modèle d'estimation en slice / hiérarchique                        |

| 3.8  | Validation du modèle d'estimation en $LUT/$ à plat $\ldots \ldots \ldots \ldots \ldots$ | 53 |

|------|-----------------------------------------------------------------------------------------|----|

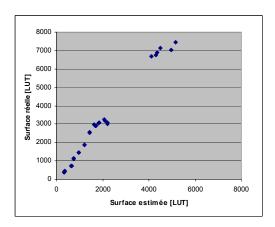

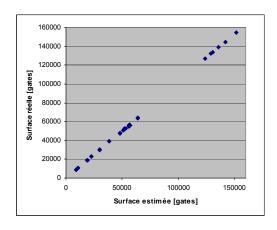

| 3.9  | Validation du modèle d'estimation en $gate/$ à plat                                     | 53 |

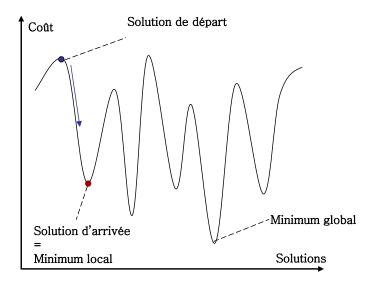

| 3.10 | Illustration de la méthode de descente                                                  | 54 |

| 3.11 | Exemple                                                                                 | 55 |

| 3.12 | Bibliothèque                                                                            | 56 |

| 3.13 | Le DFG de la figure 3.11 ordonnancé                                                     | 58 |

| 3.14 | Graphes de compatibilité déduis de l'ordonnancement de la figure $3.13$                 | 58 |

| 3.15 | Assignation des opérations de l'exemple de la figure 3.11                               | 59 |

| 3.16 | Solution de départ                                                                      | 60 |

| 3.17 | Architecture obtenue après la déplacement de la variable $e$ vers $R_2$                 | 61 |

| 3.18 | Architecture obtenue après la permutation des assignations des opérations $A_1$ et      |    |

|      | $A_2$                                                                                   | 61 |

| 3.19 | Architecture obtenue après l'ajout d'un additionneur et le déplacement de l'opé-        |    |

|      | ration +4 vers cet opérateur                                                            | 62 |

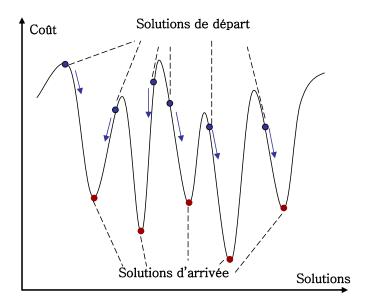

| 4.1  | Exploration de l'espace des solutions en utilisant la descente <i>Multi-start</i>       | 71 |

|      | •                                                                                       | -  |

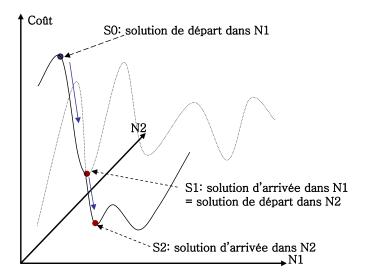

| 4.2  | Exploration de l'espace de solution en utilisant le VNS                                 | 75 |

# Liste des tableaux

| 1.1 | Evolution du nombre de concepteurs                                                     | 9  |

|-----|----------------------------------------------------------------------------------------|----|

| 2.1 | Notations                                                                              | 26 |

| 2.2 | Caractérisation d'un additionneur, un multiplieur et des MUX                           | 42 |

| 3.1 | Évaluation d'une solution                                                              | 46 |

| 3.2 | Compatibilité (unité de caractérisation/option d'implémentation)                       | 51 |

| 3.3 | Résultats de l'algorithme de descente simple et de l'algorithme de plus grande         |    |

|     | descente pour le voisinage de réassignation des registres                              | 65 |

| 3.4 | Gains en surface obtenues avec l'algorithme de descente simple et l'algorithme         |    |

|     | de plus grande descente pour le voisinage de réassignation des registres               | 66 |

| 4.1 | Application de la descente <i>Multi-start</i> à la synthèse de haut niveau             | 73 |

| 4.2 | Gains réalisés par la descente $\textit{Multi-start}$ par rapport à la simple descente | 74 |

| 4.3 | Différentes combinaisons d'ordre d'exploration des trois voisinages                    | 77 |

| 4.4 | Influence de l'ordre de l'exploration des voisinages sur la surface                    | 79 |

| 4.5 | Application du VNS à la synthèse de haut niveau                                        | 81 |

| 4.6 | Comparaison entre les résultats de la simple descente et de la recherche à voisi-      |    |

|     | nage variable                                                                          | 81 |

| 4.7 | Résultats du GRASP100                                                                  | 84 |

|     |                                                                                        |    |

| 4.8 | Résultats du GRASP10                                                                   | 85 |

## Chapitre 1

### Contexte

#### Sommaire

| 1.1 Intr | oduction                                   |

|----------|--------------------------------------------|

| 1.2 Con  | ception des circuits intégrés              |

| 1.2.1    | Évolution des besoins et des applications  |

| 1.2.2    | Évolution technologique et architecturale  |

| 1.2.3    | Évolution des méthodologies de conception  |

| 1.3 La 1 | recherche opérationnelle                   |

| 1.3.1    | Les méthodes exactes                       |

| 1.3.2    | Les méthodes approchées                    |

| 1.4 Con  | texte de ces travaux                       |

| 1.4.1    | Le challenge de la réduction de la surface |

| 1.4.2    | Plan de la thèse                           |

Dans ce premier chapitre, nous introduisons les deux domaines à la croisée desquels se situent ces travaux de thèse. D'un coté, nous présentons le contexte de la conception des circuits électroniques avec l'évolution des applications implémentées, l'évolution des technologies de gravure et les solutions dédiées pour accompagner ces évolutions. De l'autre nous adressons le domaine de l'optimisation combinatoire et ce qu'elle peut offrir aux problèmes de grande complexité. Enfin, dans la dernière section de ce chapitre, nous situons les travaux de cette thèse.

#### 1.1 Introduction

Ces travaux de thèse se situent à la croisée de deux domaines, la conception des circuits électroniques et l'aide à la décision. Dans ce chapitre nous allons préciser les contextes des deux domaines, chacun de son coté pour pouvoir situer nos travaux de recherche. Une première section présentera donc l'évolution des applications implémentés sur les circuits numériques, l'évolution technologique et une énumération non exhaustive des nouvelles méthodologies de conception. Une deuxième section s'intéressera au domaine de l'aide à la décision appelé aussi recherche opérationnelle, en introduisant les deux grandes familles de méthodes qu'offre l'aide à la décision pour résoudre les problèmes d'optimisation combinatoire. Enfin, la dernière section définira l'objectif de ces travaux.

#### 1.2 Conception des circuits intégrés

#### 1.2.1 Évolution des besoins et des applications

Grâce à l'évolution du marché de la technologie numérique, de la téléphonie mobile et du multimédia, les industriels proposent aujourd'hui dans un même produit toujours plus compact et plus autonome, de plus en plus de fonctionnalités. Les produits doivent être conçus et fabriqués dans des délais de plus en plus court, afin d'imposer les biens et de résister à la compétitivité. L'écho de la commercialisation des derniers smart phones, téléphones mobiles couplés à des PDA témoigne de la rude concurrence dans ce domaine.

Plus de fonctionnalités dans un produit plus compact et plus autonome se traduit concrètement par des applications hétérogènes et très complexes implémentées dans des circuits intégrés de tailles réduites et basse consommation. En effet, le concepteur doit gérer, d'un coté la complexité des applications qui ne cesse d'augmenter, mais aussi l'hétérogénéité des diverses applications à implémenter dans un même circuit. Par exemple, dans les nouveaux téléphones portables, un même circuit doit pouvoir gérer plusieurs protocoles de communication (Wifi, Edge, WCDMA, 3G), plusieurs normes d'encodage/décodage audio et vidéo (MPEG, H264, JPEG2000, OGG, MP4, AAC, etc).

Ainsi la conception des circuits intégrés doit prendre en compte :

- 1) l'accroissement continu de la complexité des applications,

- 2) l'hétérogénéité des applications,

- 3) la question de l'implémentation matérielle ou logicielle des applications,

- 4) la taille et la consommation du circuit,

- 5) et l'accès rapide au marché.

De ce fait, les technologies des semi-conducteurs ainsi que les méthodologies de conception sont amenées à évoluer.

#### 1.2.2 Évolution technologique et architecturale

Parallèlement à la demande accrue en puissance, en miniaturisation et en autonomie, les innovations technologiques en matière de semi-conducteurs n'ont cessé de proposer des solutions à ces exigences. L'évolution technologique repose sur deux aspects : la diminution conséquente des dimensions des structures en silicium réalisables sur un circuit intégré et l'offre de diverses solutions d'implémentation qui s'adaptent aux caractéristiques de la classe d'applications considérée.

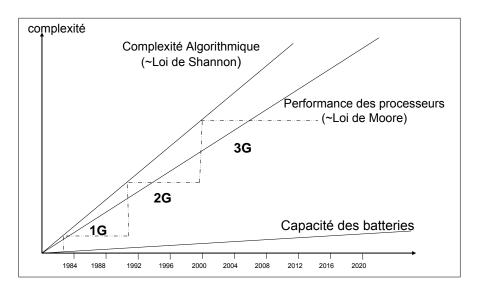

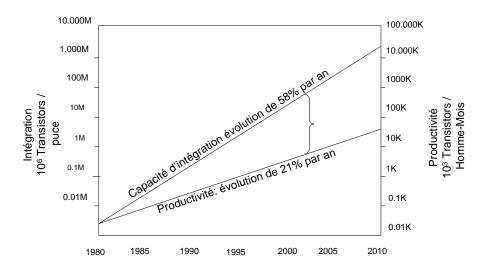

FIGURE 1.1 – Complexité algorithmique vs. performance des processeurs

#### 1.2.2.1 La finesse de gravure

L'échelle d'intégration, appelée aussi finesse de gravure qui trduit le nombre de portes logiques par  $mm^2$ , est passée de douze pour la première génération de circuits intégrés (1960) à plusieurs dizaines de millions de portes pour la dernière génération. En effet, le nombre de transistors sur une puce a régulièrement doublé tous les dix-huit mois, depuis l'invention du premier circuit intégré. Cette évolution a été prédite par la loi de Moore (Figure 1.1), une règle empirique publiée par Electronics Magazine en 1965 [Moore 1998], qui ne s'était jamais démentie. Cette avancée technologique a déclenché l'invention d'une panoplie de solutions architecturales.

#### 1.2.2.2 Taxonomie des circuits

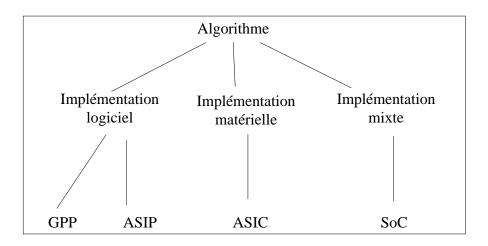

Plusieurs solutions architecturales ont été proposées pour l'implémentation d'une application donnée (Figure 1.2), les deux extrêmes : une solution purement logicielle qui s'exécute sur un microprocesseur et une solution purement matérielle qui se traduit par un circuit dédié à l'exécution de l'application.

L'objectif de cette section est de présenter brièvement les différentes solutions architecturales qui ont été proposées jusque là.

FIGURE 1.2 – Différentes solutions architecturales

L'implémentation logicielle Le microprocesseur généraliste (GPP) offre une plateforme pour l'implémentation logicielle des applications. Les principales caractéristiques d'un microprocesseur sont :

- le nombre de bits que le processeur utilise pour représenter une variable. Les microprocesseurs actuels peuvent traiter des nombres codés sur 64 bits ou plus.

- la vitesse de l'horloge : le rôle de l'horloge est de cadencer le rythme du travail du microprocesseur.

- $-\,$ le jeu d'instructions qu'il peut exécuter : additionner, comparer, multiplier deux nombres, etc

La combinaison des caractéristiques précédentes détermine la puissance de calcul du microprocesseur.

La figure 1.1 montre l'évolution de la performance des processeurs en suivant la loi de Moore et celle de la complexité algorithmique dans le domaine des télécommunications en suivant la loi de Shannon [Rabaey 2000]. La superposition des courbes révèle la croissance plus rapide de la complexité des algorithmes par rapport à la croissance de la performance des processeurs. Ainsi, la solution purement logicielle n'est pas toujours appropriée.

L'implémentation matérielle Un ASIC est un circuit intégré spécialisé. En général, il regroupe un grand nombre de fonctionnalités uniques et/ou sur mesure. L'intérêt des ASICs est de réduire le coût en silicium et d'augmenter la fiabilité du circuit. Cependant, cette

solution architecturale a un inconvénient majeur qui est le coût de développement élevé voire très élevé, dû au coût de la fabrication des masques de gravure.

Dans cette approche, le coût élevé est dû à l'intervention du fondeur dans la phase de conception. En général, celui-ci ne souhaite pas intervenir dans la phase de conception; sa tâche étant de réaliser le composant à partir des masques. Ainsi pour réduire les surcoûts dus aux modifications, il s'avère nécessaire d'être rigoureux lors de la phase de développement de telle sorte que le circuit prototype fonctionne dès les premiers essais, ce qui n'est pas du tout trivial.

De ce fait, la production d'ASIC est généralement dédiée pour des gros volumes (>100 000 pièces par an), sauf lorsque le sur-mesure est indispensable. Dans ce cas, le fabricant rattrape le coût de son investissement avec un prix de vente plus élevé.

L'implémentation sur processeur généraliste et celle sur circuit dédié des applications ne sont pas toujours des solutions réalisables vu les limites calculatoires des processeurs et le coût très élevé des ASICs. Ainsi des solutions architecturales plus adaptées ont été proposées.

La solution de compromis Un ASIP [Henkel 2007, Stojcev 2005, Jain 2001] est un processeur conçu pour une classe d'applications particulière. Ainsi l'ASIP est un compromis entre le processeur généraliste et l'ASIC. En effet, des instructions inutiles peuvent être supprimées ou au contraire le jeu d'instructions peut être enrichi d'instructions spécifiques à l'application, par exemple, une opération (mac R1, R2, R3) qui multiplie et accumule (R1 += R2\*R3). Du fait de sa spécialisation, un ASIP peut ainsi exploiter les caractéristiques spécifiques d'un ensemble d'applications pour atteindre la performance, le coût architectural et la consommation de puissance requis.

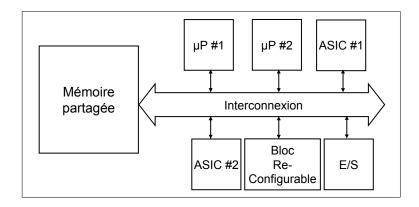

L'implémentation mixte Pour l'implémentation d'applications hétérogènes sur une même puce il y'a ce que l'on appelle les systèmes sur puce [D'silva 2005] ou encore systèmes mono-puce ou SoC (Figure 1.3). En effet, l'évolution phénoménale de la densité d'intégration a permis aussi la réalisation de systèmes complexes sur une seule puce. Un SoC désigne un système complet embarqué sur une puce, pouvant comprendre plusieurs blocs hétérogènes, entre autres, de la mémoire (data/code), un microprocesseur, des accélérateurs matériels, des périphériques d'interface, ou tout autre composant nécessaire à la réalisation de la fonction attendue. Un SoC pouvant contenir un ou plusieurs blocs reconfigurables s'appellera RSoC, s'il peut aussi contenir plusieurs microprocesseurs dans ce cas on l'appellera MPSoc.

FIGURE 1.3 – Schéma d'un système mono-puce

L'ASSP est un circuit électronique intégré regroupant un grand nombre de fonctionnalités pour satisfaire une application généralement standardisée : par exemple l'ASSP pour GSM (OMAP processeur mobile ARM fabriqué par Texas Instruments), issu d'un fabricant unique, est utilisé comme circuit de base par les différents fabricants de téléphones portables. Ainsi, les ASSPs sont généralement des SoCs.

Les circuits logiques reprogrammables Le est un circuit logique reprogrammable, est une plateforme pour l'implémentation matérielle, ou logicielle ou mixte. Cette solution architecturale est devenue la plateforme matérielle la plus courante pour l'implémentation des algorithmes à calcul intensif [Brown 1996]. Il est largement utilisé pour des applications (TDSI).

Les deux intérêts majeures des FPGAs sont la souplesse de programmation et le coût de conception réduit. En effet, les FPGAs sont composés de nombreuses cellules logiques élémentaires librement assemblables dont les fonctionnalités seront déterminées par les configurations qui leurs sont appliquées. Le coût réduit de la conception des FPGAs, permet de multiplier les essais et d'optimiser l'architecture développée. C'est effectivement, pour cette raison, la testabilité, que les FPGAs sont largement utilisés. Ainsi, bien qu'ils n'atteignent pas la performance des circuits dédiés, les FPGAs sont capables d'implémenter des algorithmes de calcul intensif tout en ayant un coût de conception raisonnable.

Bilan La figure 1.4 [Rabaey 2000] illustre le compromis performance/flexibilité de toute les solutions architecturales définies précédemment. Cette illustration simplifie le choix de la plateforme d'implémentation en fonction des besoins en performance et en flexibilité.

FIGURE 1.4 – Performance vs. Fléxibilité

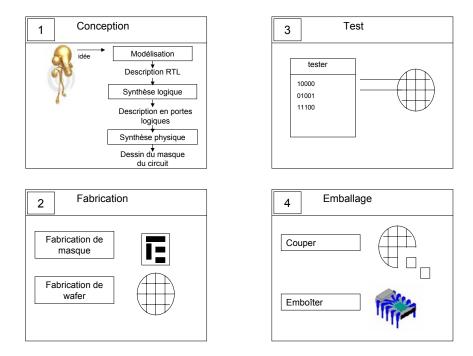

FIGURE 1.5 – Cycle de développement d'un circuit intégré

#### 1.2.3 Évolution des méthodologies de conception

Avec la maturité des technologies VLSI, l'industrie a commencé à s'intéresser au cycle de développement du produit (Figure 1.5) [Micheli 1994] afin de gagner en productivité et en compétitivité. En effet, le processus technologique autorise un accroissement de la complexité de 59% par an, alors que l'efficacité des concepteurs n'augmente que de 25% par an (Figure 1.6) [itr 2007]. Comme le montre le tableau, tiré de [Urard 2007], avec une technologie de 32 nm

et un taux de 200.000 portes par concepteur, il faut compter 300 HommeAn pour developper un circuit intégrant 60 millions de portes logiques. Ce besoin exponentiellement croissant en nombre de concepteurs coûte excessivement cher à l'industrie de la microélectronique. De ce fait, l'automatisation du processus de conception et de la spécification du silicium était devenu nécessaire pour rattraper l'écart imposé par l'évolution technologique.

FIGURE 1.6 – Productivité vs. Capacité d'intégration

La première tâche du concepteur consiste à trouver un modèle qui va représenter fidèlement le comportement de l'application. Cette représentation se fait à l'aide d'un langage de description matériel HDL tel que SystemC, Verylog et VHDL ou d'un langage de programmation simple tel que C.

L'étape suivante est le passage du niveau algorithmique au niveau transfert de registres RTL. La description RTL profile le circuit en composants (opérateurs, registres et multiplexeurs) interconnectés. On trouve, par la suite, l'étape de synthèse logique qui consiste à raffiner le modèle RTL en une représentation plus détaillée en portes logiques. Cette phase est assez longue, et peut durer des heures en fonction de la complexité des applications. Enfin, la phase de synthèse physique traduira à son tour le modèle logique en un modèle plus raffiné à base de transistors afin d'obtenir le dessin du masque du circuit.

Les outils commerciaux d'aide à la conception de circuits ont essayé de suivre l'évolution technologique en gagnant, tout les dix ans à peu prés, un niveau d'abstraction supplémentaire. Ainsi ont été commercialisé successivement, des outils de dessin de masques, puis des outils de synthèse logique (niveau portes) et enfin, à l'heure actuelle, des outils de synthèse travaillant sur le passage du niveau algorithmique au niveau transfert de registres.

1998 1994 1996 2000 2002 2004 2006 2008 2010 Finesse de gravure(nm) 0,18 0,13 # de portes / mm 1k 45k 80k 150k # de portes / die(50mm<sup>2</sup>) 50k 250k 2.25M 4M 30M # de portes / concepteur / an 4k 6k 56k 91k 125k 200k 200k Homme.Année / die(50mm<sup>2</sup>)

Table 1.1 – Évolution du nombre de concepteurs

#### 1.2.3.1 La synthèse de haut niveau

Les outils de synthèse de haut niveau automatisent la transformation d'une description algorithmique en Langage C par exemple, en une description RTL structurelle [Gajski 1992]. Jusque là, cette étape se faisait à la main. Cependant, récemment les industriels commencent à faire confiance aux outils de synthèse de haut niveau. Cette automatisation permettra la réduction du cycle de conception, l'exploration d'un espace de solutions plus large et enfin pour des circuits de grande complexité de surpasser les concepteurs humains. Plus de détails sur la synthèse de haut niveau seront donnés dans le chapitre II.

#### 1.2.3.2 La conception matérielle/logicielle

La conception matérielle logicielle appelée aussi conception conjointe ou encore Hw/Sw Co-Design est le développement conjoint de la partie matérielle et de la partie logicielle d'une application [Micheli 2001, Ernst 1998, Wolf 2003].

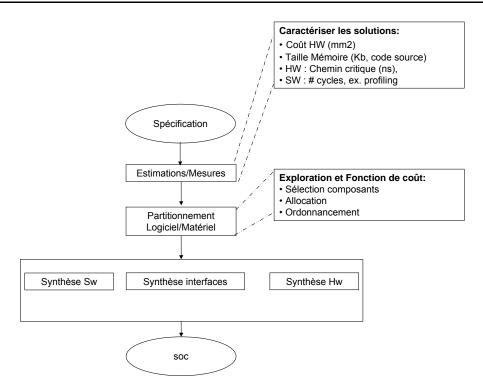

La figure 1.7 illustre le flot de la phase de conception conjointe. Comme le montre cette figure, les outils de Co-Design permettent une exploration rapide pour chacune des fonctions composants l'application considérée de plusieurs solutions architecturales (FPGA, ASIC, ASSP, etc.). En effet, ces outils partent d'une spécification d'une application composée de plusieurs fonctions, et s'appuient sur des métriques tels que le parallélisme moyen, le taux d'accès à la mémoire, les contraintes de communication, etc. pour choisir une solution architecturale pour chacune des fonctions de l'application. Pour finir, les outils de Co-Design synthétisent des interfaces de communication entre les architectures.

#### 1.2.3.3 Les composants virtuels

Les composants virtuels appelés aussi IP permettent la réutilisation des composants préconçus. Ce concept bien connu dans le domaine de la conception logiciel, s'applique depuis quelques

FIGURE 1.7 – Le flot de la conception matérielle logicielle

années à la conception matérielle. Il s'agit de construire une bibliothèque qui contiendra des blocs susceptibles d'être réutilisés.

L'IP peut prendre plusieurs formes : algorithmique [Coussy 2003], logiciel, firm [Nekoogar 2003] ou encore matérielle. Ces formes ont des niveaux de réutilisabilité différents. En effet, moins l'IP contient de détails architecturaux plus il est flexible et a un niveau de réutilisation élevé. La conception d'IPs peut se faire manuellement ou en utilisant les outils de synthèse de haut niveau.

Un composant virtuel réalise, en général, une fonction non triviale, mais à usage suffisamment générique pour être réinvesti dans un grand nombre d'applications. L'IP doit pouvoir être aisément réplicable à l'aide des outils d'intégration du commerce, en d'autres termes, il doit pouvoir être intégré à un système sans la présence de son concepteur et surtout avoir un coût de réutilisation nettement inférieur à celui de sa re-conception.

#### 1.3 La recherche opérationnelle

La recherche opérationnelle (RO), aussi appelée aide à la décision, propose des modèles conceptuels pour analyser des situations complexes et permet aux décideurs de faire les choix les plus efficaces. Ces situations dites complexes peuvent être formulées en problèmes d'optimisation combinatoire. Un problème d'optimisation combinatoire est défini par un ensemble

d'instances. A chaque instance du problème est associé un ensemble discret de solutions incluant un sous-ensemble représentant les solutions admissibles (réalisables) et une fonction de coût qui associe à chaque solution réalisable, un nombre réel évaluatif.

Résoudre un tel problème consiste à trouver une solution optimisant la valeur de la fonction de coût. Une telle solution s'appelle une solution optimale ou un optimum global. Plusieurs méthodes de résolution des problèmes d'optimisation combinatoire existent. Ces méthodes de résolution suivent quatre approches différentes pour la recherche d'une solution : l'approche de construction, l'approche de relaxation, l'approche de voisinage et l'approche d'évolution [Hao 1999].

- L'approche de construction consiste à construire pas à pas une solution. Partant d'une solution partielle initialement vide, elle cherche à étendre à chaque étape la solution partielle de l'étape précédente.

- L'approche de relaxation repose sur l'affranchissement de quelques contraintes et la résolution du problème relaxé.

- L'approche de voisinage, appelée aussi recherche locale ou la descente est un processus fondé sur deux éléments essentiels : un voisinage et une procédure exploitant le voisinage. Il s'agit de 1) débuter avec une configuration admissible quelconque, et 2) choisir un voisin tel que le coût du voisin soit inférieur à celui de la configuration de départ et considérer la nouvelle configuration comme solution de départ et répéter jusqu'à l'arrivée à la solution dont le coût est un inférieur à celui de tout ses voisins.

- L'approche d'évolution est basé sur un des principes du processus d'évolution naturelle.

Les méthodes évolutives doivent leur nom à l'analogie avec les mécanismes d'évolution des espèces vivantes. Un algorithme évolutif typique est composé de trois éléments essentiels :

1) une population constituée de plusieurs individus représentant des solutions potentielles du problème donné;

2) un mécanisme d'évaluation de l'adaptation de chaque individu de la population à l'égard de son environnement extérieur;

3) un mécanisme d'évolution composé d'opérateurs permettant d'éliminer certains individus et de produire de nouveaux individus à partir des individus sélectionnés.

Les méthodes de résolution quelque soit l'approche qu'elles suivent font partie de deux groupes de nature différente : les méthodes exactes et les méthodes approchées.

#### 1.3.1 Les méthodes exactes

Les méthodes exactes ou complètes garantissent la complétude de la résolution. Ce sont des méthodes d'énumération implicite : toutes les solutions possibles du problème peuvent être énumérées. En revanche, l'approche effective du problème se confronte à deux difficultés. La première est qu'il n'existe pas forcément un algorithme simple pour énumérer les configurations possibles. La seconde est que le nombre de solutions réalisables est très grand, ce qui signifie que

le temps d'énumération de toutes les solutions est prohibitif. La complexité algorithmique est en général exponentielle. Pour diminuer le temps de recherche, différentes techniques existent pour calculer des bornes permettant d'élaguer le plus tôt possible des branches conduisant à un échec. Ainsi, les méthodes exactes permettent de résoudre des problèmes de manière optimale, mais souvent pour des instances de petite taille. En même temps, pour les problèmes NP-difficiles ces méthodes ne sont pas applicables. Les méthodes approchées appelées aussi heuristiques ont vu le jour pour palier à cette carence et proposer des méthodes qui effectuent un compromis entre le temps de résolution et la qualité de la solution.

#### 1.3.2 Les méthodes approchées

Les méthodes approchées tentent de trouver une solution de bonne qualité en un temps de calcul raisonnable sans garantir l'optimalité de la solution obtenu. Les méthodes approchées s'appuient sur un équilibre entre l'intensification de la recherche et la diversification de celleci. L'intensification permet de rechercher des solutions de plus grande qualité en s'appuyant sur les solutions déjà trouvées. La diversification met en place des stratégies qui permettent d'explorer un plus grand espace de solutions et d'échapper aux minima locaux. En préservant cet équilibre, les heuristiques évitent de converger trop vite vers des minima locaux (manque de diversification) oude faire une exploration trop longue (manque d'intensification).

#### 1.4 Contexte de ces travaux

Le processus de conception d'un circuit numérique devient de plus en plus complexe étant donnée l'évolution des applications d'une part et l'accroissement de l'écart entre la capacité d'intégration des circuits et la capacité de conception d'autre part. En même temps, les méthodes d'optimisation exactes et approchées se sont développées pour proposer des solutions de meilleures qualités aux problèmes combinatoires de grande complexité dans tous les domaines. Ainsi, les méthodes de recherche opérationnelle peuvent fournir des solutions aux problèmes combinatoires du flot de conception des circuits numériques.

Ces travaux de thèse se situent entre le domaine de l'optimisation combinatoire et le domaine de la conception des circuits intégrés. Nous nous sommes intéressés à l'implémentation des applications de traitement de signal et de l'image sur les FPGAs. La contrainte principale de cette famille d'applications étant temporelle (le débit), nous sous sommes concentrés dans un premier temps sur la minimisation de la surface occupée une fois l'application implémentée sur un FPGA.

#### 1.4.1 Le challenge de la réduction de la surface

La réduction de la surface occupée par une application donnée a toujours était parmi les principaux objectifs des concepteurs. Plusieurs approches ont été proposées pour la réduction de la surface.

Une application se traduit par un ensemble d'opérations (addition, soustraction, comparaison, etc.) [Gajski 1992]. La surface occupée lors de l'implémentation de celle-ci sur un FPGA est comparable au :

- nombre d'unités reconfigurables occupées par l'implémentation des opérateurs qui vont exécuter les opérations de l'application considérée

- en plus de celles utilisées pour les unités de stockage appelées aussi registres responsables de la sauvegarde des données sur les quelles les opérateurs vont opérer et enfin les unités nécessaires pour l'implémentation des unités responsables du cheminement des données en cas de réutilisation des opérateurs ou des registres.

Ces travaux de thèse s'inscrivent dans la phase d'exploration de l'espace de solutions, dans un flot de synthèse de haut niveau dédié aux applications de traitement du signal et de l'image sur FPGAs.

#### 1.4.2 Plan de la thèse

Ce manuscrit est composé de cinq chapitres. Le chapitre II présentera le processus de la synthèse de haut niveau et un état de l'art non exhaustif sur les méthodes d'optimisation et leurs applications aux différents sous problèmes de ce processus. Pour chacune des méthodes présentées nous en donnerons les points forts et les insuffisances. Une première approche de résolution du problème de la minimisation de la surface au cours de la synthèse de haut niveau avec les résultats et bilan seront présentées dans le chapitre III. Le chapitre IV présentera des algorithmes plus avancées ainsi que leurs résultats respectifs. Enfin, le dernier chapitre permettra de conclure cette étude et de proposer des perspectives de recherche.

# Chapitre 2

# Etat de l'Art

#### Sommaire

| 2.1 | La s  | ynthèse de haut niveau                                         | 16        |

|-----|-------|----------------------------------------------------------------|-----------|

|     | 2.1.1 | L'élévation du niveau d'abstraction                            | 16        |

|     | 2.1.2 | Le flot de synthèse                                            | 17        |

|     | 2.1.3 | Les modèles formels                                            | 19        |

|     | 2.1.4 | Complexité de la synthèse de haut niveau                       | 21        |

| 2.2 | Min   | imisation de la surface du circuit lors de la synthèse de haut |           |

|     | nive  | au                                                             | <b>23</b> |

|     | 2.2.1 | Les méthodes exactes pour la HLS                               | 24        |

|     | 2.2.2 | Les méthodes approchées pour la HLS                            | 32        |

| 2.3 | Insu  | ffisances actuelles et proposition                             | 41        |

La première partie de ce chapitre présentera les grandes étapes qui constituent un flot de synthèse de haut niveau. La deuxième partie, présentera un état de l'art des principales méthodes d'optimisation et de leurs applications au problème de la synthèse de haut niveau. La dernière section de ce chapitre souligne les insuffisances des approches existantes et définit les objectifs de nos travaux.

#### 2.1 La synthèse de haut niveau

#### 2.1.1 L'élévation du niveau d'abstraction

Les outils de synthèse logique ont permis de combler en partie le fossé entre la modélisation d'une architecture et la réalisation proprement dite du circuit VLSI, en utilisant des langages de description matériel. Ces outils automatiques de synthèse logique ont atteint, depuis déjà une dizaine d'années, un degré de maturité tel que leur utilisation dans le domaine de conception des circuits VLSI est devenue courante.

La spécification au niveau transfert de registres, proposée à l'entrée des outils de synthèse logique est aujourd'hui principalement écrite manuellement par les concepteurs. C'est une description structurelle de l'architecture constituée de composants combinatoires (opérateurs et multiplexeurs) et des composants séquentiels (registres, RAM, etc.). Cette description s'appuie sur un ensemble bien défini et standardisé de constructions syntaxiques. Cependant avec la croissance rapide de la complexité des algorithmes et des applications à implémenter, écrire une spécification au niveau RTL devient une tâche laborieuse. Elle rallonge la durée et augmente le coût de la phase de conception. De ce fait, le recours à une automatisation de cette étape s'impose. Cette automatisation requière une élévation du niveau d'abstraction pour la spécification des systèmes.

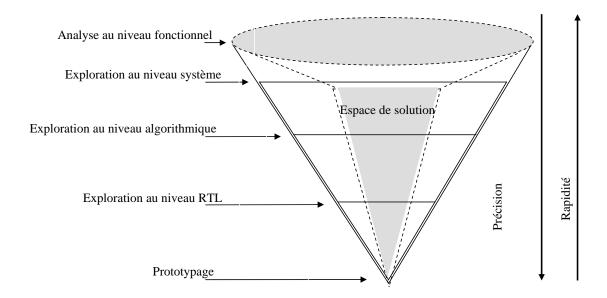

L'élévation du niveau d'abstraction de la spécification simplifie d'un coté la tâche du concepteur mais ouvre en plus la voie à un vaste champ de recherche visant à automatiser l'exploration architecturale (voir figure 2.1). Ainsi l'avènement des outils de synthèse de haut niveau HLS, appelée également synthèse architecturale ou aussi synthèse comportementale s'inscrit dans cette optique. La synthèse de haut niveau est un module complémentaire à ceux de la synthèse logique et de la synthèse physique dans une perspective d'automatisation du processus de raffinement d'un composant matériel.

Les outils commerciaux de synthèse de haut niveau sont passés par plusieurs phases depuis leur apparition en 1980. Les outils de HLS de la première et la deuxième génération souffraient d'un manque de maturité [Martin 2009]. Toutefois aujourd'hui, le besoin pressant en nouvelles techniques de synthèse permettant de passer plus rapidement et surtout à moindre coût du niveau système au silicium est en train de susciter l'intérêt des chercheurs pour le développement de ces outils et des concepteurs pour leur utilisation.

FIGURE 2.1 – Exploration de l'espace des solutions aux différents niveaux d'abstraction

#### 2.1.2 Le flot de synthèse

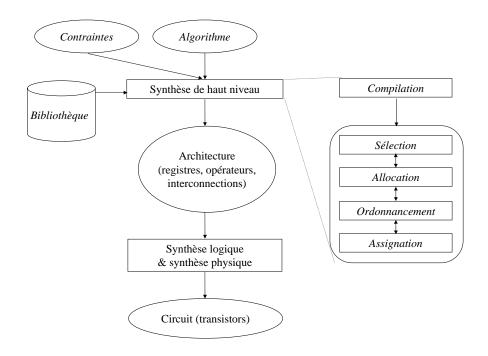

La synthèse de haut niveau peut être comparée à la compilation dans le domaine logiciel. Dans les deux processus, il s'agit de passer d'un modèle à un haut niveau d'abstraction à un modèle plus détaillé. Les modèles de départ se veulent d'une part intuitifs, lisibles et concis, et d'autre part aussi indépendants que possible des cibles chargées de l'exécution. Les outils de synthèse de haut niveau prennent en entrée une description algorithmique, les contraintes prédéterminées (débit, ressources, etc.), les objectifs attendus (minimisation de la surface, minimisation de la consommation, etc.) et génèrent automatiquement la description RTL du circuit. Le processus de la synthèse de haut niveau (Figure 2.2) passe par la compilation, la sélection, l'allocation, l'ordonnancement, l'assignation et la génération de la description RTL de l'architecture. L'ordre de ces étapes n'est pas figé et varie d'un outil à un autre selon les objectifs et les contraintes supportés par ce dernier. Chacune des étapes de la HLS a un rôle bien précis. Ainsi :

La compilation réalise la vérification syntaxique et sémantique de la description initiale pour la traduire ensuite en une représentation intermédiaire propre à l'environnement de synthèse. Cette phase se charge des optimisations telles que l'élimination du code mort, la propagation des constantes, la transformation des boucles [Bacon 1994], etc.

La représentation interne, résultat de la compilation peut prendre plusieurs formats. Deux

modèles sont généralement utilisés : Les graphes flot de données DFG [Gajski 1992] et les graphes flot de données et de contrôle CDFG [Orailoglu 1986]. Ces deux modèles seront

FIGURE 2.2 – Flot de synthèse de haut niveau

détaillés dans la section 2.1.3.

La sélection consiste à choisir pour chaque classe d'opération le type de l'opérateur qui se chargera de leur exécution parmi ceux présents dans la bibliothèque de composants matérielles. Ce choix se base sur l'évaluation de critères tels que la surface, la vitesse et la consommation de chaque composant de la bibliothèque [Bakshi 1996].

L'allocation fixe pour chaque type d'opérateur sélectionné le nombre d'instances à utiliser dans l'architecture finale [Gutberlet 1992]. Celle-ci peut se faire, par exemple, manuellement (par l'utilisateur) si l'application traitée est sous contraintes de ressources ou automatiquement si l'application est sous contraintes de temps.

L'ordonnancement affecte une date de début d'exécution aux opérations du graphe. L'ordonnancement doit respecter les contraintes imposées par le concepteur ainsi que les dépendances de données exprimées dans le graphe produit par l'étape de compilation. Les contraintes et les objectifs de cette étape varient selon les caractéristiques de la classe d'applications ciblées [Walker 1995, Micheli 1994, Rau 1994]. On distingue deux catégories d'ordonnancement : l'ordonnancement sous contraintes de ressources et l'ordonnancement sous contraintes de ressources et l'ordonnancement sous contraintes de remps. Dans la première catégorie, le nombre maximal

de ressources matérielles (opérateurs et/ou registres..) à utiliser dans le circuits est fixé à l'avance, et l'objectif consiste à minimiser la durée d'ordonnancement. Dans la deuxième catégorie, la durée totale de l'ordonnancement est fixé, et l'objectif est de minimiser le nombre de ressources matérielles.

L'assignation des opérations aux opérateurs associe une instance d'opérateur à chaque opération. Deux opérations, qui d'une part peuvent être exécutées par le même type d'opérateur et d'autre part ont des durées d'exécution qui ne se chevauchent pas, peuvent partager le même opérateur. L'assignation des opérations aux opérateurs peut se faire avant ou après l'ordonnancement.

L'assignation des variables aux registres associe un registre à chaque variable. Une variable intermédiaire (donnée) produite par une opération du graphe doit être stockée dans un registre tant que toutes les opérations utilisant cette donnée n'ont pas été exécutées. La durée de vie d'une variable est l'intervalle défini par la date de sa création et la date de sa dernière utilisation. Les variables qui ont des périodes de vie disjointes peuvent partager le même registre. L'un des principaux critères d'optimisation dans cette tâche est la minimisation du nombre de registres [Paulin 1989b] ainsi que les multiplexeurs [Cong 2008].

#### 2.1.3 Les modèles formels

Pour explorer efficacement l'espace des solutions architecturales, les étapes de la synthèse de haut niveau opèrent sur des modèles formels. Chaque modèle formel traduit une partie des informations permettant d'aboutir à une description structurelle de l'architecture.

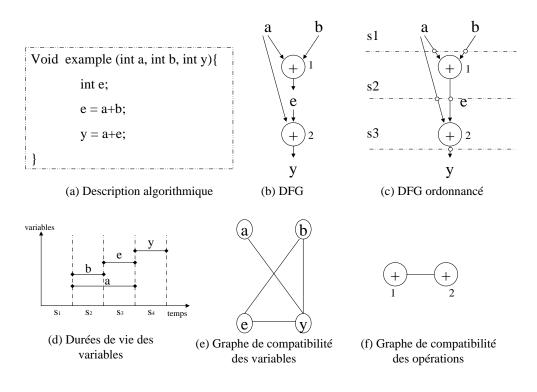

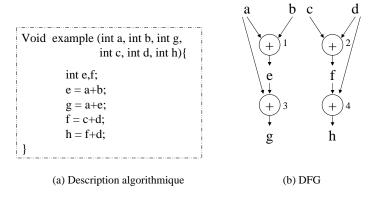

Ainsi la première étape de la synthèse de haut niveau consiste à traduire la spécification algorithmique (Figure 2.4-a) en une représentation interne, par exemple le DFG (Figure 2.4-b). Ce modèle formel est par la suite exploité par les étapes de sélection, d'allocation et d'ordonnancement afin de se rapprocher encore plus de la description structurelle de l'architecture. Le DFG permet de mettre en évidence, par analyse des dépendances, les opérations pouvant être exécutées en parallèle.

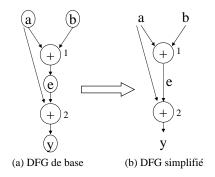

Ainsi un **Graphe Flot de Données** ou DFG,  $G(V_1, V_2, E)$  est un graphe bipartite orienté et acyclique avec  $V_1$  l'ensemble des noeuds représentant les opérations atomiques que le circuit doit réaliser,  $V_2$  l'ensemble des noeuds représentant les variables. E représente l'ensemble des arcs qui traduisent les dépendances de données entre opérations et variables. Généralement, les noeuds variables sont omis et remplacés par des étiquettes aux arcs qui dénotent les variables en entrées et en sortie des opérations (Figure 2.3).

FIGURE 2.3 – Graphe Flot de Données

Une fois la représentation fournie, les étapes d'allocation et d'ordonnancement définissent le nombre nécessaire d'opérateurs ainsi que les dates de début des opérations représentées par les noeuds du DFG.

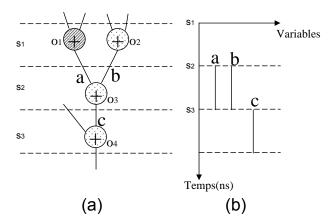

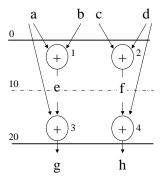

FIGURE 2.4 – Exemple

Dans l'exemple de la figure 2.4 nous allons supposer que l'étape de l'ordonnancement se fera avant l'assignation des opérations et des variables. L'opération d'addition 1 a été, ainsi, ordonnancée dans le cycle  $S_2$  et l'opération d'addition 2 a été ordonnancée dans le cycle  $S_3$ .

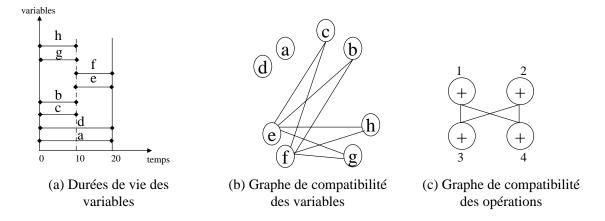

Un seul opérateur d'addition suffira : il exécutera l'opération 1 et une fois libéré sera réutilisé pour l'exécution de l'opération 2. À l'issu de l'étape d'ordonnancement, les dates de début et de fin de chaque opération sont connues ainsi que les intervalles durant lesquels les valeurs des données sont actives  $[d_c, d_u]$ , avec  $d_c$  la date de création de la variable et  $d_u$  la date de sa dernière utilisation. Ces informations génèrent des contraintes pour les étapes d'assignation des opérations et l'assignation des variables. Ces contraintes peuvent être représentées sous forme de graphes de compatibilité.

Graphe de compatibilité des variables : un graphe de compatibilité des variables  $G_{dc}$  défini par  $G_{dc} = (V_{dc}, A_{dc})$ , avec  $V_{dc}$  l'ensemble des noeuds représentant les variables. Une arête  $a_{dc} = (vd_i, vd_j) \in A_{dc}$  relie deux sommets si et seulement si leurs durées de vie respectives ne se chevauchent pas. Dans ce cas, les variables  $vd_i$  et  $vd_j$  sont dites compatibles l'une avec l'autre et peuvent être affectées au même registre. La figure 2.4-d est le graphe de compatibilité des variables déduit après l'ordonnancement figure 2.4-c. À partir de ce graphe, on peut déduire qu'il nous faut au moins deux registres, comme il existe au moins un cycle (S2 par exemple) qui a deux variables en vie simultanément. En effet, le nombre de registres minimum est égal au nombre maximum de variables qui sont en vie en même temps. Ainsi, la variable a est compatible avec y: un registre peut contenir ces deux variables. Un deuxième registre sera nécessaire pour stocker les variables b et b. Une autre affectation intuitive des variables consiste à créer un registre pour chaque variable, par conséquent quatre registres seront utilisés.

Graphe de compatibilité des opérations : un graphe de compatibilité des opérations  $G_{oc}$  défini par  $G_{oc} = (V_{oc}, A_{oc})$ , avec  $V_{oc}$  l'ensemble des noeuds représentant les opérations. Une arête  $a_{oc} = (vo_i, vo_j)$  relie deux sommets si et seulement si les opérations correspondantes peuvent être exécutées par le même type d'opérateur, et l'opération  $vo_i$  s'achève avant le début de  $vo_j$ . Dans ce cas, les opérations  $vo_i$  et  $vo_j$  sont dites compatibles et peuvent ainsi être affectées à un même opérateur.

La figure 2.4-e montre que les opérations 1 et 2 sont compatibles : un additionneur suffirait pour les exécuter.

#### 2.1.4 Complexité de la synthèse de haut niveau

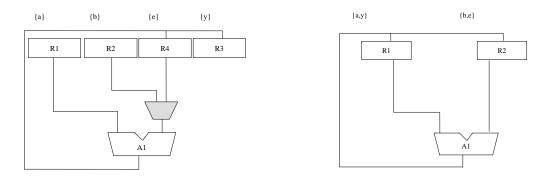

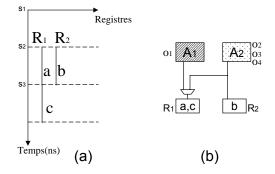

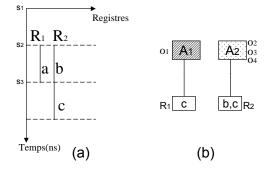

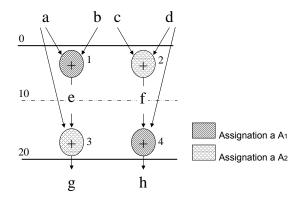

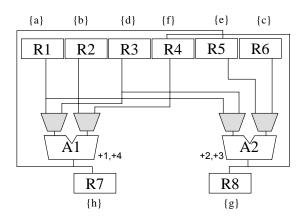

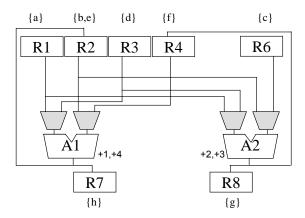

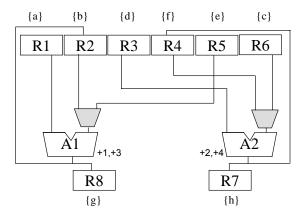

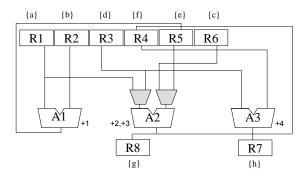

La figure 2.5 montre deux solutions possibles. Une solution correspond à une architecture composée d'opérateurs, de registres et leurs interconnexions. La différence entre les deux solutions réside au niveau de l'assignation des variables.

Dans la première solution figure 2.5-a, chaque variable a été assignée à un registre. Quatre registres, un opérateur et un multiplexeur ont été utilisés dans cette solution. Le multiplexeur

a été crée pour aiguiller les variables qui précédent l'une des entrées de l'opérateur. Celle-ci reçoit une fois la variable b et une fois la variable e, toutes deux stockées dans deux registres différents. Dans la deuxième solution figure 2.5-b les variables ont été regroupées : les variables a et y dans un registre et les variables e et e dans un deuxième registre. Chacune de ces solutions a un coût qui correspond à la somme des coûts des composants de l'architecture. La solution figure 2.5-b a un coût inférieur à celui de la figure 2.5-a comme celle-ci utilise deux registres et un multiplexeur de plus que la solution figure 2.5-b.

Figure 2.5 – Deux solutions d'un même problème

L'un des objectifs principales des outils de synthèse de haut niveau est de trouver une architecture qui a un coût minimal. Trouver les techniques d'ordonnancement, d'allocation, d'assignation des variables et des opérations qui mènent systématiquement à la solution qui coûte le moins est quasiment impossible. Ceci est dû à la complexité et l'interdépendance entre ces sous problèmes.

Parmi les stratégies utilisées dans les outils de synthèse, on trouve le choix de résolution de l'allocation avant l'ordonnancement[Coussy 2008]. Dans ce cas, le nombre d'opérateurs défini à la fin de l'étape d'allocation servira de guide pour l'ordonnancement. Dans certains cas, ce nombre n'est pas définitif et pourra être mis en cause par le résultat de l'ordonnancement. L'ordonnancement se fait ainsi sous contraintes de temps (le débit) et de ressources aussi mais cette dernière contrainte étant flexible peut être revue si son respect s'oppose à celui du respect de la contrainte de temps. Dans le cas ou l'allocation se fait après l'ordonnancement le nombre de ressources allouées sera supérieur ou égal au nombre maximum de ressources utilisées en même temps. Ainsi, le choix de l'ordre d'exécution de ces deux phases influera la solution finale.

Une forte interdépendance existe aussi entre les étapes d'ordonnancement et d'assignation. Ces deux problèmes sont NP-complets [Garey 1979, Pangrle 1991]. En outre, la résolution optimale de chacun de ces sous-problèmes ne mènent pas forcément à la solution optimale au

problème global [Cong 2008]. Ainsi, le choix de l'ordre d'exécution des étapes de la synthèse, définira l'espace de solutions explorable. Par exemple, si l'on décide de résoudre les problèmes d'ordonnancement et d'assignation des opérations en premier, le résultat obtenu limitera les possibilités d'assignations des variables.

Dans la plupart des contributions précédentes qui adressent la génération automatique de la description structurelle, un ordre d'exécution des étapes est prédéfini afin de résoudre le problème étape par étape. Dans cet optique, une étape est entièrement résolue avant de passer aux suivantes. Cette approche sacrifie la bonne résolution d'une étape en faveur des précédentes et ne conduisent pas, par conséquent, à une bonne solution au problème global.

Ainsi les travaux existants qui traitent le problème de la minimisation des ressources dans le flot de la HLS abordent un seul sous problème à la fois ou alors plusieurs de ces sous problèmes dans un ordre prédéfini.

# 2.2 Minimisation de la surface du circuit lors de la synthèse de haut niveau

Depuis une vingtaine d'années, plusieurs méthodes ont été proposées pour améliorer le résultat de la synthèse de haut niveau en terme de surface. Très peu sont les travaux qui ont tenté de résoudre tous les sous problèmes de la synthèse de haut niveau à la fois. Dans un premier temps, les chercheurs se sont focalisés sur la minimisation du nombre d'unités fonctionnelles [Gajski 1992, Paulin 1989a, Rau 1994, Cong 2006] ou des registres [Hashimoto 1971] qui semblaient être, les facteurs qui avaient le plus d'impact sur la surface occupée par une architecture.

La minimisation des opérateurs se fait lors des phases d'allocation et d'ordonnancement. Le problème d'ordonnancement est défini principalement à partir des données qui lui sont proposées en entrée. Deux cas de figures existent :

- L'allocation se fait avant l'ordonnancement. On doit résoudre alors un problème d'ordonnancement sous contraintes de ressources [Gajski 1992].

- En revanche dans le cas contraire ou l'allocation se fait en même temps ou après l'ordonnancement. Ce problème se formule en ordonnancement sous contrainte de temps [Paulin 1989a].

La minimisation des registres, quant à elle, se fait au niveau de l'assignation des variables aux registres [Hashimoto 1971].

Dans un deuxième temps, des études relativement récentes [Chen 2004, Cong 2008] ont montré que le coût des interconnexions doit être pris en compte. En effet, la surface d'un composant d'interconnexion (multiplexeur) peut dépasser celle d'un opérateur ou d'un registre. Par conséquent, des algorithmes de réduction de registres qui tentent de créer un minimum d'interconnexions ont été proposés.

Dans la partie qui suit, nous présenterons les méthodes exactes proposées pour la synthèse de haut niveau (présentation de la méthode - application à la HLS), ensuite nous présenterons les heuristiques et métaheuristiques qui ont été proposées pour la même problématique. Les méthodes exactes seront illustrées au travers de la programmation linéaire en nombre entier et la relaxation continue de cette formulation appliquées principalement aux problèmes d'ordonnancement et d'assignation des opérations. Les méthodes approchées, quant à elles, seront illustrées au travers d'heuristiques appliquées aux problèmes d'allocation, d'ordonnancement et d'assignation des variables et de métaheuristique appliquée à la totalité du flot de synthèse.

#### 2.2.1 Les méthodes exactes pour la HLS

Dans la première partie de cette section nous présentons le principe général de la formulation en programme linéaire en nombre entier. Dans la deuxième partie nous montrons comment cette approche aide à résoudre le problème d'ordonnancement et d'assignation des opérations, ainsi que la façon dont les contraintes d'intégrité de cette formulation peuvent être relaxées pour pouvoir résoudre le problème d'ordonnancement avec la programmation linéaire.

#### 2.2.1.1 La formulation en problème de programmation linéaire en nombre entier

Parmi les premières propositions pour la résolution du problème de la synthèse de haut niveau nous trouvons la formulation des sous problèmes d'ordonnancement et d'assignation en problèmes de programmation linéaire en nombres entiers (PLNE). En mathématique, les problèmes de programmation linéaire (PL) [Guéret 2000] sont des problèmes d'optimisation où la fonction objectif et les contraintes sont toutes linéaires.

Considérons le programme linéaire suivant : A est une matrice  $m \times n$  tel que ses coefficients  $a_{ij}$  sont entiers, c est un vecteur de longueur n tel que les  $c_j$  sont entiers et b est un vecteur de longueur m tel que les  $b_i$  sont entiers.

$$PL = \begin{cases} \text{Minimiser } z = c.x \\ \text{Sous les contraintes :} \\ \text{A.x=b} \\ \text{x>0} \end{cases}$$

Si l'on résout ce PL tel quel, nous allons trouver généralement une solution optimale à composante non entière. Mais, il arrive qu'une solution à composante entières soit nécessaire pour une classe de problèmes particuliers. Ainsi de nouvelles contraintes dites d'intégrités sont nécessaires. On obtient alors le Programme linéaire en Nombres Entiers suivant :

$$PLNE = \begin{cases} \text{Minimiser } z = c.x \\ \text{Sous les contraintes :} \\ \text{A.x=b} \\ x \ge 0 \ x_j \text{ entier } (j = 1..n) \end{cases}$$

Nombreux sont les problèmes NP-complets qui peuvent être exprimés comme des PLNE, les programmes linéaires en nombres entiers sont ainsi des problèmes NP-complet. La relaxation continue d'un PLNE (c'est le PLNE sans les contraintes d'intégrité) est un PL qui peut être résolu efficacement et fournir ainsi une borne inférieure.

Plusieurs approches existent pour résoudre un PLNE, on en citera deux :

- L'algorithme par séparation et évaluation qui se base sur une relaxation continue pour diminuer au maximum l'énumération des solutions (Branch and Bound).

- Les méthodes de coupes qui s'appuient sur la résolution du PL continu dans un premier temps, puis dans un deuxième temps sur l'ajout progressif de contraintes qui vont éliminer les solutions extrêmes continues sans éliminer les solutions entières (c'est ce qu'on appelle une coupe) et s'arrêter dès que notre PL nous donne une solution extrême entière.

#### 2.2.1.2 Formulations de problèmes de la HLS en PLNE

Cette sou-section présente :

- A- une formulation du problème d'ordonnancement en PLNE,

- B- une extension de cette formulation pour résoudre le problème d'assignation des opérations en même temps que l'ordonnancement,

- C- une relaxation continue du PLNE pour l'ordonnancement.

#### A- PLNE pour l'ordonnancement

La résolution du PLNE du problème d'ordonnancement sous contraintes de temps pour la synthèse de haut niveau mène à un ordonnancement optimal en terme de nombre d'opérateurs. La résolution de la formulation PLNE de ce problème peut se faire à l'aide de la méthode d'évaluation et de séparation, branch-and-bound.

Soient les notations du tableau 2.2.1.2. La fonction objectif 2.1 assure la minimisation du coût des opérateurs. La contrainte 2.2 veille à ce que chaque opération  $o_i$  soit placée dans une seule étape  $s_j$  qui appartient à la fenêtre de temps [Ei, Li]. Ei est la date d'ordonnancement de l'opé-

ration  $o_i$  au plus tôt et Li sa date d'ordonnancement au plus tard obtenues respectivement suite aux ordonnancements ASAP et l'ordonnancement ALAP. La contrainte 2.3 oblige le nombre de d'opérateurs de type k alloués, à être supérieur ou égal au nombre maximal d'opérateurs sollicité dans les différentes étapes j.

$OP = \{o_i / i = 1..n\}$ : l'ensemble des opérations et n le nombre d'opérations

$T=\{t_k/k=1..m\}$  : l'ensemble des différents types d'opérateurs et m la taille de

cet ensemble

$OP_{t_k}$ : l'ensemble des opérations de type  $t_k$

$INDEX_{t_k} = \{i/o_i \in OP_{t_k}\}$ : l'ensemble des indices des opérations de type  $t_k$

$N_{t_k}$ : le nombre d'opérateurs de type  $t_k$   $C_{t_k}$ : le coût d'un opérateur de type  $t_k$

$S = \{s_i/j = 1..r\}$ : le temps étant discrétisé, S est l'ensemble des étapes et r le

nombre d'étape

Table 2.1 - Notations

$$minimiser \sum_{k=1}^{m} C_{t_k} \times N_{t_k}$$

(2.1)

$$\forall i, 1 \leqslant i \leqslant n, (\sum_{E_i \leqslant j \leqslant L_i} x_{i,j} = 1) \tag{2.2}$$

$$\forall j, 1 \leqslant j \leqslant r, \forall k, 1 \leqslant k \leqslant m, \left(\sum_{i \in INDEX_{t_k}} x_{i,j} \leqslant N_{t_k}\right)$$

(2.3)

$$\forall i, j, o_i \in pred_{o_j}(\sum_{E_i \leqslant k \leqslant L_i} (k \times x_{i,k}) - \sum_{E_i \leqslant l \leqslant L_i} (l \times x_{j,l}) \leqslant -1)$$

(2.4)

$$x_{ij} \in \{0, 1\} \forall i, \forall j. \tag{2.5}$$

La contrainte 2.4 garantit pour une opération donnée  $o_j$ , que tous ses prédécesseurs (i.e.  $pred_{o_j}$ ) achèvent leurs exécutions plus tôt que sa date de début. En d'autres termes que si  $x_{i,k} = x_{j,l} = 1$  alors k < l, avec k et l sont respectivement les dates de début éventuelles des

opérations i et j. Enfin, la contraintes 2.5 fixe le domaine de définition des variables de décision  $x_{ij}$ . Les variables de décision sont spécifiées par :

$$x_{ij} = \begin{cases} 1 & \text{si l'opération } i \text{ est placée à l'étape } j \\ 0 & \text{sinon} \end{cases}$$

Une fois définies, les valeurs des variables de décision  $x_{ij}$  construisent une solution pour le problème d'ordonnancement des opérations d'un graphe donné.

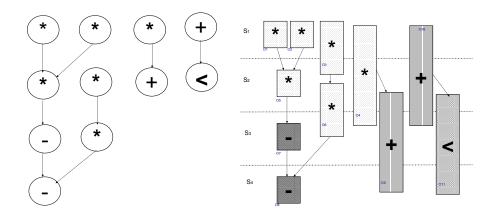

Exemple Prenons l'exemple [Gajski 1992] d'une application qui peut utiliser quatre types d'opérateurs (multiplieur, additionneur, soustracteur, comparateur).  $C_m$  et  $N_m$  sont respectivement le coût et le nombre de multiplieur;  $C_a$  et  $N_a$  sont respectivement le coût et le nombre d'additionneur;  $C_s$  et  $N_s$  sont respectivement le coût et le nombre de soustracteur;  $C_c$  et  $N_c$  sont respectivement le coût et le nombre de comparateur.

La fonction objectif est : Minimiser  $Cm * N_m + C_a * N_a + C_s * N_s + C_c * N_c$

FIGURE 2.6 – (a) DFG (b) Expression des contraintes

Ainsi, pour l'exemple de la figure 2.6, les contraintes définissant une fenêtre de temps pour chaque opération deviennent :

$$\begin{array}{lll} x_{1,1}=1, & x_{2,1}=1 \\ x_{5,2}=1, & x_{7,3}=1 \\ x_{7,3}=1, & x_{8,4}=1 \\ x_{3,1}+x_{3,2}=1, & x_{4,1}+x_{4,2}+x_{4,3}=1 \\ x_{6,2}+x_{6,3}=1, & x_{9,2}+x_{9,3}+x_{9,4}=1 \\ x_{10,1}+x_{10,2}+x_{10,3}=1, & x_{11,2}+x_{11,3}+x_{11,4}=1 \end{array}$$

les contraintes permettant de respecter les contraintes de précédences :

$$1x_{4,1} + 2x_{4,2} + 3x_{4,3} - 2x_{9,2} - 3x_{9,3} - 4x_{9,4} = -1$$

$$1x_{3,1} + 2x_{3,2} - 2x_{6,2} - 3x_{6,3} = -1$$

$$1x_{10,1} + 2x_{10,2} + 3x_{10,3} - 2x_{11,2} - 3x_{11,3} - 4x_{11,4} = -1$$

et les contraintes définissant pour chaque type le nombre d'opérateur utilisé dans un cycle donné :

$$\begin{array}{lll} x_{1,1} + x_{2,1} + x_{3,1} + x_{4,1} = N_m, & x_{9,3} + x_{10,3} = N_a \\ x_{3,2} + x_{4,2} + x_{5,2} + x_{6,2} = N_m, & x_{9,4} = N_a \\ x_{4,3} + x_{6,3} = N_m, & x_{11,2} = N_c \\ x_{7,3} = N_s, & x_{11,3} = N_c \\ x_{8,4} = N_s, & x_{11,4} = N_c \\ x_{10,1} = N_a, & x_{10,2} = N_a \end{array}$$

Ainsi, en supposant que  $C_m = 2$  et  $C_a = C_b = C_a = 1$  et  $N_m = 2$ ,  $N_a = N_s = N_c = 1$ , la fonction de coût est minimisée et toutes les contraintes sont respectées si les variables décision ont les valeurs suivantes :  $x_{1,1} = x_{1,2} = x_{1,1} = x_{3,2} = x_{4,3} = x_{5,2} = x_{6,3} = x_{7,3} = x_{8,4} = x_{9,4} = x_{10,2} = x_{11,4} = 1$  et les autres variables de décision  $x_{i,j} = 0$ .

Cette solution peut être obtenue à l'aide d'une procédure de séparation et d'évaluation (PSE).

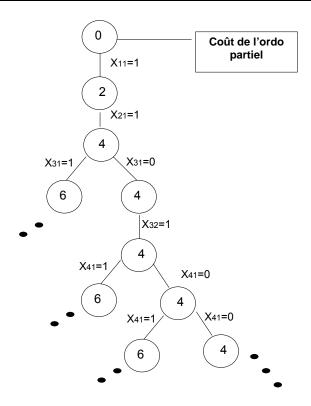

Cette procédure consiste à construire un arbre de recherche et séparation. Un arbre de recherche est un arbre (souvent binaire) dont chaque sommet représente une solution partielle réalisable. Celle-ci est retrouvée en prenant les valeurs données aux variables de décision, partant de la racine jusqu'au noeud considéré. En arrivant aux feuilles de l'arbre, nous obtenons des solutions réalisables complètes. À chaque noeud est associé une valeur qui correspond au coût de la solution partielle représentée par le noeud.

Dans la figure 2.7, le noeud racine à un coût nul. Ce noeud a un seul fils comme la variable  $x_{1,1}$  ne peut prendre qu'une seule valeur selon les contraintes définissant les fenêtres de temps. Le deuxième noeud, partant du haut dans le même arbre, correspond ainsi à la solution partielle qui affecte l'opération  $o_1$  à l'étape  $s_1$ . Cette affectation à un coût égal à deux. Ce coût correspond à l'utilisation d'un multiplieur.

FIGURE 2.7 – Arbre de recherche et séparation

#### B- PLNE pour l'ordonnancement et l'assignation

Pour résoudre le problème de l'assignation en même temps que l'ordonnancement il suffit d'ajouter une variable de décision qui associe une opération à un opérateur et des contraintes qui garantissent la compatibilité des opérations assignées à un même opérateur [Wilson 1994].

- Si deux opérations sont assignées à un même opérateur, cela signifie que l'une doit précéder l'autre.

- Si une opération précède une autre et sont toutes les deux assignées à un même opérateur, la date de début de la deuxième opération est bornée par la date de fin de la première opération.

Critique Comme dit précédemment un problème linéaire en nombre entier est un prblème NP-complet. Ainsi, cette méthode se limite aux instances ayant un nombre de noeuds et de contraintes très petit. C'est pour cette raison que cette piste n'a pas était developpée depuis. Cependant, une étude assez récente, propose une relaxation continue de la formulation PLNE du problème d'ordonnancement.

#### C- Relaxation continue de la formulation PLNE du problème d'ordonnancement

Dans les travaux de [Cong 2006] le problème d'ordonnancement pour la HLS a été modélisé par un programme linéaire. En effet, seules les solutions entières du programme linéaire correspondent à des solutions au problème. La difficulté réside donc à prouver qu'il existe toujours une solution entière au programme linéaire. Cette méthode ne garantit pas l'optimalité de la solution mais assure une solution optimisé en un temps polynomiale.

Les étapes de cette méthode sont les suivantes :

- Formuler les contraintes en un système de contraintes différenciées SDC .

- Vérifier que le SDC est faisable.

- Représenter l'objectif de l'ordonnancement en une fonction objective linéaire.

- Résoudre la relaxation linéaire et choisir la solution entière qui optimise la fonction objectif.

La première étape consiste donc à traduire les contraintes du problème en un système de contraintes différenciées .

**Définition 1** Un système de contraintes différencier SDC est un système (X,C) tel que X est l'ensemble de variables et C l'ensemble des inéquations linéaires de la forme  $x_j - x_i \leq b_k$ , ou  $1 \leq i, j \leq n$  et  $1 \leq k \leq m$ , avec n le nombre de variables d'ordonnancement qui indique le cycle de début d'exécution d'une opération donnée et m le nombre de contraintes.

Cette forme restrictive de contraintes linéaires peut être représentée par un graphe appelé graphe de contraintes. Celui-ci peut être construit en modélisant les variables par des sommets et une contraintes  $x - y \le b$  par un arc dirigé allant de y à x et ayant un poids b. Un SDC est cohérent si et seulement si son graphe de contraintes ne contient aucun cycle négatif.

**Définition 2** Dans un graphe annoté, un cycle négatif est un cycle dont la somme des poids des arcs est négative.

Pour détecter l'existence de cycle négatif dans le graphe on peut résoudre le problème du plus court chemin dans le graphe de contraintes. En utilisant l'algorithme de Bellman-Ford, la complexité est de O(mn) avec n le nombre de variables et m le nombre de contraintes. Une fois le système de contraintes SDC construit et sa faisabilité prouvée, reste à démontrer que le programme linéaire donne toujours des solutions entières au problème. En effet, la matrice sous-jacente à un système de contraintes SDC est une matrice totalement unimodulaire. Cette propriété garantie que la relaxation du problème d'ordonnancement en un programme linéaire

donne des optimums entiers en un temps polynomial.

**Définition 3** Une matrice est totalement unimodulaire, si toute sous-matrice carrée a un déterminant de -1,0 ou +1.

**Théorème 1** Un programme linéaire (min cT x tel que  $x \ge 0$ ,  $Ax \ge b$ ) a un optimum entier pour tout vecteur c, b (avec b entier) si et seulement si A est totalement unimodulaire.

Cette méthode peut modéliser les contraintes de ressources, la fréquence de l'horloge, la contrainte de latence et les contraintes de temps relatives. Elle peut optimiser ou bien la latence du chemin critique, ou la latence totale. La modélisation peut représenter les opérations multi-cycles et les opérateurs pipelines.

Les inconvénients majeurs de cette méthode sont : (1) La modélisation des contraintes de ressources se basent sur une heuristique qui supposera que certaines opérations sont plus prioritaires que d'autres. Ainsi, l'espace de solution sera partiellement exploré. (2) La modélisation d'une fonction objectif minimisant les ressources n'a pas était proposée.

## 2.2.2 Les méthodes approchées pour la HLS

Les méthodes exactes étant applicables uniquement aux petites instances, diverses heuristiques ont été proposées pour la HLS. Une heuristique est un algorithme qui fournit rapidement (en temps polynomial) une solution réalisable, pas nécessairement optimale, pour un problème d'optimisation. Généralement, une heuristique est conçue pour un problème particulier, en s'appuyant sur sa structure propre, mais les approches peuvent contenir des principes plus généraux. On parle de métaheuristiques pour les méthodes approximatives générales, pouvant s'appliquer à différents problèmes (comme le recuit simulé par exemple).

La qualité d'une heuristique peut s'évaluer selon deux critères scientifiques :

- Critère pratique, ou empirique : on implémente l'algorithme approximatif et on évalue la qualité de ses solutions par-rapport aux solutions optimales (ou aux meilleures solutions connues). Ceci passe par la mise en place d'un banc d'essai (en anglais benchmark, ensemble d'instances d'un même problème accessible à tous).

- Critère mathématique : il faut démontrer que l'heuristique garantit des performances.

La garantie la plus solide est celle des algorithmes approchés, sinon il est intéressant de démontrer une garantie probabiliste, lorsque l'heuristique fournit souvent, mais pas toujours, de bonnes solutions.

Différentes heuristiques adaptées aux sous problèmes de la HLS ont été proposées. Pour l'étape d'ordonnancement, nous citons l'ordonnancement dirigé par les forces (FDS) [Paulin 1989b] et la méthode du raffinement itératif pour l'ordonnancement [Park 1991], proposées pour le cas ou l'allocation se fait après l'ordonnancement et l'ordonnancement par liste [Gajski 1992] et de l'ordonnancement modulo [Rau 1994] proposées pour le cas ou l'allocation se fait avant l'ordonnancement.

Plusieurs heuristiques ont été proposées pour l'étape d'assignation des variables. Nous citons le "Left-Edge" [Hashimoto 1971, Kurdahi 1987], la version modifiée de cet algorithme [Andriamisaina 2008], et l'heuristique qui s'appuie sur la méthode du MWBM [Galil 1986, Papadimitriou 1998]. Cette dernière peut être utilisée pour résoudre l'assignation des opérations aussi. Des études relativement récentes [Cong 2008] ont proposé une heuristique qui assigne simultanément les opérateurs et les registres.

Dans ce manuscrit nous avons choisi de présenter les algorithmes du "Left-Edge", la version modifiée de celui-ci et l'heuristique qui assigne simultanément les opérateurs et les registres. Enfin, nous présentons une méthaheuristique qui s'appuie sur une approche évolutionniste pour l'optimisation de la surface et du temps [Ferrandi 2007]. Cette approche touche à toutes les

étapes de la synthèse de haut niveau.

Algorithme "Left-Edge" L'objectif de cette méthode est d'aboutir à une solution qui utilise un minimum de registres [Hashimoto 1971, Kurdahi 1987]. Différentes architectures utilisant le nombre minimum de registres existent. Ceci dépend des assignations des variables à ces registres. L'inconvénient majeur de cet algorithme est qu'il ne se soucie pas de la création éventuelle de multiplexeurs. Ainsi la réduction du nombre de registres peut conduire à la création de plusieurs multiplexeurs. Par conséquent, la surface occupée lors de la création des multiplexeurs peut être supérieure aux gains à cause de la réduction du nombre de registres.

La première étape de cet algorithme consiste à trier les variables par dates de production. Ensuite, un premier ensemble de registres est crée pour les variables les plus à gauche de la liste triée, dont les durées de vie se chevauchent. Enfin, pour chacune des variables restantes, une recherche de registre compatible entre ceux qui existent déjà est faite. Cette recherche se fait en partant du registre le plus à gauche et en testant si la variable est compatible avec les variables déjà assignées au registre. Si aucune possibilité d'assignation de la variable n'est trouvée alors un nouveau registre est créé pour la stocker.

Algorithme "Left-Edge" modifié L'algorithme LEA trouve le nombre optimal de registres, cependant, il ne se soucie pas du surcoût engendré par la création de multiplexeurs. Cet algorithme a été modifié par [Andriamisaina 2008] pour prendre en compte le surcoût des multiplexeurs. Cette fois, le choix du registre se fait après une phase d'évaluation de toutes les solutions partielles possibles.