# Safe Design Method of COTS based embedded systems based on COTS

S. Hajjar

#### ► To cite this version:

S. Hajjar. Safe Design Method of COTS based embedded systems based on COTS. Automatic Control Engineering. INSA de Lyon, 2013. English. NNT: . tel-01079889

### HAL Id: tel-01079889 https://hal.science/tel-01079889

Submitted on 4 Nov 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE

prsentée devant L'INSTITUT NATIONAL DES SCIENCES APPLIQUÉES DE LYON pour obtenir le grade de

DOCTEUR DE L'INSA DE LYON

Spécialité : Automatique

par

#### SALAM HAJJAR

École Doctorale : Electronique Electrotechnique et Automatique (EEA) Équipe d'accueil : Équipe FDS (Fiabilité, Diagnostique, Supervision) - Laboratoire Ampère

Titre

### CONCEPTION SÛRE DE SYSTÈMES EMBARQUÉS À BASE DE COTS

Soutenance prévue le 16 Juillet 2013 devant le jury composé de

| M. Martin FABIAN       | Université de technologie de Chalmers | Rapporteur         |

|------------------------|---------------------------------------|--------------------|

| M. Jean François PÉTIN | CRAN - Université de Lorraine         | Rapporteur         |

| M. Hassane ALLA        | GIPSA - Université de Grenoble        | Examinateur        |

| M. Armand TOGUYENI     | LAGIS - École Centrale de Lille       | Examinateur        |

| M. Éric NIEL           | AMPÈRE - INSA de Lyon                 | Directeur de these |

| M. Emil DUMITRESCU     | AMPÈRE - INSA de Lyon                 | Co-encadrant       |

## A SAFE COTS-BASED DESIGN FLOW OF EMBEDDED SYSTEMS

### Abstract

This PhD dissertation contributes to the safe design of COTS-based control-command embedded systems. Due to design constraints bounding delays, costs and engineering resources, component re-usability has become a key issue in embedded design.

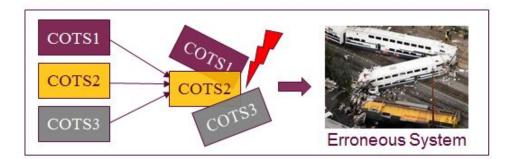

The major difficulty in designing these systems is the high number of COTS components, which usually are separately built. The design process amounts to assembling these elementary components; this often establishes a certain amount of interaction between sets components which were not initially intended to interact with each others. Thus, unwanted behaviors may occur, although each component taken separately is considered free of local errors. The challenge that the designer faces is to ensure a safe behavior of the system which is built over the COTS components.

Our proposal is a design method which ensures correction of COTS-based designs. This method uses in synergy a number of design techniques and tools. It starts from modeling of the COTS components which are stored in a generic COTS library, and ends with a design of the global control-command system, verified to be free of errors and ready to be implemented over a hardware chip such as an ASIC or an FPGA "Field Programmable Gate Array".

The designer starts by modeling the temporal and logical local preconditions and postconditions of each COTS component, then the global pre/post conditions of the assembly which are not necessary a simple combination of local properties. He models also a list of properties that must be satisfied by the assembly. Any violation of these properties is defined as a design error. Then, by using the model checking approach the model of the assembly is verified against the predefined local and global properties. Some design errors can be corrected automatically through the Discrete Controller Synthesis method (DCS), others however must be manually corrected. After the correction step, the controlled control-command system is verified. Finally a global simulation step is proposed in order to perform a system-level verification beyond the capabilities of available formal tools.

A human intellectual intervention in this design method appears is the intermediate step between detecting the errors and correcting them automatically. The model checking technique can only discover the errors and provide a counterexample which indicates where and how a property was violated, however, it leaves the correction task to the designer. On the other hand, DCS can correct errors by generating a "correct-by-construction" patch which controls the bugged component by assigning a subset of its inputs, designated as "controllable". Despite its obvious advantages, the brute force application of this operation is completely unnatural to embedded designers. We propose to use the model-checking counterexample as a hint for guiding the application of DCS.

Thus, our study combines three design techniques: the formal verification, the discrete controller synthesis and simulation, in order to provide a system safe by construction with the minimum manual interaction, to avoid making human mistakes in the design. We mention the advantages of each technique and argue its disadvantages and explain how each one is necessary for the others to provide an integrated work. We apply the method on two different systems, one concerns transferring data from senders to receivers through FIFO unit, the other is controlcommand system of a train passengers' access.

### Résumé

Le travail présenté dans ce mémoire concerne une méthode de conception sûre de systèmes de contrôle-commande matériels embarqués constitués à base des composants sur étager (COTS). Un COTS est un composant matériel ou logiciel générique qui est naturellement conçu pour être réutilisable et cela se traduit par une forme de flexibilité dans la mise en oeuve de sa fonctionnalité : en clair, une même fonction peut être réalisée par un ensemble (potentiellement infini) de scénarios différents, tous réalisables par le COTS.

Par ailleurs, comme les COTS sont souvent conçus séparément, leur interconnexion peut engendrer, de par cette flexibilité inhérente, des situations non désirées, liées à la nouvelle exigence fonctionnelle ciblée. Ces situations se traduisent par des états " à éviter " sous peine d'effectuer des actions de contrôle commande incorrectes voire dangereuses. L'intégration des COTS dans le processus de conception des systèmes matériels réduit le temps de conception et permet d'utiliser des composants génériques existant sur le marché. On assemble des COTS pour obtenir des nouvelles fonctions, plus complexes. La démarche d'assemblage de composants se heurte cependant à un dilemme entre généricité, en vue d'une réutilisation la plus large possible, et spécialisation en lien avec un besoin de contrôle commande particulier.

La complexité grandissante des fonctions implémentées fait que ces situations sont très difficiles à anticiper d'une part, et encore plus difficiles à éviter par un codage correct. Réaliser manuellement une fonction composite correcte sur un système de taille industrielle, s'avère être très coûteuse. Elle nécessite une connaissance approfondie du comportement des COTS assemblés. Or cette connaissance est souvent manquante, vu qu'il s'agit de composants acquis, ou développés par un tiers, et dont la documentation porte sur la description de leur fonction et non sur sa mise en IJuvre. Par ailleurs, il arrive souvent que la correction manuelle d'une faute engendre une ou plusieurs autres fautes, provoquant un cercle vicieux difficile à maîtriser. En plus, le fait de modifier le code d'un composant diminue l'avantage lié à sa réutilisation.

C'est dans ce contexte que nous proposons l'utilisation de la technique de synthèse du contrôleur discret (SCD) pour générer automatiquement du code de contrôle commande correct par construction. Cette technique produit des composants, nommés contrôleurs, qui agissent en contraignant le comportement d'un (ou d'un assemblage de) COTS afin de garantir si possible la satisfaction d'une exigence fonctionnelle. La méthode que nous proposons possède plusieurs étapes de conception.

La première étape concerne la formalisation des COTS et des propriété de sûreté et de vivacité (P) en modèles automate à états et/ou en logique temporelle. L'étape suivante concerne la vérification formelle du modèle d'un(des) COTS pour l'ensemble des propriétés (P). Cette étape découvrir les états de violation des propriétés (P) appelés états d'erreur. La troisième étape concerne la correction automatique des erreurs détectées en utilisant la technique SCD. Dans cette étape génère on génère un composant correcteur qui sera assemblé au(x) COTS original(aux) pour que leur comportement général respecte les propriétés souhaitées. L'étape suivante concerne la vérification du système contrôlé pour un ensemble de propriétés de vivacité pour assurer la passivité du contrôleur et la vivacité du système. En fin, une étape de simulation est proposée pour observer le comportement du système pour quelque scénarios intéressent par rapport à son implémentation finale.

Pour montrer l'applicabilité de la méthode proposée, et sa faculté à être utilisée en milieu industriel, nous l'utilisons sur un exemple de système de contrôle-commande de train.

## Contents

| A  | ostrac  | et            |                                                               | iii  |

|----|---------|---------------|---------------------------------------------------------------|------|

| Ré | ésumé   | <u>;</u>      |                                                               | v    |

| Li | st of l | Figures       |                                                               | xi   |

| Li | st of ] | <b>Fables</b> |                                                               | xiii |

| In | trodu   | ction         |                                                               | 1    |

| 1  | Safe    | design        | of hardware embedded systems based on COTS : State of the art | 7    |

|    | 1.1     | Introd        | uction                                                        | 7    |

|    | 1.2     | Model         | ling hardware systems                                         | 7    |

|    |         | 1.2.1         | Event-driven modeling                                         | 8    |

|    |         |               | 1.2.1.1 Formal language                                       | 8    |

|    |         |               | Notice.                                                       | 9    |

|    |         |               | 1.2.1.2 Common notions in event-driven modeling               | 10   |

|    |         | 1.2.2         | Sample-driven modeling                                        | 14   |

|    |         |               | 1.2.2.1 Translating event-driven into sample-driven models    | 16   |

|    |         |               | 1.2.2.2 Modeling interaction                                  | 18   |

|    |         | 1.2.3         | Synchronous product with interaction                          | 20   |

|    |         | 1.2.4         | Efficient manipulation of symbolic models                     | 21   |

|    | 1.3     | Behav         | ior requirements specification                                | 22   |

|    |         | 1.3.1         | Logic specifications                                          | 23   |

|    |         |               | 1.3.1.1 Linear-time temporal logic (LTL)                      | 24   |

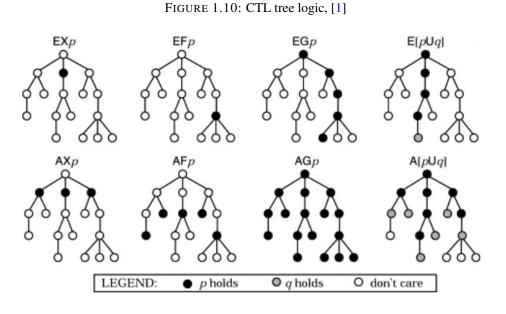

|    |         |               | 1.3.1.2 Computation tree logic (CTL)                          | 24   |

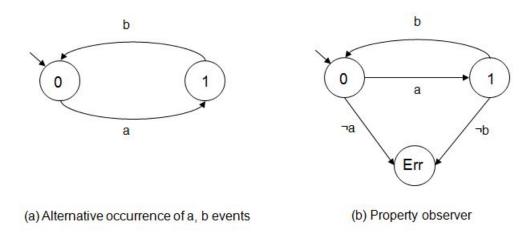

|    |         | 1.3.2         | Operational specifications                                    | 26   |

|    |         | 1.3.3         | The Property Specification Language (PSL) standard            | 27   |

|    | 1.4     | Verific       | cation of hardware embedded systems                           | 28   |

|    |         | 1.4.1         | Theorem proving                                               | 29   |

|    |         | 1.4.2         | Guided simulation                                             | 30   |

|    |         | 1.4.3         | Model checking                                                | 30   |

|    | 1.5     | Superv        | visor synthesis                                               | 32   |

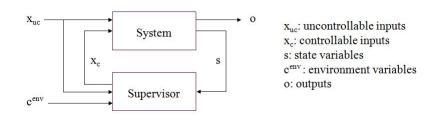

|    |         | 1.5.1         | Supervisory control                                           | 32   |

|    |         | 1.5.2         | Controllability in hardware systems                           | 33   |

|    |         | 1.5.3         | Symbolic supervisor synthesis                                 | 34   |

#### Contents

|   |     | 1.5.4   | DCS for hardware designs                                            |

|---|-----|---------|---------------------------------------------------------------------|

|   | 1.6 | COTS    | -based design                                                       |

|   |     | 1.6.1   | COTS definitions                                                    |

|   |     | 1.6.2   | COTS integration in a design process, difficulties and solutions 39 |

|   |     | 1.6.3   | Safety preserving formal COTS composition                           |

|   |     | 1.6.4   | Safety in component-based development                               |

|   | 1.7 |         | 1sion                                                               |

|   |     |         |                                                                     |

| 2 |     |         | based design method 47                                              |

|   | 2.1 |         | action                                                              |

|   | 2.2 |         | ng COTS-based control-command systems                               |

|   |     | 2.2.1   | Stand-alone COTS                                                    |

|   |     |         | The need for environment assumptions                                |

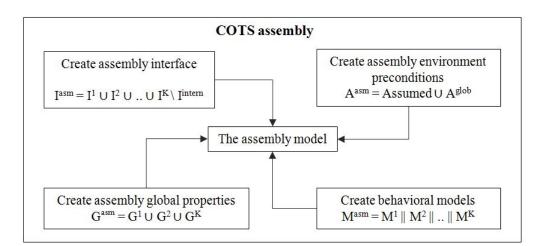

|   |     | 2.2.2   | <b>COTS</b> assembly                                                |

|   |     |         | Structural assessment of COTS interconnections                      |

|   |     | 2.2.3   | Compositional reasoning                                             |

|   |     |         | Incompatibility between environment assumptions                     |

|   |     |         | Contradiction between guarantees and environment assumptions 57     |

|   |     |         | Compatibility between guarantees and environment assumptions 58     |

|   |     |         | Cyclic reasoning                                                    |

|   |     | 2.2.4   | Adding context-specific requirements                                |

|   |     | 2.2.5   | Design errors                                                       |

|   |     | 2.2.6   | Global design error                                                 |

|   |     | 2.2.7   | Enforcing local/global properties                                   |

|   |     |         | 2.2.7.1 Computing the controllable input set                        |

|   |     |         | 2.2.7.2 Environment-aware DCS                                       |

|   |     |         | 2.2.7.3 Environment modeling                                        |

|   |     |         | 2.2.7.4 The environment aware DCS algorithm                         |

|   |     |         | 2.2.7.5 Applying EDCS to COTS-based designs                         |

|   |     |         | Specific terminology for a EDCS-corrected COTS: Glue and            |

|   |     |         | Patch controllers                                                   |

|   |     | 2.2.8   | Implementing the control loop                                       |

|   |     |         | The general control loop                                            |

|   |     |         | Controllable inputs with hard reactive constraints                  |

|   |     |         | Controllable inputs with soft reactive constraints                  |

|   |     | 2.2.9   | The "event invention" phenomenon                                    |

|   |     | 2.2.10  |                                                                     |

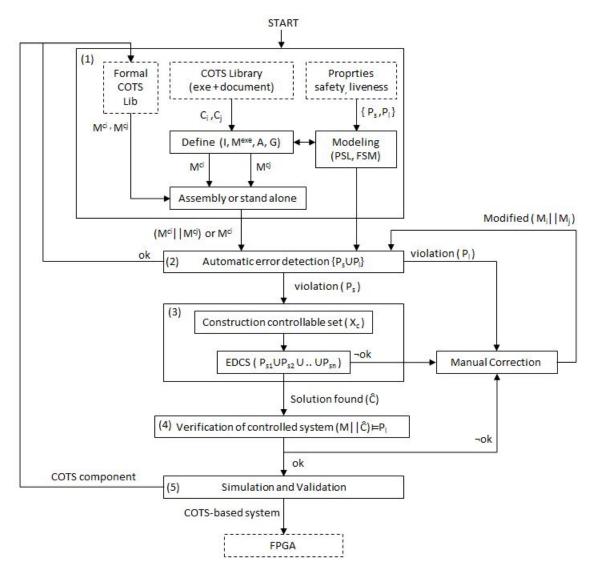

|   | 2.3 | The sa  | fe COTS-based design method                                         |

|   |     |         | Step 1: Modeling                                                    |

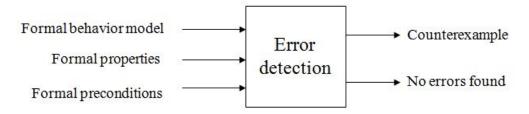

|   |     |         | Step 2: Automatic error detection                                   |

|   |     |         | Step 3: Automatic error correction                                  |

|   |     |         | Step 4: Formal verification                                         |

|   |     |         | Step 5: Simulation                                                  |

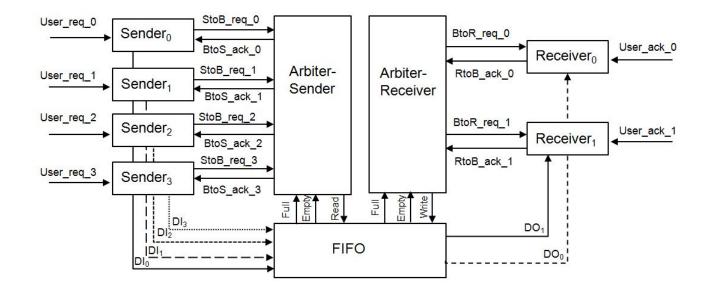

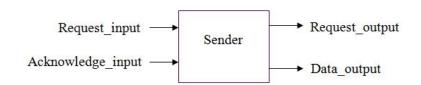

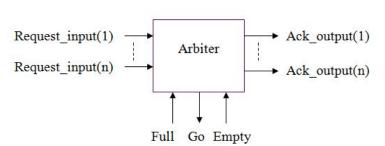

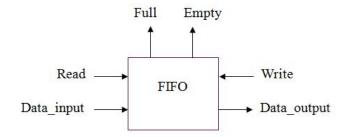

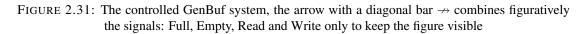

|   | 2.4 | Runnii  | ng example : the generalized buffer design                          |

|   |     |         | The GenBuf functional behavior                                      |

|   | 2.5 | Step 1. | . Modeling                                                          |

|   |     |         |                                                                     |

|   |      | 2.5.1    | From text to formal requirement expressions                            |

|---|------|----------|------------------------------------------------------------------------|

|   |      | 2.5.2    | Example: modeling components of the GenBuf design                      |

|   |      | 2.5.3    | Exemple : writing global properties for the GenBuf design 88           |

|   | 2.6  | Step 2.  | Automatic error detection                                              |

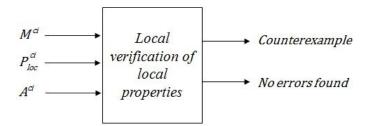

|   |      | 2.6.1    | Local verification of local properties                                 |

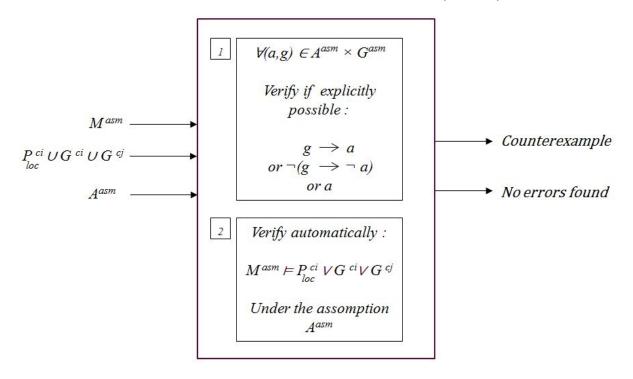

|   |      | 2.6.2    | Global verification of local properties                                |

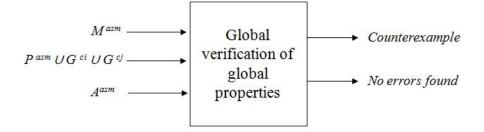

|   |      | 2.6.3    | Global verification of global properties                               |

|   | 2.7  | Step 3.  | Automatic error correction                                             |

|   |      | 2.7.1    | Automatic synthesis of a correcting controller                         |

|   | 2.8  | Step 4.  | Verification of the corrected/controlled system                        |

|   |      |          | The guarantee is a safety property with no assumptions 97              |

|   |      |          | The guarantee is a safety property relying on assumptions 97           |

|   | 2.9  | Step 5.  | Simulation                                                             |

|   | 2.10 | Conclu   | sion                                                                   |

| 3 | Арр  | lication | on an industrial system 103                                            |

|   | 3.1  | Introdu  | lection                                                                |

|   | 3.2  | FerroC   | OTS: Presentation and Goal                                             |

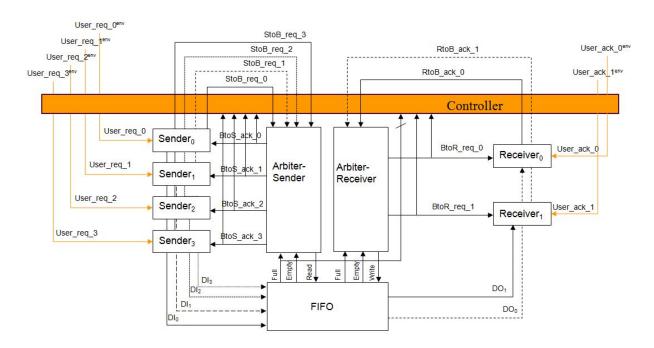

|   | 3.3  | The Pa   | ssengers Access System                                                 |

|   |      | 3.3.1    | Design objectives                                                      |

|   |      | 3.3.2    | Structural description of the available COTS                           |

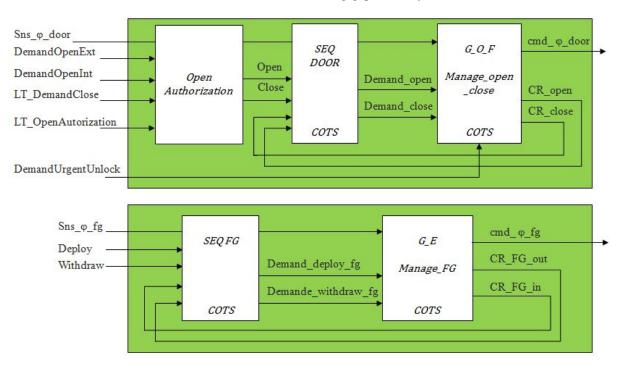

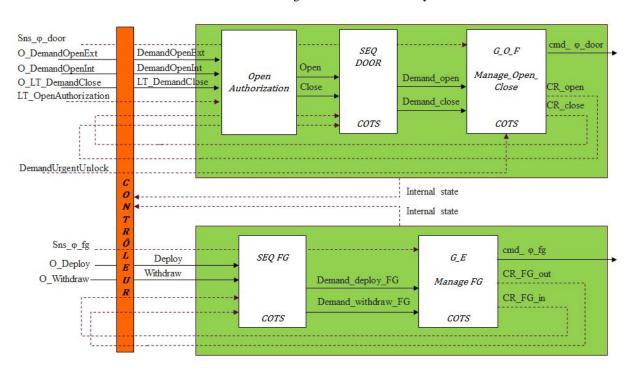

|   |      | 3.3.3    | Behavioral description of the COTS assembly                            |

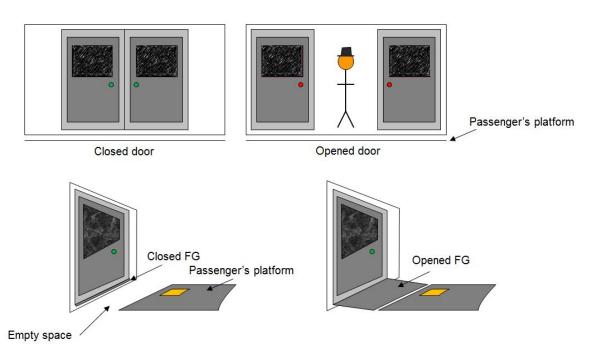

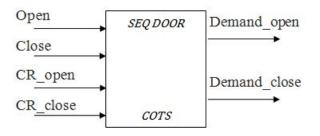

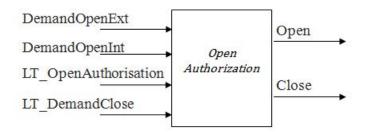

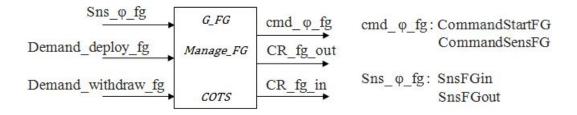

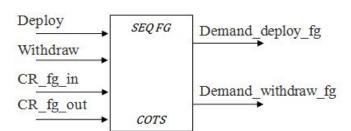

|   |      | 3.3.4    | Modeling and formal specification                                      |

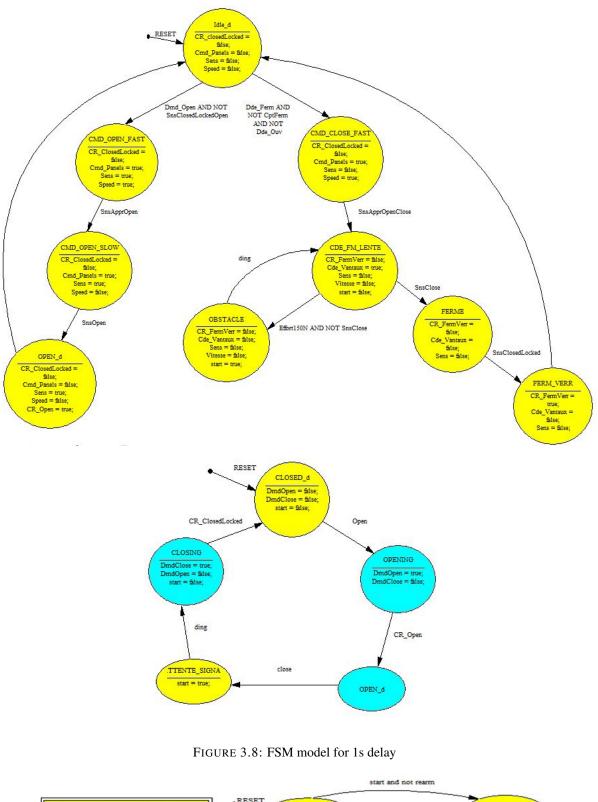

|   |      |          | 3.3.4.1 The stand-alone door component                                 |

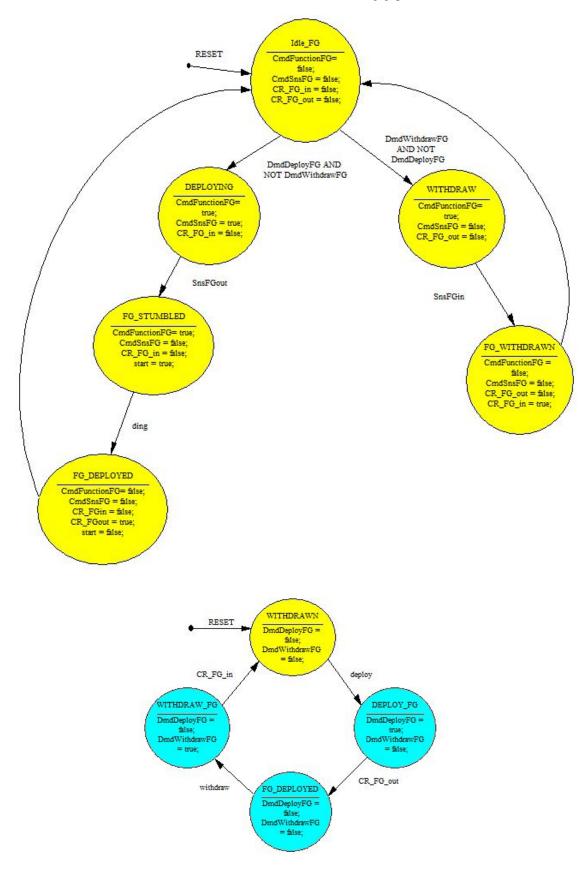

|   |      |          | 3.3.4.2 Stand-alone filling-gap component                              |

|   |      |          | 3.3.4.3 The Door / Filling-gap assembly                                |

|   |      |          | 3.3.4.4 Functional requirements of the door - filling-gap assembly 115 |

|   |      | 3.3.5    | Error detection                                                        |

|   |      | 3.3.6    | Error correction                                                       |

|   |      |          | 3.3.6.1 Controllable variables                                         |

|   |      |          | 3.3.6.2 Correcting controller generation                               |

|   |      |          | Overview of the generated controller                                   |

|   |      | 3.3.7    | Verification of controlled passenger access system                     |

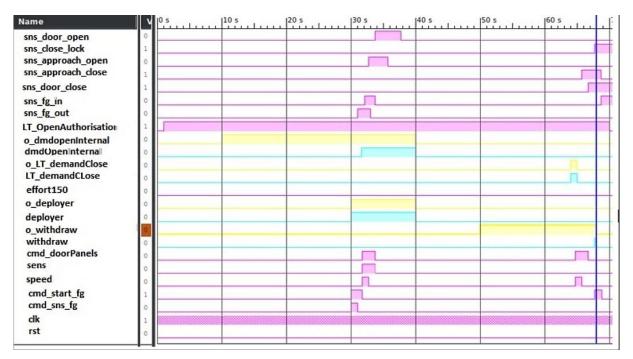

|   |      | 3.3.8    | Simulation                                                             |

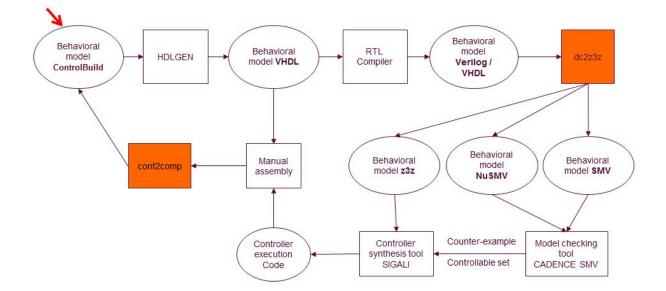

|   | 3.4  | Compa    | rison: assembly controlled synthesis vs. the initial assembly          |

|   | 3.5  | Implen   | nentation                                                              |

|   | 3.6  | Conclu   | sion                                                                   |

|   |      |          |                                                                        |

| A | Cah                         | Cahier des charges fonctionnel Système d'accès voyageurs |                                         |     |  |  |

|---|-----------------------------|----------------------------------------------------------|-----------------------------------------|-----|--|--|

|   | 1 Le système accès voyageur |                                                          |                                         |     |  |  |

|   | 2                           | Choix                                                    | techniques et interfaces fonctionnelles | 131 |  |  |

|   |                             | 2.1                                                      | Porte                                   | 131 |  |  |

|   |                             | 2.2                                                      | Emmarchement mobile                     | 132 |  |  |

|   |                             | 2.3                                                      | Cabine/train                            | 132 |  |  |

Contents

| B | Notation table | 133 |

|---|----------------|-----|

|   |                |     |

#### Bibliography

137

## List of figures

| 1.1Two concurrent finite state machines121.2Synchronous product of two concurrent finite state machine M1, M2131.3finite state model of M1, M2, M3 machines141.4Product operation of finite state model for M1, M2, M3 machines141.5Sample-driven model of a FSM151.6Sample-driven to event-driven modeling171.7Environment of a block181.8Moore vs. Mealy FSM models201.9Product of communicating FSMs211.10CTL tree logic, [1]251.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framew | 1    | Erroneous COTS-based system                                       | 5  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------|----|

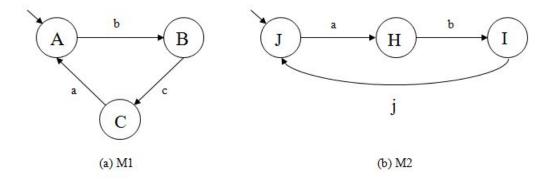

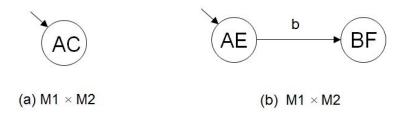

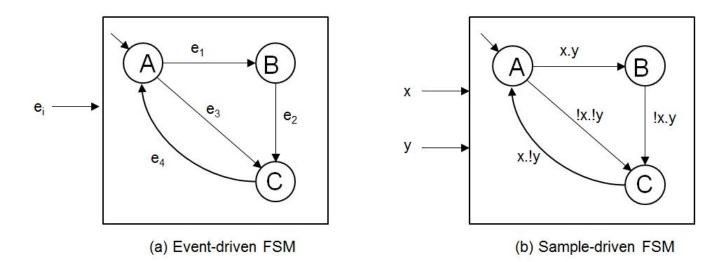

| 1.3finite state model of M1, M2, M3 machines141.4Product operation of finite state model for M1, M2, M3 machines141.5Sample-driven model of a FSM151.6Sample-driven to event-driven modeling171.7Environment of a block181.8Moore vs. Mealy FSM models201.9Product of communicating FSMs211.10CTL tree logic, [1]251.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design to be controlled using DCS351.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS basembly architectures562.5Circular reasoning for a COTS assembly612.6COTS interface before and after assembly612.7COTS assembly framework632.8Local assembly error652.9Local assembly error652.10Control architecture for ha                                     | 1.1  | Two concurrent finite state machines                              | 12 |

| 1.4Product operation of finite state model for M1, M2, M3 machines141.5Sample-driven model of a FSM151.6Sample-driven to event-driven modeling171.7Environment of a block181.8Moore vs. Mealy FSM models201.9Product of communicating FSMs211.10CTL tree logic, [1]251.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly612.7COTS assembly renticetures632.8Local asambly framework632.8Local asambly framework632.8Local assembly renticeture for hardware designs672.11Cottro architecture for hardware designs672.11Cottro architecture for hardware                                      | 1.2  | Synchronous product of two concurrent finite state machine M1, M2 | 13 |

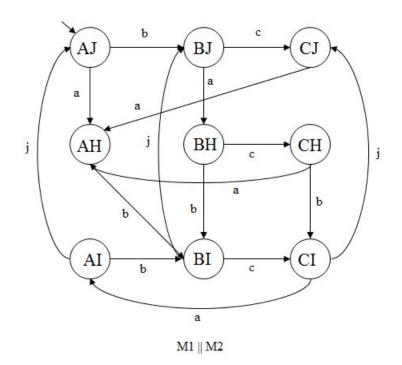

| 1.5Sample-driven model of a FSM151.6Sample-driven to event-driven modeling171.7Environment of a block181.8Moore vs. Mealy FSM models201.9Product of communicating FSMs211.10CTL tree logic, [1]251.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly612.7COTS assembly framework632.8Local assembly framework632.9Local assembly error642.9Local assembly error642.9Local assembly error642.9Local assembly error672.10Control architecture for hardware designs<                                                                         | 1.3  | finite state model of M1, M2, M3 machines                         | 14 |

| 1.6Sample-driven to event-driven modeling171.7Environment of a block181.8Moore vs. Mealy FSM models201.9Product of communicating FSMs211.10CTL tree logic, [1]251.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^e, Y^e$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.8Local assembly error652.9Cortrol architec                                     | 1.4  | Product operation of finite state model for M1, M2, M3 machines   | 14 |

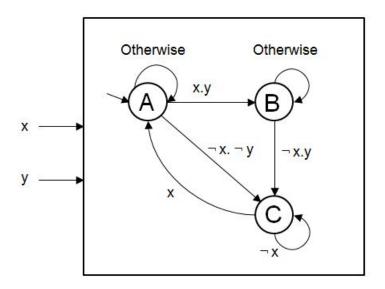

| 1.7Environment of a block181.8Moore vs. Mealy FSM models201.9Product of communicating FSMs211.10CTL tree logic, [1]251.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^e, Y^e$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly612.7COTS assembly framework632.8Local astand-alone error642.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs672.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design to be corrected using DCS<                                          | 1.5  | Sample-driven model of a FSM                                      | 15 |

| 1.8Moore vs. Mealy FSM models201.9Product of communicating FSMs211.10CTL tree logic, [1]251.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design to be corrected using DCS71                                                                                | 1.6  | Sample-driven to event-driven modeling                            | 17 |

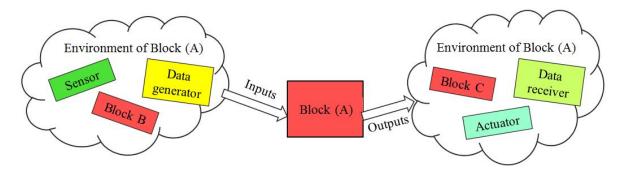

| 1.9Product of communicating FSMs211.10CTL tree logic, [1]251.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^e, Y^e$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs integrating environment assumptions6921Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                               | 1.7  | Environment of a block                                            | 18 |

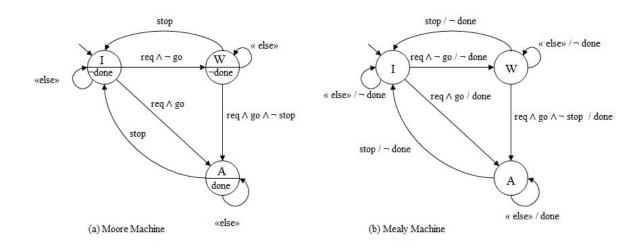

| 1.9Product of communicating FSMs211.10CTL tree logic, [1]251.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^e, Y^e$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs integrating environment assumptions6921Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                               | 1.8  | Moore vs. Mealy FSM models                                        | 20 |

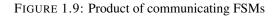

| 1.10CTL tree logic, [1]251.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^e, Y^e$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                  | 1.9  |                                                                   | 21 |

| 1.11Alternative occurrence of events271.12Control architecture for hardware designs341.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                        | 1.10 |                                                                   | 25 |

| 1.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local astand-alone error642.9Local assembly error652.10Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                               |      |                                                                   | 27 |

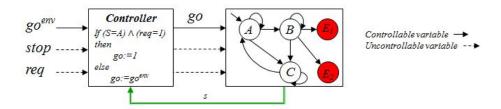

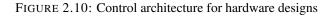

| 1.13A 5-states design to be controlled using DCS351.14A 5-states design assembled to the controller371.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local astand-alone error642.9Local assembly error652.10Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                               | 1.12 | Control architecture for hardware designs                         | 34 |

| 1.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                   | 1.13 | A 5-states design to be controlled using DCS                      | 35 |

| 1.15Composition environment of embedded systems based on EFSMs [2]401.16High-level generic processes for PORE method [3]411.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error652.10Control architecture for hardware designs integrating environment assumptions692.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS71                                                                                                                                                                                                                                                                                                              | 1.14 | A 5-states design assembled to the controller                     | 37 |

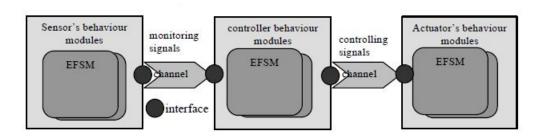

| 1.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | -                                                                 | 40 |

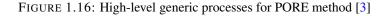

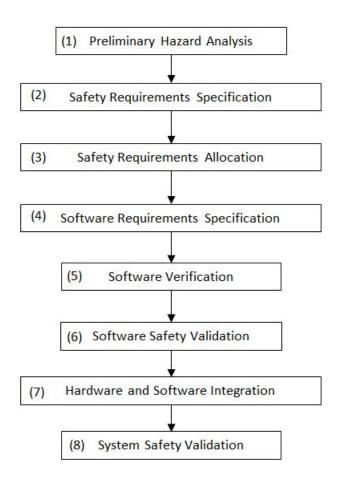

| 1.17Overview of the PORE's iterative process [3]411.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.16 | High-level generic processes for PORE method [3]                  | 41 |

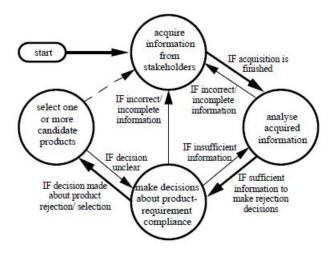

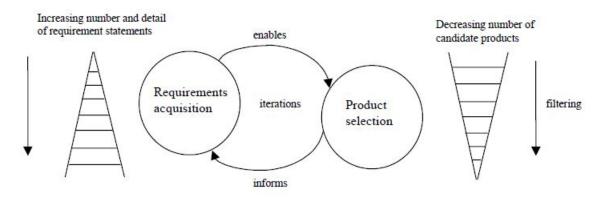

| 1.18System safety V and V for COTS based systems421.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                                                                   | 41 |

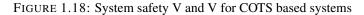

| 1.19Hierarchical definition for COTS evaluation criteria [5]432.1COTS-based control command system made of interacting blocks502.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.14A 5-states design to be corrected using DCS71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                                                                   | 42 |

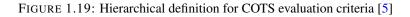

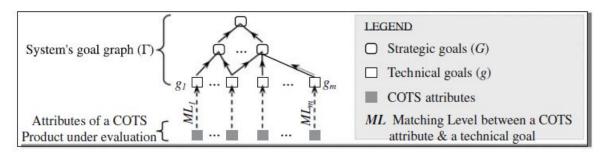

| 2.2Interface of a COTS represented by $X^c, Y^c$ 502.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                                                                   | 43 |

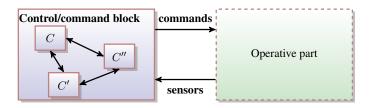

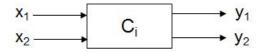

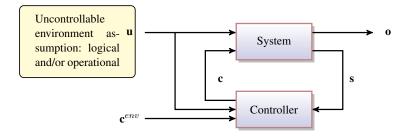

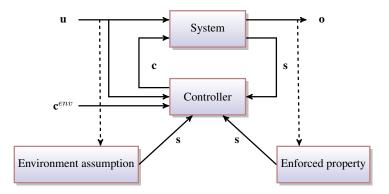

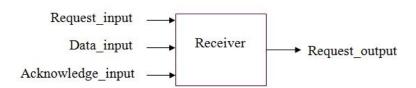

| 2.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.1  | COTS-based control command system made of interacting blocks      | 50 |

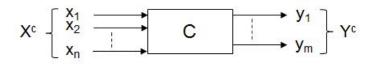

| 2.3COTS behavior532.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.2  | •                                                                 | 50 |

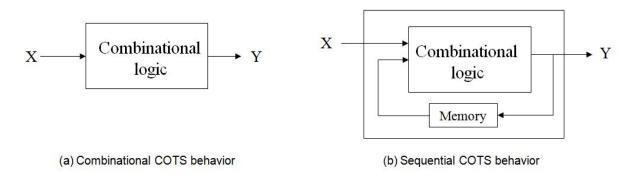

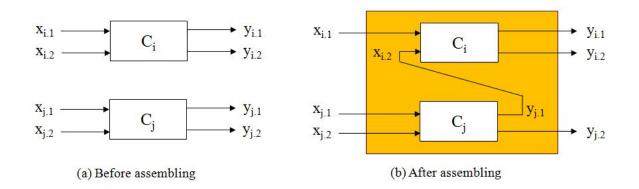

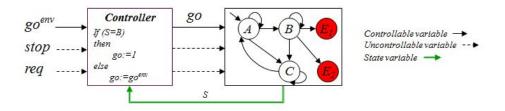

| 2.4Different COTS assembly architectures562.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.3  |                                                                   | 53 |

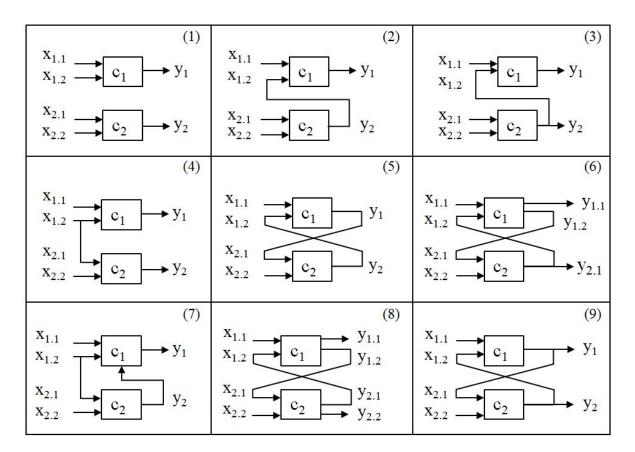

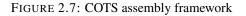

| 2.5Circular reasoning for a COTS assembly602.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.4  |                                                                   | 56 |

| 2.6COTS interface before and after assembly612.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.5  |                                                                   | 60 |

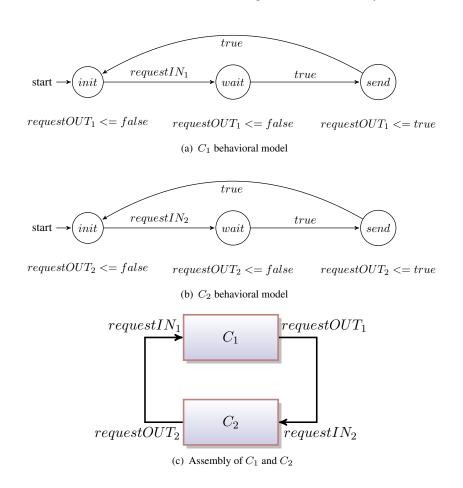

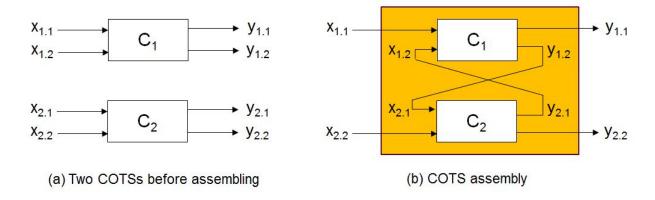

| 2.7COTS assembly framework632.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.6  | COTS interface before and after assembly                          | 61 |

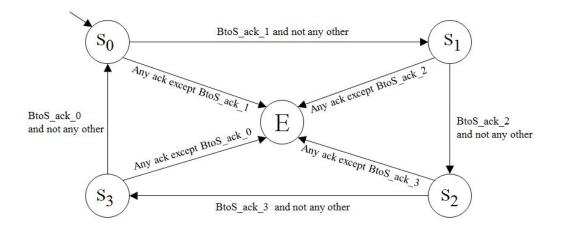

| 2.8Local stand-alone error642.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.7  |                                                                   | 63 |

| 2.9Local assembly error652.10Control architecture for hardware designs672.11Control architecture for hardware designs integrating environment assumptions692.12Environment monitor FSM B-> req712.13A 5-states design to be corrected using DCS712.14A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.8  |                                                                   | 64 |

| 2.11 Control architecture for hardware designs integrating environment assumptions692.12 Environment monitor FSM B-> req712.13 A 5-states design to be corrected using DCS712.14 A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.9  |                                                                   | 65 |

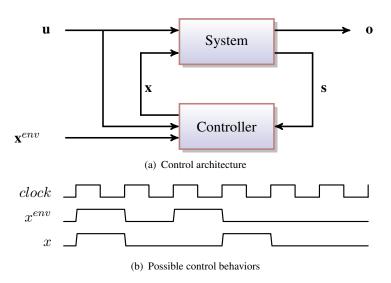

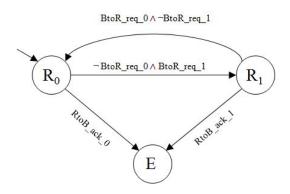

| 2.11 Control architecture for hardware designs integrating environment assumptions692.12 Environment monitor FSM B-> req712.13 A 5-states design to be corrected using DCS712.14 A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.10 | Control architecture for hardware designs                         | 67 |

| 2.12 Environment monitor FSM B-> req712.13 A 5-states design to be corrected using DCS712.14 A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                                                   | 69 |

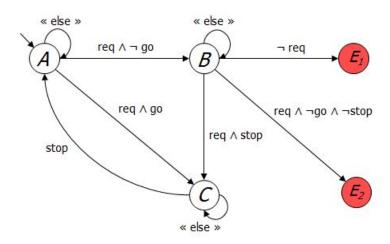

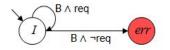

| 2.13 A 5-states design to be corrected using DCS712.14 A 5-states design assembled to the controller72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.12 |                                                                   | 71 |

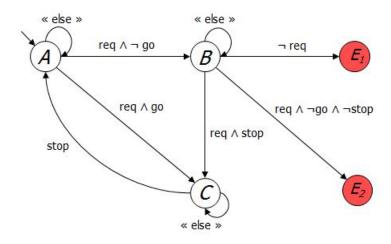

| 2.14 A 5-states design assembled to the controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                                                                   | 71 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                                                                   |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | The generic control architecture                                  | 73 |

| 2.16                                                                                                   | Hard reactive constraints for a controllable input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73                                                                              |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

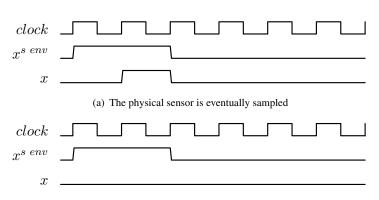

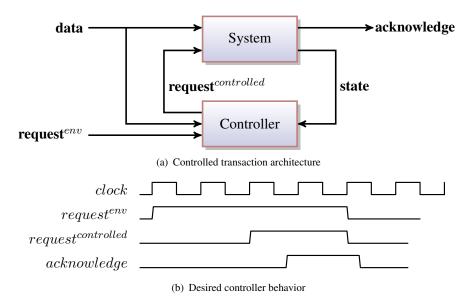

| 2.17                                                                                                   | Controlling transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74                                                                              |

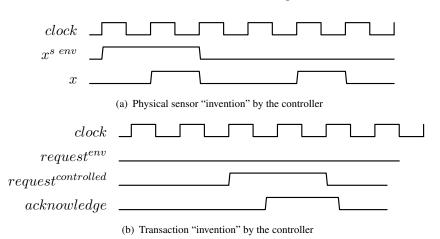

| 2.18                                                                                                   | The event "invention" phenomenon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76                                                                              |