# Etude des phénomènes de transport de porteurs et du bruit basse fréquence en fonction de la température dans les transistors MOSFETs nanométriques (FinFETs)

Rachida Talmat

#### ▶ To cite this version:

Rachida Talmat. Etude des phénomènes de transport de porteurs et du bruit basse fréquence en fonction de la température dans les transistors MOSFETs nanométriques (FinFETs). Electronique. université de caen, 2011. Français. NNT: . tel-01076455

## HAL Id: tel-01076455 https://hal.science/tel-01076455v1

Submitted on 22 Oct 2014

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITE de CAEN/BASSE-NORMANDIE

**U.F.R** Sciences

#### **ECOLE DOCTORALE SIMEM**

Cotutelle de thèse

entre

L'Université de Caen Basse-Normandie (France)

et

L'Université de Tizi-Ouzou (Algérie)

Arrêté du 6 janvier 2005

#### **THESE**

Présentée par

#### Melle Rachida TALMAT

En vue de l'obtention du

#### DOCTORAT de l'UNIVERSITE de CAEN

Spécialité : Electronique, Microélectronique et Nanoélectronique

Arrêté du 7 août 2006

Etude des phénomènes de transport de porteurs et du bruit basse fréquence en fonction de la température dans les transistors MOSFETs nanométriques (FinFETs)

## soutenue le 29/11/2011

#### MEMBRES du JURY

| Mr Djamel BENNAZOUZ   | Professeur   | Université de Boumerdès              | (Rapporteur)           |

|-----------------------|--------------|--------------------------------------|------------------------|

| Mr Alain HOFFMANN     | Professeur   | Université de Montpellier 2          | (Rapporteur)           |

| Mr Fayçal RAHMOUNE    | Docteur (HDR | ) Université de Boumerdès            | (Examinateur)          |

| Mr Jean-Marc ROUTOURE | Professeur   | Université de Caen Basse-Normandie   | (Examinateur)          |

| Mr Arezki BENFDILA    | Professeur   | Université de Tizi-Ouzou             | (Codirecteur de thèse) |

| Mr Régis CARIN        | Professeur   | Université de Caen Basse-Normandie ( | (Codirecteur de thèse) |

# Etude des phénomènes de transport de porteurs et du bruit basse fréquence en fonction de la température dans les transistors MOSFETs nanométriques (FinFETs)

Au cours de cette thèse, des mesures en régime statique et en bruit ont été effectuées sur des transistors FinFETs réalisés sur substrat SOI, issus de la technologie 32 nm, ayant deux différents isolants de grille. L'un est l'oxyde d'hafnium (HfO<sub>2</sub>) et le second est le silicate d'hafnium nitruré (HfSiON). La plupart de ces dispositifs ont subi des techniques de contrainte mécanique locales et globales. Les résultats de mesures en statique ont montré l'amélioration considérable des performances dans les transistors contraints par rapport aux transistors standards. Il a été montré que ces transistors contraints semblent être moins sensibles à la variation de la température (300 K - 475 K) indiquant un autre atout de l'ingénierie des contraintes. Les résultats de mesures de bruit ont permis d'évaluer la qualité de l'isolant de ces dispositifs, le silicate d'hafnium nitruré semble avoir une meilleure qualité. L'étude du bruit a permis aussi d'apporter des informations sur le transport ainsi que sur les mécanismes physiques qui génèrent le bruit en 1/f dans ces dispositifs. On n'a remarqué aucun impact significatif des contraintes mécaniques sur le niveau du bruit. Le mécanisme qui prédomine dans ces dispositifs est le mécanisme des fluctuations de nombre de porteurs dans les type n et type p. Les mesures de bruit en fonction de la température (100 K – 300 K) ont permis d'identifier des défauts, souvent liés à la technologie de fabrication, dans le film de silicium par la méthode de spectroscopie de bruit.

# Study of carriers transport phenomena and low frequency noise as a function of temperature in nanometric MOSFETs transistors (FinFETs).

In this thesis, DC measurement and noise were performed on FinFETs on silicon on insulator substrate (SOI) processed in 32 nm technologies, with two different gate dielectrics; hafnium oxide (HfO<sub>2</sub>) and nitrided hafnium silicate (HfSiON). Most of these devices have undergone local and global mechanical strain. The results of static measurements have shown an improvement of the performances. Temperature measurements (300 K – 475 K) showed that strained devices seem to be less sensitive to the temperature variation than standard ones, indicating an additional benefit of strain engineering. The noise measurements were used to evaluate the quality of the gate oxide of these devices, the nitrided hafnium silicate seems to have a better quality. The study of noise has also provided information about the transport and physical mechanisms that generate the 1/f noise in these devices. One can notice that there is no significant impact of strain on the 1/f noise level. The carrier number fluctuations dominate the 1/f noise for all studied devices. Noise measurements as a function of temperature (100 K - 300 K) allowed to identify defects in the silicon film, often associated to the technological process, by noise spectroscopy method.

MOTS-CLES: Transistor MOSFET, technologie silicium sur isolant, bruit électronique, semiconducteurs\_défauts

**DISCIPLINE**: Electronique, microélectronique et nanoélectronique

LABORATOIRE: GREYC UMR 6072 (Université de Caen-ENSICAEN-CNRS), Equipe Electronique

# Table des matières

| Introduction générale                                                                  |       |

|----------------------------------------------------------------------------------------|-------|

| Chapitre 1 : Le transistor MOSFET                                                      | 13    |

| 1.1 Introduction                                                                       | 13    |

| 1.2 Transistor MOSFET                                                                  | 14    |

| 1.2.1 Principe de base d'un transistor MOSFET                                          | 15    |

| 1.2.1.1 Effet de champ                                                                 | 15    |

| 1.2.1.2 Régimes de fonctionnement                                                      | 15    |

| 1.2.1.3 Potentiel de bandes plates                                                     | 17    |

| 1.2.1.4 Tension de seuil                                                               | 17    |

| 1.2.1.5 Pente sous le seuil                                                            | 18    |

| 1.2.1.6 Courants I <sub>OFF</sub> et I <sub>ON</sub>                                   | 18    |

| 1.2.2 Modélisation d'un transistor MOSFET classique                                    | 19    |

| 1.2.2.1 Régime linéaire                                                                | 19    |

| 1.2.2.2 Régime de saturation                                                           | 21    |

| 1.2.3 Mobilité de porteurs de charge                                                   | 22    |

| 1.2.3.1 Collisions avec les phonons                                                    | 22    |

| 1.2.3.2 Collisions sur les centres coulombiens                                         | 23    |

| 1.2.3.3 Collisions sur la rugosité de surface                                          | 23    |

| 1.2.3.4 Combinaison des trois mécanismes de collisions                                 | 23    |

| 1.3 Effets de miniaturisation                                                          | 24    |

| 1.3.1 Loi de Moore et de réduction d'échelle                                           | 24    |

| 1.3.2 Nouveaux phénomènes physiques engendrés par la miniaturisation                   | 25    |

| 1.3.2.1 Effets quantiques de confinement                                               | 26    |

| 1.3.2.2 Saturation de la vitesse des porteurs                                          | 26    |

| 1.3.2.3 Transport balistique et quasi balistique                                       | 26    |

| 1.3.2.4 Effet tunnel                                                                   | 28    |

| 1.3.2.5 Effets de canaux courts                                                        | 28    |

| 1.4 Solutions technologiques                                                           | 29    |

| 1.4.1 Transistor MOSFET SOI                                                            | 29    |

| 1.4.2 Utilisation d'empilements avec isolant à haute permittivité et grille métallique | լսе30 |

| 1.4.3 Amélioration du transport de charge dans le canal                                | 31    |

| 1.4.3.1 L'orientation cristalline du canal ou du substrat                              | 31    |

| 1.4.3.2 L'ingénierie de contraintes mécaniques                           | 32              |

|--------------------------------------------------------------------------|-----------------|

| 1.4.3.3 Silicium sur isolant contraint (sSOI)                            | 32              |

| 1.4.3.4 Couche d'arrêt à la gravure (CESL)                               | 33              |

| 1.4.3.5 Croissance épitaxiale sélective (SEG)                            | 33              |

| 1.4.4 MOSFET à grilles multiples                                         | 34              |

| 1.4.5 Au delà du MOSFET classique                                        | 35              |

| 1.5 Le transistor FinFET                                                 | 35              |

| 1.6 Conclusion                                                           | 37              |

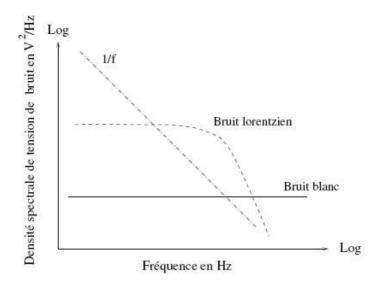

| Chapitre 2 : Etude du bruit basse fréquence                              | 39              |

| 2.1 Introduction                                                         | 39              |

| 2.2 Généralités sur le bruit basse fréquence                             | 40              |

| 2.3 Le bruit basse fréquence dans les transistors MOSFETs                | 41              |

| 2.3.1 Le bruit blanc                                                     | 42              |

| 2.3.1.1 Le bruit thermique                                               | 42              |

| 2.3.1.2 Le bruit de grenaille « Shot noise »                             | 43              |

| 2.3.2 Le bruit en 1/f <sup>9</sup> « Flicker noise »                     | 43              |

| 2.3.2.1 Fluctuations du nombre de porteurs ( $\Delta N$ )                | 43              |

| 2.3.2.2 Fluctuation de mobilité corrélée à une fluctuation du nomb       | ore de porteurs |

| $(\Delta N + \Delta \mu)$                                                | 46              |

| 2.3.2.3 Fluctuations de la mobilité des porteurs $(\Delta \mu)$          | 46              |

| 2.3.2.4 Bruit en 1/f dû aux résistances d'accès                          | 47              |

| 2.3.2.5 Synthèse sur le bruit en 1/f                                     | 48              |

| 2.3.3 Bruit lorentzien                                                   | 49              |

| 2.3.3.1 Lorentziennes dues aux défauts                                   | 49              |

| 2.3.3.2 Lorentziennes dues à une source de bruit blanc associée à un rés | eau réactif53   |

| 2.3.3.3 Le bruit RTS (Random Telegraph Signal)                           | 53              |

| 2.4 Principe de mesure du bruit                                          | 54              |

| 2.4.1 Banc de caractérisation du bruit                                   | 55              |

| 2.4.2 Incertitude de mesure                                              | 56              |

| 2.4.3 Extraction de paramètres du bruit                                  | 57              |

| 2.5 Mesures et extractions statiques                                     | 57              |

| 2.5.1 Mesures en statique                                                | 57              |

| 2.5.2 La méthode de la fonction Y                                        | 58              |

| 2.6 Le bruit dans les FinFFTs                                            | 60              |

| 2.7 Conclusion                                                           | 63              |

|--------------------------------------------------------------------------|-----------------|

| Chapitre 3 : Mesures en statique et en bruit basse fréqu                 | ence dans les   |

| pFinFETs avec HfO <sub>2</sub>                                           | 65              |

| 3.1 Introduction                                                         | 65              |

| 3.2 Description des transistors étudiés                                  | 66              |

| 3.3 Mesures en statique                                                  | 66              |

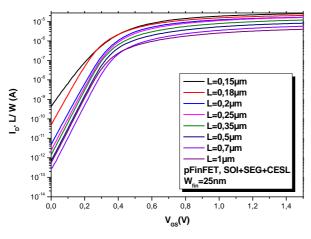

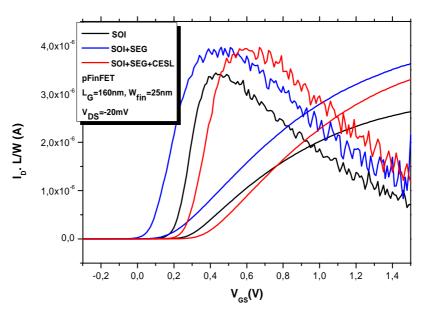

| 3.3.1 Mesures en fonction de la longueur et pour différentes structures  | ;6 <del>6</del> |

| 3.3.2 Extraction des paramètres principaux du transistor                 | 68              |

| 3.4 Mesures de bruit basse fréquence                                     | 70              |

| 3.4.1 Mesures à température ambiante                                     | 70              |

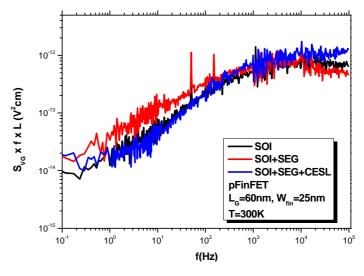

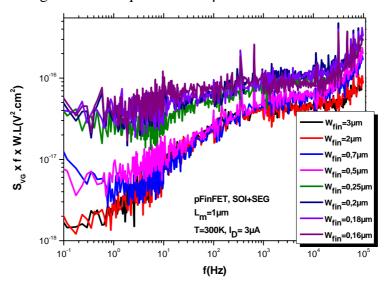

| 3.4.1.1 Observation de bruit inhabituel                                  | 70              |

| 3.4.1.2 Mesures de bruit en fonction de la géométrie                     | 72              |

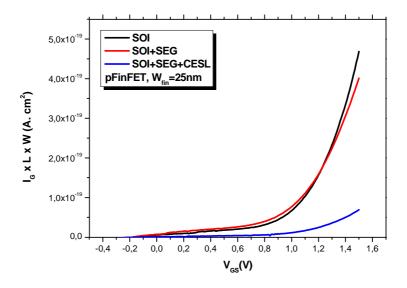

| 3.4.1.3 Qualité de l'oxyde de grille                                     | 75              |

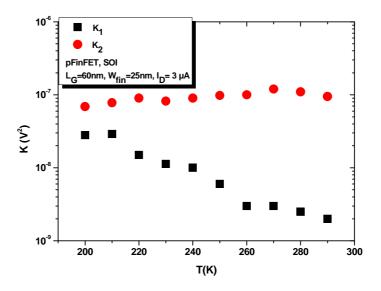

| 3.4.2 Mesure en bruit basse fréquence en fonction de la température      | 77              |

| 3.4.2.1 Mesures entre 200 K et 300 K                                     | 77              |

| 3.4.2.2 Mesures à une température de 80 K                                | 78              |

| 3.5 Conclusion                                                           | 80              |

| Chapitre 4 : Mesures en statique et en bruit basse fréqu                 | ence dans les   |

| FinFETs avec HfSiON                                                      | 81              |

| 4.1 Introduction                                                         | 81              |

| 4.2 Description des transistors étudiés                                  | 82              |

| 4.3 Etude en statique des nFinFETs à température ambiante et à hautes to | empératures82   |

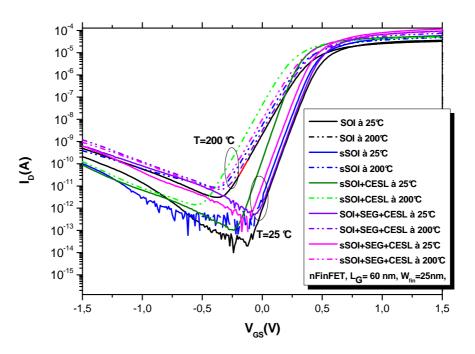

| 4.3.1 Résultats des mesures                                              | 83              |

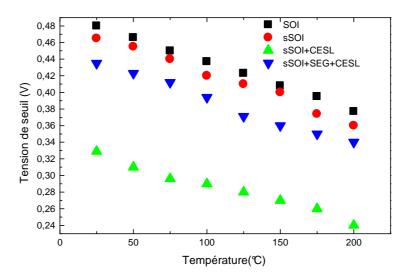

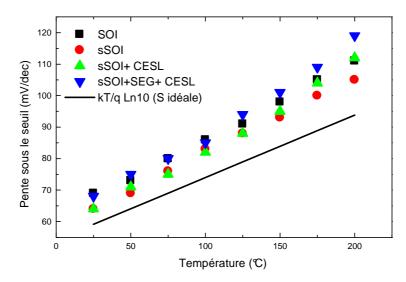

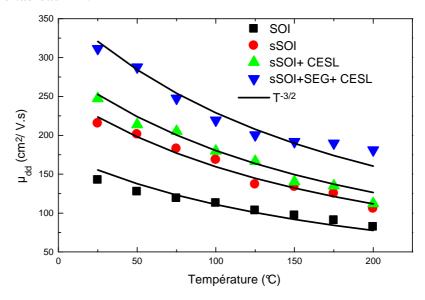

| 4.3.2 Variations avec la température des principaux paramètres           | 84              |

| 4.3.2.1 La tension de seuil                                              | 84              |

| 4.3.2.2 La pente sous le seuil                                           | 86              |

| 4.3.2.3 La mobilité                                                      | 87              |

| 4.3.2.4 Résistances d'accès                                              | 88              |

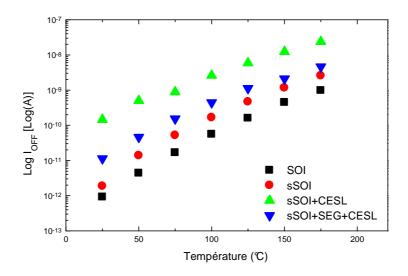

| 4.3.2.5 Le courant sous le seuil                                         | 88              |

| 4.3.2.6 « Zero temperature coefficient »                                 | 89              |

| 4.3.3 Conclusion partielle                                               | 90              |

| 4.4 Mesures du bruit basse fréquence des nFinFETs                        | 91              |

| 4.4.1 Mesures du bruit basse fréquence à température ambiante            | 91              |

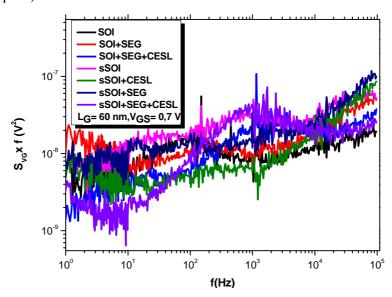

| 4.4.1.1 Le bruit basse fréquence observé dans les nFinFETs                         | 91           |

|------------------------------------------------------------------------------------|--------------|

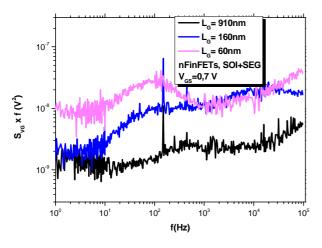

| 4.4.1.2 Bruit en 1/f observé dans les nFinFETs (effet longueur et nombre de        | doigts).92   |

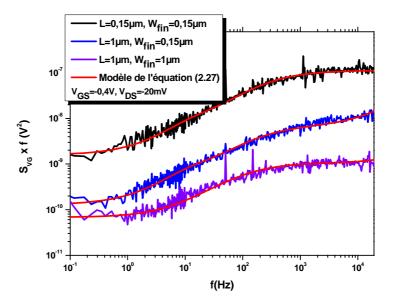

| 4.4.2 Bruit en 1/f des nFinFETs à température ambiante                             | 93           |

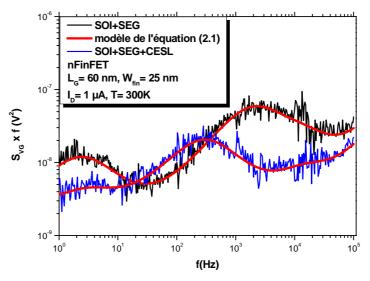

| 4.4.2.1 Modélisation du bruit en 1/f observé                                       | 93           |

| 4.4.2.2 Conclusion partielle                                                       | 94           |

| 4.4.3 Exploitation du bruit en 1/f des nFinFETs à température ambiante             | et à des     |

| températures plus basses                                                           | 95           |

| 4.4.3.1 Evolution avec la température du bruit en 1/f des nFinFETs                 | 95           |

| 4.4.3.2 Qualité de l'oxyde de grille déduite du bruit en 1/f                       | 96           |

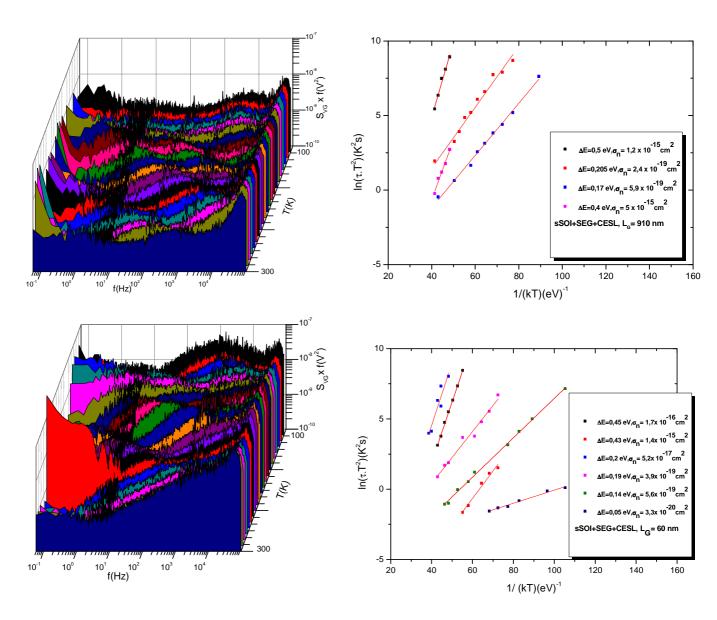

| 4.4.4 Mesures de bruit en fonction de la température : étude des lorentziennes     | 97           |

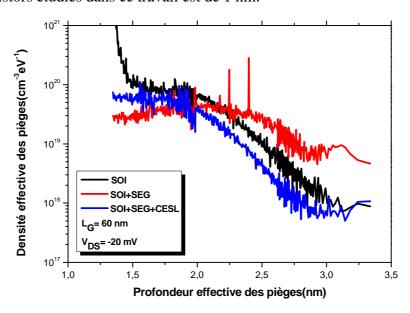

| 4.4.4.1 Identification des défauts dans la zone de déplétion                       | 97           |

| 4.4.4.2 Synthèse des défauts trouvés                                               | 100          |

| 4.4.4.3 Densités de pièges des défauts identifiés                                  | 104          |

| 4.4.5 Conclusion partielle                                                         | 105          |

| 4.5 Mesures de bruit basse fréquence dans les pFinFETs                             | 106          |

| 4.5.1 Bruit mesuré dans les pFinFETs                                               | 106          |

| 4.5.2 Mesures de bruit en fonction de la géométrie                                 | 107          |

| 4.5.3 Qualité de l'oxyde de grille                                                 | 108          |

| 4.5.4 Conclusion partielle                                                         | 109          |

| Chapitre 5 : Synthèse                                                              | 111          |

| 5.1 Discussion de l'effet de la contrainte sur les résultats en régime de fonct    | ionnemen     |

| statique                                                                           | 112          |

| 5.2 Bruit inhabituel                                                               | 112          |

| 5.3 Présence importante de lorentziennes dans les spectres de bruit des transistor | s FinFETs    |

| à HfSiON                                                                           | 112          |

| 5.4 Bruit en 1/f dans les transistors FinFETs à HfSiON                             | 114          |

| 5.5 Cas particulier du transistor FinFET à un seul doigt : bruit RTS               | 114          |

| 5.6 Comparaison de l'incidence des deux isolants de grille HfO2 et HfSiON sur      | · la qualité |

| des transistors FinFETs                                                            | 114          |

| 5.7 Comparaison des résultats obtenus entre les transistors FinFETs de type n et p | )11 <i>6</i> |

| 5.8 Identification des défauts par spectroscopie de bruit                          | 116          |

| Conclusion Générale                                                                | 117          |

| Liste des publications issues de cette thèse                                       | 110          |

| Annexe: Résultats des mesures de bruit basse fré | quence en fonction de |

|--------------------------------------------------|-----------------------|

| la température                                   | 121                   |

| Notations                                        | 129                   |

| Acronymes                                        | 134                   |

| Liste des figures                                | 135                   |

| Liste des tableaux                               | 136                   |

| Références                                       | 137                   |

### Introduction générale

L'intégration du transistor MOSFET n'a pas cessé d'évoluer depuis plus d'un demi-siècle vers des tailles nanométriques. La réduction de la longueur de grille a permis d'augmenter la densité d'intégration des transistors sur une puce et d'améliorer la rapidité des circuits suivant la fameuse loi de Moore qui prédit que le nombre de transistors doublerait tous les 2 ans. Ceci augmente donc les opérations de plus en plus complexes tout en augmentant la fréquence de fonctionnement. La réduction des dimensions induit l'émergence des effets parasites tels que les effets de canaux courts ainsi que les effets liés à la mécanique quantique qui tendent à modifier les caractéristiques électriques du transistor MOSFET. Avec la réduction du canal, l'épaisseur de l'oxyde de grille doit être réduite pour maintenir le contrôle de la grille or ceci engendre un courant de fuite tunnel à travers ce dernier. A de telles dimensions, le bruit basse fréquence peut devenir un problème dans les applications analogiques et digitales car plus le transistor est rapide, plus le bruit est élevé. Toutefois, le bruit basse fréquence peut être utilisé comme un outil de caractérisation non destructif de la qualité de l'oxyde de grille et permet d'évaluer l'impact des étapes technologiques sur ce dernier.

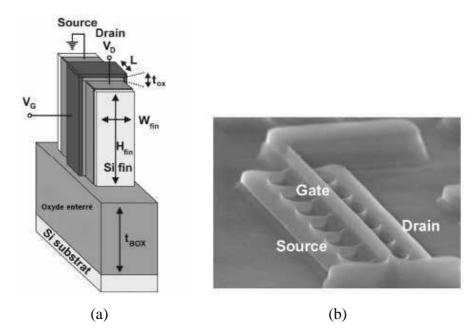

L'intégration continue du transistor MOSFET conventionnel requiert de nouvelles innovations pour contrecarrer ces limites physiques obligeant les chercheurs à trouver des solutions pour pouvoir réaliser des transistors toujours performants. Afin de réduire les effets néfastes dus à la miniaturisation des transistors MOSFETs, plusieurs solutions ont été utilisées dans les technologies les plus avancées pour améliorer les performances du transistor. Parmi ces innovations, on peut citer l'utilisation de nouveaux oxydes de grille à haute permittivité (high-k) pour réduire le courant de grille, l'utilisation de l'ingénierie de contrainte pour améliorer les propriétés du transport des porteurs de charge, la conception de nouvelles architectures telles que les transistors multigrilles pour améliorer le contrôle électrostatique, etc. Parmi les transistors multigrilles figure le transistor FinFET qui est un transistor MOSFET 3D, il est considéré comme un candidat prometteur pour l'ère du nanomètre des circuits intégrés CMOS. Le transistor FinFET a été mis en production par Intel pour le nœud technologique 22 nm au cours de l'année 2011.

Afin de quantifier les avantages et inconvénients de ces nouveaux dispositifs, il est indispensable de pouvoir les caractériser électriquement en statique et en bruit et de modéliser le comportement de leurs paramètres électriques avec la réduction des dimensions.

Au cours de cette thèse, des mesures en régime statique et en bruit ont été effectuées sur des transistors FinFETs réalisés sur substrat SOI ayant deux différents isolants de grille. L'un est l'oxyde d'hafnium (HfO<sub>2</sub>) et le second est le silicate d'hafnium nitruré (HfSiON). La plupart de ces dispositifs ont subi des techniques de contrainte mécanique locales et globales. Les résultats de

mesures en statique ont montré l'amélioration considérable de la mobilité obtenue dans les transistors contraints par rapport aux standards et que l'utilisation des techniques de contrainte attenue la variation du courant liée à l'élévation de la température.

Les résultats de mesures en bruit ont permis d'évaluer la qualité de l'isolant de ces dispositifs, le silicate d'hafnium nitruré semble avoir une meilleure qualité. L'étude du bruit a permis aussi d'apporter des informations sur le transport ainsi que les mécanismes physiques qui génèrent le bruit en 1/f dans ces dispositifs. On n'a remarqué aucun impact des contraintes mécaniques sur le niveau du bruit. Les mesures de bruit en fonction de la température ont permis d'identifier des défauts dans le film du silicium par la méthode de spectroscopie en bruit.

L'articulation du mémoire de thèse est la suivante.

Dans le premier chapitre, on présentera le transistor MOSFET conventionnel et son évolution vers de nouvelles architectures innovantes. Dans un premier temps, le fonctionnement du transistor MOSFET, ses paramètres électriques importants, les effets de miniaturisation des dispositifs et leurs limites ainsi que les diverses solutions technologiques qui ont été utilisées pour améliorer les performances du transistor à canal court seront présentés. Plus particulièrement, une description des transistors FinFETs sera faite, objet d'étude en statique et en bruit de ce travail de thèse.

Le second chapitre s'attache au bruit basse fréquence dans les transistors MOSFETs et au dispositif expérimental de mesure. Dans un premier temps, les origines des différents types de bruit ainsi que leurs modèles seront décrits. Dans la dernière partie du chapitre, une description du banc expérimental de mesure en bruit et en régime statique de fonctionnement sera donnée.

Le troisième chapitre concerne les transistors FinFETs avec l'oxyde d'hafnium (HfO<sub>2</sub>). Les transistors de type n ont fait l'objet d'une étude antérieure. On décrit ici les résultats de mesures en régime statique de fonctionnement et en bruit des transistors pFinFETs avec l'oxyde d'hafnium ayant des structures standards et contraintes. Les mesures en bruit ont été faites à température ambiante et à une température de 80 K. Un bruit inhabituel a été mis en évidence dans tous les transistors étudiés à température ambiante.

Dans le quatrième chapitre, les résultats de mesures en régime statique de fonctionnement et en bruit basse fréquence sur des transistors FinFETs standards et contraints ayant le silicate d'Hafnium nitruré (HfSiON) seront présentés. D'une part, afin d'étudier les performances de ces transistors, des mesures en statique ont été faites à température ambiante et à hautes températures afin d'extraire les principaux paramètres du transistor et leurs variations en fonction de la température. D'autre part, des mesures de bruit basse fréquence ont été effectuées pour étudier la qualité de l'oxyde de grille et son impact sur les performances en bruit, à température ambiante et à

basse température. Ces dernières mesures ont permis de mettre en évidence des défauts dans la zone déplétion de ces transistors.

Finalement, dans un chapitre plus court, une synthèse de tous les résultats trouvés dans les transistors pFinFETs ayant HfO<sub>2</sub> et les transistors FinFETs ayant HfSiON sera discutée, permettant de conclure sur une comparaison de la qualité des deux oxydes et du niveau du bruit entre les divers transistors.

# Chapitre 1 : Le transistor MOSFET

#### 1.1 Introduction

Dans ce chapitre, nous allons présenter le transistor MOSFET conventionnel et son évolution vers de nouvelles architectures innovantes. Dans un premier temps, le fonctionnement du MOSFET, ses paramètres électriques importants ainsi que les effets de miniaturisation des dispositifs et leurs limites sont présentés. Les diverses solutions technologiques qui ont été utilisées pour améliorer les performances du transistor à canal court telle que l'ingénierie de contrainte, architectures multigrilles sont décrites. Il en suivra une description des transistors FinFETs, objet d'étude en statique et en bruit de ce travail de thèse.

#### 1.2 Transistor MOSFET

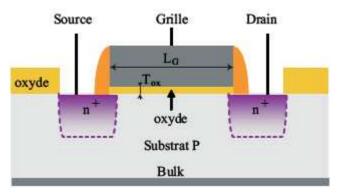

Le transistor MOSFET est le dispositif le plus répandu dans la production actuelle de composants semi-conducteurs, il est le composant de base de tout circuit intégré CMOS (Complementary Metal Oxide Semiconductor). La technologie CMOS est basée sur l'utilisation de deux types de transistors complémentaires: le transistor nMOSFET dont les porteurs sont des électrons et le transistor pMOSFET dont les porteurs sont des trous. Elle englobe plus de 80 % de la production mondiale de circuits intégrés, grâce aux qualités de faible consommation et de faible taille. Le principe de fonctionnement d'un transistor MOSFET (Metal Oxide Semiconductor Field Effet Transistor) est basé sur le concept de la modulation de la conductivité des matériaux mise en évidence par J. E. Lilienfeld en 1928 [1]. Il n'a cependant pu être exploité qu'à partir des années 60, lorsque des interfaces silicium/oxyde ont été suffisamment de bonne qualité et que Jack Kilby ait fabriqué le premier circuit intégré [2]. Le transistor MOSFET à enrichissement, qui est représenté sur la figure 1-1, se caractérise par le fait que la grille, par l'effet de champ électrique, contrôle à travers l'oxyde de grille, la densité de porteurs dans le canal du dispositif et ainsi l'intensité du courant. Le canal est relié de part et d'autre à deux régions fortement dopées entre lesquelles est appliquée une tension donnant lieu à la circulation du courant.

Le transistor MOSFET est utilisé dans de multiples applications. Il est utilisé comme amplificateur dans certaines applications analogiques. Il est aussi utilisé comme bit pour stocker et lire l'information sous forme de zéros et uns. Son utilisation est plus importante dans les applications numériques comme élément de base de différentes fonctions logiques (porte AND, OR,..). On peut distinguer deux catégories importantes d'applications :

- applications haute performance HP (« *High Performance* ») comme le microprocesseur pour les ordinateurs de bureau pour lesquelles la fréquence de commutation du transistor est privilégiée par rapport à la consommation.

- applications à basse consommation avec un compromis sur la fréquence de commutation du transistor :

- Les dispositifs à faible puissance active LOP (« Low Operating Power »), ce sont des dispositifs à basse consommation en fonctionnement tels que les ordinateurs portables.

- Les dispositifs à faible puissance statique LSTP (« Low STandby Power»); ce sont des dispositifs nécessitant un faible courant de repos (lorsque le transistor est bloqué) pour obtenir une meilleure autonomie tels que les téléphones portables.

#### 1.2.1 Principe de base d'un transistor MOSFET

#### 1.2.1.1 Effet de champ

Le principe de fonctionnement d'un transistor MOSFET repose sur l'effet de champ, qui consiste à moduler de façon électrostatique une densité de charges mobiles dans un semi-conducteur. La modulation est provoquée par un champ électrique perpendiculaire à la direction du mouvement de ces charges. La structure se décompose en trois parties principales : l'électrode de grille (G) qui commande l'intensité du champ électrique vertical et par conséquent la densité de charges mobiles, les électrodes de source (S) et de drain (D) séparées par un canal de conduction qui conduit le courant en fonction de son niveau de remplissage en charges mobiles [3] . Dans tout ce qui suit le transistor est considéré de type n.

Figure 1-1: Représentation schématique d'un transistor MOSFET.

La grille est polarisée par la tension grille-source  $V_{GS}$ . Les charges sont mises en mouvement par l'intermédiaire du champ électrique longitudinal lié à l'application d'une tension entre le drain et la source  $V_{DS}$ . La source sert de référence de potentiel. Les tensions  $V_{GS}$  et  $V_{DS}$  permettent de contrôler le courant qui passe dans le canal. Le dopage du canal  $N_A$ , la profondeur  $X_j$  des jonctions source et drain, la longueur de masque L entre drain et source, la largeur de masque L et l'épaisseur  $L_{CS}$  de l'oxyde de grille sont les paramètres caractéristiques d'un transistor MOSFET conventionnel. Avec la réduction de la taille du transistor, la différence entre la longueur du masque L et la longueur effective  $L_E$  n'est plus négligeable. De même pour la largeur effective du canal  $L_{CS}$  Deux paramètres correctifs sont alors introduits. Ils sont définis par :  $L_{CS}$  et  $L_{CS}$  et L

#### 1.2.1.2 Régimes de fonctionnement

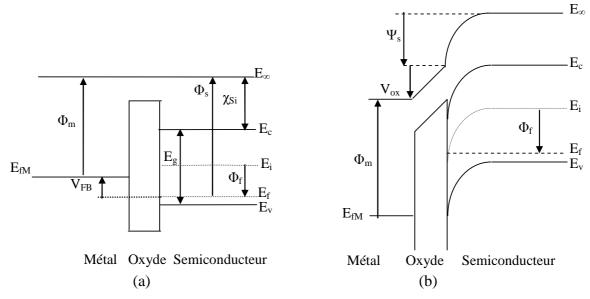

L'application d'un potentiel électrique sur la grille modifie les courbures de bandes d'énergie du semiconducteur. La figure 1-2 représente un diagramme de bande d'énergie d'un transistor nMOSFET dans le régime des bandes plates et dans le régime de faible inversion.

Figure 1-2 : Diagramme de bande d'un transistor nMOSFET en régime de bandes plates (a) et en régime de faible inversion (b),  $\chi_{Si}$  est l'affinité électronique,  $E_g$  est la largeur de la bande interdite.  $E_c$ ,  $E_v$ ,  $E_i$  sont les énergies de bas de la bande de conduction, haut de la bande de valence et l'énergie intrinsèque du silicium.  $\Phi_m$ ,  $\Phi_s$  sont les travaux de sortie du métal et du semiconducteur,  $\Phi_f$  est le potentiel de Fermi.  $\Psi_s$  est la différence de potentiel entre la surface et le volume (le potentiel de surface).

Le niveau de Fermi est donné par :  $E_F = E_i - q\Phi_f$ , le potentiel de Fermi  $\Phi_f$  est donné par l'équation suivante dans le cas d'un dopage modéré :

$$\Phi_f = \frac{kT}{q} \cdot \ln \frac{N_A}{n_i} \tag{1.1}$$

k est la constante de Boltzmann, T est la température, q est la charge élémentaire et  $n_i$  est la concentration intrinsèque de porteurs dans le matériau.

En fonction de la polarisation de la grille, on distingue différents régimes, séparés par deux valeurs, celle de la tension de bandes plates  $V_{FB}$  ( $\Psi_s=0$ ) et celle de la tension de seuil  $V_{Th}$  ( $\Psi_s=2~\Phi_f$ ):

- régime d'accumulation ( $\Psi_s$  < 0,  $V_{GS}$  <  $V_{FB}$ ): dans ce cas, les porteurs majoritaires (trous) sont attirés à l'interface oxyde/semiconducteur. Ils y sont encore plus nombreux que dans le volume.

- régime de déplétion  $(0 < \Psi_s < \Phi_f, V_{Th} < V_{GS} < V_{FB})$ : dans ce cas, les porteurs majoritaires (trous) sont repoussés de l'interface. Il se crée ainsi une zone de charge d'espace, chargée par les impuretés ionisées fixes (dopants, accepteurs) et désertée en porteurs mobiles.

- régime d'inversion faible  $(\Phi_f < \Psi_s < 2\Phi_f, V_{FB} > V_{GS} > V_{Th})$ : Lorsque  $\Psi_s = \Phi_f$ , les concentrations des porteurs majoritaires et minoritaires sont égales en surface, donc égale à la valeur de la concentration  $n_i$ .

• régime d'inversion forte ( $\Psi_s > 2\Phi_{f,} \ V_{GS} > V_{Th}$ ): la concentration des porteurs minoritaires en surface devient supérieure à la concentration des porteurs majoritaires dans le volume du semiconducteur.

#### 1.2.1.3 Potentiel de bandes plates

Les structures MOS ont des oxydes contenant des charges fixes distribuées, de sorte que même si  $V_{GS}=0$ , il y a toujours une courbure de bande à la surface du semi-conducteur. En général, ces charges d'origines technologiques sont positives (Na<sup>+</sup>, K<sup>+</sup>,...). La valeur de la tension  $V_{GS}$  qu'il faut appliquer pour contrecarrer l'effet de ces charges s'appelle la tension de bande plate  $V_{FB}$ . L'équation de continuité des potentiels s'écrit alors:

$$V_{GS} = V_{FB} + \Psi_s - \frac{Q_{sc}}{C_{ox}} \tag{1.2}$$

$Q_{sc}$  est la charge du semiconducteur.  $C_{ox}$  est la capacité de l'oxyde de grille, elle est donnée par :

$$C_{ox} = \frac{\mathcal{E}_0 \mathcal{E}_{ox}}{T_{ox}} \tag{1.3}$$

$\varepsilon_{ox}$ ,  $\varepsilon_0$  sont respectivement la permittivité relative de l'oxyde et la permittivité du vide. La tension  $V_{FB}$  est non seulement reliée à la densité de charges dans l'oxyde  $Q_{ox}$  mais aussi à la différence des travaux de sortie du métal et du semiconducteur:  $\Phi_{ms} = \Phi_m - \Phi_s$ . Si  $\Psi_s = 0$ , on aura :

$$V_{FB} = \Phi_{ms} - \frac{Q_{ox}}{C_{ox}} \tag{1.4}$$

La valeur de la tension  $V_{FB}$  permet de déduire la quantité de charges fixes présentes dans les oxydes. La structure MOS réelle se distingue de la structure idéale à cause de l'état de l'interface  $SiO_2/Si$  qui n'est pas parfaite. La tension  $V_{GS}$  est donc :

$$V_{GS} = V_{FB} + \Psi_{s} - \frac{Q_{inv} + Q_{dep} + Q_{it}}{C_{OX}}$$

(1.5)

La charge d'états d'interface excédentaire est donnée par:  $|Q_{it}| = q \cdot N_{it} \cdot N_{it}$  est la densité de défauts à l'interface,  $Q_{inv}$  et  $Q_{dep}$  sont respectivement la charge d'inversion et la charge de déplétion.

#### 1.2.1.4 Tension de seuil

La tension de seuil d'un transistor MOSFET est définie comme la tension qu'il faut appliquer pour que le potentiel de surface  $\Psi_s$  soit égal à  $2\Phi_f$ . La tension de seuil est donnée par la

somme de la tension de bandes plates et de la chute du potentiel sur le diélectrique et celle sur la zone de déplétion :

$$V_{Th} = V_{FB} + \Phi_d + \frac{Q_{dep}}{C_{ov}} \tag{1.6}$$

$\Phi_d$  représente la hauteur de la barrière entre la source et le canal. Lorsque cette barrière est de l'ordre de quelques kT/q (énergie thermique des porteurs dans la source), les porteurs peuvent circuler librement dans le canal. Cette hauteur de barrière dépend aussi des dopages de la source et du canal.

#### 1.2.1.5 Pente sous le seuil

Quand le transistor est en régime de fonctionnement de faible inversion. L'inverse de la pente sous le seuil S, exprimé en mV/décade, informe de combien il faut diminuer la tension  $V_{GS}$  pour réduire le courant sous le seuil d'une décade. Elle est l'inverse de la pente, au sens mathématique de la droite  $log(I_D) = f(V_{GS})$ :

$$S = \frac{kT}{q} \cdot \ln 10 \left[ 1 + \frac{C_{dep}}{C_{ox}} + \frac{C_{it}}{C_{ox}} \right]$$

(1.7)

$C_{dep}$  est la capacité de la couche de déplétion dans le substrat.  $C_{it}$  est la capacité associée aux états d'interface. Par sa dépendance en  $C_{it}$ , la pente sous le seuil est révélatrice de la qualité de l'interface. La pente idéale, en négligeant  $C_{dep}$  et  $C_{it}$  devant  $C_{ox}$ , vaut  $S = kT/q \ln 10$ , ce qui correspond à environ 60 mV/décade à température ambiante.

#### 1.2.1.6 Courants I<sub>OFF</sub> et I<sub>ON</sub>

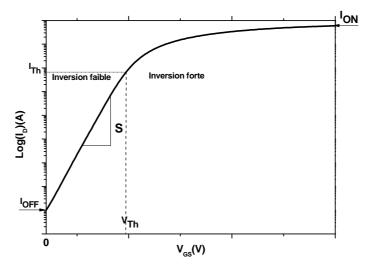

Le comportement électrique idéal d'un transistor est celui d'un interrupteur parfait dans les applications logiques. Si les tensions appliquées sur la grille  $V_{GS}$  et sur le drain  $V_{DS}$  sont nulles, l'interrupteur est bloqué, le courant de drain doit être nul, si  $V_{GS} = V_{DS} = V_{DD}$  (tension nominale), l'interrupteur est passant et le courant de drain  $I_{ON}$  est maximal. Dans le comportement réel, à l'état bloqué, le courant de drain n'est pas nul, il y a un courant de fuite  $I_{OFF}$  qui circule, qui est limité par la diffusion coté source et drain. La meilleure qualité du transistor MOSFET se concrétise par un courant de fuite le plus faible, un courant  $I_{ON}$  le plus fort et un passage le plus rapide de l'état OFF à l'état ON. La figure 1-3 illustre une caractéristique  $I_{D}(V_{GS})$  d'un transistor MOSFET. Le courant  $I_{OFF}$  est dépendant de la pente sous le seuil. Il est donné par la relation suivante :

$$\log(I_{OFF}) = \log(I_{Th}) - \frac{V_{Th}}{S} \tag{1.8}$$

avec  $I_{Th}$ : le courant de drain à  $V_{GS} = V_{Th}$ .

Figure 1-3: Caractéristique  $I_D(V_{GS})$  d'un transistor MOSFET.

#### 1.2.2 Modélisation d'un transistor MOSFET classique

En fonction de l'importance de la polarisation du drain, on peut distinguer principalement deux régimes : régime linéaire et régime de saturation.

#### 1.2.2.1 Régime linéaire

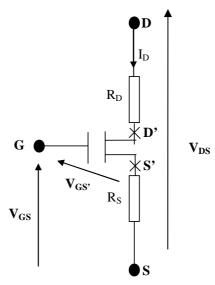

Lorsque la tension  $V_{DS}$  est faible et négligeable devant la tension  $V_{GS}$ , l'effet du champ est quasi uniforme le long du canal. Le canal se comporte donc comme une résistance indépendante de la polarisation du drain. Ce régime se caractérise par une dépendance linéaire du courant en fonction de la tension  $V_{DS}$ . Le courant de drain sera donné dans les deux cas de faible et de forte inversion en tenant compte des résistances d'accès de source  $R_S$  et de drain  $R_D$  qui sont schématisées dans la figure 1-4, les extrémités du canal réel étant notées S' et D':

Figure 1-4 : Schéma électrique équivalent d'un MOSFET avec l'influence des résistances série source et drain.

#### 1.2.2.1.1 Cas de faible inversion

En régime de faible inversion, le courant de drain varie exponentiellement avec  $V_{GS}$  et il est donné par:

$$I_{D} = \frac{W}{L} \frac{kT}{q} \mu_{0} C_{dep} V_{D'S'} \exp \left[ \frac{qA(V_{GS} - V_{Th})}{kT} \right]$$

(1.9)

$\mu_0$  est la mobilité à faible champ électrique. Le facteur A est donné par :

$$A = \frac{C_{ox}}{C_{ox} + C_{dep} + C_{it}}$$

(1.10)

La transconductance est donnée par la formule suivante :

$$g_m = \frac{q}{kT} A I_D \tag{1.11}$$

A une tension de drain  $V_{DS}$  constante, elle est donnée par :  $g_m = \frac{dI_D}{dV_{GS}}$ .

#### 1.2.2.1.2 Cas de forte inversion

En régime de forte inversion, le courant de drain s'écrit comme suit :

$$I_D = \frac{W}{L} \mu_{eff} Q_{inv} V_{D'S'} \tag{1.12}$$

$\mu_{\it eff}$  est la mobilité effective des porteurs dans le canal qui dépend de la charge d'inversion  $Q_{\it inv}$ , elle est donnée par :

$$\mu_{eff} = \frac{\mu_0}{1 + \frac{Q_{inv}}{Q_C}} \tag{1.13}$$

$Q_c$  est la charge critique qui caractérise la diminution de la mobilité aux fortes tensions de grille. Une valeur typique de  $Q_c$  est de l'ordre de  $10^{13}$  q·cm<sup>-2</sup>. En régime de forte inversion, la charge d'inversion peut s'écrire :

$$Q_{inv} = -C_{ox}(V_{GS} - V_{Th} - \frac{V_{DS}}{2})$$

(1.14)

La mobilité effective devient alors :

$$\mu_{eff} = \frac{\mu_0}{1 + \theta_0 (V_{GS} - V_{Th} - \frac{V_{DS}}{2})}$$

(1.15)

où  $\theta_0 = \frac{C_{ox}}{Q_c}$  est le facteur de réduction intrinsèque de la mobilité. On obtient donc la formule du courant de

drain suivante:

$$I_{D} = \frac{\beta V_{D'S'} (V_{GS'} - V_{Th} - \frac{V_{D'S'}}{2})}{1 + \theta_{0} (V_{GS'} - V_{Th} - \frac{V_{D'S'}}{2})}$$

(1.16)

avec

$$\beta = \frac{W}{L} \mu_0 C_{ox}$$

En prenant en compte que  $R_S = R_D = R_{SD}/2$ , le courant de drain est donné par :

$$I_{D} = \frac{\beta V_{DS} (V_{GS} - V_{Th} - \frac{V_{DS}}{2})}{1 + \theta_{1} (V_{GS} - V_{Th} - \frac{V_{DS}}{2})}$$

(1.17)

où

$$\theta_1 = \theta_0 + \beta (R_S + R_D)$$

La transconductance du transistor devient :

$$g_{m} = \frac{\beta V_{DS}}{\left[1 + \theta_{1}(V_{GS} - V_{Th} - \frac{V_{DS}}{2})\right]^{2}}$$

(1.18)

#### 1.2.2.2 Régime de saturation

Lorsque la tension de drain  $V_{DS}$  augmente, la différence de potentiel entre le drain et la grille diminue, en conséquence la charge d'inversion diminue en s'approchant du drain. Pour une valeur de la tension appliquée sur le drain proche de  $V_{GS}$ - $V_{Th}$ , le canal à proximité du drain est pincé et le courant de drain reste constant avec l'augmentation de  $V_{DS}$  (dans le cas idéal). Le courant de drain est alors donné par :

$$I_{Dsat} = \int_{0}^{V_{DS}} \frac{W}{L} \mu_{eff} Q_{inv} d\Phi_{c} \approx \frac{1}{2} \beta V_{Dsat}^{2}$$

(1.19)

Avec:  $Q_{inv} = C_{ox}(V_{GS} - V_{Th} - \Phi_c)$ ,  $\Phi_c$  étant la différence entre les quasi niveaux de Fermi des électrons et des trous.

Dans le cas réel, le courant de drain ne reste pas constant mais continue à augmenter légèrement avec la polarisation du drain. L'augmentation du courant est due à l'éloignement du point de pincement par rapport au drain, à la réduction de la tension de seuil avec la tension  $V_{DS}$  et à l'effet d'avalanche. Le point de pincement se caractérise par la disparition de l'inversion. Tout excédent de la tension  $V_{DS}$  au delà de  $V_{Dsat}$  développe, autour du drain, une zone de charge d'espace d'une épaisseur:

$$\lambda = \lambda_0 \ln \left[ 1 + \frac{V_{DS} - V_{Dsat}}{V_{Dsat}} \right] \tag{1.20}$$

Avec  $\lambda_0 = \sqrt{(\frac{\varepsilon_{Si}}{\varepsilon_{ox}} X_j T_{ox})}$ : la zone de charge d'espace minimale.

Le développement de la zone de charge d'espace, d'épaisseur  $\lambda$ , implique un raccourcissement du canal inversé dont la longueur devient L-  $\lambda$  au lieu de L, donc au régime de saturation, on aura un courant de drain qui sera de la forme suivante :

$$I_{DS} = I_{Dsat} \cdot \frac{L}{L - \lambda} = I_{Dsat} \left[ 1 + \frac{V_{DS} - V_{Dsat}}{V_E} \right]$$

(1.21)

où  $V_E = \frac{L}{\lambda_0} V_{Dsat}$  est la tension d'Early, plus cette tension est élevée, meilleures seront les performances du transistor.

#### 1.2.3 Mobilité de porteurs de charge

La mobilité traduit l'aptitude des porteurs à se déplacer dans la couche d'inversion sous l'effet d'un champ électrique longitudinal. Elle dépend de nombreux paramètres dont les principaux sont le champ électrique transversal, l'orientation du cristal, la température et le dopage du substrat. Les différents mécanismes de collision qui influent sur la mobilité dans la couche d'inversion d'un transistor MOSFET sont les collisions avec les phonons, les collisions sur les centres coulombiens et les collisions sur la rugosité de surface [4].

#### 1.2.3.1 Collisions avec les phonons

Ce type de collisions résulte des vibrations du réseau. Pour une température T < 100K, on trouve les phonons acoustiques, qui donnent des collisions quasi-élastiques à faible champ et conduisent à une mobilité à l'interface de la forme:

$$\mu_{ph} = \mu_{pha} \propto N_{inv}^{1/3} T^{-1} \tag{1.22}$$

$N_{inv}$  représente la concentration des porteurs de charge de la couche d'inversion. A des températures plus élevées (100 < T < 370 K), on trouve les phonons optiques, ils conduisent à l'expression suivante :

$$\mu_{ph} = \mu_{pho} \propto N_{inv}^{1/b} T^{-n}$$

(1.23)

avec :  $3 \le b \le 6$  et  $1 \le n \le 1,5$ , ces constantes dépendent de l'orientation cristallographique.

#### 1.2.3.2 Collisions sur les centres coulombiens

Ce mécanisme est dû aux sites chargés près du canal. Généralement, ces charges sont localisées principalement à l'interface Si/SiO<sub>2</sub>. Ces collisions commencent à se manifester à des températures suffisamment basses lorsque les collisions sur les phonons ne sont pas dominantes. Elles sont importantes en faible inversion, mais deviennent moins effectives lorsqu'on passe en forte inversion à cause de l'effet d'écrantage des charges par les porteurs minoritaires. L'atténuation de la mobilité est donnée par :

$$\mu_c \propto N_{cs}^{-1} T \tag{1.24}$$

$N_{cs}$  représente la concentration de charges de surface, comprenant la charge fixe de l'oxyde, la charge d'états d'interfaces ainsi que la charge localisée due aux impuretés ionisées.

#### 1.2.3.3 Collisions sur la rugosité de surface

Les défauts à l'interface Si/SiO<sub>2</sub> sont une importante source de collisions. Les collisions sur les rugosités de surface sont indépendantes de la température et dominantes pour les forts champs électriques transversaux. Elles peuvent être modélisées par :

$$\mu_{sr} \propto E_{eff}^{-2} \tag{1.25}$$

$E_{\it eff}$  est le champ électrique transversal effectif qui est donné par :

$$E_{eff} = \frac{q(\eta N_{inv} + N_{dep})}{\varepsilon_{Si}} \tag{1.26}$$

$N_{inv}$  et  $N_{dep}$  sont les densités de charges des zones d'inversion et de déplétion respectivement,  $\varepsilon_{Si}$  est la permittivité relative du silicium,  $\eta$  est une constante.

#### 1.2.3.4 Combinaison des trois mécanismes de collisions

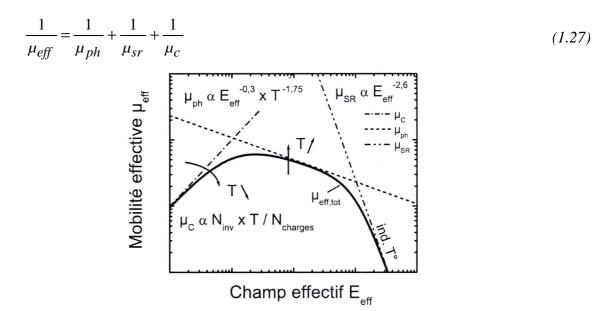

La contribution relative de ces trois mécanismes dépend de la température et de la concentration des porteurs dans le canal. A température ambiante et en faible inversion, la mobilité est contrôlée par les collisions sur les phonons et par les collisions coulombiennes, alors qu'en forte inversion, les collisions sur les rugosités de surface sont prépondérantes. A basses températures, seuls les deux derniers mécanismes sont significatifs. La figure 1-5 représente les dépendances empiriques de la mobilité effective associée à chaque mécanisme en fonction du champ effectif et de la température. La mobilité totale dans la couche d'inversion peut être extrapolée en utilisant la loi empirique de Matthiessen qui considère que tous les mécanismes sont statistiquement indépendants des uns des autres:

Figure 1-5 : Dépendances empiriques de la mobilité effective associée à chaque mécanisme en fonction du champ effectif et de la température [5].

#### 1.3 Effets de miniaturisation

#### 1.3.1 Loi de Moore et de réduction d'échelle

Depuis les années 60, l'intégration en microélectronique suit une évolution exponentielle. Cette évolution est connue sous le nom de « loi de Moore ». G. Moore, l'un des co-fondateurs d'Intel avait prédit, en 1973, que le nombre de transistors intégrés sur une puce doublerait environ tous les 2 ans. La diminution soutenue des dimensions depuis 50 ans accélère la rencontre de la microélectronique avec la mécanique quantique et d'autres lois régissant le transport des porteurs de charge. Pour des applications hautes performances, l'oxyde de grille du transistor ne doit pas avoir une épaisseur supérieure à 1,2 nm (une monocouche de silice a environ 5 Å). En outre, une si fine couche d'isolant ne jouera plus son rôle d'isolant à cause de l'augmentation des fuites par effet tunnel. Cela engendrera un autre problème pour les applications basse consommation. Le maintien de l'augmentation exponentielle du nombre de transistors devient extrêmement difficile et coûteux. Des tendances sont apparues : « More Moore » et « More Than Moore ». La première repousse les limites en essayant de continuer le plus longtemps possible la technologie actuelle et l'autre en proposant d'aller plus loin avec d'autres matériaux et de nouveaux concepts technologiques. La réduction des dimensions (« The scaling ») demeure essentielle pour mieux intégrer des fonctions électroniques, parmi les autres avantages de celle-ci; la réduction du coût de fabrication, la réduction de consommation, etc. L'association de l'industrie des semiconducteurs SIA (« Semiconductor Industry Association ») publie depuis 1998 une feuille de route ITRS; (« The international Technology Roadmap for Semiconductors») qui est un guide pour l'industrie mondiale

des semiconducteurs [6]. Les caractéristiques physiques et électriques sont fixées pour une génération donnée ainsi que les principaux critères de performances à atteindre dans divers processus d'élaboration (gravure, architecture.) et pour diverses applications (microprocesseurs, mémoires..).

La réduction des dimensions génère des problèmes technologiques complexes et des effets néfastes au bon fonctionnement du transistor, tels que la diminution de la mobilité et la dépendance de la tension de seuil avec la longueur du canal. Pour cela, des lois de réduction d'échelles ont été proposées afin de minimiser ces effets. Des lois de réduction d'échelle ont été énoncées pour la première fois en 1974 par Dennard et al [7] et révisées plusieurs fois. Parmi ces révisions, il y a eu celle de Baccarani en 1984 [8]. Leur but est de garder le même niveau du champ électrique interne quelles que soient les dimensions du transistor. Cette réduction de paramètre entraine une amélioration intrinsèque des performances du transistor. La méthode utilise des facteurs d'échelle différents ( $\lambda$  et k). Le tableau suivant représente ces lois de réduction d'échelle pour les applications sub-0.25 $\mu$ m:

| Paramètres physiques | Grandeur                          | Facteur d'échelle |

|----------------------|-----------------------------------|-------------------|

| Dimensions           | $W, L, T_{ox}, X_{j}(m)$          | 1/λ               |

| Potentiels           | $V_{GS}, V_{DS}, V_{Th}(V)$       | 1/k               |

| Dopage               | $N_A$ , $N_D$ (cm <sup>-3</sup> ) | $\lambda^2$ /k    |

| Champ électrique     | E (V/cm)                          | λ/k               |

| Capacités            | $C_{ox}, C_{j}$                   | 1/ λ              |

| Puissance            | $I_D.V_{DD}(W)$                   | $1/k^2$           |

Tableau 1-1 : Lois de réduction d'échelle [8].

Le tableau montre qu'il ne suffit pas de diminuer les dimensions géométriques du transistor (L et W) mais aussi les dimensions des couches technologiques de celui-ci : oxyde de grille, jonction source et drain, etc.

#### 1.3.2 Nouveaux phénomènes physiques engendrés par la miniaturisation

De nombreux phénomènes physiques apparaissent au fur et à mesure de la réduction des dimensions des transistors et ne peuvent plus être ignorés. Parmi ces phénomènes dont l'impact sur les caractéristiques électriques des transistors est le plus important, on peut citer l'effet de confinement quantique, la saturation de la vitesse, le transport balistique et l'effet tunnel [9].

#### 1.3.2.1 Effets quantiques de confinement

L'introduction d'oxydes de grille de plus en plus minces et des niveaux de dopage de plus en plus élevés dans le canal des transistors courts, a pour conséquence l'augmentation du champ électrique à l'interface oxyde/canal. Ceci se traduit par une courbure accentuée des bandes d'énergies en régime d'accumulation et en inversion et induit le confinement des charges à l'interface dans un puits de potentiel de plus en plus étroit. Les électrons ne se comportent plus comme un gaz à 3 dimensions mais plutôt comme un gaz à 2 dimensions. Leur énergie étant quantifiée, il apparait des niveaux d'énergies discrets dans un puits de potentiel. En plus, la charge d'inversion totale est plus faible que dans le cas classique en raison du nombre réduits de niveaux d'énergies peuplés et d'une densité d'états bidimensionnelle. L'impact de ce confinement quantique, le plus important sur les propriétés électriques, est la diminution de la capacité de grille et de la transconductance ou encore l'augmentation de V<sub>Th</sub> [10].

#### 1.3.2.2 Saturation de la vitesse des porteurs

Sous l'action d'un champ électrique longitudinal  $E_L$  entre la source et le drain, les porteurs se déplacent avec une vitesse de dérive v en régime stationnaire qui est définie par :  $v = \mu L_L$ .

A partir d'une certaine valeur du champ, appelée champ critique  $E_{c, L}$  ( $10^4$  V/cm dans le silicium), la vitesse tend vers une valeur limite appelée vitesse de saturation  $v_{sat}$  ( $10^7$  cm/s dans le silicium) [11]. Dans ce cas, le courant se sature avant le pincement du canal puisque les porteurs atteignent leur vitesse limite. Avant d'atteindre  $v_{sat}$ , la dimunition de la mobilité effective avec  $V_{DS}$   $\mu_{eff}$  ( $V_{DS}$ ) peut être écrite selon l'équation suivante pour  $E < E_{c, L}$ :

$$\mu_{eff}(V_{DS}) = \frac{\mu_{eff}}{1 + \frac{E_L}{E_{c,L}}} = \frac{\mu_{eff}}{1 + \theta_D V_{DS}}$$

(1.28)

avec  $V_{DS} \approx E_L L$  et  $\theta_D = \frac{\mu_{eff}}{2v_{sat}L}$  est le facteur d'atténuation de la mobilité dû au champ électrique longitudinal.

#### 1.3.2.3 Transport balistique et quasi balistique

En dessous de quelques dizaines de nanomètres de longueur de grille, la distance entre la source et le drain devient comparable au libre parcours moyen des porteurs  $\lambda$  entre deux collisions. Les porteurs passent ainsi d'un « réservoir » à un autre sans subir aucune interaction dans le canal. Le transport est qualifié de balistique. Le courant est seulement limité par la vitesse d'injection  $v_{inj}$  des porteurs au niveau de la source selon l'équation suivante [12]:

$$I_{Dsat} = WQ_{inv}\nu_{inj} \tag{1.29}$$

Dans le cas d'un transport balistique pur, les porteurs injectés au niveau de la source atteignent le drain et si l'on considère un gaz de porteurs non dégénérés,  $v_{inj}$  est égale à la vitesse thermique des porteurs  $v_{th}$  définie par :

$$v_{\rm th} = \sqrt{\frac{2kT}{\pi m^*}} \tag{1.30}$$

où  $m^*$  est la masse effective isotrope de conduction des porteurs de charges.

Dans le cas d'un régime quasi-balistique, certains porteurs injectés au niveau de la source sont rétrodiffusés, on définit le coefficient de rétrodiffusion r (*«backscattering coefficient »*) qui traduit la proportion de porteurs qui ne sont pas collectés par le drain. Selon Lundstrom  $et\ al$ , le courant de drain dans le régime linéaire peut s'écrire :

$$I_{D} = (1 - r)\frac{W}{L}\mu_{bal}Q_{inv}V_{DS} = r\frac{W}{L}\mu_{dd}Q_{inv}V_{DS} = \frac{W}{L}\mu_{exp}Q_{inv}V_{DS}$$

(1.31)

où  $\mu_{bal}$  est la mobilité balistique,  $\mu_{dd}$  est la mobilité dérive-diffusion,  $\mu_{exp}$  est la mobilité mesurée expérimentalement. On peut obtenir le coefficient de rétrodiffusion à partir de l'équation suivante :

$$r = 1 - \frac{\mu_{\text{exp}}}{\mu_{bal}} \tag{1.32}$$

La mobilité balistique  $\mu_{bal}$  peut être estimée à partir de l'équation (1.31) en considérant que le courant de drain est dans la limite balistique (r = 0) comme suit [13]:

$$\mu_{\text{bal}} = \frac{q \, \nu_{inj} L}{2kT} \frac{i_{-1/2}(\eta_F)}{i_0(\eta_F)} \tag{1.33}$$

$v_{inj} \approx 1,2 \, 10^7 \, \mathrm{cm/s}$  pour le silicium ;  $i_{-1/2} \, (\eta_F)$  et  $i_0 \, (\eta_F)$  sont les fonctions de Fermi-Dirac avec  $\eta_F$  étant le niveau réduit de Fermi. Le facteur de dégénérescence  $i_{-1/2} \, (\eta_F)/i_0 \, (\eta_F)$  égale à 1 dans la limite de la statistique de Boltzmann; ce facteur peut être approximé par  $1/(1+Q_{inv}/Q_c)$  pour le cas d'une seule sous-bande dans la limite quantique.

En ayant  $\mu_{exp}$  et estimé  $\mu_{bal}$ , on peut retrouver le coefficient de rétrodiffusion r et la mobilité dérive-diffusion  $\mu_{dd}$  en utilisant l'expression de Matthiessen de la mobilité:

$$\frac{1}{\mu_{\rm exp}} = \frac{1}{\mu_{bal}} + \frac{1}{\mu_{dd}} \tag{1.34}$$

#### **1.3.2.4 Effet tunnel**

Quand l'oxyde de silicium atteint des épaisseurs nanométriques, des courants de fuite tunnel de grille peuvent survenir. Pour des épaisseurs d'environ 3 nm, il peut y avoir un courant tunnel Fowler-Nordheim. Pour des épaisseurs inferieures à 3 nm, un courant tunnel direct peut apparaitre. D'autres courants peuvent être générés à cause des défauts dans le volume de l'oxyde; tels que la conduction Poole Frenkel ou la conduction par sauts « Hopping » [14], [15], [16].

Un autre courant tunnel entre la source et le drain peut apparaître quand les longueurs de grilles sont seulement de quelques nanomètres. La barrière de potentiel source-canal-drain devient si faible que les porteurs peuvent directement passer par effet tunnel de la source au drain, même sous faible polarisation de grille et/ou drain. Il s'agit ici d'une des limites physiques les plus fondamentales puisque cet effet tunnel parasite est susceptible d'affecter la caractéristique sous le seuil et donc le courant  $I_{OFF}$  des dispositifs ultimes de la microélectronique [14].

#### 1.3.2.5 Effets de canaux courts

Le transistor à canal court subit l'influence de plusieurs effets parasites qui affectent le bon fonctionnement du dispositif. Dans le régime de conduction, plusieurs effets viennent perturber la caractéristique idéale du transistor MOSFET.

Dans un transistor long, le potentiel de surface est plat pratiquement sur l'ensemble de la longueur de grille. Les expansions des zones de charges d'espaces autour des jonctions ne dépendent pas de la longueur du canal. Dans un transistor court, le potentiel de surface peut être complètement dominé par les zones de charges d'espaces. La partie plate peut être réduite jusqu'à une disparition totale. La superposition de zones de charges d'espaces des jonctions source et drain conduit à l'abaissement de la barrière de potentiel entre la source et le canal ; c'est l'effet de canal court SCE (« Short Channel Effect »). Si, de plus, la polarisation du drain augmente, la barrière se réduit davantage ; on parle alors de l'effet DIBL (« Drain Induced Barrier Lowering »), on utilise aussi le terme « roll-off » qui décrit la chute totale de la tension V<sub>Th</sub>. Ainsi, la charge d'inversion est contrôlée par le drain en plus de la grille ; il en résulte une augmentation du courant dans le régime de saturation [11]. Un autre effet est le courant de fuite GIDL (« Gate Induced Drain Leakage ») [17]; en raison de la réduction de l'épaisseur de l'oxyde de grille, de forts champs électriques transversaux sont créés au niveau du drain. Ceci peut générer un courant de fuite entre la grille et le drain à l'état bloqué du transistor MOSFET. D'autres effets parasites peuvent dégrader le fonctionnement à l'état bloqué, tels que l'effet des courants de fuite des jonctions source/canal et canal/drain polarisées en inverse (« Reverse Short Channel »), appelé aussi « roll-up » et le courant de perçage source/drain (« punchthrough »).

Tous ces effets constituent une limitation importante pour la miniaturisation des technologies. L'incovenient ne consiste pas uniquement en la diminution de la tension de seuil elle-même, mais aussi en l'accentuation de la sensibilité des circuits aux dispersions technologiques.

#### 1.4 Solutions technologiques

Afin de limiter les effets néfastes dus à la miniaturisation des transistors MOSFETs, des ajouts sont couramment utilisés dans les technologies les plus avancées pour améliorer les performances du transistor à savoir l'amélioration du contrôle électrostatique en créant de nouvelles architectures, la réduction des fuites de grille en utilisant de nouveaux matériaux et d'autres solutions technologiques pour l'amélioration des propriétés du transport des porteurs.

#### 1.4.1 Transistor MOSFET SOI

La première révolution dans l'architecture du transistor MOSFET est l'apparition des transistors sur film mince SOI (« Silicon On Insultor »). Ce type de transistor est caractérisé par deux paramètres supplémentaires par rapport aux transistors conventionnels : l'épaisseur du film Si (t<sub>Si</sub>) sur lequel est intégrée la région active du dispositif et l'épaisseur de la couche d'oxyde (t<sub>BOX</sub>) dit oxyde enterré. On distingue deux types de dispositif sur film mince. Lorsque l'épaisseur t<sub>Si</sub> du film est suffisamment épaisse, une partie seulement du film est désertée. On parle alors du transistor sur isolant partiellement déserté PD-SOI (« Partialy Depleted Silicon On Insulator »), son fonctionnement et ses caractéristiques sont proches de ceux du transistor sur silicium massif. Lorsque l'épaisseur t<sub>Si</sub> est plus fine, l'ensemble du substrat est déserté et on parle cette fois d'un transistor totalement déserté ; FD-SOI (« Fully Depleted Silicon On Insulator »). Ce dernier présente de nombreux avantages tels que l'obtention des jonctions ultra-minces permettant un bon contrôle des effets de canaux courts. Les avantages de la technologie SOI sont que le substrat est isolé de la couche active, il y a minimisation des capacités parasites associées au substrat et pas de courant de fuite du substrat.

Les transistors SOI possèdent aussi quelques inconvénients, tels que l'augmentation des résistances d'accès, les effets d'auto-échauffement qui se traduisent par une diminution du niveau du courant [18]. Le film se comporte comme un substrat flottant, ce qui génère des effets néfastes comme l'effet « Kink » qui peut entrainer un blocage définitif du transistor [19], [20], l'effet bipolaire parasite qui peut empêcher le transistor de repasser de l'état ouvert à l'état fermé [21], [22] ainsi que la dégradation de la mobilité des porteurs dans le canal liée à la faible épaisseur du film [23]. Malgré ces inconvénients, les transistors SOI sont très prometteurs et ils ont ouvert la voie à

des architectures plus évoluées; les transistors MOSFET à grilles multiples abordés dans le paragraphe 1.4.4.

#### 1.4.2 Utilisation d'empilements avec isolant à haute permittivité et grille métallique

L'empilement de grille est une brique technologique essentielle d'un transistor MOSFET. Il est devenu ces dernières années le centre d'intérêt pour améliorer les performances, notamment en réduisant fortement l'épaisseur de l'oxyde de grille afin d'augmenter le courant du drain.

Pour tenter de s'affranchir des problèmes posés par l'amincissement de l'oxyde de grille, notamment en termes de courant de grille, fiabilité et consommation électrique, une alternative consiste à remplacer le siliciure (SiO<sub>2</sub>) par un matériau de permittivité diélectrique supérieure (« high-k »). On peut alors avoir un isolant de grille d'épaisseur plus importante, tout en gardant les mêmes performances électriques (c'est à dire la même capacité d'oxyde). La capacité devient alors :

$$C_{ox} = \frac{\mathcal{E}_{hk}^r \mathcal{E}_0}{T_{hk}} \tag{1.35}$$

$\mathcal{E}_{hk}^{r}$ ,  $T_{hk}$  sont la permittivité relative et l'épaisseur du matériau high-k respectivement.

Pour des raisons de commodité, ces performances sont toujours évaluées en épaisseur équivalente d'oxyde EOT (« *Equivalent Oxide Thickness* »), c'est à dire l'épaisseur physique de  $SiO_2$  qu'il faudrait pour obtenir la même valeur de la capacité d'oxyde  $C_{ox}$ , l'objectif étant d'obtenir une épaisseur équivalente inférieure à 1 nm, elle se définit comme suit :

$$EOT = T_{hk} \frac{\varepsilon_{SiO_2}^r}{\varepsilon_{hk}^r}$$

(1.36)

La permittivité électrique étant supérieure à celle de SiO<sub>2</sub>, l'épaisseur du matériau high-k déposé est donc supérieure à l'épaisseur équivalente d'oxyde (EOT). L'utilisation des diélectriques à haute permittivité permet une amélioration de l'autonomie pour des applications basse consommation [24]. L'utilisation d'un oxyde épais permet aussi de réduire les interactions coulombiennes entre les porteurs du canal et les charges dans la grille (déplétion de la grille) ce qui améliore le transport électrique dans le canal.

Quelques inconvénients se manifestent tel que l'augmentation de la densité de charges fixes dans les diélectriques à haute permittivité high-k et le phénomène d'ancrage du niveau de Fermi dans la grille (« Fermi level pinning ») qui modifie la structure de bande du matériau high-k quand ce dernier est associé à une grille en polysilicium [25]. Tous ces phénomènes engendrent une augmentation de la tension de seuil. En conséquence, la grille en polysilicium a été remplacée par une grille métallique « mid-gap », ce matériau doit avoir une stabilité thermique, chimique et

mécanique avec les oxydes de grille [26]. Les métaux les plus prometteurs, ayant une meilleure compatibilité avec les high-k sont le nitrure du titane (TiN) et le nitrure de tantale (TaN) [27].

Le dépôt du high-k sur le silicium engendre une couche de silice non intentionnelle de mauvaise qualité. Cet effet est néfaste au bon fonctionnement du transistor. La solution est d'utiliser une couche interfaciale IL (« *Interfacial layer* ») bien maitrisée d'oxyde de silicium (SiO<sub>2</sub>, SiO<sub>x</sub>, SiON). Le choix de la technique de dépôt est aussi important pour une bonne qualité de l'oxyde de grille [28].

La dégradation de la mobilité des porteurs dans le canal limite l'intégration de matériaux high-k dans les transistors. Cette dégradation est due aux interactions coulombiennes (« *Coulomb Scattering* ») qui sont causées par les pièges d'interface et les charges dans l'oxyde ainsi que les interactions avec les phonons optiques (« *Phonon scattering* ») [29]. Toutefois, d'autres solutions ont été trouvées pour y remédier telles que les contraintes mécaniques qui améliorent la mobilité comme on le verra plus en détail dans le paragraphe 1.4.3.2.

Les matériaux high-k les plus utilisés actuellement, en empilement avec une grille métallique et une couche interfaciale (SiO<sub>2</sub>) bien maitrisée sont l'oxyde d'hafnium (HfO<sub>2</sub>) et le silicate d'hafnium nitruré (HfSiON). Ce sont ces types d'empilement qu'on a eu l'occasion d'étudier dans les transistors FinFETs caractérisés au cours de cette thèse.

#### 1.4.3 Amélioration du transport de charge dans le canal

Le maintien de l'intégration demande une amélioration continue de la mobilité des porteurs dans le canal. De nombreuses méthodes ont été trouvées pour augmenter la mobilité telle que l'utilisation de nouveaux matériaux dans le canal du transistor, le changement de l'orientation cristalline du canal et du substrat et l'implémentation de nouvelles techniques de contrainte.

#### 1.4.3.1 L'orientation cristalline du canal ou du substrat

La mobilité des porteurs de la couche d'inversion dépend de l'orientation de la surface et de la direction du flux du courant. Ceci est dû à l'asymétrie des masses effectives des porteurs dans le réseau du silicium cristallin [30]. Il existe deux orientations potentielles du substrat pour les transistors planaires : (100) et (110). Le meilleur transistor nMOSFET a été fabriqué sur un substrat (100) avec une direction du canal <110> et le meilleur pMOSFET a été fabriqué sur un substrat (110) avec une direction du canal <110> [31]. Dans les transistors non-planaires, il est un peu compliqué d'optimiser l'orientation du substrat et du canal. Par exemple, de nouvelles structures de transistors FinFETs peuvent être orientés dans les directions différentes pour différentes

orientations, par exemple, placer un nFinFET à 45° du pFinFET sur une surface (100) donne (110) <110> pour le pFinFET et un nFinFET (100) <110> [32].

#### 1.4.3.2 L'ingénierie de contraintes mécaniques

La contrainte mécanique a un impact considérable dans la continuité de l'intégration. Un grand nombre de techniques sont employées aujourd'hui dans la fabrication des transistors. La contrainte mécanique induit des déformations qui modifient les propriétés électroniques en changeant la symétrie du cristal. Elle permet d'augmenter la mobilité donc les performances du transistor. La contrainte a été considérée comme néfaste dans les années 80 [33], car elle générait des défauts ponctuels (lacunes, impuretés...) ainsi que des dislocations qui modifient les propriétés électriques du matériau. Ce n'est que dans cette dernière décennie qu'on a commencé à étudier et à utiliser les contraintes mécaniques à petite échelle pour améliorer les performances du transistor MOSFET. La contrainte modifie la structure de bande du semiconducteur. L'énergie de la bande interdite est modifiée et les dégénérescences de la bande de conduction et de valence sont levées, réduisant la probabilité d'interaction entre les porteurs et les phonons. La mobilité effective des porteurs s'écrit comme suit :

$$\mu_{eff} = \frac{q\tau}{m^*} \tag{1.37}$$

$1/\tau$  est la fréquence de collisions des porteurs,  $m^*$  est la masse effective de conduction des porteurs, q est la charge élémentaire.

L'introduction des contraintes améliore la mobilité grâce à la réduction de la masse effective de conduction et/ou de la fréquence de collisions des porteurs. Il existe deux manières d'introduire une contrainte dans le canal du transistor : contrainte mécanique globale ou locale. La contrainte globale peut être introduite par le substrat, la couche du silicium active est alors contrainte sur toute la surface de la plaque. D'autre part, la contrainte peut être introduite localement au niveau du canal lors des procédés de fabrication. L'effet d'une contrainte est différent pour les électrons et les trous. Pour les transistors nMOSFETs, une contrainte en tension est nécessaire tandis que pour les transistors pMOSFETs, la contrainte doit être en compression. Les transistors contraints offrent une grande robustesse au claquage de l'oxyde et une meilleure immunité aux effets de porteurs chauds [34].

#### 1.4.3.3 Silicium sur isolant contraint (sSOI)

Une des anciennes techniques de contrainte dans la technologie CMOS est de déposer une fine couche du silicium par épitaxie sur une couche tampon de Si<sub>1-x</sub>Ge<sub>x</sub> relaxée (SRB; « *Strain*

relaxed buffer »). Ce dernier a une maille plus grande que celle du silicium, l'alignement des mailles induit une contrainte en tension en deux axes dans la couche du silicium [35], [36]. Cependant, la diffusion des atomes du Ge vers l'interface Si/SiO<sub>2</sub> et son accumulation créent des densités de pièges à l'interface et dans le volume de l'oxyde qui augmentent le courant de fuite de grille assisté par pièges (conduction Poole-Frenkel) ainsi qu'une dégradation de la mobilité. Grâce au procédé « Smart Cut », la couche tampon peut être enlevée, on peut avoir des substrats de silicium contraints directement sur isolant sSOI (« Strained Silicon On Insulator »). Ce substrat permet d'améliorer la mobilité dans le transistor [37]. La contrainte introduite permet d'obtenir une contrainte en tension, dans le canal d'un transistor MOSFET, qui peut atteindre 1 GPa. Les gains obtenus avec les substrats sSOI sont de l'ordre de 70 % pour les nMOSFETs longs et 40 % pour les pMOSFETs par rapport aux transistors sur substrat SOI. En plus de cet atout, ils possèdent une grande compatibilité avec les procédés d'intégration et avec les architectures standards des dispositifs CMOS.

#### 1.4.3.4 Couche d'arrêt à la gravure (CESL)

L'une des techniques locales d'introduction de contrainte pour les transistors nMOSFETs et pMOSFETs est le CESL (« *Contact Etch Stop Layer* »). C'est une couche qui recouvre la grille, généralement en nitrure du silicium (SiN<sub>x</sub>) [38]. De telles couches peuvent introduire une contrainte en tension ou en compression afin d'améliorer la mobilité dans les nMOSFETs ou dans les pMOSFETs respectivement surtout dans les transistors à faibles dimensions puisqu'il s'agit d'un effet de bord. L'un des principaux facteurs qui contrôle la contrainte dans le film est lié aux liaisons d'Hydrogène ; le rapport N-H/Si-H. Un grand nombre de liaisons N-H induit une contrainte en compression dans le film et un grand nombre de liaisons Si-H augmente la contrainte en tension. Les contraintes sont de l'ordre de 1-2 GPa. L'amélioration du courant de drain est de 10 à 30 % quand on utilise les types de techniques CESL appropriées pour les nMOSFETs et les pMOSFETs.

#### 1.4.3.5 Croissance épitaxiale sélective (SEG)

La contrainte est introduite par une croissance épitaxiale sélective SEG (« Selective Epitaxial Growth ») du SiGe ou du Si:C dans les régions de la source et du drain. La grande maille du SiGe crée une contrainte parallèle en compression dans le canal, ce type de contrainte est bénéfique pour les transistors pMOSFETs. Cette contrainte induit une réduction des résistances d'accès [39], [40], améliore la mobilité des porteurs et réduit le courant de fuite GIDL [41].

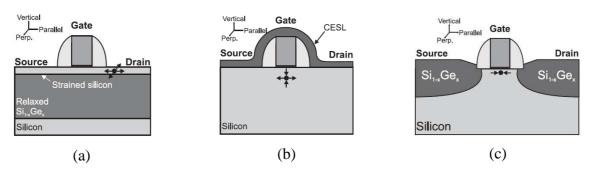

La figure 1-6 illustre des coupes schématiques de transistors MOSFETs avec les trois différentes techniques de contraintes citées ci-dessus. La coupe schématique (a) représente un

transistor sSOI, la coupe schématique (b) est celle d'un transistor ayant subi la technique CESL et la coupe schématique (c) est celle d'un transistor ayant subi la technique SEG.

Figure 1-6 : Coupes schématiques de transistors MOSFET avec différentes techniques de contraintes ; la coupe schématique (a) sSOI : un substrat contraint avec du SiGe relaxé, (b) CESL : dépôt de la couche CESL qui recouvre totalement la grille, (c) SEG : croissance du SiGe dans la source et le drain par une épitaxie sélective [34].

#### 1.4.4 MOSFET à grilles multiples

Les transistors à grilles multiples (MUGFETs) sont largement reconnus comme des candidats prometteurs pour satisfaire les exigences de l'ITRS, grâce au bon contrôle du canal par la grille. La première publication décrivant un transistor SOI MOSFET double grille date de 1984. Le composant a été nommé « XMOS », car sa section efficace ressemble à la lettre grecque  $\Xi$  (Xi), en utilisant cette configuration un meilleur contrôle du canal a été obtenu par rapport au transistor MOSFET SOI standard [42], [43], [44]. Depuis, plusieurs architectures à grilles multiples ont vu le jour. Les dispositifs sont considérés parmi les architectures les plus innovantes, les plus prometteuses pour les générations technologiques les plus intégrées. Un transistor double-grille est équivalent à une structure SOI dans laquelle l'oxyde de grille et l'oxyde enterré ont la même épaisseur, les grilles avant et arrière étant connectées ensemble. D'un point de vue électrostatique, le transistor MOS double-grille est plus robuste que le transistor MOS à une simple grille puisque la double-grille, fortement couplée au canal, contrôle simultanément le potentiel de surface aux deux interfaces du film du silicium. Par conséquent, les effets de canaux courts sont réduits. Un autre avantage de ces dispositifs vient du caractère symétrique de la distribution du potentiel électrostatique qui induit un champ nul au milieu du film ce qui permet d'augmenter la mobilité, une réduction des phénomènes parasites liés aux fluctuations de dopants et, simultanément, une augmentation de la probabilité de transport balistique dans le cas des canaux courts (< 20 nm).

Il existe de nombreuses variantes de la configuration double-grille, par exemple si la grille est présente sur deux des quatre cotés du film. Lorsque le film de silicium est enrobé par la grille, on parle de transistor GAA (« *Gate-All-Around* ») où le contrôle du canal est amélioré. Pour une

grille présente sur trois des quatre interfaces, plusieurs structures ont été proposées :  $\Omega$ -FET,  $\Pi$ -FET, FinFET. Dans ces configurations le contrôle électrostatique du film est encore amélioré, ce qui permet de gagner jusqu'à 50 % au niveau de la réduction des dimensions [45], [46].

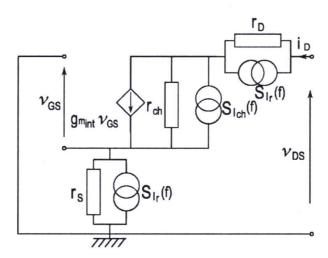

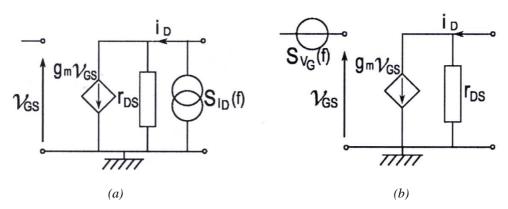

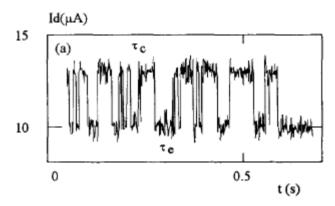

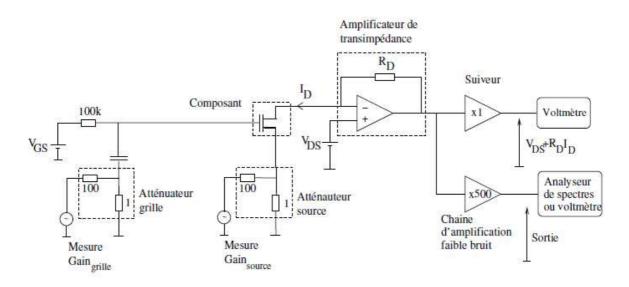

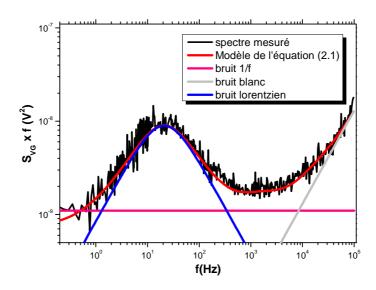

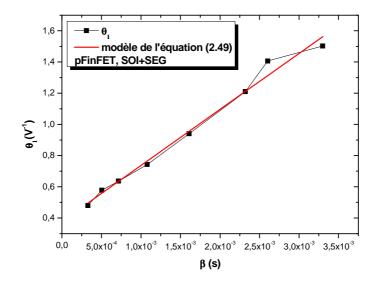

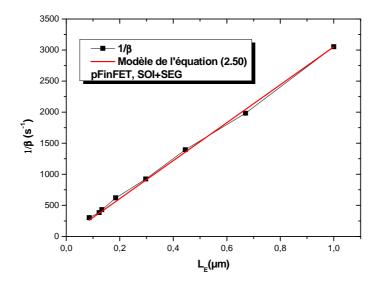

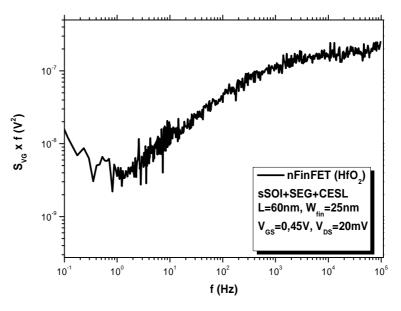

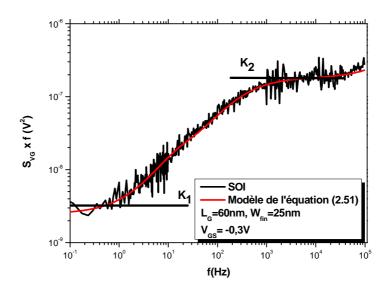

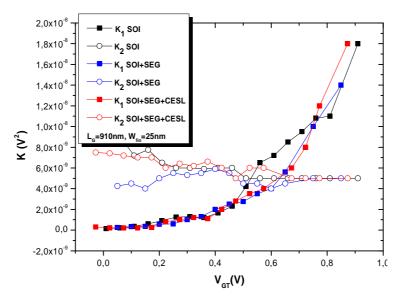

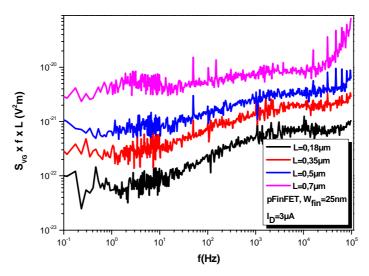

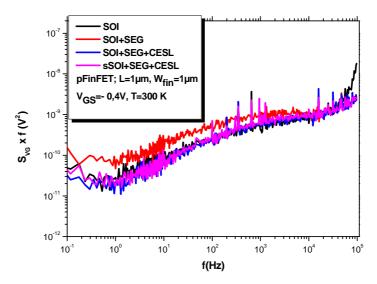

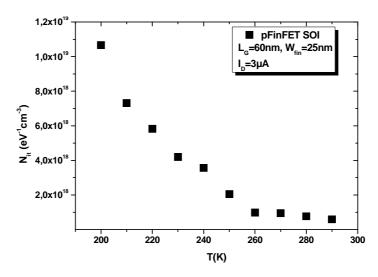

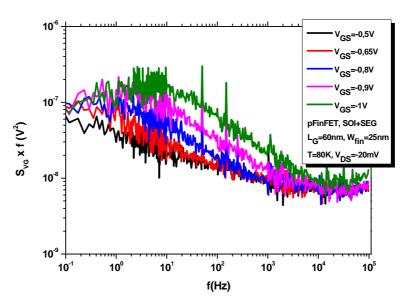

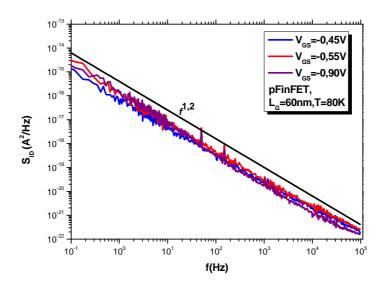

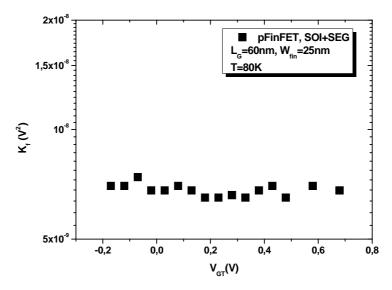

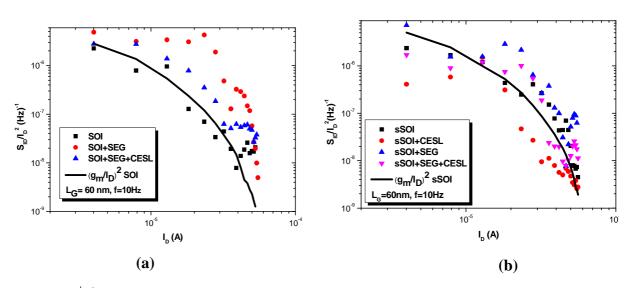

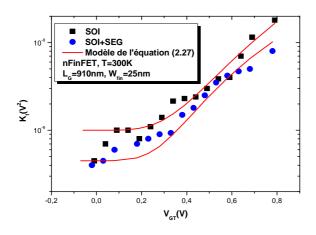

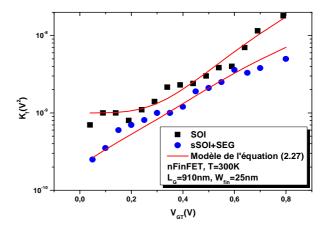

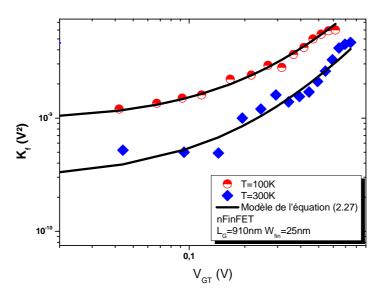

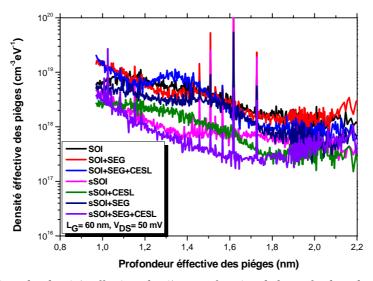

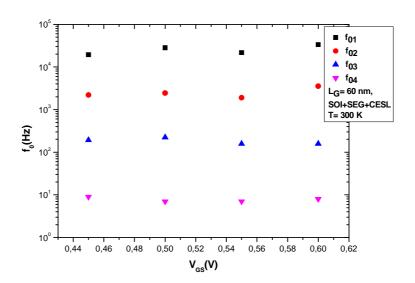

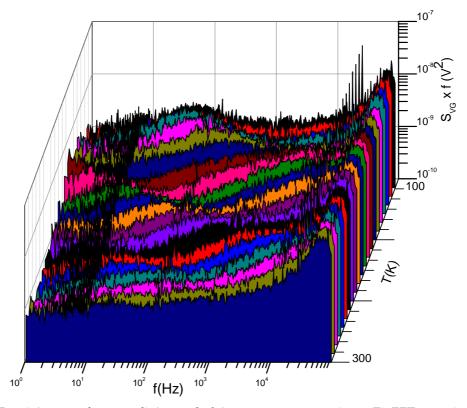

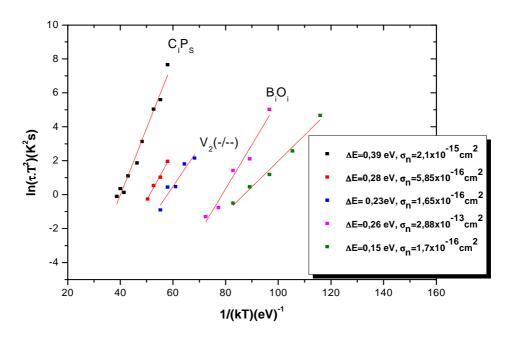

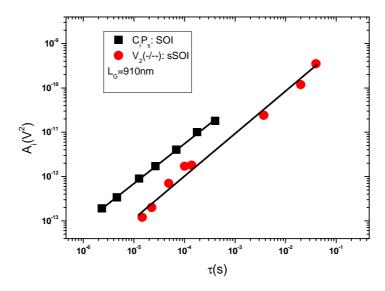

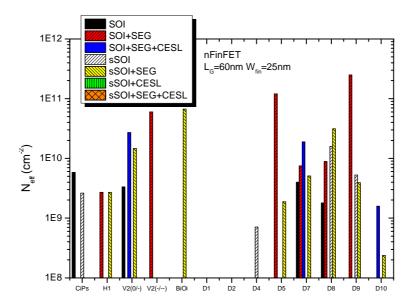

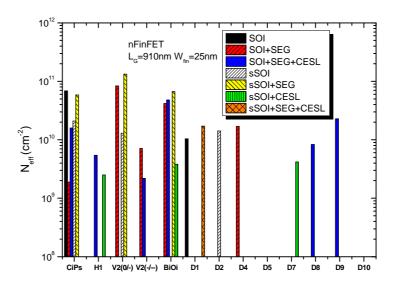

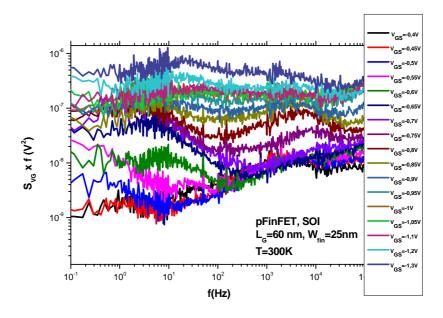

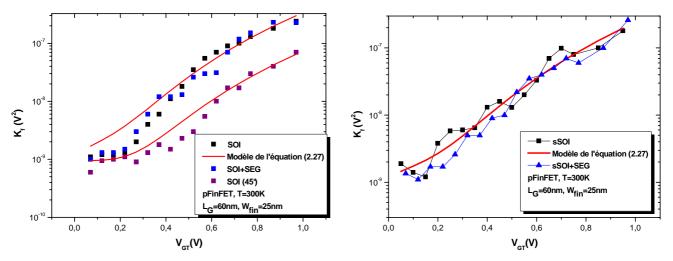

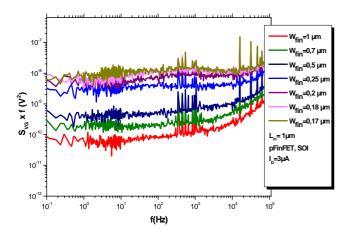

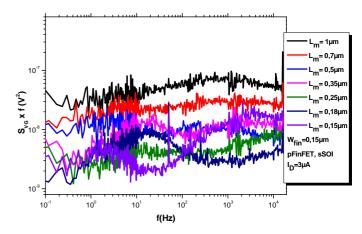

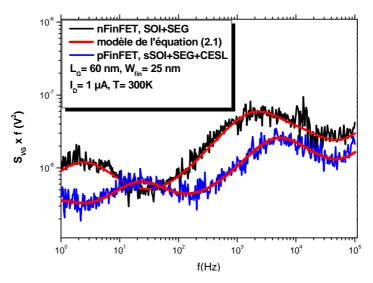

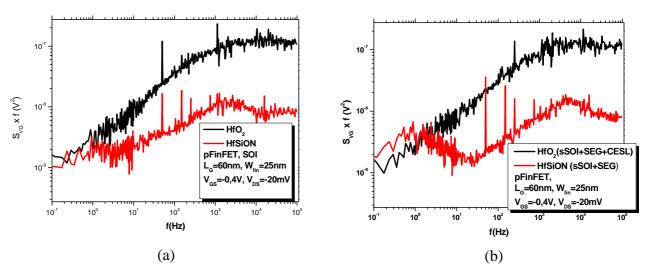

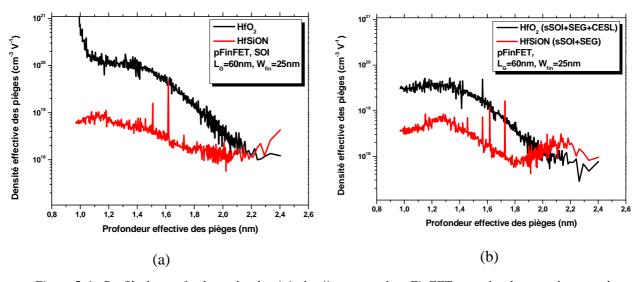

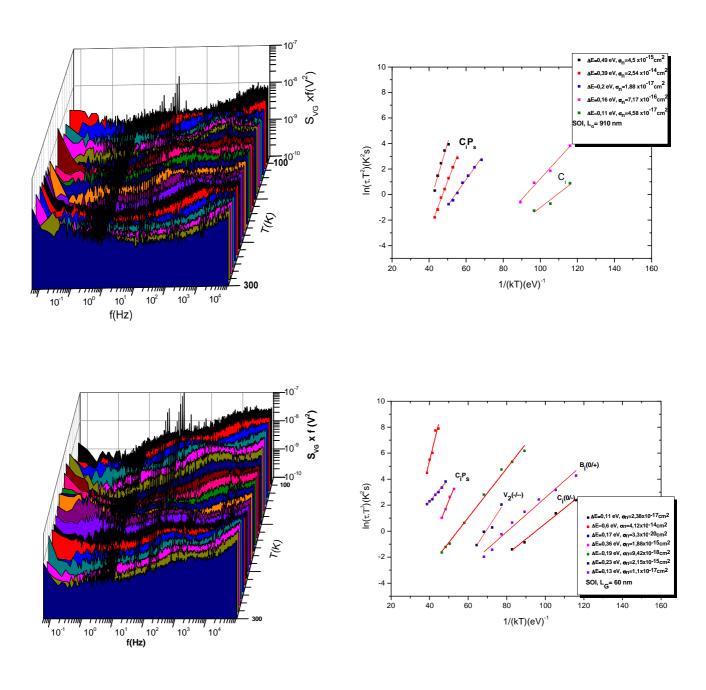

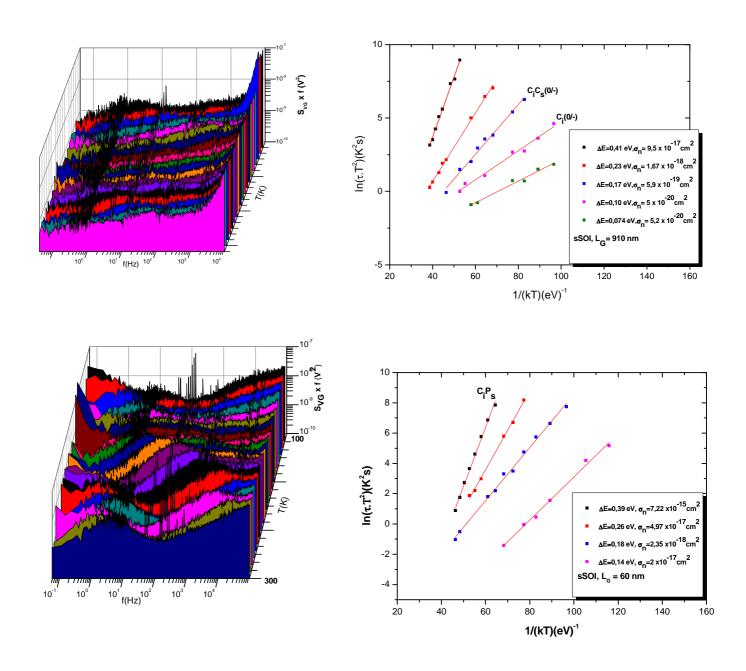

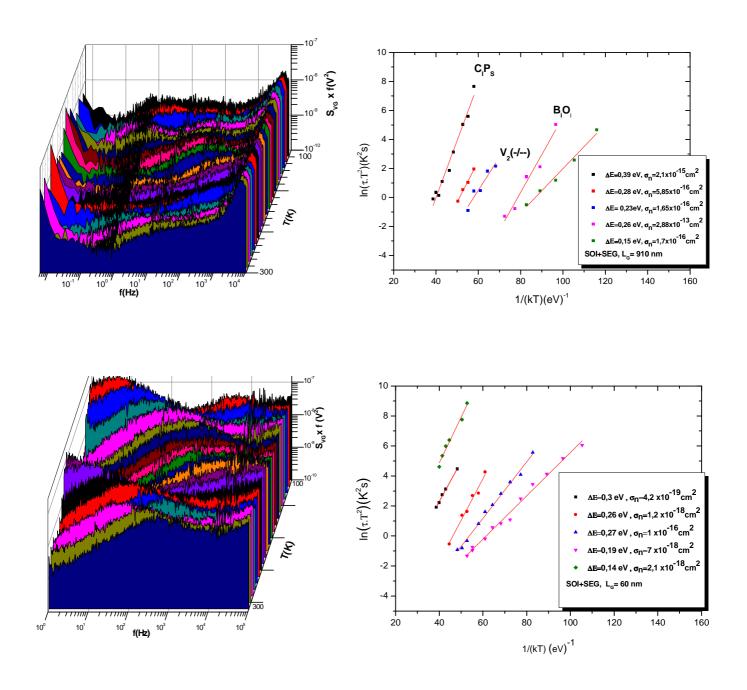

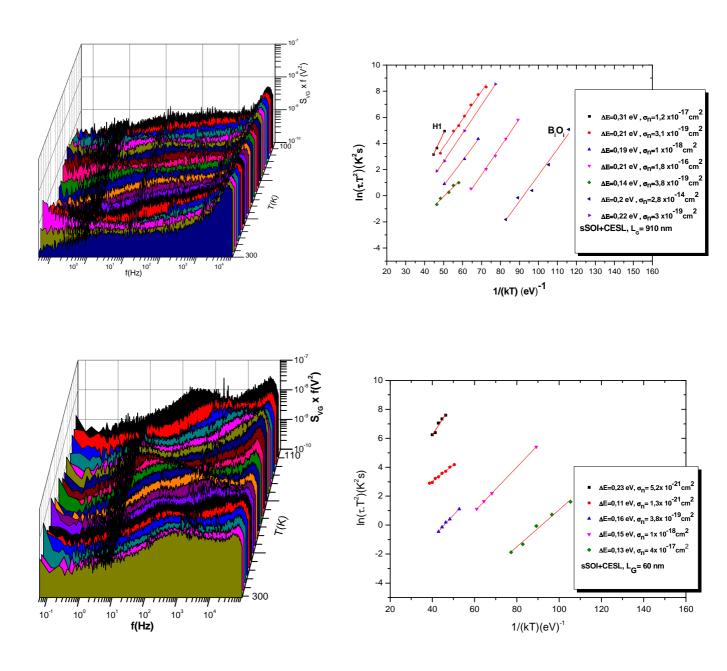

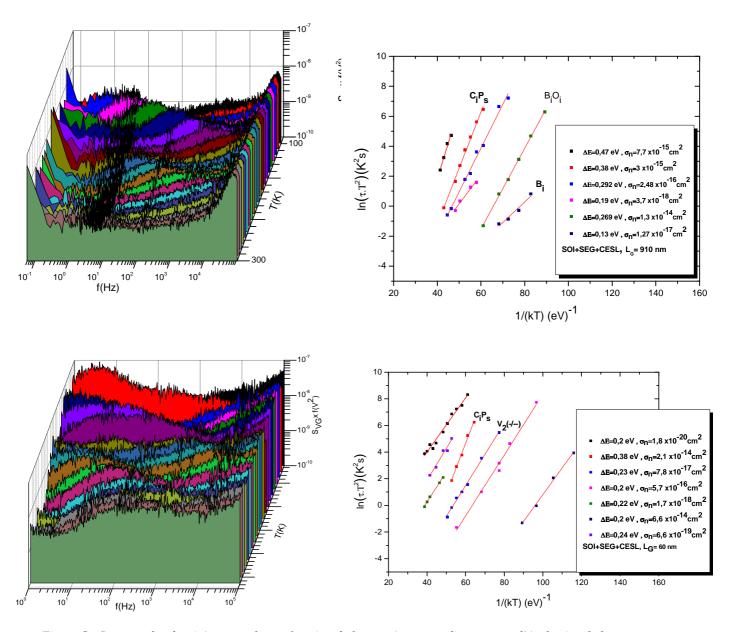

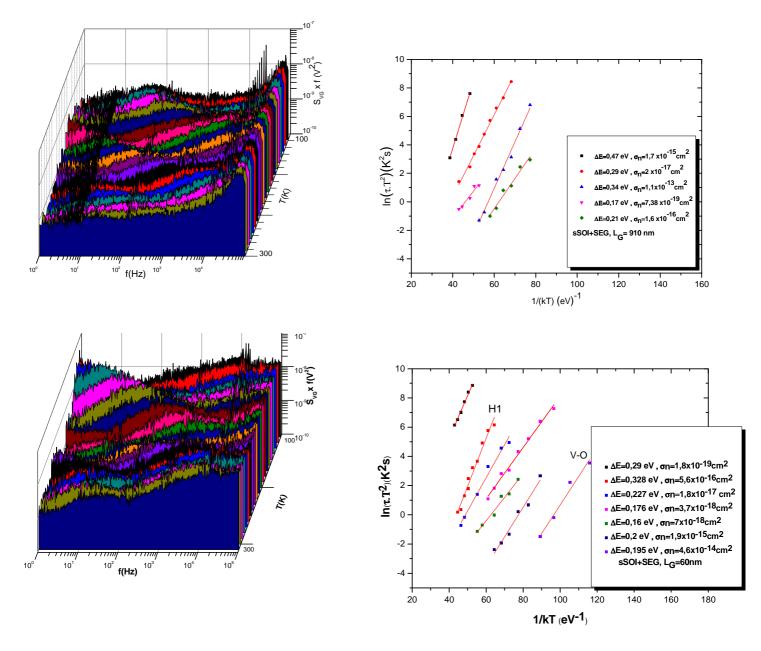

#### 1.4.5 Au delà du MOSFET classique