# Semantic foundations of intermediate program representations

Delphine Demange

#### ▶ To cite this version:

Delphine Demange. Semantic foundations of intermediate program representations. Other [cs.OH]. École normale supérieure de Cachan - ENS Cachan, 2012. English. NNT: 2012DENS0053. tel-00905442

### HAL Id: tel-00905442 https://theses.hal.science/tel-00905442

Submitted on 18 Nov 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE / ENS CACHAN - BRETAGNE

sous le sceau de l'Université européenne de Bretagne

pour obtenir le titre de

DOCTEUR DE L'ÉCOLE NORMALE SUPÉRIEURE DE CACHAN Mention : Informatique École doctorale MATISSE présentée par

### Delphine Demange

Préparée à l'Unité Mixte de Recherche 6074 Institut de recherche en informatique et systèmes aléatoires

### Semantic Foundations of Intermediate Program Representations

#### Thèse soutenue le 19 octobre 2012

devant le jury composé de :

**Xavier Leroy**Directeur de recherche - INRIA / rapporteur

#### John Gregory Morrisett

Professeur des universités - Harvard University / rapporteur

#### Luc BOUGÉ

Professeur des universités - ENS Cachan - Bretagne / examinateur

#### Albert COHEN

Directeur de recherche - INRIA / examinateur

#### Marie-Laure POTET

Professeur des universités - ENSIMAG / examinatrice

#### Thomas JENSEN

Directeur de recherche - INRIA / directeur de thèse

#### David PICHARDIE

Chargé de recherche - INRIA / co-directeur de thèse

Je tiens en premier lieu à remercier Xavier Leroy et Greg Morrisett d'avoir accepté de rapporter ma thèse, et de l'intérêt qu'ils ont porté à mon travail. C'est un grand honneur, et je les remercie très sincèrement pour les retours de grande qualité qu'ils m'ont donnés à propos du manuscrit. Je remercie également Albert Cohen et Marie-Laure Potet d'avoir accepté d'être examinateurs à ma soutenance et de l'intérêt qu'ils ont porté à ma présentation. Je remercie aussi Luc Bougé d'avoir bien voulu présider ce jury, 6 années après m'avoir ouvert les portes de l'ENS Cachan Antenne Bretagne et du Magistère Informatique et Télécommunications.

Cette thèse ne serait pas sans mes deux encadrants, Thomas Jensen et David Pichardie. Ces trois ans de travail à leur côté ont été très intenses, car passionnants. Je les remercie de m'avoir montré les directions à suivre, mais aussi pour leur disponibilité, leur enthousiasme, les conseils précieux qu'ils m'ont donnés, leurs encouragements, et toutes les opportunités de de collaborations, en France ou à l'étranger, qu'ils m'ont offertes durant ces trois ans. Leurs retours sur les versions préliminaires du manuscrit en ont considérablement amélioré la qualité, et je les en remercie.

Je remercie également Gilles Barthe, avec qui collaborer a été très enrichissant et un réel plaisir. Durant presque une année de collaboration, ses visites à Rennes et les nôtres à Madrid, Gilles m'a, par ailleurs, beaucoup appris par son expérience et ses conseils d'ordre extra scientifiques, et je lui en suis reconnaissante. Un grand merci aussi à Jan Vitek et Suresh Jagannathan pour cette aventure très riche passée à Purdue avec Vincent Laporte, David Pichardie et Lei Zhao. Je les remercie pour avoir réussi à me transmettre, grâce à leur expertise et nos nombreux échanges, des intuitions sur un sujet déroutant de prime abord. Je les remercie aussi pour leur accueil très chaleureux, leurs conseils, et le soutien académique qu'ils m'ont apporté.

Merci aussi à toute l'équipe Celtique, au sein de laquelle j'ai fait ma thèse. Merci à Frédéric Besson, Laurent Hubert, et aux ingénieurs de l'équipe avec qui j'ai pu travailler sur Sawja: Nicolas Barré, Tiphaine Turpin, Vincent Monfort et Pierre Vittet. Une mention spéciale à Arnaud Jobin, mon co-bureau hors-pair de presque 4 ans. Je remercie aussi Lydie Mabil pour sa patience, sa disponibilité et son aide efficace pour mes démarches administratives.

Un énorme merci à Philippe Aoustin, de l'atelier, pour avoir réussi à réssuciter ma machine de travail à 15 jours de la soutenance.

Finalement, je remercie mes parents et ma soeur d'avoir fait le déplacement jusqu'à Rennes pour assister à ma soutenance, mais aussi toute ma proche famille, qui aurait tant voulu y assister. Je les remercie de m'avoir soutenue depuis le début, et ce quelles que soient les circonstances. Je leur en suis infiniment reconnaissante, et leur dédie ce manuscrit.

## Contents

| R            | emer                              | ciements                                                  | 3  |  |  |  |  |  |  |  |  |

|--------------|-----------------------------------|-----------------------------------------------------------|----|--|--|--|--|--|--|--|--|

| $\mathbf{R}$ | ésum                              | né étendu en français                                     | 9  |  |  |  |  |  |  |  |  |

| 1            | Introduction                      |                                                           |    |  |  |  |  |  |  |  |  |

|              | 1.1                               | Formal verification of software                           |    |  |  |  |  |  |  |  |  |

|              |                                   | 1.1.1 Compilers and program verifiers                     | 15 |  |  |  |  |  |  |  |  |

|              |                                   | 1.1.2 Verified compilers and verifiers                    |    |  |  |  |  |  |  |  |  |

|              | 1.2                               | Intermediate representations to the rescue                | 19 |  |  |  |  |  |  |  |  |

|              | 1.3                               | Contributions and structure of the document               | 20 |  |  |  |  |  |  |  |  |

| <b>2</b>     | Inte                              | ermediate representations                                 | 23 |  |  |  |  |  |  |  |  |

|              | 2.1                               | A first informal definition                               | 23 |  |  |  |  |  |  |  |  |

|              | 2.2                               | Some leading IRs                                          | 24 |  |  |  |  |  |  |  |  |

|              |                                   | 2.2.1 Three-address code: TAC                             | 25 |  |  |  |  |  |  |  |  |

|              |                                   | 2.2.2 Stack-based code: STACK                             | 26 |  |  |  |  |  |  |  |  |

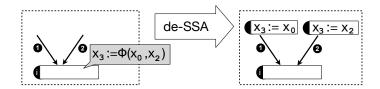

|              |                                   | 2.2.3 Static Single Assignment: SSA                       | 28 |  |  |  |  |  |  |  |  |

|              |                                   | 2.2.4 Continuation-passing style: CPS                     | 29 |  |  |  |  |  |  |  |  |

|              |                                   | 2.2.5 Cost analysis: Costa                                | 32 |  |  |  |  |  |  |  |  |

|              |                                   | 2.2.6 Program verification: Boogie                        | 33 |  |  |  |  |  |  |  |  |

|              | 2.3                               | Discussion                                                |    |  |  |  |  |  |  |  |  |

|              |                                   | 2.3.1 The semantic impact of syntax and structure         | 35 |  |  |  |  |  |  |  |  |

|              |                                   | 2.3.2 A perfect IR?                                       | 36 |  |  |  |  |  |  |  |  |

|              | 2.4                               | Conclusions                                               | 37 |  |  |  |  |  |  |  |  |

| 3            | Proving transformations correct 3 |                                                           |    |  |  |  |  |  |  |  |  |

|              | 3.1                               | Semantics preservation                                    | 39 |  |  |  |  |  |  |  |  |

|              |                                   | 3.1.1 Formal semantics                                    | 40 |  |  |  |  |  |  |  |  |

|              |                                   | 3.1.2 Observational semantics                             | 41 |  |  |  |  |  |  |  |  |

|              |                                   | 3.1.3 Choosing the right preservation criteria            | 43 |  |  |  |  |  |  |  |  |

|              | 3.2                               | Simulation relations                                      | 45 |  |  |  |  |  |  |  |  |

|              |                                   | 3.2.1 Simulations for semantics preservation              | 45 |  |  |  |  |  |  |  |  |

|              |                                   | 3.2.2 Simulations as semantic transformations             |    |  |  |  |  |  |  |  |  |

|              | 3.3                               | Proof techniques for transformation                       | 49 |  |  |  |  |  |  |  |  |

|              |                                   | 3.3.1 Provably correct transformations                    | 49 |  |  |  |  |  |  |  |  |

|              |                                   | 3.3.2 Translation validation                              |    |  |  |  |  |  |  |  |  |

|              | 3.4                               | Related work and conclusion                               |    |  |  |  |  |  |  |  |  |

|              |                                   | 3.4.1 Relational approaches to transformation correctness |    |  |  |  |  |  |  |  |  |

|              |                                   | 3.4.2 Summary                                             |    |  |  |  |  |  |  |  |  |

| 4 | $\mathbf{A} \mathbf{s}$ | tackless IR for Java bytecode 53                               |  |  |  |  |  |  |  |  |  |  |  |

|---|-------------------------|----------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|   | 4.1                     | Introduction                                                   |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.1.1 Key problems to address                                  |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.1.2 Contribution and content                                 |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.2                     | The source and target languages                                |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.2.1 Languages syntax                                         |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.2.2 Semantics                                                |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.2.2.1 Semantic domains                                       |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.2.2.2 Transition relations                                   |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.2.2.3 Semantics of BC                                        |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.2.2.4 Semantics of BIR                                       |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.3                     | The BC2BIR algorithm                                           |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.0                     | 4.3.1 Transforming instructions                                |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.3.2 Transforming method code                                 |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.4                     | Semantic correctness of BC2BIR                                 |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.4                     |                                                                |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.4.1 Semantic relations                                       |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.4.2 Soundness result                                         |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.4.3 Application examples                                     |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.5                     | The Sawja tool bench                                           |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.5.1 Overview of the library                                  |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.5.2 From BC to JBC                                           |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.5.3 Experiments                                              |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.6                     | Related work                                                   |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.6.1 Transformation and analysis frameworks                   |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 4.6.2 Transformation techniques and proofs                     |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.7                     | Conclusions                                                    |  |  |  |  |  |  |  |  |  |  |  |

| 5 | Stat                    | Static Single Assignment form 83                               |  |  |  |  |  |  |  |  |  |  |  |

| J | 5.1                     | Introduction                                                   |  |  |  |  |  |  |  |  |  |  |  |

|   | 0.1                     | 5.1.1 Powerful properties require care                         |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.1.2 Verified compilers need semantic properties              |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.1.3 Contributions                                            |  |  |  |  |  |  |  |  |  |  |  |

|   |                         |                                                                |  |  |  |  |  |  |  |  |  |  |  |

|   | <b>F</b> 0              | 5.1.4 Contents                                                 |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.2                     | Background on SSA                                              |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.3                     | The CompCert C compiler                                        |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.3.1 Observational semantics                                  |  |  |  |  |  |  |  |  |  |  |  |

|   | _ ,                     | 5.3.2 Behavior preservation                                    |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.4                     | The RTL language                                               |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.4.1 Syntax and semantics                                     |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.4.2 Normalizing RTL syntax                                   |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.5                     | The SSA language                                               |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.5.1 SSA programs                                             |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.5.1.1 Syntax                                                 |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.5.1.2 Strict SSA                                             |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.5.1.3 Well-formed SSA programs                               |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.5.2 Semantics                                                |  |  |  |  |  |  |  |  |  |  |  |

|   |                         | 5.5.2.1 Exploiting normalization for an intuitive semantics 94 |  |  |  |  |  |  |  |  |  |  |  |

|   |      |        | 5.5.2.2     | Parallel execution of $\phi$ -blocks                                                                                                          |

|---|------|--------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5.6  | Transl | ation vali  | dation of the SSA generation                                                                                                                  |

|   |      | 5.6.1  | Type sys    | stem                                                                                                                                          |

|   |      |        | 5.6.1.1     | Liveness                                                                                                                                      |

|   |      |        | 5.6.1.2     | Typing rules for instructions                                                                                                                 |

|   |      |        | 5.6.1.3     | Typing rules for edges and functions                                                                                                          |

|   |      | 5.6.2  | The type    | e system ensures strict SSA form                                                                                                              |

|   |      | 5.6.3  | Soundne     | ess of the type system                                                                                                                        |

|   |      |        | 5.6.3.1     | Simulation relation                                                                                                                           |

|   |      |        | 5.6.3.2     | Proof sketch                                                                                                                                  |

|   |      | 5.6.4  | -           | seness of the type system $\dots \dots \dots$ |

|   |      | 5.6.5  | -           | entation                                                                                                                                      |

|   | 5.7  | SSA-b  | -           | mizations and the equational lemma                                                                                                            |

|   |      | 5.7.1  | •           | nal lemma                                                                                                                                     |

|   |      | 5.7.2  |             | tion to Copy Propagation                                                                                                                      |

|   |      | 5.7.3  |             | on of Global Value Numbering                                                                                                                  |

|   |      | 5.7.4  |             | on                                                                                                                                            |

|   | 5.8  |        |             | of SSA                                                                                                                                        |

|   |      | 5.8.1  |             | edges $\dots \dots \dots$                     |

|   |      | 5.8.2  |             | p problem                                                                                                                                     |

|   |      | 5.8.3  |             | ness proof                                                                                                                                    |

|   | 5.9  | -      |             | and experimental results                                                                                                                      |

|   |      | 5.9.1  |             | ey of the SSA validator                                                                                                                       |

|   |      | 5.9.2  |             | eness of the GVN optimizer                                                                                                                    |

|   |      | 5.9.3  |             | ey of the generated code                                                                                                                      |

|   |      |        |             |                                                                                                                                               |

|   | 5.11 | Concli | isions and  | d future work                                                                                                                                 |

| 6 | Mer  | norv n | nodel for   | r concurrent Java IRs 113                                                                                                                     |

|   | 6.1  | •      |             | weak memory models                                                                                                                            |

|   |      | 6.1.1  |             | re memory models                                                                                                                              |

|   |      |        | 6.1.1.1     | Relaxing SC                                                                                                                                   |

|   |      |        | 6.1.1.2     | Total Store Order                                                                                                                             |

|   |      |        | 6.1.1.3     | DRF guarantee                                                                                                                                 |

|   |      | 6.1.2  | Software    | e memory models                                                                                                                               |

|   |      |        | 6.1.2.1     | SC-enforcing compilers                                                                                                                        |

|   |      |        | 6.1.2.2     | SC for correctly synchronised programs                                                                                                        |

|   |      |        | 6.1.2.3     | Weak DRF memory models                                                                                                                        |

|   |      |        | 6.1.2.4     | The limits of the Java Memory Model                                                                                                           |

|   | 6.2  | An alt | ernative of | contract: BMM                                                                                                                                 |

|   |      | 6.2.1  | BMM fr      | om a larger perspective                                                                                                                       |

|   |      | 6.2.2  |             | y                                                                                                                                             |

|   |      | 6.2.3  | Contribu    | itions and content                                                                                                                            |

|   | 6.3  | _      |             | Java Memory Model                                                                                                                             |

|   |      | 6.3.1  |             | read actions                                                                                                                                  |

|   |      | 6.3.2  |             | read semantics                                                                                                                                |

|   | 6.4  | Axiom  | atic mem    | ory model: BMM                                                                                                                                |

|            |       | 6.4.1                | BMM is a least post-fix<br>point $\ \ldots \ \ldots$ . |  |  |  |  |  |  |           |

|------------|-------|----------------------|--------------------------------------------------------|--|--|--|--|--|--|-----------|

|            |       | 6.4.2                | BMM is a subset of JMM                                 |  |  |  |  |  |  |           |

|            |       | 6.4.3                | DRF guarantee                                          |  |  |  |  |  |  |           |

|            | 6.5   | -                    | tional memory model: BMM <sub>o</sub>                  |  |  |  |  |  |  |           |

|            | 6.6   | BMM                  | and BMM <sub>o</sub> are equivalent                    |  |  |  |  |  |  |           |

|            |       | 6.6.1                | $\rho(BMM_o) \subseteq BMM \dots \dots$                |  |  |  |  |  |  | <br>. 137 |

|            |       | 6.6.2                | $BMM \subseteq \rho(BMM_o) \dots \dots \dots \dots$    |  |  |  |  |  |  | <br>. 139 |

|            | 6.7   | Validit              | y of transformations                                   |  |  |  |  |  |  | <br>. 139 |

|            |       | 6.7.1                | Validity of WR and WR*R                                |  |  |  |  |  |  | <br>. 140 |

|            |       | 6.7.2                | Proving transformations invalid                        |  |  |  |  |  |  | <br>140   |

|            | 6.8   | Empiri               | ical evaluation of BMM                                 |  |  |  |  |  |  | <br>. 141 |

|            | 6.9   | Relate               | d work                                                 |  |  |  |  |  |  | <br>. 142 |

|            | 6.10  | Conclu               | sion                                                   |  |  |  |  |  |  | <br>143   |

| 7          | Con   | clusion              | as and perspectives                                    |  |  |  |  |  |  | 145       |

|            | 7.1   |                      | ary                                                    |  |  |  |  |  |  | <br>145   |

|            | 7.2   |                      | ctions between IRs and analyses                        |  |  |  |  |  |  |           |

|            |       | 7.2.1                | Semantics preservation and program proof.              |  |  |  |  |  |  |           |

|            |       | 7.2.2                | IR as an analysis                                      |  |  |  |  |  |  |           |

|            | 7.3   | Extens               | sions                                                  |  |  |  |  |  |  |           |

|            |       | 7.3.1                | A verified front-end for Sawja                         |  |  |  |  |  |  |           |

|            |       | 7.3.2                | Concurrent BIR                                         |  |  |  |  |  |  |           |

|            |       | 7.3.3                | SSA deconstruction                                     |  |  |  |  |  |  |           |

|            |       | 7.3.4                | SSA-based optimizations                                |  |  |  |  |  |  |           |

|            | 7.4   | Perspe               | ective: towards more abstract IRs                      |  |  |  |  |  |  |           |

|            |       | _                    |                                                        |  |  |  |  |  |  |           |

| 8 Appendix |       |                      |                                                        |  |  |  |  |  |  | 153       |

|            | 8.1   | Correc               | tness of BC2BIR                                        |  |  |  |  |  |  | <br>. 153 |

|            | 8.2   | Compl                | eteness of the SSA validator                           |  |  |  |  |  |  | <br>. 157 |

|            |       | 8.2.1                | Specification of Cytron et al.'s algorithm             |  |  |  |  |  |  | <br>. 157 |

|            |       | 8.2.2                | Building a witness global typing                       |  |  |  |  |  |  | <br>. 158 |

|            |       | 8.2.3                | The witness global typing is a correct typing          |  |  |  |  |  |  | <br>. 159 |

|            | 8.3   | $\operatorname{BMM}$ | and $BMM_o$ are equivalent                             |  |  |  |  |  |  | <br>. 161 |

| Ri         | hling | raphy                |                                                        |  |  |  |  |  |  | 164       |

| 1/1        | Ug    | - apiny              |                                                        |  |  |  |  |  |  | 104       |

### Résumé étendu en français

#### Motivations

#### Contexte général

Nos vies quotidiennes dépendent de plus en plus, sans même parfois que nous nous en rendions compte, de l'utilisation de programmes informatiques. Ces programmes n'ont toutefois pas tous le même niveau de criticité. Par exemple, les programmes embarqués dans les sytèmes bancaires, dans les systèmes de contrôle de vol des avions, ou même dans la chirurgie assistée par ordinateur ou les centrales nucléaires sont appelés systèmes critiques: la présence d'erreur durant leur exécution pourrait avoir des conséquences désastreuses, que ce soit en termes de vies humaines, de dégâts écologiques, ou de coût financier. Ce type de programme requiert donc de fortes garanties: leur exécution ne devrait pas échouer, et leur correction fonctionelle devrait être garantie.

De manière générale, nous nous intéressons dans ces travaux à la vérification formelle de logiciel, c'est à dire à l'ensemble des techniques et d'outils scientifiques qui permettent d'assurer qu'un logiciel remplit ces exigences. Cela consiste en l'utilisation d'outils mathématiques dans le but de prouver l'absence d'erreur dans les programmes, sans même avoir à les exécuter. Ces techniques, dites statiques, comprennent par exemple la vérification de modèle, l'analyse statique, ou la preuve formelle de programme.

La vérification formelle de programme connaît un succès grandissant dans le milieu industriel. Astrée [BCC<sup>+</sup>03] est un des analyseurs statiques en pointe. En 2003, il a été utilisé pour vérifier l'absence d'erreur dans le code embarqué dans le système de contrôle de vol de l'Airbus A340, un programme C de 132 000 lignes. Un autre exemple est Caveat [BPR<sup>+</sup>02], qui été appliqué également chez Airbus pour la vérification de programmes C critiques.

#### Vérifier formellement les compilateurs et les analyseurs

Pour que la garantie apportée par la vérification formelle de programmes soit complète, il convient de considérer les deux problèmes suivants. Tout d'abord, l'outil de vérification est lui-même un programme, il pourrait donc contenir des bugs. Ensuite, les programmes sont généralement vérifiés au niveau source, avant d'être compilés en code machine exécutables. Le compilateur utilisé pourrait également introduire des bugs lors de la phase de compilation.

Ces problèmes sont d'autant plus importants que les compilateurs et vérifieurs modernes sont des programmes très complexes, de part les langages très haut niveau qu'ils doivent traiter, la difficulté des propriétés à analyser, et les besoin en performance qu'ils doivent en plus assurer (le temps d'analyse ou de compilation devrait rester raisonable).

Parce que les compilateurs et les vérifieurs interviennent dans la génération ou la vérification de programmes critiques, ils demandent le même niveau de garantie que les programmes critiques eux-mêmes. Le principe est donc d'appliquer la vérification formelle à ces outils. La vérification formelle des compilateurs et vérifieurs est le sujet général auquel nous nous intéressons dans cette thèse.

#### Les représentation intermediaires de programmes

Les compilateurs et vérifieurs de programmes sont des programmes complexes. Pour simplifier l'analyse et la transformation de code, ils font appel à des représentations intermédiaires (IR) de programmes. Par exemple, la chaîne de compilation est décomposée en plusieurs étapes clef, chacune traitant un aspect particulier du langage. Ainsi, le programme source n'est compilé en un code machine que progressivement. Typiquement, les constructions redondantes du langage sont d'abord unifiées; puis, les expressions riches sont décomposées en expressions de base, auxquelles on peut faire correspondre des instructions du processeur cible; plus tard a lieu l'allocation de registres, où la contrainte du nombre de registres physiques du processeur est prise en compte. A chaque phase de la chaîne de compilation correspond une représentation, ou un langage, intermédiaire. Certaines IRs sont particulièrement bien adaptées à l'optimisation et la transformation de code. Les IRs sont aussi beaucoup utilisées dans les vérifieurs et analyseurs de programmes, qui se sont inspirés des choix effectués dans les compilateurs. Parfois, les vérifieurs définissent des IRs spécifiques à leur besoin, en les adaptant par exemple au type de propriétés à analyser. Les IRs sont alors conçues pour rendre moins coûteux les calculs à effectuer sur les programmes.

Le Chapitre 2 de ce document est dédié à la notion générale de représentation intermédiaires. Nous y donnons un aperçu, nécessairement partiel, des IRs utilisées dans les compilateurs et vérifieurs modernes. Nous présentons leur avantages, et aussi leur inconvénients ou les difficultés posées par leur utilisation. Il n'existe en effet pas d'IR qui soit adaptée à tout type d'analyse, d'optimisation, ou de transformation. Ce chapitre tente, par le biais de cet aperçu, de caractériser, ou définir ce qu'est une IR. Essentiellement, une IR est un langage orienté analyse (car la transformation de programme requiert la plupart du temps une forme d'analyse, aussi simple soit elle), qui possède des propriétés structurelles et sémantiques.

#### Fondements sémantiques des IRs

Le point de vue que nous défendons dans ces travaux est que la preuve formelle des compilateurs et des vérifieurs ou analyseurs réalistes, c'est à dire tels que ceux qui sont utilisés en pratique (avec une distance idéallement nulle entre la formalisation et le code propre de ces programmes), ne peut être envisagée sans considérer les IRs comme levier. En effet, si les IRs sont utilisées en pratique, ce sont pour leur propriétés sémantiques. Ainsi, les IRs ne simplifient pas uniquement l'implantation des algorithmes de transformation ou d'analyse, mais elles devraient aussi en simplifier la preuve de correction.

Pour soutenir ce point de vue, nous étudions d'un point de vue sémantique et formel les IRs. Nous sommes évidemment contraints d'effectuer un choix dans les études de cas que nous menons. Aussi, nous choissisons d'étudier trois aspects ou problématiques récurrentes, que nous détaillons dans la section suivante.

Pour chacun des cas d'étude, notre approche est la suivante. Nous voulons d'abord formaliser la sémantique de l'IR. Cette formalisation doit être fidèle à la réalité, ou capturer l'intuition généralement admise dans la littérature. Puis, nous formalisons les algorithmes de génération de ces IRs, et les prouvons corrects vis à vis d'un critère sémantique adapté (il arrive qu'une IR modifie en un certain sens la sémantique du programme initial). Les algorithmes formalisés doivent être à l'état de l'art, pour s'inscrire dans notre démarche. Un autre objectif pour ces formalisations est de pouvoir les utiliser pour prouver des analyses ou des optimisations correctes. Cela demande que la sémantique soit suffisamment simple à utiliser.

Egalement, cela requiert d'identifier les propriétés sémantiques des IRs, et de les isoler dans des lemmes sémantiques, facilement applicables. Finalement, nous validerons nos formalisations de manière expérimentale, vis à vis de critères de succès tels que le temps de génération, ou l'efficacité du code généré.

Le Chapitre 3 rappelle les notions de base de sémantique formelle. Nous y discutons également différents critères de préservation sémantique pour les transformations de programmes. Finalement, nous rappelons aussi la technique de preuve principale que nous utilisons dans notre travail, qui repose sur des diagrammes de simulation entre systèmes de transition.

#### Résumé des contributions

#### Une IR basée registres pour le bytecode Java

Le Chapitre 4 présente notre travail sur BIR, une IR basée registres pour le bytecode Java. L'algorithme de génération de l'IR utilise une technique d'évaluation symbolique du bytecode, inspirée du travail de Whaley [Wha99] pour le compilateur optimisant de la machine virtuelle Jikes RVM [Jik]. Dans cette IR, les arbres d'expressions sont reconstruits tout en restant sans effet de bord. De plus, le processus de création d'objet, i.e. allocation de l'objet, construction des paramètres d'initialisation, puis appel du constructeur, est décompilé en une seule instruction.

Nous présentons la preuve de correction sémantique de la transformation. Notre théorème sémantique explicite ce que la transformation préserve (comme l'initialisation des objets, et l'ordre de levée des exceptions) mais aussi ce qu'elle modifie et comment (par exemple, l'ordre d'allocation des objets).

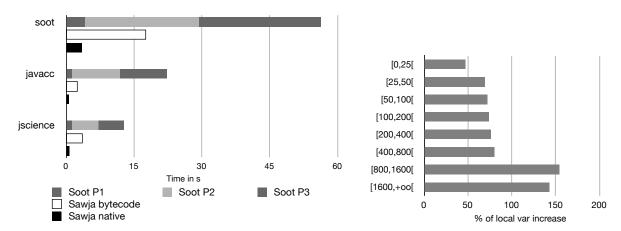

Nous avons implémenté l'IR dans Sawja, un outil de développement d'analyses statiques pour Java développé au sein de l'équie projet Celtique, et une évaluation empirique de ses performances, en terme d'efficacité de génération, et de compacité du code obtenu (mesuré en nombre de variables temporaires introduites pour les besoins de la transformation). Nous veillons à ce que la formalisation modélise fidèlement la version implanté de la transformation.

#### La représentation SSA

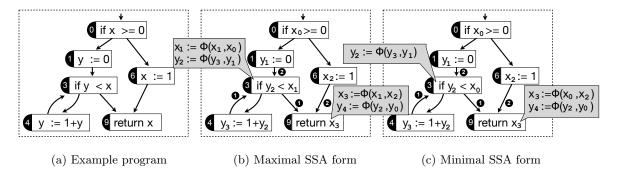

Puis, nous nous intéressons à la forme Single Static Assignment (SSA), une IR au coeur des compilateurs et vérifieurs modernes. Dans cette IR, chaque variable du programme ne possède qu'un unique point de définition (statique). Chaque point de définition correspond ainsi à une nouvelle version de la variable initiale. Aux points de jonction du graphe de flôt de contrôle, des instructions virtuelles, les *phi-instructions*, sont utilisées pour assurer la sélection de la bonne version de variable, selon le chemin suivi par le flôt d'exécution. Bien que la forme SSA soit beaucoup utilisée en pratique, les travaux de formalisation de sa sémantique et de ses propriétés restent encore insuffisamment développés. Typiquement, l'intuition selon laquelle la forme SSA serait une forme equationnelle de programme n'a jamais été formalisée, ni même clairement énoncée.

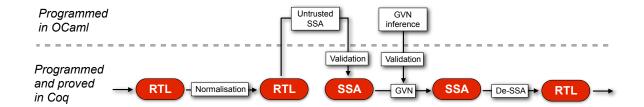

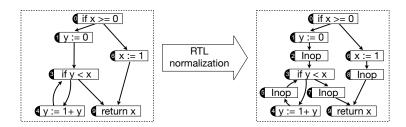

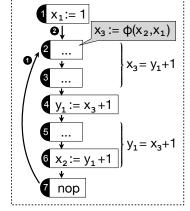

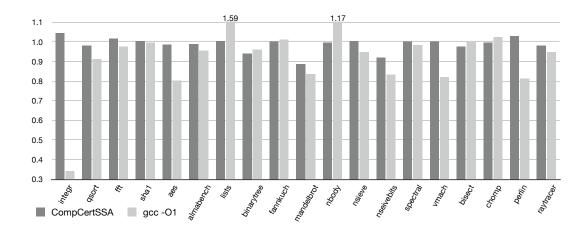

Dans le Chapitre 5, nous présentons les contributions suivantes. Nous implantons et prouvons correct dans l'assistant de preuve Coq un middle-end SSA pour le compilateur C CompCert. Ceci comprend donc la formalisation de la sémantique de SSA, ainsi que la preuve de préservation sémantique des algorithmes de génération et de destruction associés. Notamment, nous utilisons la technique de validation a posteriori pour l'algorithme de construction

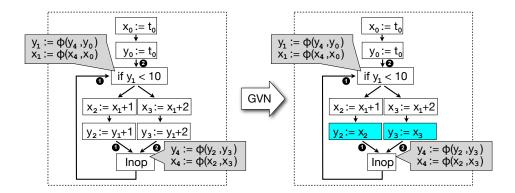

de la forme SSA. Nous avons aussi implanté et prouvé correcte une optimisation typique de la forme SSA, l'Elimination des Sous-expressions Communes (CSE), basée sur une technique de Numérotation Globale des Valeurs [AWZ88] (GVN).

Nous identifions et prouvons l'ingrédient clef pour la preuve de ce type d'optimisation, c'est à dire l'invariant global sémantique de SSA permettant de voir les programmes SSA comme définissant un ensemble d'équations. Notamment, nous montrons que les égalités ainsi "générées" par SSA ne sont pas valides à tout endroit du programme, mais uniquement dans les régions strictement dominées par les points de définition des variables impliquées dans les égalités.

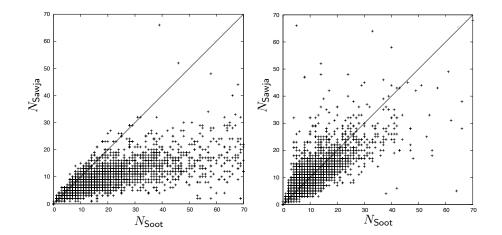

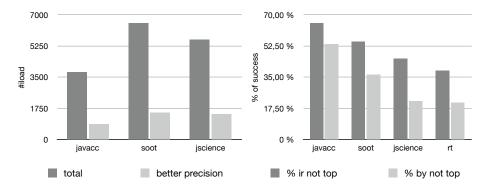

Grâce au mécanisme d'extraction fourni par Coq, nous obtenons une version OCaml du middle-end formalisé, complètement exécutable, et qui satisfait les propriétés que nous prouvons à son propos. Ceci nous permet également de conduire quelques expériences pour évaluer les performances du middle-end. Tout d'abord, le validateur SSA a un temps de calcul raisonable par rapport au temps de génération de la forme SSA. Ensuite, nous observons que l'optimisation CSE à base de GVN est capable d'optimiser davantage (en nombre d'instructions) l'ensemble de programmes que nous considérons. Finalement, les temps d'exécution des programmes compilés n'est pas drastiquement amélioré, mais les résultats préliminaires sont encourageants.

#### Un modèle mémoire pour les IRs de Java concurrent

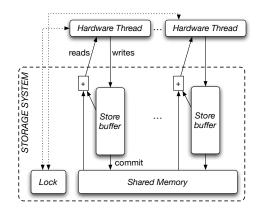

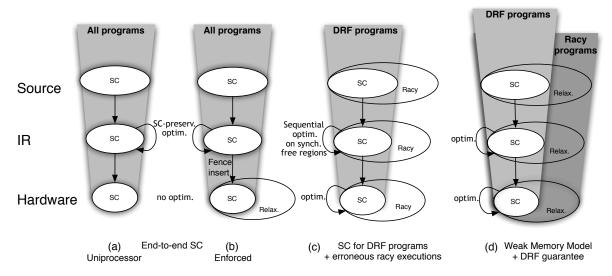

Enfin, nous étudions un aspect difficile des languages modernes auquel les compilateurs et les analyseurs modernes devront faire face de plus en plus, la concurrence. IdÃl'alement, la sémantique d'un language concurrent, dans lequel les fils d'exécution communiquent au travers d'une mémoire partagée, pourrait être modélisée par un simple entrelacement des fils d'exécution; ceux-ci auraient à chaque étape de calcul une vision cohérente de la mémoire. Cependant, pour certains langages, ce modèle dit séquentiellement consistant ne suffit pas à décrire tous les comportements des programmes. En effet, les architectures multi-processeurs modernes utilisent des mécanismes de tampons, de caches mémoire, et des mécanismes de spéculation, qui invalident ce modèle, car ils introduisent des comportements que l'on pourrait observer si certaines instructions du programme étaient exécutées dans un ordre différent de celui du code programme. Ces modèles de mémoire sont dits faiblement consistants. Nous donnons au début du Chapitre 6 une brève introduction à cette problématique, dans le cadre de la vérification de compilateurs.

Dans ce chapitre, nous nous penchons sur le cas du modèle mémoire Java (JMM), lui aussi faiblement consistant. Il a été formalisé en 2005 par Manson et al. [MPA05]. Les garanties de sécurité que se veut offrir Java demandent de définir aussi une sémantique pour les programmes dont les fils d'exécution peuvent entrer en conflit entre eux, lors d'accès simultanés à la mémoire partagée. Ceci complique la définition du JMM, puisque les relaxations du modèle mémoire apparaissent pour de tels programmes. La définition actuelle du Java Memory Model (JMM) autorise également les optimisations aggressives des compilateurs et des architectures parallèles sous-jacentes, sans faire a priori d'hypothèse sur une architecture cible particulière.

Ainsi, la sémantique des programmes Java concurrent est, strictement parlant, définie. Toutefois, cette sémantique est très complexe, trop pour pouvoir envisager, à ce jour, de manière raisonable, la preuve d'un compilateur vis à vis d'elle; elle fait d'ailleurs encore l'objet de travaux de recherche récents [AŠ07b, Šev08, TVD10]. Ces travaux montrent que cette définition n'est pas celle attendue (elle autorise des optimisations qui ne devraient pas être

permises, et en interdit d'autres qui le devraient), terriblement complexe, et qu'un compilateur actuel de référence, Sun Hotspot JVM, n'est pas conforme vis à vis de cette sémantique.

Devant ce constat, nous choisissons de fixer une famille d'architectures cibles, TSO (Total Store Order), dont le modèle de mémoire, bien que faiblement consistant, reste suffisamment simple pour envisager une preuve formelle de compilateur vis à vis de lui, comme en témoigne le travail de Ševčík et al. [ŠVZN+11]. Nous proposons un modèle de mémoire Java spécialisé pour ces architectures. Nous le caractérisons axiomatiquement par les réordonnancements d'actions mémoire qu'il autorise, et montrons qu'il constitue un sous-ensemble du JMM. Ainsi, la solution proposée est sémantiquement valide, consistant en un raffinement sémantique des programmes. Dans le but de pouvoir conduire des preuves formelles dans la lignée de Ševčík et al., nous montrons également qu'il peut être défini de manière opérationnelle, et prouvons l'équivalence avec le modèle axiomatique. Ces preuves s'appliquent à toutes les couches objet du compilateur, étant donné que le modèle mémoire est paramétrisé par la sémantique intrathread (les actions locales aux threads) des programmes. Finalement, une validation expérimentale préliminaire a été conduite, montrant que, sur les architectures TSO, en choisissant avec soin les optimisations du compilateur, le coût d'implanter ce modèle est raisonnable, en comparaison avec le JMM.

#### Notes à propos des chapitres 4, 5, and 6

Matériel disponible en ligne. Du matériel additionnel pour ces chapitres est disponible en ligne. Les liens spécifiques sont précisés dans les chapitres.

**Preuves.** Ces trois chapitres contiennent des résumés étendus des preuves réalisées pendant cette thèse. Les preuves complètes des résultats apparaissent, soit en Annexe de ce document, soit dans les documents supplémentaires disponibles en ligne.

Publications. La contribution présentée dans le Chapitre 4 a été publiée dans les actes de la conférence internationale 8th Asian Symposium on Programming Languages and Systems (APLAS'10) et présentée à Shanghai en Décembre 2010 [DJP10]. La présentation technique plus complète de l'outil Sawja a été publiée dans les actes de la conférence internationale Conference on Formal Verification of Object-Oriented Software (FoVeOOS'10) [HBB+11]. Ont contribué à l'implémentation de Sawja et Javalib, en ordre alphabétique : Etienne André, Nicolas Barré, Frédéric Besson, Nicolas Cannasse, Delphine Demange, Laurent Hubert, Florent Kirchner, Vincent Monfort, David Pichardie et Tiphaine Turpin.

La contribution présentée dans le Chapitre 5 a été publiée dans les actes de la conférence internationale 21th European Symposium on Programming (ESOP'12) et présentée à Tallin en Mars 2012 [BDP12]. La preuve mécanisée en Coq de l'optimisation CSE basée sur GVN est principalement due à David Pichardie.

La contribution présentée en Chapitre 6 a été acceptée pour publication dans les actes de la conférence 40th ACM SIGPLAN-SIGACT Symposium on Principles of Programming Languages (POPL'13) [DLZ<sup>+</sup>13]. L'évaluation empirique, dont un résumé des résultats est présenté dans ce chapitre dans un souci de complétude, a été conduite par Vincent Laporte et Lei Zhao.

### Chapter 1

### Introduction

#### 1.1 Formal verification of software

Our daily lives rely more and more on the use of computer programs. Sometimes we do not even realize it. These programs are embedded in systems ranging from alarm clocks, washing machines, elevators and vending machines to smart cards, mobile banking, smart phones, automated driverless subways, computer-assisted surgery, aircraft flight control systems, or nuclear power plants. Obviously, these programs do not all have the same level of criticality. Among them, we distinguish safety-critical software, the category of programs whose malfunction can result in considerable losses, either financially or humanly. This category of software demands a high level of confidence in its execution. No error should arise at runtime (the system should not crash) and their functional correctness should be guaranteed (the system should compute the right information).

Formal software verification is a set of scientific techniques and tools that can be used to ensure that a software system fulfills these requirements. It consists in using mathematical tools for proving the absence of bugs in programs without actually executing the programs. These are static verification techniques that are based on either model-checking, static analysis or program proof. Formal software verification is becoming increasingly popular in the safety-critical industry. Astrée [BCC+03] is one of the leading static analyzers of safety-critical embedded software. In 2003, it was able to verify the absence of certain classes of errors in the primary flight control software of the Airbus A340 fly-by-wire system, a program of 132,000 lines of C code. Another example is Caveat [BPR+02], that has been applied at Airbus to verify safety-critical C programs.

To achieve an end-to-end guarantee, there are two sources of bugs that must be accounted for. First, there might be errors in the verification tool itself. Second, the formal verification is usually applied at the source level of the program, before it is compiled to an executable machine code. In the end, what matters is that the compiled program (the one who is executed) fulfills these requirements. Thus, the compilation should also be trustworthy.

We now discuss these two issues, and then how to tackle them. This will lead us to the topic of our thesis: the *intermediate representations* of programs on which these tools are built.

#### 1.1.1 Compilers and program verifiers

Compilers and program verifiers are equally important potential sources of bugs due to their complexity.

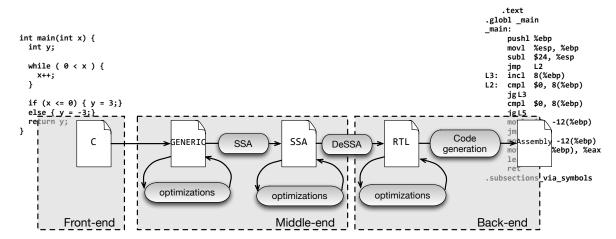

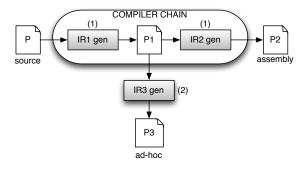

Figure 1.1: Distance between what the programmer writes and what the machine executes. A C source program (left) written by a programmer compiled by GCC into the assembly program (right).

Compilation errors Compilers are complex pieces of software for several reasons. First, they must translate the rich features of high-level languages, e.g. exception handling, object creation, function pointers or automatic memory management, down to the processor instruction set. In order to simplify this process, the compilation chain is split into several phases, each translation step focusing on a particular feature of the language to compile. To each step of the compilation corresponds an intermediate representation (IR) of the program.

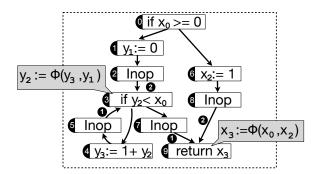

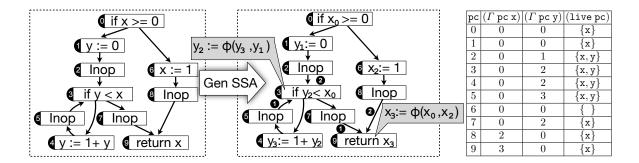

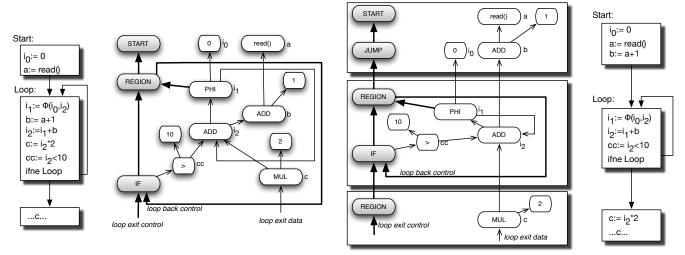

Figure 1.1 shows an example of source program written in C (left), and the corresponding x86 assembly code (right) generated by the GCC compiler [FSF]. GCC's IRs mainly comprise GENERIC, SSA (Static Single Assignment) and RTL (Register Transfer Language) formats. We will come back to these IRs in the rest of this document. Second, the generated code should be efficient, so the compiler performs code optimization. In Figure 1.1, optimizations are performed at each stage of the chain. But some IRs are particularly well suited to program optimization. SSA [AWZ88, CFR<sup>+</sup>91] is one of them. It comes with strong properties (in particular, variables definition points are unique) that analyses and optimizations can exploit for more precision and efficiency. The SSA optimization phase of GCC comprises around 100 passes [FSF]. Finally, the compilation time should be reasonable. The code of the compiler itself is thus usually optimized, in terms of algorithms and data structures.

The inherent complexity of compilers make their implementation error-prone. This can result in the failure of the compiler to process the input program: the compiler crashes. A more problematic outcome is miscompilation: the compiler succeeds to produce an output program, but this program behaves differently from the source program. The recent work of Yang et al. [YCER11] shows, using a randomized test-case generator, that these errors remain frequent in mainstream C compilers. They report:

We found and reported hundreds of previously unknown bugs [...]. Many of the bugs we found cause a compiler to emit incorrect code without any warning. 25 of the bugs we reported against GCC were classified as release-blocking.

**Verification errors** Formal verification relies on the use of mathematical tools for (i) stating the *specification* of the program, i.e. its expected behavior (ii) modelling the behaviors of the

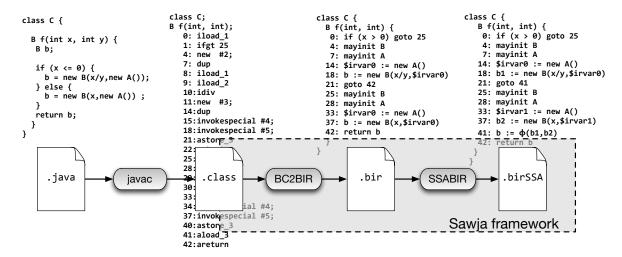

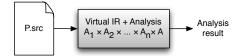

Figure 1.2: Java bytecode analysis and the IRs provided by the Sawja framework. A Java program (.java) is compiled into a Java bytecode program (.class), executable by the Java Virtual Machine. Some analyses cannot be performed at the source level (e.g. the source code could be unavailable to the client). Sawja provides high-level IRs of the bytecode to simplify the design and implementation of static analyses.

program, or its *semantics* and (iii) proving that the semantics of the program conforms to its specification. Once the program has been formally verified, it is mathematically ensured, relative to the model of the environment, not to crash, and to always – meaning for all the possible input parameters – yield a correct result, with regard to a formal specification. Formal verification techniques are numerous. They include model-checking, static analysis, or program proof. In this work, we consider program static analyzers and program proofs.

Static analyzers, automatically check that the program execution is free of run-time errors. Examples include the absence of division by zero, null pointer dereferencing, out-of-bound array accesses, or arithmetic overflows. The absence of run-time errors in a program is not decidable in general, so static analyzers must over-approximate the set of possible program executions into a domain in which properties become decidable. For instance, a set of values is abstracted into an interval of integers. In return, a coarse approximation can make the analyzer raise false-alarms. Program provers use deductive reasoning techniques, such as Hoare logic, to prove that programs satisfy their specification. Usually, these tools are less automatic than static analysis. The program is first annotated with its specification (that takes the form of pre- and post-conditions, as well as loop invariants). These annotations can express high level properties, such as the functional correctness of the program (e.g. this program sorts a list). Then, some verification conditions are automatically generated, and then solved either automatically or manually.

Program verification tools are programs too, and their implementation is a challenging task, for several reasons. Consider program analyzers. They should first be accurate, i.e. the abstraction should be precise, so that the analyzer does not raise too many false-alarms. Precise abstract domains, such as polyhedra, are algorithmically costly, and thus complex to implement efficiently and correctly. The APRON library [JM09] provides such features; the domains of convex polyhedra and linear equalities represent a total of 12,000 lines of delicate and optimized C code. Also, some analyses, such as the analysis of resource consumption or

worst-case execution time, need to be done on low-level code, where the timing information about the hardware and all its specific features are known. Low-level code can be harder to manipulate and to reason about in analyzers.

Increasingly, verification tools also rely on program transformations and IRs to either simplify their implementation design, or gain precision and efficiency. They either reuse the IRs from the compiler community, e.g. SSA, or define their own ones, specifically tailored to the language or the analyses to perform. We give some examples of such IRs and verifiers in Chapter 2. Figure 1.2 illustrates the use of Sawja, an OCaml library developed in the Celtique research group for developing Java Bytecode static analyzers. It provides high level IRs of the bytecode (BIR and an SSA form of BIR) which simplify the design and implementation of bytecode static analyses. In particular, these IRs are register-based, and avoid the need of reasoning on the operand stack of the bytecode. This kind of IR is very popular in low level code analysis frameworks (e.g. Soot [VRCG<sup>+</sup>99] or Wala [Fin]).

#### 1.1.2 Verified compilers and verifiers

Compilers and verification tools are thus complex programs. When they are used for compiling and analyzing critical software, they require the same level of confidence as the critical software itself. In order to reach a high-level of guarantee, the idea is then to apply formal verification techniques to the compilers and analyzers themselves.

They both manipulate the same notions: programs and semantics. Proving their correctness hence follows a similar pattern. First, the semantics of programs is formalized with e.g. transition systems. Then, the algorithms used in the compiler or analyzer are rigorously proved with respect to these formal semantics, using results coming from graph and lattice theory, Hoare logic, data-flow analyses [Kil73, NNH99], or abstract interpretation [CC77].

Trusting proofs Again, there can be a gap between the algorithm that is formalized and its actual implementation. To solve this issue, a more radical approach consists in conducting the proofs with the help of proof-assistants, such as Coq [CDT] or Isabelle/HOL [NPW]. These programming environments allows for writing programs, their specification, and the corresponding correctness proof in a unified, logical framework that ensures that the proofs are valid. In this case, the validity of the proofs only relies on the proof checking kernel of the assistant, whose correctness is apparent thanks to its small size and its relative simplicity. Besides, proof-assistants provide an extraction mechanism that automatically generates executable code that fulfills the formalized specification. The extraction mechanism is a key feature of proof-assistants, as it amounts to performing the proof directly on the compiler or verifier implementation code.

Compiler verification Compiler verification aims at providing a formal, i.e. mathematically-grounded, proof that the compiler does not insert bugs in the compiled program. More specifically, a compiler should be proved to preserve the semantics of programs, i.e. their dynamic behaviors. Compiler verification is not a new problem, and has a 40-years history, starting with the work of McCarthy and Painter [MP67] on the correctness of a compiler for arithmetic expressions. In 1973, Morris proposed in [Mor73] a methodology for proving the correctness of real size compilers using simulation diagrams. Moore [Moo89, Moo96] provided in the 90's the first machine-assisted proof of a compiler for a high-level assembly language. The compilation of Java has also been formally studied. Stark et al. [SBS01] provide an on-paper

formalization for a subset of source and target language, and a simplified compilation scheme. Strecker [Str02] and Klein and Nipkow [KN06] formalized Java-like non-optimizing compilers to a Java-like bytecode in Isabelle. The Verisoft project [LPP05] provides a simple compiler for C0, a type-safe fragment of C. The CompCert C compiler of Leroy et al. [Ler09, Ler12] is the most advanced and realistic formally verified compiler. It handles a large subset of C¹, provides some carefully chosen optimizations – e.g. tail-call detection, constant propagation, common subexpression elimination with memory variables or function inlining – and produces assembly code for realistic processors (PowerPC, x86 and ARM). Ševčík et al. [ŠVZN+11] provide an adaptation of CompCert for C with concurrency primitives for thread management and synchonization. Chlipala [Chl10] formalized in Coq a compiler from a small, untyped functional language with mutable references and exceptions to an idealized assembly language. Finally, the Vellvm project [ZNMZ12] aims at verifying in Coq components of the LLVM compiler [LLV].

Analyzer verification Analyzers prove the absence of runtime errors only if the abstraction they rely on is an over-approximation of the possible concrete values – they may otherwise miss some bugs. This correctness criteria is called the *semantic soundness* of the verifiers. Proof assistants become increasingly popular for proving realistic analyses. For instance, the Java Bytecode Verifier [LY99], a data-flow analysis for type-checking Java Virtual Machine bytecode programs, has been formalized and proved sound in Isabelle by Klein and Nipkow [KN06] for a subset of the language. Other examples of realistic analyses on Java bytecode include the work of Dabrowski et al. [DP09] on a static data-race analysis implemented and verified in Coq, and Barthe et al. [BPR07] on a type system for detecting unsecure information flows. Appel et al. [App11, SBA12] provide a formally verified analysis of shape properties about programs' heap-data. The analysis is done on Cminor, an IR of C provided by CompCert, where expressions are side-effect free, the evaluation order is fixed, control structures are simplified, and local variables' addresses cannot be taken anymore.

#### 1.2 Intermediate representations to the rescue

Viewed broadly, our work aims at studying the formal proofs of compilers and verifiers. The goal of this work is not to provide new optimizations techniques for compilers, nor to design new static analyzers. Rather, we aim at finding appropriate formalizations and proof methods of existing techniques that have demonstrated their usefulness.

Our work is grounded on the observation that these tools heavily rely on intermediate representations. We believe that formalizing these IRs is a key element for the formal verification of compilers and analyzers. The notion of IR and the benefits it brings will be discussed in more detail in a dedicated chapter, but the previous examples already give an overview: they allow numerous front-ends, aggressive optimizations or fast, simple and precise analyses. The approach followed in CompCert confirms this need for formalized IRs. Its compilation chain comprises 11 differents IRs, that is twice as many IRs as used in GCC. The proof of correctness would not have been possible without splitting the compilation chain in such elementary steps.

We argue that IRs should be exploited more by formal verified compilers and verifiers. Some recent techniques used by mainstream compilers, mostly related to optimization, are still missing in the picture. Compared to GCC or LLVM, CompCert does not include an SSA

<sup>&</sup>lt;sup>1</sup>The only missing features in the current version of CompCert are unstructured switches, unprototyped, long long arithmetic and variable-argument functions. longjmp and setjmp statements are partially handled.

form in its middle-end. The gap is even wider for formally verified analyses. For instance, the analysis presented in [BPR07] is performed at the bytecode level. Keeping track of information flow in a bytecode program requires defining a subtle notion of undistinguishability both on the operand stack and local registers, that must be handled differently in the analysis. Handling the operand stack is difficult in the analysis itself, and hence considerably complicates its soundness proof. Relying on an IR such as the one provided by Sawja could help scaling the analysis (and its proof) to the full language. The data-race analysis of [DP09] must keep track of a flow-sensitive alias information on local registers. An interesting property one gets with the SSA form is that flow-insensitive analyses have the same precision as flow-sensitive ones, thus allowing to implement simpler analyses, that are easier to prove.

The thesis we defend in this dissertation is the following:

"The intermediate program representations used in modern compilers and analyzers can be faithfully formalized and their formalization can be leveraged to simplify the proof of analyses and optimizations."

To support our claim, we study from a formal point of view the semantic foundations of IRs, with an emphasis on real-size languages and modern techniques. Obviously, the spectrum of existing IRs that are used in the analysis and compilation communities is too large, so we focus on three representative cases. The first IR we study is BIR, the stackless Java bytecode IR introduced in Figure 1.2, where the use of the operand stack is replaced with local variables. The second IR we study is SSA, whose apparently simple property of unique variable definition points triggers many semantic invariants. Finally, we investigate a feature that modern compilers and analyzers have to face: concurrency on multiprocessor architectures. From a syntactic point of view, concurrent IR languages differ from sequential IR languages only by a few extra instructions. However, their semantics are far more complex, in particular with respect to shared memory accesses. We focus on concurrent Java IRs. Their semantics are dictated by the so-called Java memory model [MPA05], whose definition is so complex that reasoning formally about it is still an active field of reasearch [AŠ07b, Šev08, TVD10].

More specifically, for each of these case studies, our objectives are the following:

- IR semantics. Capturing the intuition that compiler writers have about an IR, and to reflect this intuition in the formalization. The semantics should also be amenable to formal proof, i.e. it should be easy to reason formally about it.

- IR properties. Stating adequate semantics preservation results for the generation algorithms, and understanding what makes the IR valuable. This means identifying and formalizing its properties, and leveraging them in the proof of subsequent optimizations or analyses.

- **IR generation.** Providing realistic versions of the formalized generation algorithms, to confront our formalizations with practical considerations of performance, and making them usable in compilers or analysis frameworks.

#### 1.3 Contributions and structure of the document

The first two chapters are introductory. Chapter 2 is dedicated to the general notion of intermediate representation and gives a (necessarily incomplete) overview of the leading IRs used in modern compilers or program verification tools. In Chapter 3, we recall the basic notions of

formal semantics, and discuss the possible semantics preservation criteria for program transformations. We also recall the proof technique, based on simulation diagrams, that we will use throughout this work.

Chapter 4 presents our work on BIR. Its conversion algorithm is based on a symbolic execution of the bytecode, a technique that we borrow from the work of Whaley [Wha99] on the optimizing compiler of the Jikes RVM [Jik]. This IR aims at reconstructing side-effect free expressions, and simplifying the object creation scheme that is used in the bytecode. We present its formal correctness proof, which is not mechanized, but rigorous. We also present its implementation within Sawja, and an experimental validation of its performance. We have taken care that the implementation follows closely our formalization.

In Chapter 5, we provide a formally verified SSA-based compiler middle-end. It includes the formalization of the semantics of SSA, and its generation and deconstruction algorithms. We also have implemented and proved a typical and challenging SSA-based optimization, Common-Subexpression Elimination (CSE) based on Global Value Numbering [AWZ88] (GVN). The proof relies on key properties of the SSA form, that we identify and prove as global invariants of the IR. All this formalization work has been done within the Coq proof assistant, relying on the CompCert C compiler. Thanks to the extraction mechanism provided by Coq, we obtain an OCaml version of our middle-end. We provide some experimental results about its performance.

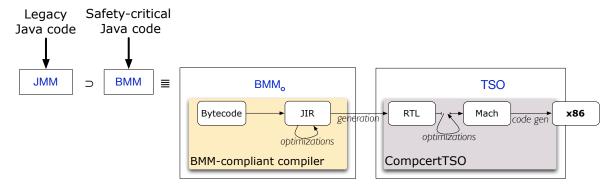

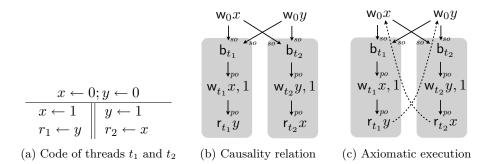

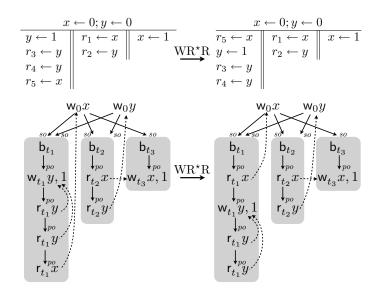

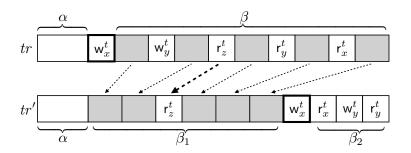

In Chapter 6, after an introduction to the field of weak memory models, we identify a subset of the Java memory model for which we can capture the intuition that is used in the folklore example-driven presentations of the Java memory model. To do so, we expose the valid reorderings directly in the model. Additionally, we make its definition amenable to formal reasoning in a proof assistant like Coq by relying on an operational characterization. We argue that this model is nonetheless efficiently implementable on TSO multiprocessor architectures.

Chapter 7 concludes this dissertation with a summary of our contributions and implementation results. We also discuss extensions to this work, and future perspectives.

#### Notes about Chapters 4, 5, and 6

On-line material. Additional material for these chapters can be found on-line, links are indicated in the chapters.

Proofs. These chapters provides some extended proof sketches to give an intuition about the complete proofs, which can be found either in Appendix or in the on-line material.

Publications. The work presented in Chapter 4 is published in the proceedings of the 8th Asian Symposium on Programming Languages and Systems (APLAS'10) [DJP10]. The presentation of the Sawja tool bench is published in the proceedings of the International Conference on Formal Verification of Object-Oriented Software (FoVeOOS'10) [HBB+11]. The contributors to Sawja and Javalib are, in alphabetic order: Etienne André, Nicolas Barré, Frédéric Besson, Nicolas Cannasse, Delphine Demange, Laurent Hubert, Florent Kirchner, Vincent Monfort, David Pichardie and Tiphaine Turpin.

The work in Chapter 5 has been published in the proceedings of the 21th European Symposium on Programming (ESOP'12) [BDP12]. The Coq proof of the GVN-based CSE optimizations is mainly due to David Pichardie.

The work in Chapter 6 has been accepted for publication in the 40th ACM SIGPLAN-SIGACT Symposium on Principles of Programming Languages (POPL'13) [DLZ<sup>+</sup>13]. The experimental results are due to Vincent Laporte and Lei Zhao.

### Chapter 2

### Intermediate representations

As pointed out in Chapter 1, intermediate representations (IRs) are a key component of compilers and analyzers. Their variety is explained by the diversity of source and target languages, of the program properties to analyze, and on the numerous existing verification techniques. Nevertheless, an IR is not just yet another language, some characteristics can be identified. This chapter aims at giving a more precise definition of what IRs are. We then review six leading IRs that are particularly relevant to our purpose, give the main features that make them used in practice, and also point out their main limitations. This necessarily incomplete overview will help us refining the informal definition of intermediate representation, and motivating our work upon the limitations we observed.

#### 2.1 A first informal definition

What is an IR? To answer the question, we first recall the two main use cases of an IR.

Elementary transformation step Historically speaking, compilers were initially not optimizing: the first task that a compiler had to accomplish was the translation of human-readable code into machine code. Grace Hopper in 1952 developed the very first compiler for the A-0 system language [Hop52], a simple language for arithmetic expressions. It was only later in 1957, that the FORTRAN team led by John W. Backus at IBM introduced the first complete compiler [BBB+57], with the clear intention of producing machine code that could compete, in terms of quality, with hand-written machine code. Thus, IRs were originally introduced to split the compilation chain in elementary steps, each phase focusing on one aspect of the language only. A whole compilation process comprises several internal representations of the code (e.g. abstract syntax tree, control-flow graph or instruction array), but more importantly several languages and instruction sets, that allows for progressively transforming source code into low-level code. In this case, the representation is intermediate in the sense that it is part of a complex process, and helps its design and implementation.

This role is even more crucial for verified compilers, where IRs represent not only a basic step in the compilation process, but also a basic step in its proof. To simplify the proof process, verified compilers thus tend to use more IRs. As an example, the GCC compiler architecture builds on about 6 IRs [FSF], whereas the formally verified CompCert C compiler chain is made of about ten [Ler12].

**Right level of abstraction** The second role of an IR is to provide a representation of a program at the right level of abstraction. Typically, the compiler middle-end IRs are independent from both the source and target languages. This is what allows a given middle-end to be used by different front-ends and back-ends. **GCC** for instance comprises front-ends for

C, C++, OBJECTIVE-C, FORTRAN or Java. All of these front-ends generate GENERIC code, the highest level IR of the middle-end (see Figure 1.1). The IR is used here as a way to factorize the common phases of a compiler: programs written in different languages can be normalized into the IR language. Beyond, what the IR really brings here is an appropriate representation abstracting all the information irrelevant for further transformations. In particular, the number of distinct IR statements can be drastically reduced compared to a source language: an IR provides only the basic constructs required to reach a given expressivity — it is syntactically desugared. This also holds for program analyzers: almost all realistic analyzers or verifiers will work on an IR rather than on the source language directly (see Sections 2.2.5 and 2.2.6).

At the light of this discussion, we note that the first characteristic of an IR is that it is not a programming language: it is not designed to write programs in this language. An IR is automatically generated by tools, and well suited to further transformations and/or analyses. In this respect, it is an analysis-oriented – all non-trivial program transformations requiring a preliminary analysis – and not a user-oriented language.

**Definition 2.1** (Intermediate representation). An intermediate representation is an analysis-oriented language, usable by program-processing tools, and designed according to a verification or transformation purpose.

In order to refine Definition 2.1, we present in the next section six IRs that are widely used in the compilation and analysis communities. For making clearer their differences, we will use the following common source language: While, a simple structured and imperative programming language. Its syntax is given in Figure 2.1, together with a simple program used as a running example. While provides arithmetic and comparison expressions, built on integers constants and variables. While is not typed, but we assume all values are integers. For the sake of simplicity, we do not consider function definitions or function calls.

```

prog foo (n, t) {

const \mid var \mid expr \ op \ expr

r := 0

+ \mid \leq

::=

i := 0

while (i \leq n) {

skip \mid x := expr \mid stmt ; stmt

stmt

r := r+i ;

| if expr then stmt else stmt

i

:= i+t

};

| while expr { stmt }

return r

\mid return e

}

prog ::= prog name (var, ..., var) \{ stmt \}

(b) Example program

(a) Syntax

```

Figure 2.1: While programming language

### 2.2 Some leading IRs

The IRs we present here fall into two categories. TAC, STACK, SSA and CPS are *elementary*: they can be thought of independently, and can be used as basic units of more complex IRs found in compilers or analyzers. The two last IRs we present are *rich* IRs; they are used in the Costa analysis system and the Boogie program verifier respectively.

In the following, we will stay as much as possible at the concrete syntax level, abstracting the internal representation of IRs (e.g. instruction vectors or graphs). The IR internal representation is undoubtely crucial for the ease of code manipulation and traversal (and thus efficiency) but this issue is quite orthogonal to what this chapter aims at presenting, i.e. what information is embedded in IRs, rather than how it is represented.

#### 2.2.1 Three-address code: TAC

TAC stands for *Three-Address Code*. It is a *virtual register transfer* representation. It is one of the most common IRs, described in all compiler textbooks [ASU86, Muc97, App98a]. Any compiler for an imperative language will use a variant of TAC: it corresponds to RTL in the CompCert C compiler and to low-GIMPLE in GCC [FSF]. The concrete syntax of TAC is given in Figure 2.2a. Figure 2.2b gives the TAC representation of our example program.

```

prog foo (n, t) {

bexpr

const \mid var

1: r := 0

2: i := 0

expr

bexpr \mid bexpr \ op \ bexpr

+ | >

if c

goto 8

goto \ell \mid var := expr

stmt

i+t

i :=

| if bexpr goto \ell

goto 3

return r

return var

prog name (var, ..., var) \{ (\ell : stmt) \ list \}

(b) Example program

(a) Syntax

```

Figure 2.2: TAC language

Syntax Each instruction represents exactly one fundamental operation: expression trees have height at most one, so that each statement references at most three virtual registers (e.g. one result and two arguments). Hence the name *three-address code* in the literature. In Figure 2.2b, notice that a new temporary variable c must be used to store the result of the comparison i > n, since the condition must be a basic expression. Similarly, complex While assignments like x := a+b+c-1 would be decomposed in TAC as e.g. t1 := a+b; t2 := t1+c; t3 := t2-1.

TAC is not structured: while-loops and if-statements are encoded using conditional and unconditional jumps only. In Figure 2.2b the while-loop is encoded by the instructions between program points 3 and 7. While could have included many other kinds of loops (such as for-loop, or do-while loops) without TAC needing any other statement.

**Expressions and control lowering** In TAC, the evaluation order of expressions has been determined thanks to the decomposition of computations into elementary expressions. They also match better the machine instruction format (there is no hidden computation). Control structures have also been lowered<sup>1</sup>, and are closer to the assembly representation.