# ELECTRICAL PERFORMANCES COMPARISON OF SEMI AND FULLY RECESSED ISOLATION STRUCTURES

Emmanuel Dubois, J.-L. Coppee, B. Baccus, D. Collard

## ▶ To cite this version:

Emmanuel Dubois, J.-L. Coppee, B. Baccus, D. Collard. ELECTRICAL PERFORMANCES COMPARISON OF SEMI AND FULLY RECESSED ISOLATION STRUCTURES. Journal de Physique Colloques, 1988, 49 (C4), pp.C4-813-C4-816.  $10.1051/\mathrm{jphyscol:19884171}$ . jpa-00227913

## HAL Id: jpa-00227913 https://hal.science/jpa-00227913v1

Submitted on 4 Feb 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## ELECTRICAL PERFORMANCES COMPARISON OF SEMI AND FULLY RECESSED ISOLATION STRUCTURES

E. DUBOIS(1), J.-L. COPPEE\* (2), B. BACCUS and D. COLLARD

ISEN, Institut Supérieur d'Electronique du Nord, CNRS-LA 253, 41, Bd Vauban, F-59046 Lille Cedex, France \*Université Catholique de Louvain, Laboratoire de Microélectronique, Place du Levant 3, B-1348 Louvain-la-Neuve, Belgium

$\frac{\text{Résumé}}{\text{LOCOS}}$  - Les caractéristiques de structures d'isolation LOCOS semi-enterré et LOCOS enterré ont été analysées. En particuliers, les simulations bidimensionnelles couplées de technologie et de dispositif, réalisées avec le logiciel IMPACT, ont démontré l'influence de l'interface Si/SiO  $_2$  sur les performances d'isolation. Un excellent accord simulation-expérimentation a été trouvé pour les structures étudiées.

Abstract - Electrical characteristics of semi-recessed and fully-recessed LOCOS isolation techniques are analyzed. Two-dimensionnal process/device simulations, performed with the IMPACT package, have demonstrated the effect of the Si/SiO<sub>2</sub> interface shape on isolation efficiency. An excellent agreement has been found between simulations and measurements for the studied structures.

#### I - INTRODUCTION

Device isolation presents critical aspects for circuit packing density in VLSI. LOCal Oxidation of Silicon (LOCOS) is classically limited by the bird's beak extension and lateral diffusion of the channel stop region into active transistor area. Several technological alternatives were proposed to control lateral growth of oxide, such as SILO technique (Sealed Interface Local Oxidation) by using successive silicon nitride and deposited oxide layers /1,2/. In order to evaluate a new isolation process, numerous technological and device physics aspects have to be investigated to clarify important two dimensional (2D) parasitic effects /3/. So the use of coupled process/device simulations is of prime necessity. This paper proposes a comparison of electrical performances for both semi and fully-recessed isolation structures by means of process-device simulations and experimental results. A special attention has been devoted to the bird's beak shape description to demonstrate the electrical implications induced by geometrical effects. An advanced version of the IMPACT3 device simulator extended for isolation structure modeling linked to the IMPACT2 /4/ process simulator was extensively used for two dimensional electrical analysis.

## II - PROCESS DESCRIPTION

Table I outlines the main characteristics of the isolation stuctures that has been investigated. SEM cross-sectional views of both structures are shown in figure 1. For each of them, two versions have been fabricated:

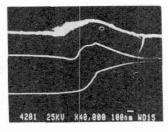

- an aluminium gate version for which a 0.5 micron poly-silicate-glass (PSG) layer was deposited prior the aluminium level. (figure 2)

- a polysilicon gate version. In this case, the n\* diffusion regions are self-aligned to the polysilicon. A 550 A\* thick oxide layer of about 3 microns long exists between the field oxide mask and the edge of the poly mask. (figure 3)

### III - ISOLATION PROPERTIES

The major difference between the semi-rox and the full-rox structure is the bird's beak shape. Because the junctions are shallower than the planar part of the

<sup>(1)</sup> Subsidized by Centre National de la Recherche Scientifique - CNRS

<sup>(2)</sup> Supported by l'Institut pour l'encouragement de la recherche scientifique dans l'industrie et l'agriculture - IRSIA

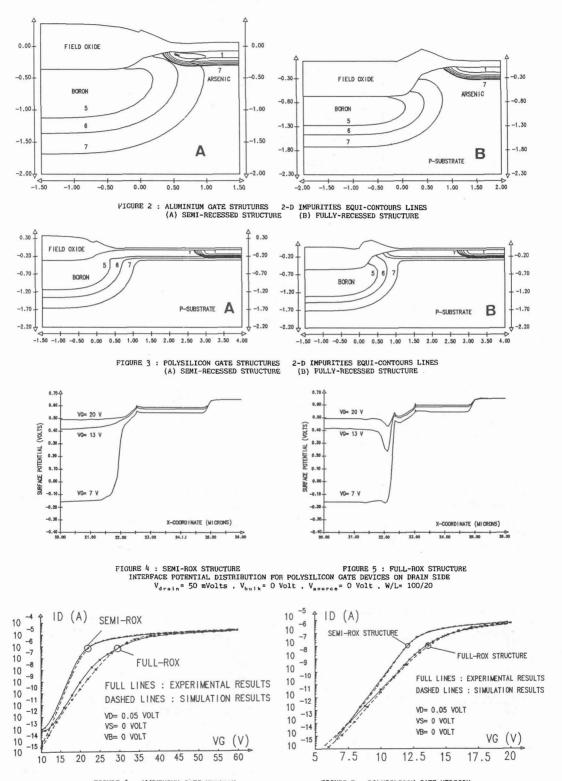

Si/SiO, interface, the oxide corners are incorporated into the channel region. Figures 4 and 5 show the potential variations along the interface for both structures with a polysilicon gate. Differents barrier deformations are observed when the gate bias affects sufficiently the interface potential distribution. Indeed, the potential barrier of the fully-recessed structure is then located under each bird's beak corner. but remains spread over the whole field oxide interface in the case of the semi-recessed structure. Because the current in the overall structure is controlled by electron emission over the potential barrier at the source side, the fully-recessed device shows better isolation properties than the semi-recessed one. This point is illustrated by the ID-VG characteristics for both aluminium and polysilicon gates (resp. figures 6 and 7). Notice that an excellent agreement is found between measured and calculated drain currents that validates the simulation approach.

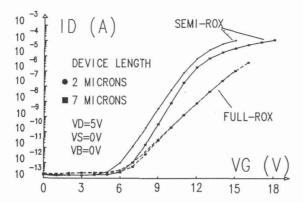

Further simulations have been carried out on 2 and 7 microns long aluminium gate devices without the PSG layer, for a 5 volts drain bias condition. Characteristics plotted in figure 8 demonstrates the sensitivity of the semi-recessed isolation structure to the  $n^*$  to  $n^*$  spacing (L). By opposition, the fully-recessed structure does not reveal this typical 1/L dependence in the subthreshold mode of operation. Indeed, the effective channel length is in this case reduced to the curved part of the field oxide interface and makes the whole parasitic transistor dominated by the two corner devices.

#### IV - SENSIBILITY TO DIBL EFFECT

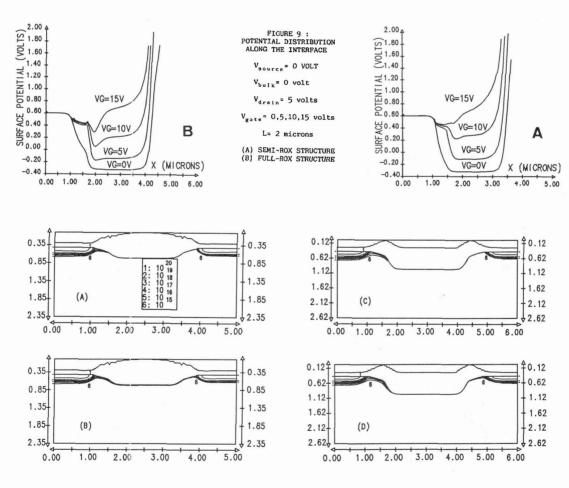

The simulations performed on a 2 microns long device have allowed to analyze the effect of Drain Induced Barrier Lowering (DIBL) combined to the corner effect. The drain bias modulates the potential distribution around the n \* diffusion and first affects the potential barrier in the corresponding region. As the curved part of the interface located on the drain side requires more band bending to invert because of the influence of the drain controlled depletion region, the channel is firstly formed in the source region (figure 9). Figure 10 illustrates the potential distribution along the interface for gate bias varying from 0 to 15 volts. This result shows, once again, how the newly located potential barrier leads to a better immunity against the DIBL effect, for the full-rox isolation structure.

## CONCLUSION

The presented results obtained from coupled process-device analysis have outlined the sensitivity of isolation structure to the field oxide shape. As the corner effect provides better characteristics for threshold voltage, subthreshold slope and drain voltage dependence, buried oxide isolation structures with sharpened corners appear as a valuable solution for micron and submicron technologies. Moreover, the experimental characteristics of the studied structures have revealed to be in good agreement with two dimensional numerical modeling, and have proved the capabilities of the IMPACT simulation tool to investigate physics of new isolation structures.

### REFERENCES

- /1/: J. HUI et al., IEDM Technical Digest, pp 220-223, Dec. 1982

/2/: S. SAWADA et al., IEDE Trans. Electron. Devices, vol ED-32, 1985

/3/: J.L. COPPEE and F. VAN DE WIELE, Solid-State Electronics, vol 31, 1988

/4/: D. COLLARD and K. TANIGUCHI, IEDE Trans. Electron. Devices, vol. ED-33, 1986

/5/: S. GOODWIN and J. PLUMMER, IEDE Trans. Electron. Devices, vol. ED-31, 1984

FIGURE 1 : SEM CROSS-SECTIONAL VIEWS OF THE FIELD OXIDE EDGE SEMI-RECESSED STRUCTURE FULLY-RECESSED STRUCURE

TABLE I

| × 30               | Semi-Rox<br>Structure                            | Full-Rox<br>Structure                  |

|--------------------|--------------------------------------------------|----------------------------------------|

| Field<br>Implant   | 2 10 <sup>13</sup> cm <sup>-2</sup><br>at 25 Kev | 2 10 13cm <sup>-2</sup><br>at 25 Kev   |

| Field<br>Oxidation | 1000° C<br>220 mn                                | 950° C<br>370 mn                       |

| Oxide<br>thickness | 716 nm                                           | 735 nm                                 |

| S/D implant        | 5 10 15 cm <sup>-2</sup> at 140 Kev              | 5 10 15 cm <sup>-2</sup><br>at 140 Kev |

| Annealing          | 950° C                                           | 950° C                                 |

FIGURE 6 : ALUMINIUM GATE VERSION FIGURE 7 : POLYSILICON GATE VERSION SIMULATED AND MEASURED ID-VG CHARACTERISTICS W/L= 100/20

FIGURE 8 : CALCULATED ID-VG CURVES FOR DIFFERENT DEVICE LENGHTS  $V_{\tt source}$  0 Volt ,  $V_{\tt bulk}$ = 0 Volt ,  $V_{\tt drain}$ = 5 Volts W = 100 Microns

FIGURE 10: ELECTRON DENSITY DISTRIBUTION DURING CHANNEL FORMATION  $V_{\tt source}$  = 0 volt ,  $V_{\tt bulk}$  = 0 volt ,  $V_{\tt drain}$  = 5 volts

SEMI-ROX STRUCTURE : (A)  $V_{\rm gate}$  = 5 volts , (B)  $V_{\rm gate}$  = 15 volts FULL-ROX STRUCTURE : (C)  $V_{\rm gate}$  = 5 volts , (D)  $V_{\rm gate}$  = 15 volts