## A 37–43.5-GHz fully integrated 16-element phased-array transceiver with 64-QAM 7.2-Gb/s data rates supporting dual-polarized MIMO

Xin Chen, Xiaokang Niu, Xuan Wang, Haipeng Duan, Jing Feng, Lin Lu, Long He, Qin Chen, Depeng Cheng, Lei Luo, et al.

#### ▶ To cite this version:

Xin Chen, Xiaokang Niu, Xuan Wang, Haipeng Duan, Jing Feng, et al.. A 37–43.5-GHz fully integrated 16-element phased-array transceiver with 64-QAM 7.2-Gb/s data rates supporting dual-polarized MIMO. IEEE Microwave and Wireless Technology Letters, 2024, 34 (6), pp.789-792. 10.1109/LMWT.2024.3375888. hal-04870153

### HAL Id: hal-04870153 https://hal.science/hal-04870153v1

Submitted on 7 Jan 2025

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Copyright

# A 37-43.5-GHz Fully-Integrated 16-Element Phased-Array Transceiver with 64-QAM 7.2-Gb/s Data Rates Supporting Dual-Polarized MIMO

Xin Chen, Graduate Student Member, IEEE, Xiaokang Niu, Member, IEEE, Xuan Wang, Graduate Student Member, IEEE, Haipeng Duan, Graduate Student Member, IEEE, Jing Feng, Graduate Student Member, IEEE, Lin Lu, Graduate Student Member, IEEE, Long He, Member, IEEE, Qin Chen, Graduate Student Member, IEEE, Depeng Cheng, Member, IEEE, Lei Luo, Member, IEEE, Xu Wu, Member, IEEE, Jiachen Si, Xujun Ma, Member, IEEE, Xiangning Fan, Member, IEEE, and Lianming Li, Member, IEEE

Abstract—This paper presents a fully-integrated 16-element phased-array transceiver (TRX) supporting dual-polarized multi-input multi-output (DP-MIMO). Transmitting/receiving (T/R) switches are embedded for time division duplexing (TDD) operation. High linearity bi-directional variable gain amplifiers (Bi-VGA) and passive phase shifters (PS) are designed for compact area and low power consumption, respectively. Fabricated in a 65-nm CMOS process, this TRX occupies an area of 25.76 mm<sup>2</sup>. With integrated frequency synthesizer, the TRX can work from 37 to 43.5 GHz, which can fully cover 5G NR FR2 n259 and n260 bands. In the receiver (RX) mode, a noise figure (NF) of 5.4-6.3 dB and a peak conversion gain (CG) of 27.3 dB are achieved. The transmitter (TX) mode achieves a peak CG of 48.7 dB, a 13.1-dBm OP<sub>1dB</sub>, and a 15.8-dBm P<sub>sat</sub>. By using 64-QAM modulation, measurement results show that the TRX achieves a data rate up to 7.2 Gb/s per independent data stream with 7.65 dBm output power per channel.

Index Terms—5G, CMOS, dual-polarization multi-input multi-output (DP-MIMO), frequency synthesizer, millimeter wave (mm-Wave), phased-array, quadrature amplitude modulation (QAM), transceiver (TRX).

#### I. INTRODUCTION

OR the increasing demand in high data throughput for emerging applications, e.g., augmented reality (AR), virtual reality (VR), mixed reality (MR), etc., several mm-Wave bands including 37-43.5-GHz (n259 and n260)

This work was supported in part by the National Key Research and Development Program of China under Grant 2018YFE0205900 and in part by the Major Key Project of PCL. (Corresponding authors: Xiangning Fan, Lianming Li.)

Xin Chen, Xuan Wang, Haipeng Duan, Jing Feng, Lin Lu, Qin Chen, Xu Wu, and Lianming Li are with the National Mobile Communication Research Laboratory, Southeast University, Nanjing 211189, China, and also with the Purple Mountain Laboratories, Nanjing 211111, China. (e-mail: lianming.li@seu.edu.cn).

Xiaokang Niu, Long He, Depeng Cheng, and Lei Luo are with the Purple Mountain Laboratories, Nanjing 211111, China.

Jiachen Si, and Xiangning Fan are with the School of Information Science and Engineering, Southeast University, Nanjing 211189, China. (e-mail: xnfan@seu.edu.cn)

Xujun Ma is with Télécom SudParis, Institut Polytechnique de Paris, 91120 Palaiseau, France.

This article was presented at the IEEE MTT-S International Microwave Symposium (IMS 2024), Washington, DC, USA, June 16–21, 2024.

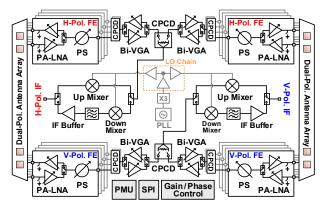

Fig. 1. The proposed dual-polarization phased-array transceiver architecture.

have been allocated in the 5G new radio (NR) frequency range 2 (FR2). To compensate the large propagation loss and to spatial mobility accommodate for the communication, the phased-array technique is urgently required [1]-[3]. In addition to improving the noise figure (NF), linearity, and power efficiency of transmitting/receiving (T/R) elements, the system data throughput could be significantly extended with the dual-polarization multi-input multi-output (DP-MIMO) technique. Recent works prove the feasibility in integrating high data-rate dual-polarized phasedarray transceiver chips without scaling up the physical size of the antenna array [4]-[9]. Nevertheless, due to the increasing demands for the miniaturized smart user equipment (UE), it poses more challenges in designing a compact and fullyintegrated phased-array transceiver that incorporates more elements while balancing the overall performance and packaging difficulties [10].

To this end, a fully-integrated 16-element phased-array transceiver (TRX) supporting DP-MIMO with compact architecture is proposed in this work, which integrates RF front-end (FE), frequency converter, and frequency synthesizer. Specifically, bi-directional variable gain amplifier (Bi-VGA) is designed to drive multiple T/R elements, reducing the required number of active stages in the TRX. The passive phase shifter (PS) is adopted to reduce the power consumption as well as the T/R element area due to its bi-directional feature. Fabricated in a 65-nm CMOS process, the

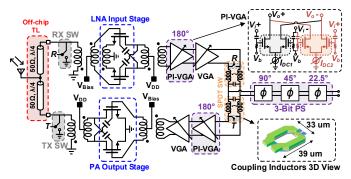

Fig. 2. Structure of the T/R element.

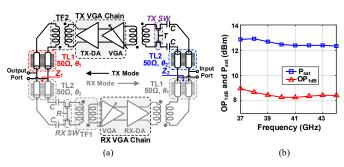

Fig. 3. (a) Structure of the high linearity Bi-VGA. (b) Simulated TX Mode Bi-VGA  $OP_{1dB}$  and  $P_{sat}$  at 37-43.5 GHz.

proposed fully-integrated 16-element TRX achieves a data rate of 7.2 Gb/s per independent data stream in 64-QAM with a 7.65 dBm output power per channel, while occupying a chip area of 25.76 mm<sup>2</sup>.

#### II. TRANSCEIVER ARCHITECTURE AND BUILDING BLOCKS

#### A. Transceiver Architecture

The architecture of the proposed phased-array TRX is depicted in Fig. 1, which comprises 16 T/R elements (8H + 8V) to support the DP-MIMO. In each T/R element, benefitting from the 1-bit 180° phase-inverting (PI) feature implemented in both the low noise amplifier (LNA) and power amplifier (PA), a 4-bit 360° phase control could be realized by merely integrating a 3-bit 180° passive PS. In this way, the size and insertion loss (IL) of the PS are reduced significantly.

The configurable power combiners and dividers (CPCDs) are adopted to support sub-array operations and to expand the TRX dynamic range while maintaining the system power efficiency. High linearity Bi-VGA is adopted to drive four T/R elements and compensate for the significant losses caused by passive components, such as PS, CPCDs, and transmission lines (TLs). Benefiting from the compact Bi-VGA and T/R element, the entire chip size could be significantly reduced. In addition, the local-oscillator (LO) signal is provided by the integrated phase-locked loop (PLL) and frequency tripler. Peripheral circuits, i.e., serial peripheral interface (SPI) and power management unit (PMU), are integrated to support the phased-array applications.

#### B. Compact T/R Element

The structure of the compact T/R element is shown in Fig. 2. On the antenna side, the T/R switches are co-designed with off-

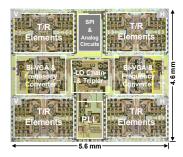

Fig. 4. Chip micrograph of the fully-integrated dual-polarization phased-array transceiver with PLL.

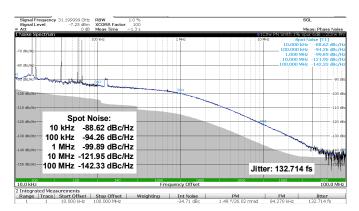

Fig. 5. Measured LO phase noise at 31.2 GHz.

chip 50- $\Omega$   $\lambda/4$  TLs, which are integrated into the packaging to reduce chip area. Meanwhile, to minimize the side-effect of the T/R switches on the element performance, the receiver (RX) switch is designed for low IL performance by using small-sized transistors with lower parasitics, while the stacked transistors are used in the transmitter (TX) switch for high linearity performance. On the other side of the T/R element, a single-pole double-throw (SPDT) switch is integrated with an ultra-compact  $\pi$ -type LC network, which only occupies a core area of  $39\mu m \times 33\mu m$ , as shown in Fig. 2.

To reduce PS units for low IL and chip area, the 1-bit  $180^{\circ}$  phase-inverting variable gain amplifier (PI-VGA) is used. Such PI-VGA contains double balanced common-source (CS) amplifier with tail current sources  $I_{DC1}$  and  $I_{DC2}$ , which are digitally controlled for gain tuning to compensate for the PS IL variation between different phase states. The PI-VGA output phase can be reversed by  $180^{\circ}$  by swapping the current of  $I_{DC1}$  and  $I_{DC2}$ , while maintaining the same gain level. By combining the 1-bit  $180^{\circ}$  PI-VGA and a 3-bit  $180^{\circ}$  PS, 4-bit  $360^{\circ}$  phase control is achieved. Note that, the 3-bit  $180^{\circ}$  PS is realized with phase steps of  $22.5^{\circ}$ ,  $45^{\circ}$ , and  $90^{\circ}$ , respectively, and it has a typical cascaded 7 dB IL.

#### C. High Linearity Bi-VGA

Fig. 3(a) depicts the Bi-VGA structure, which contains two identical VGA chains reversely connected in parallel. In each VGA chain, a driver amplifier (DA) is integrated in the VGA output to improve its linearity performance, and four T/R elements could be driven simultaneously for the compact TRX architecture. At each VGA chain input, an asymmetric SPDT switch is implemented with low IL features. Meanwhile,  $50-\Omega$

| TIBLE ITEM CRAIMED COMPARISON WITH STATE OF THE PRICE CHARGE PRICE PRICE. |                              |                                                                                                             |                                                                   |                                          |                                                                             |                                                 |

|---------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------|

|                                                                           |                              | This Work                                                                                                   | TMTT'23 [3]                                                       | RFIC'19 [8]                              | ISSCC'20 [9]                                                                | JSSC'20 [11]                                    |

| Technology                                                                |                              | 65-nm CMOS                                                                                                  | 65-nm CMOS                                                        | 28-nm CMOS                               | 28-nm CMOS                                                                  | 65-nm CMOS                                      |

| Integration                                                               |                              | Dual Pol. 16ch. TRX                                                                                         | 4ch. FE                                                           | Dual Pol. 8ch. FE                        | 16ch. TRX                                                                   | 4ch. TRX                                        |

|                                                                           |                              | w/ PLL                                                                                                      | w/o PLL                                                           | w/o PLL                                  | w/o PLL                                                                     | w/o PLL                                         |

| T/R Switch                                                                |                              | Yes (w/ off-chip TLs)                                                                                       | Yes (On-chip)                                                     | Yes (On-chip)                            | No                                                                          | Yes (On-chip)                                   |

| Carrier Frequency (GHz)                                                   |                              | 37-43.5                                                                                                     | 33.5-37.5                                                         | 37-40                                    | 37-40                                                                       | 39                                              |

| Phase Resolution (bits)                                                   |                              | 4                                                                                                           | 6                                                                 | 5                                        | 4                                                                           | 13                                              |

| RX                                                                        | Peak Gain (dB)               | 27.3                                                                                                        | 26                                                                | 41.9                                     | 59                                                                          | 3                                               |

|                                                                           | NF/ch (dB)                   | 5.4-6.3                                                                                                     | 4.2-10.7                                                          | 6-7.6                                    | 4.2-4.6                                                                     | 7.7                                             |

|                                                                           | IP <sub>1dB</sub> /ch (dBm)  | -26.5                                                                                                       | N/A                                                               | -44                                      | -44#                                                                        | -22                                             |

|                                                                           | P <sub>DC</sub> /ch. (mW)    | 69.7 <sup>§</sup>                                                                                           | 164                                                               | 78.5                                     | 39                                                                          | 500 (4RX)                                       |

|                                                                           | Peak Gain (dB)               | 48.7                                                                                                        | 44                                                                | 48                                       | 60                                                                          | 7                                               |

| TX                                                                        | OP <sub>1dB</sub> /ch. (dBm) | 13.1                                                                                                        | 17.2                                                              | 12.3                                     | 15.3                                                                        | 9                                               |

|                                                                           | P <sub>sat</sub> /ch. (dBm)  | 15.7                                                                                                        | 19.8                                                              | N/A                                      | 16.5                                                                        | 15.5                                            |

|                                                                           | P <sub>DC</sub> /ch. (mW)    | 210@P <sub>1dB</sub> §                                                                                      | 496                                                               | 339@P <sub>1dB</sub>                     | 105/115\$                                                                   | 1500 (4TX)                                      |

|                                                                           | Modulation<br>Results        | 64-QAM, 3.6/7.2 Gb/s<br>10.6/7.65 dBm P <sub>out</sub> /ch<br>-25.2/-25.54 dB EVM<br>-29.43/-30.38 dBc ACLR | 16-QAM, 0.8 Gb/s<br>11.2 dBm P <sub>out</sub> /ch<br>-29.7 dB EVM | 64-QAM OFDM<br>0.6 Gb/s<br>-32.57 dB EVM | 64-QAM OFDM<br>4.8 Gb/s<br>6/8.8 dBm P <sub>out</sub> /ch<br>-34/-27 dB EVM | 8TX 8RX OTA<br>64-QAM, 2.4 Gb/s<br>-30.2 dB EVM |

|                                                                           |                              | 256-QAM, 1.6 Gb/s<br>6.9 dBm P <sub>out</sub> /ch<br>-30.12 dB EVM                                          | 64-QAM, 1.2 Gb/s<br>11.2 dBm P <sub>out</sub> /ch<br>-30.4 dB EVM | 64-QAM OFDM<br>4.8 Gb/s<br>-26.5 dB EVM# |                                                                             | 8TX 8RX OTA<br>256-QAM, 3.2 Gb/s<br>-30 dB EVM  |

TABLE I. PERFORMANCE COMPARISON WITH STATE-OF-THE-ART CMOS PHASED-ARRAY TRANSCEIVERS.

$^{\S}$ Including T/R element, Bi-VGA, up (or down) Mixer, and LO buffer.  $^{\#}$ Estimated from figures.  $^{\S}$ With 6/8.8 dBm  $^{P}$ Out/ch.

25.92

25.76

Chip Area (mm<sup>2</sup>)

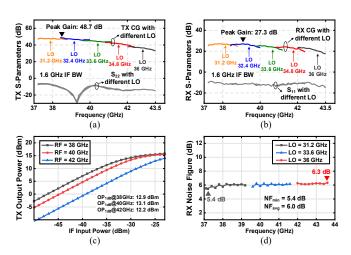

Fig. 6. Measured (a) TX and (b) RX S-Parameters. (c) Measured  $OP_{1dB}$  of the full TX path. (d) Measured NF of the full RX path.

differential TL1 and TL2 are designed with different electrical length for the impedance matching as well as port isolation purposes in both TX and RX modes. Taking the TX mode as an example, the TX SW is turned on while RX SW are off. Meanwhile, the RX VGA chain is powered off, and with the impedance matching network, its input and output impedances, i.e.,  $Z_1$  and  $Z_2$ , respectively, are transformed to higher values, introducing only 0.74 and 0.93 dB simulated ILs at the Bi-VGA input and output, respectively. To illustrate the linearity performance of the Bi-VGA, the simulated OP<sub>1dB</sub> and P<sub>sat</sub> of Bi-VGA in the TX mode are shown in Fig. 3(b).

#### III. MEASUREMENT RESULTS

Fabricated in a 65-nm CMOS process, the proposed phased-array TRX occupies a total area of  $5.6 \times 4.6 \text{ mm}^2$ , as shown in Fig. 5. The T/R element and Bi-VGA occupy 0.55 and 0.22

12

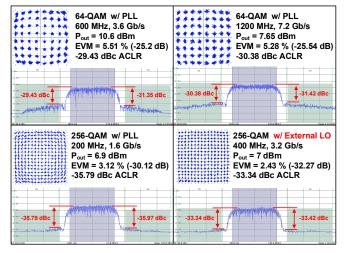

Fig. 7. Measures 64-/256-QAM EVM and ACLR at 38 GHz.

mm<sup>2</sup>, respectively. All measurements were conducted with the on-chip PLL.

As shown in Fig. 5, with a 10.4 GHz LO from the PLL, the measured phase noise (PN) of the 31.2 GHz LO after the frequency tripler achieves -99.89 and -121.95 dBc/Hz PN at 1 MHz and 10 MHz offsets, respectively. With an intermediate frequency (IF) ranging from 6 to 7.6 GHz, the measured TX and RX conversion gains in five sub-bands of the 5G NR FR2 37-43.5 GHz bands are shown in Fig. 6(a) and (b), respectively. Peak conversion gains of 48.7 and 27.3 dB are achieved in the TX and RX modes, respectively. The TX output power from 38 to 42 GHz is shown in Fig. 6(c), where an OP<sub>1dB</sub> from 12.2 to 13.1 dBm is achieved, respectively. The measured RX NF over the desired frequency band is shown in Fig. 6(d), achieving a NF from 5.4 to 6.3 dB and demonstrating a good NF performance over the interested frequency range.

To further evaluate the TX performance, the modulation measurements are performed. Fig. 7 presents the measured constellations and ACLR results of 64-/256-QAM signal at 38 GHz. As indicated, with 600-/1200-MHz 64-QAM modulation, a P<sub>out</sub> of 10.6/7.65 dBm is achieved with -25.2/-25.54 dB error vector magnitude (EVM), respectively, which is mainly limited by TX linearity and noise performance. It achieves a P<sub>out</sub> of 6.9 dBm for 200-MHz 256-QAM with -30.12 dB EVM, which is mainly limited by the LO PN. Besides, with an external LO signal, it achieves a Pout of 7 dBm for 400-MHz 256-QAM with -32.27 dB EVM.

Table I compares the performance of the proposed phased-array TRX with the state-of-the-art phased array transceiver results. As indicated, this work integrates PLL and can fully cover the 5G NR FR2 37-43.5 GHz n259 and n260 bands, while achieving lower power consumption and a more compact area. Benefiting from the excellent bandwidth, NF and linearity performance, this work achieves the fastest data rate up to 7.2 Gb/s.

#### IV. CONCLUSION

This paper presents a fully-integrated 16-elements phased-array TRX supporting DP-MIMO with a compact system architecture. Fabricated in a 65-nm CMOS process, the proposed phased-array TRX occupies a total chip area of 25.76 mm². The measured TRX can fully cover the 5G NR FR2 37-43.5 GHz n259 and n260 bands with a 1.6 GHz IF bandwidth in each sub-channel. Consuming an average 210 mW power consumption per channel, the TRX achieves the OP<sub>1dB</sub> and P<sub>sat</sub> of 13.1 and 15.8 dBm, respectively, and supports 1200-MHz 64-QAM and 200-MHz 256-QAM with high output power. Furthermore, the proposed TRX achieves a data rate up to 7.2 Gb/s per independent data stream, which is very suitable for high-throughput and small-scale 5G UE applications.

#### REFERENCES

- [1] K. Kibaroglu, M. Sayginer and G. M. Rebeiz, "A Low-Cost Scalable 32-Element 28-GHz Phased Array Transceiver for 5G Communication Links Based on a 2 × 2 Beamformer Flip-Chip Unit Cell," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 5, pp. 1260-1274, May 2018.

- [2] W. Zhu et al., "A 24–28-GHz Four-Element Phased-Array Transceiver Front End With 21.1%/16.6% Transmitter Peak/OP1dB PAE and Subdegree Phase Resolution Supporting 2.4 Gb/s in 256-QAM for 5-G Communications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 69, no. 6, pp. 2854-2869, June 2021.

- [3] Pingda Guan et al., "A 33.5–37.5-GHz Four-Element Phased-Array Transceiver Front-End With Hybrid Architecture Phase Shifters and Gain Controllers," *IEEE Transactions on Microwave Theory and Techniques*, vol. 71, no. 9, pp. 4129-4143, Sept. 2023.

- [4] S. Shakib, M. Elkholy, J. Dunworth, V. Aparin and K. Entesari, "A Wideband 28-GHz Transmit–Receive Front-End for 5G Handset Phased Arrays in 40-nm CMOS," *IEEE Transactions on Microwave Theory and Techniques*, vol. 67, no. 7, pp. 2946-2963, July 2019.

- [5] J. D. Dunworth et al., "A 28GHz Bulk-CMOS dual-polarization phased-array transceiver with 24 channels for 5G user and basestation equipment," IEEE International Solid-State Circuits Conference (ISSCC), Feb. 2018, pp. 70-72.

- [6] S. Wang, A. Alhamed and G. M. Rebeiz, "An 8-Element 5G Multistandard 28-/39-GHz Dual-Band, Dual-Polarized Phased Array for Compact Systems," *IEEE Transactions on Microwave Theory and Techniques*, vol. 71, no. 9, pp. 4109-4118, Sept. 2023.

- [7] J. Pang et al., "A CMOS Dual-Polarized Phased-Array Beamformer Utilizing Cross-Polarization Leakage Cancellation for 5G MIMO Systems," *IEEE Journal of Solid-State Circuits*, vol. 56, no. 4, pp. 1310-1326, April 2021.

- [8] A. G. Roy et al., "A 37-40 GHz Phased Array Front-end with Dual Polarization for 5G MIMO Beamforming Applications," in *IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, June 2019, pp. 251-254.

- [9] H. -C. Park et al., "A 39GHz-Band CMOS 16-Channel Phased-Array Transceiver IC with a Companion Dual-Stream IF Transceiver IC for 5G NR Base-Station Applications," *IEEE International Solid-State Circuits Conference (ISSCC)*, Feb. 2020, pp. 76-78.

- [10] S. Shahramian, M. Holyoak, A. Singh, B. J. Farahani and Y. Baeyens, "A fully integrated scalable W-band phased-array module with integrated antennas, self-alignment and self-test," *IEEE International Solid-State Circuits Conference (ISSCC)*, Feb. 2018, pp. 74-76.

- [11] Y. Wang et al., "A 39-GHz 64-Element Phased-Array Transceiver With Built-In Phase and Amplitude Calibrations for Large-Array 5G NR in 65-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 5, pp. 1249-1269, May 2020.