# 10.7 An 11GHz 2nd-order DPD FMCW chirp generator with 0.051% rms frequency error under a 2.3GHz chirp bandwidth, 2.3GHz/ $\mu$ s slope, and 50ns idle time in 65nm CMOS

Xuan Wang, Xujun Ma, Yupeng Fu, Yuqian Zhou, Ang Li, Shuo Yang, Xu Wu, Dongming Wang, Lianming Li, Xiaohu You

### ► To cite this version:

Xuan Wang, Xujun Ma, Yupeng Fu, Yuqian Zhou, Ang Li, et al.<br/>. 10.7 An 11GHz 2nd-order DPD FMCW chirp generator with<br/> 0.051% rms frequency error under a 2.3GHz chirp bandwidth,<br/> 2.3GHz/µs slope, and 50ns idle time in 65nm CMOS. 2024 IEEE International Solid-State Circuits Conference (ISSCC), Feb 2024, San Francisco, United States. pp.200-202, 10.1109/ISSCC49657.2024.10454283 . hal-04870066

## HAL Id: hal-04870066 https://hal.science/hal-04870066v1

Submitted on 7 Jan 2025

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. 10.7 An 11GHz 2<sup>nd</sup>-order DPD FMCW Chirp Generator with 0.051% rms Frequency Error under a 2.3GHz Chirp Bandwidth, 2.3GHz/μs Slope, and 50ns Idle Time in 65nm CMOS

Xuan Wang<sup>\*1,2</sup>, Xujun Ma<sup>\*3</sup>, Yupeng Fu<sup>1</sup>, Yuqian Zhou<sup>1</sup>, Ang Li<sup>1</sup>, Shuo Yang<sup>1</sup>, Xu Wu<sup>1,2</sup>, Dongming Wang<sup>1,2</sup>, Lianming Li<sup>1,2</sup>, Xiaohu You<sup>1,2</sup>

<sup>1</sup>Southeast University, Nanjing, China, <sup>2</sup>Purple Mountain Laboratories, Nanjing, China, <sup>3</sup>Télécom SudParis, Paris, France

#### \*Equally Credited Authors (ECAs)

A frequency-modulated continuous-wave (FMCW) chirp generator serves as the pivotal building block for short-range 3D imaging radar systems, which have been widely utilized in medical and security applications. To enable quick and precise scanning with submillisecond snapshot duration and sub-centimeter depth resolution in a 79GHz largescale MIMO radar imaging system, which composes of hundreds of TX/RX elements, the FMCW chirp generator must generate chirps with about 1µs chirp duration and operate >15GHz bandwidth (BW), necessitating an ultra-fast chirp slope exceeding 15GHz/µs. Meanwhile, high chirp linearity and low phase noise (PN) are also essential to improve the signal-to-noise ratio (SNR) for high-quality imaging, and the between-chirp idle time (Tidle) must be shortened to 50ns given that at least 95% of the chirp duty-cycle is required. To resolve the contradictions between narrow PLL BW for low PN and quick loop response for fast chirp, two-point-modulation (TPM) technique is widely implemented in fractional-N PLLs [1-5]. Regarding the linearity of an ultra-fast wideband chirp, it is challenging to effectively compensate for the residual frequency error (Ferror) of a 1st-order digital pre-distortion (DPD) [2-4] and the ramp non-linearity of a ramp tracker [1,5] with an insufficient PLL bandwidth, calling for advanced curve fitting techniques. In this work, to diminish rms Ferror in the context of ultra-fast wideband chirp generation, a ramp-tracker assisted 2nd-order curve-fitting (2nd-CF) DPD is proposed in a fractional-N sub-sampling (SS) PLL, achieving an 11GHz fast saw-tooth chirp with a 2.3GHz chirp bandwidth, 2.3GHz/µs chirp slope, and 0.051% rms Ferror. Leveraging an integral path in the digital loop filter (DLF), dynamic track-and-hold functionalities are realized in the voltage tracking loop (VTL) for robust LUT calibration. Advanced phase control is investigated in a DTC modulator to eliminate the fluctuation of the loop locking voltage during large frequency hopping (>20% of the center frequency  $f_{center}$ ), which further secures 50ns  $T_{idle}$ .

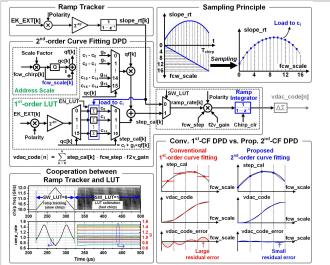

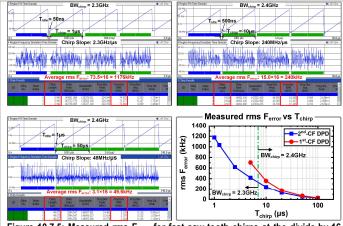

Conventionally, a 1st-order curve-fitting (1st-CF) DPD technique can be used to obtain a well-fitted VCO tuning curve, in which a 1st-order look-up table (1st-LUT) for ramp fitting [3] and 0th-order LUT for ramp-rate fitting [2] are both practical solutions. However, with an enlarged chirp BW and slope, the residual Ferror becomes more severe; thus, a higherorder curve-fitting DPD is required. Unfortunately, direct ramp fitting using a 2nd-order LUT suffers from high design and hardware complexity. In this work, by leveraging the integral mechanism of the ramp integrator, the 2nd-CF DPD functionality for ramp fitting is realized by implementing a 1st-LUT ahead of the ramp integrator as shown in Fig. 10.7.1. In the 1st-LUT, ci is estimated with an LMS algorithm, and gi is calculated by ci+1-ci. The chirpfrequency control word (FCW) fcw\_chirp[k] is scaled to cover 16 registers. As shown in Fig. 10.7.1 (bottom right), the proposed 2<sup>nd</sup>-CF DPD achieves smaller residual Ferror compared with the conventional 1st-CF DPD. However, due to the integral operation of the calibrated ramp rate and interactions among  $c_i$  through the calculation of  $g_i$  [4], the convergence of the LUT slows down and becomes unstable. To tackle this problem, a pre-running ramp tracker is leveraged to initialize the LUT with the coefficients that are close to final convergent states, and a multiplexer is utilized to switch between the ramp tracker and the LUT in different time slots. In the first chirp period, the ramp tracker is enabled to configure a slower chirp but with the same target BW. The sampling principle of the estimated slope slope\_rt[k] is demonstrated in Fig. 10.7.1 top right. Addressed by the scaled FCW fcw\_scale[k], 16 coefficients are sampled from slope\_rt[k] and then passed to ci in the LUT. Subsequently, the LUT is enabled to configure the desired fast chirp with the initialized c<sub>i</sub>. The cooperation between the ramp tracker and LUT is elaborated in Fig. 10.7.1 (bottom left) for over 100% VCO gain variations. Clearly, as most of the ramp non-linearity is estimated by the ramp tracker, the converged ci gets very close to the initialized value, greatly reducing the convergence time.

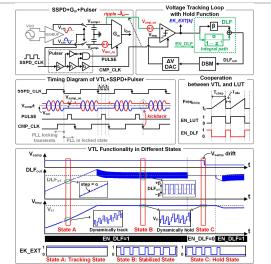

In an SS-PLL, the sign of the phase error for background calibration could not be extracted directly. Conventionally, it could be extracted from the output current of a transconductor  $G_m$  [2,3], but the comparator offset would cause calibration inaccuracies. Alternatively, as the sampling voltage  $V_{samp}$  of the SSPD stays stable while the SS-PLL is locked, a VTL could be utilized for sign extraction [6]. The architecture of the proposed VTL in cooperation with SSPD,  $G_m$ , and pulser and their timing diagrams are shown in Fig. 10.7.2. In each SSPD clock cycle, the comparator clock CMP\_CLK is delayed by a  $G_m$  pulse, which effectively prevents the PLL performance deterioration caused by the kickback effect. Within the voltage tacking range of the VTL, the locking point could be tracked precisely, overcoming the impact of process variations and circuit offsets (i.e.,

comparator offset  $V_{cmp_os}$  and  $G_m$  offset  $G_{m_os}$ ). However, in the ramp duration before the LUT convergence is accomplished, V<sub>samp</sub> fluctuates largely due to the unlocked phase, which further disturbs  $V_{tmp}$  and generates inaccurate EK\_EXT for the LUT calibration. As a result, the LUT convergence inevitably slows down. To tackle this issue, by newly involving an integral path to the DLF in the VTL, the non-zero offset of EK\_EXT could be removed, and  $V_{tmp}$  could be held during the ramp duration for a robust LUT calibration. In the DLF,  $\beta$  is set much larger than  $\alpha$  to ensure stability, and the tracking speed can be improved by enlarging  $\alpha$ . The detailed functionality of the VTL in three working states is shown in Fig. 10.7.2 (bottom). In the tracking state, with EK\_EXT=1, V<sub>tmp</sub> grows steadily along with DLFout, covering a wide trackable voltage range. In the stabilized state, DLFout tends to stabilize, and V<sub>tmp</sub> fluctuates around V<sub>samp</sub> within the maximum step of ΔV-DAC, generating a zero-mean EK\_EXT. In the hold state, the DLF is disabled, and its output maintains the last state of the integral path, which makes  $V_{\text{tmp}}$  immune to a  $V_{\text{samp}}$  drift. Subsequently, the DLF is enabled, and the VTL is activated again to update  $V_{tmp}$ . In this work, to operate the VTL properly with the LUT for robust sign extraction, EN DLF is enabled in T<sub>idle</sub> and disabled in T<sub>chirp</sub>, while EN\_LUT takes the inverse logic as shown in Fig. 10.7.2 (middle right).

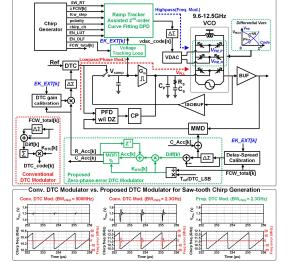

The architecture of the proposed FMCW chirp generator is shown in Fig. 10.7.3. In the lowpass injection path, a delay-spread calibration [7] is utilized to compensate for the response time of the VDAC. The DTC modulator could compensate the phase error caused by the quantization of a delta-sigma modulator (DSM), but there still exists a residual mismatch of the compensated phase error during the large frequency hopping in the conventional structure [2,3], which causes a  $V_{PLL}$  fluctuation in the  $T_{idle}$ . As shown in the two bottom-left figures in Fig. 10.7.3, the voltage fluctuation becomes more severe with wider BW<sub>chirp</sub>, and the loop fails to settle within tens of nanoseconds, which deteriorates Ferror at the beginning of each chirp. In this work, a zero-phase-error DTC modulator designed for the ultra-fast wideband saw-tooth chirp is proposed to eliminate the V<sub>PLL</sub> fluctuation over 2.3GHz frequency hopping. Based on the principles of the DTC compensation and phase modulation in the TPM, the exact extra phase, Diff[k]×K<sub>DTC</sub>[k], to be compensated in the k-th cycle is accumulated to generate a DTC code for sampling the next zero-crossing precisely, whereas the conventional DTC modulator fails, especially facing with large frequency hopping. To avoid an unbounded DTC code, the accumulated phase error ACC[k] is wrapped by the DTC gain KDTC[k], further generating the carries C ACC[k] and the residues R ACC[k] for the multi-modulus divider (MMD) and DTC, respectively. As shown in Fig. 10.7.3 (bottom right), with the proposed DTC modulator, the voltage fluctuation due to 2.3GHz frequency hopping is eliminated significantly, thus ns-level Tidle could be achieved. Moreover, an LC-VCO with complementary varactors is designed to enhance the linearity under >2.5GHz/V KVCO, and following the VDAC additional lowpass RC filters are used to suppress the DSM guantization noise.

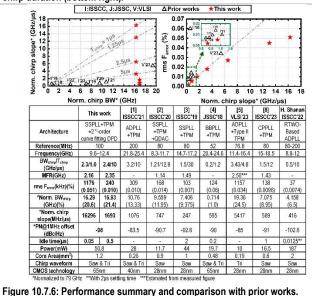

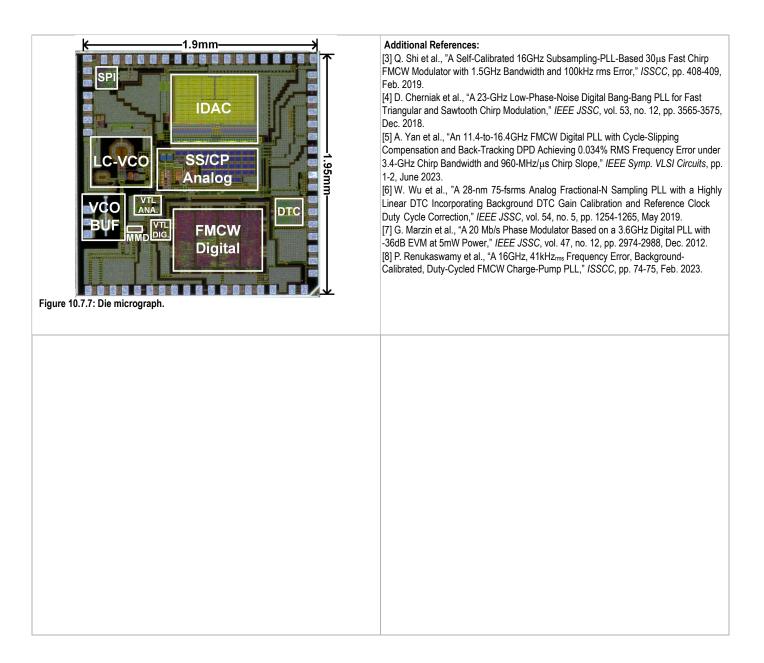

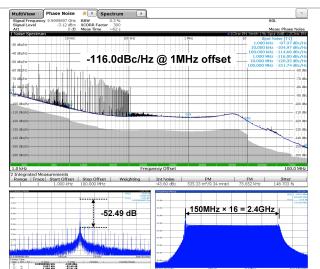

The proposed FMCW generator is fabricated in a 65nm CMOS process. The die micrograph is shown in Fig. 10.7.7, and the core area is about 1.2mm<sup>2</sup> excluding decoupling capacitors and test circuits. During chirp modulation, the measured power consumption is about 50.8mW. The fractional-N SS-PLL could generate frequency from 9.6 to 12.4GHz with a 100MHz reference clock. At 10GHz, the measured PN and spectrum of the proposed PLL in the fractional-N mode are shown in Fig. 10.7.4 to indicate the worst-case performance. The measured PN is -116.0dBc/Hz at a 1MHz offset, which is equivalent to -98dBc/Hz normalized to 79GHz, and the worst-case spur is -52.49dBc at a 1.5kHz offset. The divide-by-16 spectrum of the FMCW is measured with a 2.4GHz BW<sub>chiro</sub>. Figure 10.7.5 shows that the measured rms F<sub>error</sub> of the fastest chirp configured with a 2.3GHz/1µs chirp slope and 50ns T<sub>idle</sub> is around 1176kHz (0.051% of BW<sub>chirp</sub>) and the measured frequency range (MFR) is 2.16GHz. For a slower chirp with a 2.4GHz/10µs slope and 500ns T<sub>idle</sub>, the rms F<sub>error</sub> is about 240kHz (0.01% of BW<sub>chirp</sub>). Configured with a 2.4GHz/50  $\mu s$  slope and 1  $\mu s$  T  $_{idle},$  the rms  $F_{error}$  of the chirp is about 49.6kHz (0.002% of BW<sub>chirp</sub>). As shown in Fig. 10.7.5 (bottom right), the rms F<sub>error</sub> with the 1st-CF DPD and 2nd-CF DPD are compared under different chirp slopes, demonstrating that the 2<sup>nd</sup>-CF DPD outperforms the 1<sup>st</sup>-CF DPD especially for the faster chirp slope. Compared with prior works in Fig. 10.7.6, the proposed FMCW generator achieves the fastest chirp slope and the best chirp linearity with a ns-level idle time.

#### Acknowledgement:

This work was supported by the National Key R&D Program of China, No. 2018YFE0205900, and in part by Major Key Project of PCL (PCL2021A01-2).

#### References:

[1] Z. Shen et al., "A 24GHz Self-Calibrated ADPLL-Based FMCW Synthesizer with 0.01% rms Frequency Error Under 3.2GHz Chirp Bandwidth and 320MHz/µs Slope," *ISSCC*, pp. 450-451, Feb. 2021.

[2] P. Renukaswamy et al., "A 12mW 10GHz FMCW PLL Based on an Integrating DAC with 90kHz rms Frequency Error for 23MHz/µs Slope and 1.2GHz Chirp Bandwidth," ISSCC, pp. 278-279, Feb. 2020.

Figure 10.7.1: Block diagram of the ramp-tracker-assisted  $2^{nd}$ -order curve-fitting DPD.

Figure 10.7.3: Block diagram of the proposed FMCW synthesizer and the comparison of the frequency error between conventional and proposed DTC modulators (bottom).

Figure 10.7.5: Measured rms  $F_{error}$  for fast saw-tooth chirps at the divide-by-16 output. Comparison of the measured rms  $F_{error}$  between the 1st-CF DPD and 2nd-CF DPD under different chirp slopes.

Figure 10.7.2: Block diagram and the working principles of the VTL.

Figure 10.7.4: Measured PLL phase noise (top) and spectrum (bottom left) and measured saw-tooth chirp spectrum with a 2.4GHz chirp bandwidth and a  $10\mu s$  chirp duration (bottom right).