# Innovative 3D Power Module Defaults Detection via Thermal Impedance Analysis and Simulations

Louis Alauzet, Jean-Pierre Fradin, Alexandre Dezalay, Anne Castelan, Patrick Tounsi, Sophie Regnier

#### ► To cite this version:

Louis Alauzet, Jean-Pierre Fradin, Alexandre Dezalay, Anne Castelan, Patrick Tounsi, et al.. Innovative 3D Power Module Defaults Detection via Thermal Impedance Analysis and Simulations. PCIM Europe 2024 - International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Jun 2024, Nuremberg, Germany. hal-04810047

# HAL Id: hal-04810047 https://hal.science/hal-04810047v1

Submitted on 2 Dec 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Innovative 3D Power Module Defaults Detection via Thermal Impedance Analysis and Simulations

ALAUZET Louis<sup>1,2</sup>, CASTELAN Anne<sup>1,3</sup>, REGNIER Sophie<sup>1</sup>, FRADIN Jean-Pierre<sup>1</sup>, DEZALAY Alexandre<sup>1</sup>,TOUNSI Patrick<sup>2</sup>

<sup>1</sup> Icam School of Engineering, Toulouse campus, 75 av. De Grande Bretagne, CS 97615, 31076 Toulouse Cedex 3, France

<sup>2</sup>LAAS-CNRS, Univ. De Toulouse, INSA-Toulouse, Toulouse, France

<sup>3</sup>Laboratory of Plasma and Energy Conversion (LAPLACE), University of Toulouse, 31000 Toulouse, France

Corresponding author:ALAUZET Louis, louis.alauzet@icam.frSpeaker:ALAUZET Louis, louis.alauzet@icam.fr

## Abstract

This article presents a method for detecting physical defects in an innovative 3D Silicon (Si) power module by measuring thermal impedance (Zth). A non-invasive method for measuring the junction temperature of dies is introduced (voltage drop across a diode under constant current), and a comparison is made with simulation results (CELSIUS EC SOLVER software). The observed differences are analyzed to propose hypotheses for defects origins and location. A scanning electron microscopy (SEM) observation is also used to validate these hypotheses. The results confirm that the comparison between experimental and simulation data of Zth is a precise method for determining the areas of physical defects.

### Terms and definitions

$\alpha$ : thermal diffusivity [ $m^2$ /s]

λ: thermal conductivity [W/m/K]

P: Power dissipated by the die [W]

$Tj_c(t)$ : Junction temperature of a die acquired after cooling during a time t [°C]

$Tj_h(t)$ : Junction temperature of a die acquired after heating during a time t [°C].

T<sub>ref</sub>: Ambient temperature [°C]

### 1 Introduction

The electrification of transportation systems (aircrafts, automotive, trains), along with current environmental challenges, have led to an increased demand for higher performance in power electronic modules. It is crucial to reduce electrical and thermal losses. Packaging plays a significant role in this task: it allows efficient heat dissipation from the dies and enables an expansion of the Safe Operating Area (SOA). The need for improved performance has driven innovation in packaging technology.

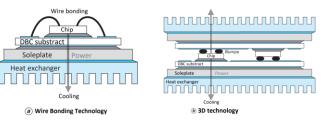

Fig. 1 bonding 2D and bump 3D architectures

Traditional 2D architectures evolves into 3D architectures, as shown in Fig.1 where bonding wires are replaced by a second substrate and cooling system, with an electrical connection made of bumps [1]. As it can be seen on the same figure, dies are also staggered (alternate between the first and second substrate) to improve cooling efficiency.

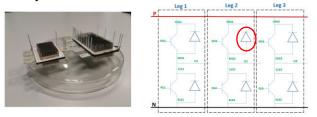

Fig. 2 Monobox module and its electrical composition

$aPSI^{BD}$  startup offers a 3D module, named Monobox, with low theoretical thermal resistance (Rth) of 0.35°C/W for its diodes.

The module is a half-bridge three-phase inverter designed for the automotive industry, as shown in Fig.2. Each switching cell consists of two IGBTs and two diodes in anti-parallel configuration. The dies are directly sintered onto a substrate (Backside), and the connection on the other side is achieved by sintered bumps (Frontside). The substrates use DBC (Direct Bonded Copper) technology. Heatsinks are directly brazed onto them.

The main advantages of this architecture are a reduction in parasitic inductance (caused by wire bonding) and a decrease in Rth (0.75 °C/W for the Acepack 2 sixpack topology module, which is the 2D equivalent of the 3D Monobox (0.35°C/W) by STMicroelectronics). The innovation of this 3D module is the fact that there are no thermal interface materials with high thermal conductivity: everything is brazed or sintered. That's why the Monobox power density theoretically reach 100kW/L, where best commercialized modules struggle to reach 60kW/L (Fig.3).

Fig. 3 Power density of traction inverters from various electrical vehicles [1]

While very promising for the future, the use of this architecture still faces a major struggle: the technological maturity of the module assembly processes. In fact, this kind of architecture has been on the market since 2008 [1], but mostly with one phase inverters. This module being a three-phase inverter, manufacturing is a greater challenge: the mechanical and thermal constraints currently encountered during the manufacturing process and the use of the module can lead to delamination and fractures between the various materials inside the module.

The objective of this article is therefore to detail a method for the thermal characterization of a power module through comparison between thermal impedance measurements and simulations, to perform a design validation.

#### 2 Methods of measurement

#### 2.1 Cooling and pulsed heating Zth

The thermal impedance can be obtained by two distinct processes depending on the curve studied: Cooling or heating. In both case it describes the thermal comportment of a module to a particular pulsed power [2].

The heating curve Zth expression is:

$$Z_{th_h} = \frac{Tj_c(t) - T_{ref}}{P}$$

(1)

The cooling curve Zth expression is:

$$Z_{th_{c}} = \frac{Tj(t=0) - Tj_{c}(t)}{P}$$

(2)

With the cooling method, a power is applied to the device until it is thermalized. Then the power is shut down and the junction temperature is acquired until the device is again thermalized. With this method a curve is obtained, depending on the frequency of acquisition of the temperature.

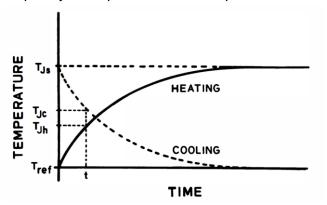

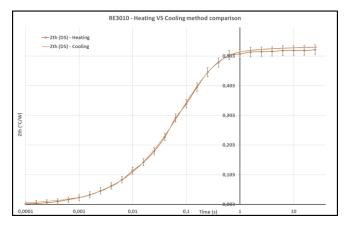

**Fig. 4** Comparison of cooling and heating curves for a semiconductor device

With the heating method, a power is applied for a known time, then at the end of the injection the junction temperature is measured. It is repeated with increasingly long injection times, until thermalization time is obtained. With this method, only few points are obtained, corresponding to power injection times (from 100µs to 100s, with 5 points per decade in this article)

In theory, if the thermal diffusivity and conductivity of the tested device are not dependent of the temperature, the two temperature curves should be conjugate (Fig.4). As the thermal conductivity of the Silicon is temperature dependent, it should be expected that results will differ depending on which method is used.

#### 2.2 Extrapolation of junction temperature

Whatever method is chosen to get the Zth, measuring the junction temperature is needed. To do so, many solutions exist: Thermocouple, IR cameras and optical fibers to name but a few. But as all of those solutions need a direct access to the die tested, or at least a visual access, they are not suited to obtain junction temperature of 3D modules.

Another well-known solution is the thermally sensitive electrical parameter (TSEP). It's a non-intrusive solution since only an electrical parameter is measured. To determine the thermal characterization of the Monobox, it has been decided that the Zth studied would be the diode's Zth (easier to measure than the IGBT with TSEPs) [3]. Hence the voltage drop of the diode under low continuous current (Vf) will be the TSEP used [3].

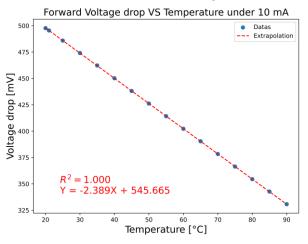

This TSEP shows good linearity and is quite sensible to thermal variation (2.39mV/°C) (see Fig.5). This curve has been obtained by heating the diodes with a modification of the temperature of the cooling system, between 20°C to 90°C, and measuring the voltage drop with a 10mA injection. Moreover, with 10mA forward current, the power dissipation of the measure is negligible (under 5mW at 20°C), meaning it's a truly non-invasive solution that won't self-heat diodes during measure.

**Fig. 5** Temperature VS Voltage drop under 10mA for Monobox diodes.

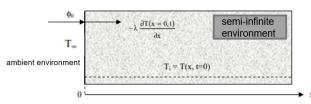

A drawback of the use of Vf as a TSEP is the fact that the measure of the junction temperature cannot be obtained during the self-heating process, nor after few hundreds of microseconds after it's shutdown. This is due to non-thermal electrical transient variations. Its origin is still unknown, but certainly due to parasite inductances, resistances, and capacitances in the circuit or module [4]. [4] and [3] propose the solution of the extrapolation of the junction temperature: In a semi-infinite solid, if the dissipation of power is surfaced based, the evolution of the temperature is linear with the root of the time (cf. Fig.6 and equation 4).

Fig. 6 Semi-infinite slab scheme with imposed surface flux

$$\overline{T}(x,t) = \operatorname{ierfc}\left(\frac{x}{2\sqrt{\alpha t}}\right)\frac{2P}{\lambda}\sqrt{\alpha t}$$

(3)

$$\Rightarrow T_j(0,t) = \frac{2P}{\lambda}\sqrt{\alpha t} + T_a \tag{4}$$

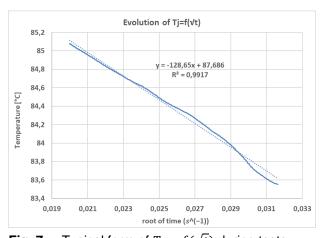

**Fig. 7** Typical form of  $T_j = f(\sqrt{t})$  during tests It should be noted that the power dissipation of a diode is not surface based, but volumic [4]. Despite this approximation, extrapolation has proven to give precise results when compared to other means of temperature measurement. [4]. The Fig.7. shows good linearity of the temperature with the root of time, using the diodes of the module.

Hence even with non-thermal electrical transient, extrapolation allows the use of the voltage drop of the diode under low continuous current to get junctions temperatures, for cooling and pulsed heating measures.

# 2.3 First results: comparison between heating and cooling curves

The two possible tests were conducted to determine if a noticeable difference could be found between them.

**Fig. 8** Comparison on the RE3010 module (double sided cooling) between Zth curves using cooling and heating method.

For the Rth value, the relative deviation is less than 1.7%, (Fig.8) and under the error margin. A small difference can be observed for the smallest times, which can be explained by the difference of conductivity of Si depending on the temperature. Hence for this module it is shown that the two methods give about the same results. However, the constraints to be respected during testing are different: for the heating curves, each point requires the module to be heated. It's not a problem for times under 1 second, but the fact that each point is tested multiple times to reduce dispersion of the results could lead to premature aging of the module. Where more than 40 temperature cycling are needed to get a heating curve, only 4 are done to get the cooling one.

Since it has been noticed during tests that the module ages after multiple cycles, the cooling method will be preferred.

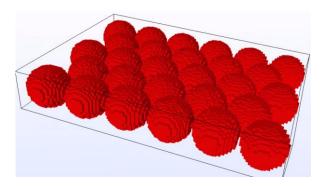

### 3 Simulation analysis

#### 3.1 Power module presentation

To compare results of said TSEP temperature measurement and hence to conclude on the presence of defects, a simulated functioning module was made.

The 3D thermofluidic finite element volume software used for this study is CELSIUS EC SOLVER. Numerical simulation aims to precisely reproduce the experimental conditions of the tests.

The cooling fluid is a 50% glycoled water, at 20°, and 4L/min flow rate in each cooling duct.

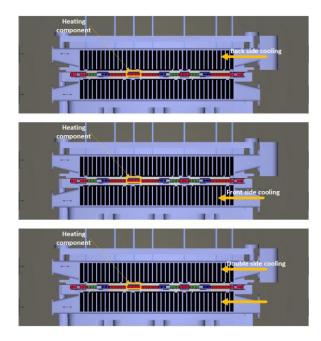

To precisely reproduces experimental tests, three cooling solutions are available on this module (one or double side cooling), that are defined as Front side cooling (FS), Back Side cooling (BS) and Double side cooling (DS) (Fig.11).

**Fig. 9** Isometric view of power module (left) and top view of one's power module side (right)

The direction of cooling is based on the position of the active cooling duct with the heating component (Fig.11).

To be close to experimental test conditions, when a one side cooling simulation is done, the cooling duct associated to the turned off pump is still full of glycoled water, with no flow rate.

As the power module geometry is complex (strong scale factor), define a precise mesh is a key factor for an accurate simulation result.

Bumps are doing thermal and electrical contact, so their mesh shape must be well defined. Final non conform parallelepiped volumic mesh provides a good definition of the assembly, as shown in Fig.10.

Fig. 10 Mesh of thermal bumps inside power module

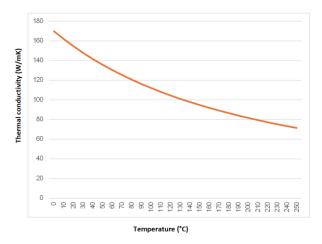

It should be noted that the thermal conductivity of the Silicon of the dies is dependent of its temperature (Fig.12). Other material properties are summarized in Table 1.

|                             | Conductivity<br>(W/m.K) | Specific heat<br>(J/kg.K) |

|-----------------------------|-------------------------|---------------------------|

| PEI-Plastic                 | 0.25                    | 1260                      |

| Al2O3 Curamik               | 24                      | 900                       |

| Aluminum metal-<br>lization | 235                     | 921                       |

| Porous silver               | 100                     | 232                       |

| Copper pure                 | 386                     | 380                       |

| Glue joitns                 | 0.1                     | 700                       |

| Underfill                   | 0.7                     | 3000                      |

| Sumitomo braze              | 20                      | 1005                      |

Table. 1 3D power module material properties

**Fig. 11** Three types of possible cooling configuration for a heating component inside the module: BackSide, FrontSide, and double side.

Fig. 12 Thermal conductivity of Silicon

# 3.2 Simulated thermal impedances on 3D module and classic 2D module.

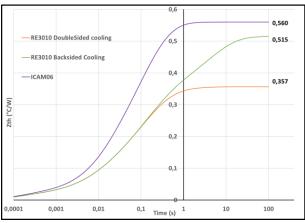

**Fig. 13** Thermal impendences curves (Zth) of RE3010 with doubleside and backside cooling and Icam06 modules

To prove the interest of such 3D modules of classic ones, a simulation of the 3D RE3010 module and the ICAM06 one (a classic 2D module made by  $aPSI^{\beta D}$ , using only one ceramic substrate with bonding dies) has been done (Fig.13).

When the RE3010 is backside cooled, part of the flux passes through the bumps to the opposite ceramic substrate before using other dies to transfer the heat flux. This contributes to die cooling and explains the difference between Icam06 Rth and backside cooling RE3010 Rth.

This study shows the theorical 3D architecture is a huge improvement (diminution of the Rth by 65%) compared to a classic module.

### 4 Experimental setup and Tests

Tests have been conducted on the <u>DepTH-LAB</u> [6] platform at Icam Toulouse.

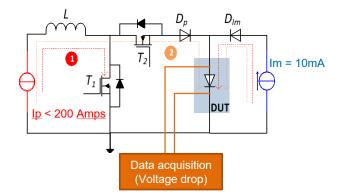

The electrical part of the test bench consists of two current circuits. The first circuit comprises a power current source with an inductance (L) of 8mH, ensuring a constant current flow even with minimal injection times. This circuit (Fig.14) utilizes two Mosfets (T1 and T2) to control the power current (Ip) through the diode. Precise switching of the Mosfets is essential to ensure accurate current injection timing and prevent the circuit from remaining open with the inductance still charged.

Fig. 14 Electrical schematic of the test bench

The second circuit consists solely of a 10mAmps current source (Im) that remains continuously active, providing temperature readings when the power current (Ip) is deactivated.

Voltage drop is continuously monitored to extrapolate the temperature when the power current is off and to determine the power dissipation of the diode when the power current is on.

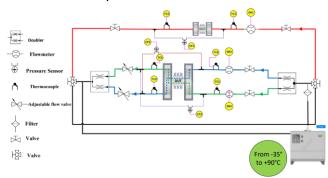

Fig. 15 hydraulic schematic of the test bench

The thermal part of the test bench (Fig.15) has been constructed to allow such control on the cooling process. A cryostat is used to precisely set the temperature of the cooling fluid (50% glycoled water, at 20°C).

Splitters are employed to enable cooling of the module on both sides, and two valves can be used to fine-tune the flow rates independently. Temperature of the liquid can be acquired by thermocouples if needed. The temperature of the liquid used for subsequent tests is 20°C unless otherwise specified.

# 5 Comparison between tests and simulations for Zth Curves

A first steady state analysis is done, using both simulation software and experimental setup previously discussed.

The first studied module, named RE3010 is a complete 3D module, with radiators. In each case the

diode under test will be the diode HS2 (visible in red circle in Fig.2).

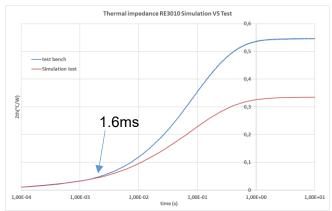

Fig. 16 Simulated and tested Zth on RE3010 double sided cooling

The differences between experiments and simulations show that the thermal resistance (Rth) of real modules is much higher than it should be (relative deviation of 63%).

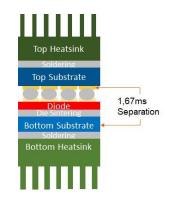

This indicates that defects are present. By studying separation moment between simulated and test curves and by linking it with the thermal diffusivity and thermal transit time of each material of the module a location where a defect is present can be extrapolated. It should be added that since cooling takes place in a true 3D environment, with thermal loops through the two substrates that occur due to other unheated dies, the study of the structure functions usually used [5] is of little relevance here and the deduction of the delamination site is rendered more difficult. These Zth results are shown in Fig.16.The comparison between the two curves of the figure indicates a separation at approximately 1.6ms.

Fig. 17 Trench View of the module with proposed sites of defect

Then, thanks a study of the different thermal diffusivity and transit times of materials, a conclusion can be drawn: defects might be present either in the upper bump bonding or in the bottom substrate of the die (cf. Fig.17).

To investigate the two possible defects, it has been decided to manufacture a new module, named ICAM06. It's a half-module, meaning that the bumps are replaced for classical bonding. As there isn't top substrate nor top heatsink the cooling process can only be achieved by its backside.

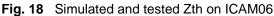

A special simulation model is created for this module.

It appears with those curves (Fig.18) that there is no significant difference between simulations and tests. Meaning that there is no delamination in substrates.

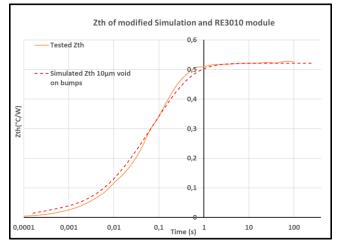

**Fig. 19** Comparison of RE3010 double and backside cooling Zth curves

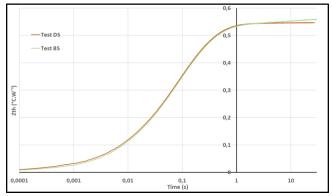

The Fig.19 seems to indicate that there is no difference between double sided cooling and backside cooling on the RE3010 module, which could mean that the bumps play no role in the cooling process. To test the possible delamination of the bumps, simulations have been conducted with air gaps between bumps and their sintering, to be compared with experimental results. The obtained curves in Fig.20 demonstrates that the addition of these imperfections enables the simulation to closely match the experimental results. The differences in Rth do not exceed 6% (maximum deviation observed at the backside).

As simulations match tests, it is considered that defects indeed come from the bumps, or its sintering.

#### 6 SEM analysis

Some interfaces between small Cu bumps / Sintered Ag / Cu substrate are observed using SEM (Scanning Electron Microscope Hitachi TM4000Plus) to conclude about delamination of bumps.

#### 6.1 Preliminary preparations

Before observations, the module has been cut foll owing the Fig.21, polished using SiC papers (from grade P600 to P1200) and finally polished with di amond suspension up to a size of  $1\mu m$ .

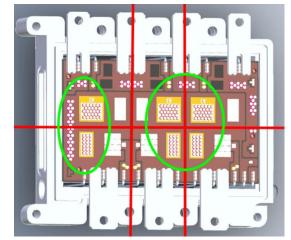

**Fig. 21** Position of cutting areas (red lines: Limit of the cutting – green circles, planned observation areas)

#### 6.2 SEM observations

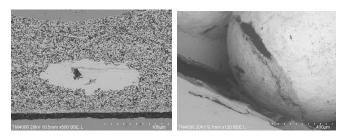

Some of the observed samples indicate sintered Silver as waited, showing sintered silver without any microcracks nor cracks (Fig.22-left); but most of the observations indicate some defaults as:

- Inefficient sintering (fig.22-right)

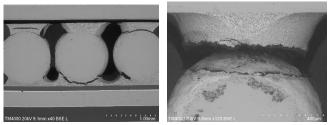

- Microcracks (fig.23-left)

- Total delamination between sintered silver and bumps due to a frequent lack of diffusion between bumps and silver powder (Fig.23-right).

- Compression areas in the substrate leading to cracks (Fig.22-right).

**Fig. 22** Left: Well sintered Silver – Right: Microcracks of the substrate and inefficient sintering

**Fig. 23** Left: Microcracks – Right: Total delamination between bump and silver.

Those observations conclude that the defects of the module were indeed situated at the level of the bumps. The advantage of the SEM observation remains the capability to conclude on the origin of the defect (bad quality of sintering), where the thermal curve analysis could only describe the place where the defect occurred (but is non-invasive and doesn't necessitate the destruction of said module). Advice was given to the manufacturer (aPSI3D) to resolve those defects: More Sintering should be used, of better quality.

#### 7 Conclusions

A non-intrusive test has been developed to acquire diodes junction temperature of 3D inverter module, using the voltage drop of diodes under low current, and the extrapolation of temperature with the surface-based power dissipation hypothesis.

A perfect module was simulated using the CEL-SIUS EC SOLVER software. The comparison between simulations and tests, linked with thermal diffusivity, has made possible to formulate two hypotheses on the defects.

The possible delamination in the substrate was not observed on a one substrate module (ICAM06). Modified simulations of the module with air gap between the bumps and the substrate proved to obtain Zth curves very similar to tested ones.

SEM observations tend to demonstrate that bumps and their sintering show a large disparity of quality, which comfort the fact that the defects of 3D modules can be found by thermal impedance curves analysis and comparisons.

#### References

- M. Liu, A. Coppola, M. Alvi, and M. Anwar, "Comprehensive review and state of development of double-sided cooled package technology for automotive power modules," IEEE Open Journal of Power Electronics, vol. 3, pp. 271–289, 2022.

- DOI: 10.1109/ojpel.2022.3166684.

- [2] D. L. Blackburn et F. F. Oettinger, « Transient thermal response measurements of power transistors », IEEE Transactions on Industrial Electronics and Control Instrumentation, no 2, p. 134-141, 1975.

- [3] Q.C.Nguyen, "développement d'outils electrothermiques pour la localisation de defauts et pour l'optimisation de la performance de modules mecatroniques de puissance SiC," Theses, INSA de Toulouse, Sep. 2021..

- [4] B. Thollin, « Outils et méthodologies de caractérisation électrothermique pour l'analyse des technologies d'interconnexion de l'électronique de puissance », Université de Grenoble, 2013.

- [5] V. Szekely, "A new evaluation method of thermal transient measurement results," ´ Microelectronics Journal, vol. 28, no. 3, pp. 277– 292, Mar. 1997. DOI: 10.1016/s0026-2692(96)00031-6.

- [6] https://en.icam.fr/research/depth-lab/