# Cryptanalysis of Algebraic Verifiable Delay Functions

Alex Biryukov, Ben Fisch, Gottfried Herold, Dmitry Khovratovich, Gaëtan Leurent, Maria Naya Plasencia, Benjamin Wesolowski

## ▶ To cite this version:

Alex Biryukov, Ben Fisch, Gottfried Herold, Dmitry Khovratovich, Gaëtan Leurent, et al.. Cryptanalysis of Algebraic Verifiable Delay Functions. CRYPTO 2024 - 44th Annual International Cryptology Conference, Aug 2024, Santa Barbara (CA), United States. pp.457-490, 10.1007/978-3-031-68382-4 14. hal-04782206

# HAL Id: hal-04782206 https://hal.science/hal-04782206v1

Submitted on 14 Nov 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Cryptanalysis of Algebraic Verifiable Delay Functions\*

Alex Biryukov<sup>1</sup>, Ben Fisch<sup>2</sup>, Gottfried Herold<sup>3</sup>, Dmitry Khovratovich<sup>4</sup>, Gaëtan Leurent<sup>5</sup>, María Naya-Plasencia<sup>5</sup>, and Benjamin Wesolowski<sup>6</sup>

- $^{\rm 1}$  University of Luxembourg, Esch-sur-Alzette, Luxembourg  $^{\rm 2}$  Yale University, New Haven, USA

- $^{3}$  Ethereum Foundation, Bonn, Germany

- Ethereum Foundation, Luxembourg City, Luxembourg INRIA, Paris, France

- <sup>6</sup> ENS de Lyon, CNRS, UMPA, UMR 5669, Lyon, France

**Abstract.** Verifiable Delay Functions (VDF) are a class of cryptographic primitives aiming to guarantee a minimum computation time, even for an adversary with massive parallel computational power. They are useful in blockchain protocols, and several practical candidates have been proposed based on exponentiation in a large finite field: Sloth++, Veedo, MinRoot. The underlying assumption of these constructions is that computing an exponentiation  $x^e$  requires at least  $\log_2 e$  sequential multiplications. In this work, we analyze the security of these algebraic VDF candidates. In particular, we show that the latency of exponentiation can be reduced using parallel computation, against the preliminary assumptions.

**Keywords:** Verifiable Delay Functions  $\cdot$  MinRoot  $\cdot$  Veedo  $\cdot$  Sloth++  $\cdot$  cryptanalysis  $\cdot$  smoothness

#### 1 Introduction

A verifiable delay function (VDF) [11] is a function  $f\colon X\to Y$  that on average cannot feasibly be evaluated much faster than some prescribed time T, even on a parallel machine, but every output y=f(x) comes with a proof that allows anyone to quickly verify the output is correct. The first property makes it a delay function and the second makes it verifiable. In more detail, a VDF is a triple of algorithms:

- Setup $(1^{\lambda}, T) \to pp$ ; returns public parameters pp given a security parameter  $\lambda$  and delay parameter T.

- Eval $(pp, x) \to (y, \pi)$ ; returns  $y \in Y$  given  $x \in X$  and a proof  $\pi$ .

- Verify $(pp, x, y, \pi) \to \{0, 1\}$ ; returns 1 if y is the correct output of input x.

$<sup>^\</sup>star$  © IACR 2024. This article is the full version of the paper with the same title published by Springer-Verlag in the proceedings of CRYPTO 2024.

The algorithms Setup and Verify are polynomial time and the algorithm Eval(pp, x), which is allowed to use up to  $\text{poly}(\lambda)$  parallel processors, runs in time at most  $(1+\varepsilon)T$  for some  $0<\varepsilon<1$ . Any parallel algorithm using at most  $\text{poly}(\lambda)$  processors and running in time less than T should not be able to compute f(x)=y except with  $\text{negl}(\lambda)$  probability over random x. We refer to [11] for a more complete and formal definition.

VDFs have been most notably applied to removing bias in randomness beacons<sup>7</sup>, which play an important role in consensus protocols, especially those used in modern blockchains [11,15,23,44]. The randomness may be used both to select block proposers unpredictably, or in the application layer, e.g. to simulate lotteries or more sophisticated protocols. Unbiasable randomness beacons can also be constructed from coin-tossing protocols [10], or from distributed key generation and verifiable random functions (VRFs) [30], but these constructions require a majority of parties participating in the protocol to be honest. In addition to requiring honest-majority assumptions, such protocols are communication-intensive and prone to delays in the case of a dynamic player set. In contrast, constructions of randomness beacons using VDFs are simple, communication efficient, and only require one participating party to be honest. VDFs have also been particularly important for constructing blockchains using proof-of-space as an alternative to proof-of-work<sup>8</sup>, or more broadly achieving dynamic availability in consensus protocols without proof-of-work [20]. There are many other applications, including to proofs-of-replication [11,25], voting protocols [5], and preventing front-running of trades in decentralized exchanges [17]. See [37] for a survey of applications.

Any delay function can be made verifiable using generic SNARKs [11,36]. However, it is desirable to construct delay functions with specialized proof systems that result in a more efficient Eval algorithm than the generic construction (i.e., requiring fewer parallel processors and lower overall complexity).

There are two elegant and efficient constructions of VDFs based on repeated squaring in a group of unknown order [59,39], as well as constructions based on sequential compositions of isogenies on elliptic curves [19,46,4]. There are several candidates for groups of unknown order. One is the RSA group  $\mathbb{Z}_N^*$  for  $N=p\cdot q$  a product of two unknown safe primes, provided that the group is set up by a trusted party who discards p and q. The assumption that repeated squaring is sequential in this group was previously used in the construction of timelock puzzles [41], and over generic rings has been proven equivalent to the difficulty of factoring [42]. Multiparty computation can be used to generate a trusted RSA modulus [12,16,27], but this has been found to be challenging and error-prone to implement. Two candidates that do not require a trusted setup are class groups of quadratic number fields and Jacobians of hyperelliptic curves [22]. Unfortunately, the security of VDFs in class groups or Jacobians is based on less

<sup>7</sup> https://a16zcrypto.com/posts/article/public-randomness-and-randomness-beacons/

<sup>8</sup> https://docs.chia.net/green-paper-abstract/

https://medium.com/zengo/dogbyte-attack-playing-red-team-for-eth2-0vdf-ea2b9b2152af

studied assumptions (e.g., difficulty of finding low order elements in the class group of an imaginary quadratic number field). The security of VDFs based on isogenies is similarly based on relatively new assumptions.

In theory, a sequential composition of hash functions, when modeled as random oracles, is provably a delay function [35]. While this might suggest that the generic construction from SNARKs is the most robust direction for VDFs, in practice no concrete hash function behaves like a true random oracle. Moreover, the way this hash function is constructed can have a big impact on the efficiency of Eval, specifically the complexity of computing a SNARK for many interactions of the functions. The complexity of the SNARK is proportional to the complexity of verifying f(x) = y directly, using an arithmetic circuit over a finite field. One direction that was suggested in [11] and explored further in [52,29] is to use an iterated permutation  $\Pi$  over  $\mathbb{F}^n$  that has (a) low arithmetic complexity as a circuit over  $\mathbb{F}$ , and (b)  $\Pi^{-1}$  has even lower complexity than  $\Pi$ , which helps with the SNARK. One such candidate are permutations that use a round function  $x^e \mod p$  for  $e \gg 2$  where the inverse operation is exponentiation by  $a = e^{-1} \mod p - 1$  for  $a \ll e$ . The assumption that  $x^e \mod p$  is sequential, i.e. that it cannot be evaluated substantially faster than repeated squaring on a reasonable number of parallel processors, originates in the Sloth system [33], a precursor to VDFs. This method is used in the VDF candidates Sloth++ [11], Veedo [52], and MinRoot [29].

In this work, we present parallel algorithms for evaluating  $x^e \mod p$  several factors faster than  $\log_2 e$  steps, challenging this assumption that was widely used in constructions of VDFs, including one that was planned for use in Ethereum's consensus protocol and Filecoin, and for which an ASIC had already been developed [53,54]. As a response to our attacks, those plans have been put on hold [28]. We conclude by suggesting several alternative directions for VDFs that are not known to suffer from our attacks.

#### 1.1 Algebraic VDF Proposals

We first describe concrete VDF proposals based on exponentiation in a finite group and their security claims.

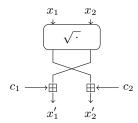

Sloth++ [11]. The round function in the Sloth++ VDF candidate involves two interleaved permutations  $\rho$  and  $\sigma$  over  $\mathbb{F}_{p^2}$  where  $p \equiv 3 \mod 4$ . The function  $\rho(\mathbf{x}) = \mathbf{x}^{(p^2+1)/4}$  returns a square root of  $\mathbf{x} \in \mathbb{F}_{p^2}$  and has inverse  $\rho^{-1}(\mathbf{y}) = \mathbf{y}^2$ . The function  $\sigma(\mathbf{x})$  interprets  $\mathbf{x} = (x_1, x_2)$  as a vector over  $\mathbb{F}_p^2$  (i.e., the coefficients of a degree two polynomial) and returns  $\sigma(x_1, x_2) = (x_2 + c_1, x_1 + c_2)$  for some fixed constants  $c_1, c_2 \in \mathbb{F}_p$ .

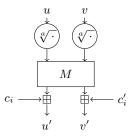

**Veedo [52].** The round function of Veedo operates on a pair of elements (u, v) in  $\mathbb{F}_p$ . It first applies a root operation to each element, then applies a linear layer defined by an MDS matrix.

**Algorithm 1.** Sloth++ VDF.

**Fig. 1.** Sloth++ round function.

```

Input: u, v \in \mathbb{F}_p

for 0 \le i < n_{\text{iterations}} do

(u, v) \leftarrow M \times (\sqrt[a]{u}, \sqrt[a]{u}) + (c_i, c_i')

return u, v

```

Algorithm 2. Veedo VDF.

Fig. 2. Veedo round function.

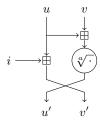

**MinRoot** [29]. MinRoot is a VDF proposal that was designed to be used as a randomness beacon in the core layer of the Proof-of-Stake Ethereum protocol<sup>10</sup>. It iterates  $n_{\text{iterations}}$  times a simple round function, which is concretely given as an a'th root for small a in a finite field defined by a prime number p such that  $\gcd(a, p-1)=1$ , as shown in Algorithm 3. A proof of evaluation is supposed to be a SNARK proof, output by the Nova prover [31]. We denote the internal state of MinRoot as (u, v), and the round counter as i.

```

Input: u, v \in \mathbb{F}_p

for 0 \le i < n_{\text{iterations}} do

(u, v) \leftarrow (\sqrt[a]{u + v}, u + i)

return u, v

```

Algorithm 3. MinRoot VDF.

Fig. 3. MinRoot round function.

The concrete parameters proposed by the MinRoot designers are as follows:

$$\begin{array}{l} -\ p = 2^{254} + 2^{32} \cdot {\tt 0x224698fc094cf91b992d30ed} + 1, \\ -\ a = 5, \end{array}$$

<sup>10</sup> https://ethereum.github.io/consensus-specs/

- The number  $n_{\text{iterations}}$  of iterations is typically in the order of  $2^{40}$ .

MinRoot has concrete security claims and an ASIC implementation has been developed, therefore we explain in more detail its implementation properties, security claims, and functionality.

Currently, in the Proof-of-Stake Ethereum protocol every 32 blocks constitute an epoch, and the epoch block proposers contribute some entropy values  $s_1, s_2, \ldots, s_{32}$  (omissions are possible). The values are passed to a classical hash function whose output is declared a *random beacon*, which determines proposers and signers for the next epochs. Clearly, the last of 32 proposers can influence the beacon value by trying different entropy values.

To mitigate this issue, VDF f would be applied to  $(s_1, s_2, \ldots, s_{32})$ . The calculation of f would run for the M next epochs, and the result would then determine the block proposers for the M+1-th epoch. Assuming that no parallel adversary could compute the VDF faster than by a factor of M and that each epoch has at least one honest proposer, there is no way for any malicious proposer, who learns the other contributions of a given epoch only during that epoch, to precompute f and find some contribution  $s_i$  of his own that would give a desired VDF output.

**MinRoot Implementation.** A standard implementation of MinRoot, such as the one by Supranational [53], computes the rounds iteratively. The root is the most expensive operation in the round function; in each round, it is computed using Fermat's little theorem (as  $\sqrt[q]{x} = x^{1/a \mod p - 1}$ ), with a square and multiply algorithm. We define  $e = 1/a \mod p - 1$  so that the round function is written as  $\sqrt[q]{x} = x^e$ . Recall that a is chosen such that  $\gcd(a, p - 1) = 1$ .

Exponentiation to the power e with the square and multiply algorithm requires  $\log_2(e) \approx \log_2(p)$  squarings. There are techniques to reduce the number of multiplications (such as the sliding-window method or addition chains), but in the context of a low latency implementation it is better to use a naive binary decomposition because the multiplications can be evaluated in parallel with the squarings. Therefore, the delay of one round is essentially  $\log_2(p)$  squarings (254 squarings with the proposed parameters), and the delay of MinRoot is essentially  $n_{\text{iterations}} \cdot \log_2(p)$  squarings (using two processors: one for the squarings and one for the multiplications).

In practice, Supranational built an optimized ASIC implementation of MinRoot, on a 12 nm node [53,55]. Their implementation requires 257 cycles per round, where each cycle essentially corresponds to a squaring and takes 0.9 ns (230 ns per round).

MinRoot security claims and their interpretation. The security claim of MinRoot is that it is a sequential function. Informally, this means that MinRoot cannot be computed faster by using some parallelism. There should be a lower bound to the delay required to evaluate the function, and the standard implementation with a delay of  $n_{\text{iterations}} \log_2(p)$  squarings should be close to this lower bound (up to a small constant factor).

This implies at least two distinct assumptions:

- 1. The round function itself is a sequential function (*i.e.* the root cannot be computed faster using parallelism);

- 2. The iteration is sequential (*i.e.* there is no shortcut to evaluate  $n_{\text{iterations}}$  rounds faster than by iterating them).

Formally, MinRoot is claimed to have 128 bits of VDF security, defined as follows: Given up to  $2^{128}$  parallel processors, no adversary using these processors and spending up to  $2^{128}$  MinRoot calls in precomputation, can compute MinRoot on any input from a challenge set faster than by a factor of 2.

One may notice that the security claim of MinRoot is somewhat vague. Concretely, it misses the following details, which became apparent at the time of third party analysis:

- What the reference implementation of MinRoot is and what timing it claims.

- What the computation model is, which might be needed to determine whether the adversary is faster than the legitimate computation.

For the first issue, we refer to the third-party implementation of MinRoot in hardware by Supranational [53]. They report latency benchmarks and chip sizes [55]. For the second issue we had to choose between existing models in the parallel computation analysis (cf. a survey in [43]) and some ad-hoc model. We resorted to the second option for two reasons:

- Our model matches nicely with the existing hardware implementation by Supranational.

- We assign realworld-inspired numbers to memory access and CPU access timings, which scale reasonably with the network size.

#### 1.2 Notations and Assumptions

We focus on the latency of evaluating VDFs in parallel from an algorithmic point of view. In particular we evaluate the latency of the computation and neglect the latency of communication between the processors, and implementation issues such as large fan-in or large fan-out.

While the VDF we study naturally works with modular values in  $\mathbb{F}_p$ , in this paper, we sometimes consider the values as integers instead; we believe this should be clear depending on the context. The notation  $x \mod q$  refers to the integer in  $\{0, 1, \ldots, q-1\}$  that is congruent to x. When taking logarithms, we default to base-2 (but usually write it out unless it does not matter, such as in  $\mathcal{O}$ -expressions).

Latency Assumptions. We consider the following results on low-latency arithmetic operations:

**Integer addition:** Addition of two *n*-bit integers has a latency of  $\mathcal{O}(\log(n))$  using a carry look-ahead adder (*e.g.* the Brent-Kung adder [13]). Addition of k *n*-bit integers has a latency of  $\mathcal{O}(\log(k) + \log(n))$ , using a tree of carry-save adders [24], followed by a carry look-ahead adder.

**Integer multiplication:** Multiplication of two *n*-bit integers has a latency of  $\mathcal{O}(\log(n))$  using a tree of carry-save adders (*e.g.* a Wallace tree [57]) followed by a carry look-ahead adder.

**Trial division:** Trial division of an up to n-bit integer x by a hardwired constant c of at most m < n bits can e.g. be performed by checking whether  $x \cdot c^{-1} \mod 2^{n+m}$  has at most n bits if c is odd. Since division by powers of two is essentially free and  $c^{-1} \mod 2^{n+m}$  can be precomputed, trial divisions by such constants have latency  $\mathcal{O}(\log n)$ .

**Modular reduction:** Modular reduction of a 2n-bit value modulo an n-bit value has a latency of  $\mathcal{O}(\log(n))$ . For instance, the Barrett reduction [8] computes the reduction using integer division by a constant, which is computed using an integer multiplication.

The results above imply that modular addition Add, modular multiplication Mul, and modular reduction (this includes trial division) Mod in  $\mathbb{F}_p$  all have a latency of  $\mathcal{O}(\log(\log(p)))$ . For simplicity, we assume that those operations have the same latency, and consider it as one unit of time (for practical purposes, this time unit is estimated to be 0.9 ns in an ASIC implementation, following the Supranational implementation of MinRoot).

Adding up to  $\log_2(p) \approx 256$  values (integers smaller than p or modular values in  $\mathbb{F}_p$ ) also has latency  $\mathcal{O}(\log(\log(p)))$ ; we assume this also corresponds to one unit. Trial division of 256-bit integers by hardwired constants cost essentially the same and we assume unit latency for this.

We also assume that a multiply-and-add operation  $(x \cdot y + z)$  has unit latency, because the addition term can be included in the tree of carry-save adders.

A table lookup in a table with k entries, denoted by  $\mathsf{Table}(k)$ , has a latency  $\mathcal{O}(\log(k))$  when implemented as a combinatorial circuit. For small tables (up to  $\log_2(p) \approx 256$  entries), we treat this as having unit latency. Larger tables must be stored in RAM, and have a larger latency. Assuming a DDR RAM with a latency of 5 ns, we consider that a memory access has a cost of 6 units of time.

When evaluating the number of processors required to implement an algorithm, we consider that one processor corresponds to a circuit of roughly the size of a modular multiplier. Adding up to  $\log_2(p)$  values and table lookups with up to  $\log_2(p)$  values are each assumed to require one processor.

These latency estimations are strongly dependent on the architecture used to implement a circuit, and are therefore somewhat arbitrary. <sup>11</sup> Nonetheless, they are useful to compare algorithms in a concrete setting, when an asymptotic complexity estimate is hard to derive. In particular, we evaluate all our algorithms in the context of a 256-bit prime, to match the parameters of MinRoot, since we have ASIC implementation results available. The implementation from [53] uses algorithms for addition, multiplication, and modular reduction that roughly match these latency assumptions.

<sup>&</sup>lt;sup>11</sup> The Supranational team mentioned in private communication that it should be possible to reduce the latency by a factor of up to 3 at the cost of longer and more expensive circuit scrutiny (e.g. better layout), using smaller technical process, larger lookup tables etc.

#### 1.3 Our results

We study how to compute VDF functions in parallel in order to achieve a lower latency than the described standard implementations. Instead of looking for shortcuts when iterating a large number of rounds, we focus on the round function itself, and the most expensive operation, the root computation. We are able to provide some algorithms that achieve latency gains that clearly break the original security claims, considering our (reasonable) model. Despite breaking the security claims, it is still unclear whether our algorithms can be implemented in practice, as they require a large number of parallel processors. Even if the practicality of our algorithms might be debatable, they clearly show that computing a root  $\sqrt[q]{x}$  in  $\mathbb{F}_p$  via square and multiply is not necessarily sequential. Several previous works [32,11,52,29] assume that there is no parallel algorithm with lower latency than the square and multiply algorithm with latency  $\log_2(p)$ , but our results show that this assumption is wrong.

We explore several ideas to evaluate monomial functions in parallel in Section 2. Our best algorithm is a smoothness-based algorithm in Section 2.2 that uses the same basic ideas as a paper from Adleman and Kompella [2]. We propose various optimizations of this algorithm in Section 3, and prove a close connection to the discrete logarithm problem in Section 4. We demonstrate the impact of our methods on several VDF constructions in Section 5. In Section 6, we consider the related problem of evaluating low-degree functions in parallel. In Section 7 we briefly discuss practical issues to implement our algorithms. Finally, in conclusion we discuss possible tweaks of algebraic VDF functions to improve their security.

Table 1 shows a summary of our results, with concrete number corresponding to the MinRoot setting with a 256-bit prime.

**Table 1.** Summary of our attacks to compute  $\sqrt[a]{x}$ , with concrete speedups for a 256-bit prime (as in MinRoot).

| Algo  | T   | #CPU       | Μ          | speedup | Techniques                                        |

|-------|-----|------------|------------|---------|---------------------------------------------------|

| naive | 256 | 1          | 0          | 1       | Fast exponentiation                               |

| 1     | 8   | $2^{128}$  | $2^{128}$  | 32      | Baby-step, giant-step                             |

| 2     | 6   | $2^{54.5}$ | 0          | 42      | Smoothness                                        |

| 3     | 13  | _          | $2^{59.5}$ | 20      | Smoothness with medium-size factor                |

| 4     | 14  | $2^{40}$   | $2^{59.5}$ | 18      | Smoothness with medium-size factor and pre-filter |

| 5     | 21  | $2^{36}$   | $2^{64}$   | 12      | Smoothness with special shape of $p$              |

| 6     | 54  | $2^{34}$   | $2^{40}$   | 4.7     | Smoothness with rational reconstruction           |

| 7     | 13  | $2^{29}$   | $2^{40}$   | 20      | Smoothness with parallel smoothness test          |

| 8     | 68  | $2^{25}$   | $2^{40}$   | 3.7     | Smoothness with parallel rational reconstruction  |

#### 2 Low-latency Evaluation of Power Functions

We explore in this section how to reduce the latency of root functions using their homomorphism property. We propose algorithms that make use of the fact that monomial functions f over  $\mathbb{F}_p$  have the following properties:

```

- f is easy to precompute on any single input.

```

```

- f(x \cdot y) = f(x) \cdot f(y), \, \forall x, y \in \mathbb{F}_p.

```

In the following, we consider roots  $f(x) = \sqrt[a]{x} = x^{1/e \mod p - 1}$  in  $\mathbb{F}_p$ , where  $\gcd(a, p - 1) = 1$ . We take  $p \approx 2^{256}$  for concrete examples to match the MinRoot parameters.

The root is the most expensive operation in VDF constructions, and has a latency of  $\log_2(p)$  squaring in the standard implementation. We show in this section two basic algorithms for evaluating it with smaller latency. These algorithms will be refined and improved in the next section.

In an actual VDF such as MinRoot, the round function is applied a large number  $(n_{\rm iterations} \approx 2^{40})$  of times. Due to that, we really care about *expected* (over a random choice of input) time/latency. For the probabilistic algorithms in this and the next sections, we therefore aim for a good, but not necessarily overwhelming success probability. See 7.1 for some further discussion.

#### 2.1 A Baby-step Giant-step Approach

We first propose a simple algorithm using precomputation. The MinRoot submission document [29] also described a precomputation attack, but in our case we target the root operation instead of targeting the iterated function MinRoot. Additionally, we use a self-randomization property to make the attack successful for any given input instead of having a multi-target attack. Let  $\alpha, \beta > 0$  be two parameters.

**Precomputation.** We precompute the following values:

- Compute  $\sqrt[a]{i}$  for  $i \leq \alpha \sqrt{p}$ .

- Compute  $r^a, r^{-1}$  for a set of  $\beta \lfloor \sqrt{p} \rfloor$  random values r.

Online phase. Given a challenge x, do the following in parallel with  $\beta\lfloor\sqrt{p}\rfloor$  processors:

- 1. Pick one of the randomly generated r.

- 2. Compute  $y = x \cdot r^a \mod p$ .

- 3. If  $y \leq \alpha \sqrt{p}$ , then return  $\sqrt[a]{y} \cdot r^{-1}$ .

This algorithm is similar to the baby step-giant step algorithm to compute discrete logarithms. Due to the birthday paradox, its probability of success is approximately  $1 - \exp(-\alpha\beta)$ , so one can fix reasonably small values  $\alpha, \beta \in \mathcal{O}(1)$ . The method has a latency of two multiplications and one table lookup. This implies T = 2 + 6 = 8 time units using the assumptions of Section 1.2, using  $\mathcal{O}(\sqrt{p})$  precomputations, and  $\beta\sqrt{p} = \mathcal{O}(\sqrt{p})$  parallel processors, versus the T = 256 of the sequential computation.

For MinRoot, with  $p \approx 2^{256}$ , this requires approximately  $2^{128}$  precomputations and parallel processors. Since MinRoot claims 128 bits of security, this algorithm has a very close complexity to the claim, and shows that it is at best tight.

In practice, each of the  $2^{128}$  processors will use a different r that can be hard-coded in the processor, together with  $r^a$  and  $r^{-1}$ . The algorithm requires a memory of size  $\sqrt{p}$ . However, note that for uniformly random input, only  $\alpha \cdot \beta$  processors are expected to succeed, and only a single one of those needs to access the memory for each root computation.

#### Algorithm 1: Using precomputation to evaluate $\sqrt[a]{x}$

$$T_{\rm general} = 2 {\rm Mul} + {\rm Table}(M)$$

$$T_{\rm MinRoot} = 8 \qquad \# CPU = 2^{128} \qquad M = 2^{128} \qquad {\rm speedup}: 32$$

#### 2.2 An Approach Using Smoothness

We now describe an algorithm based on smoothness, which is similar to a previous work published by Adleman and Kompella in STOC '88 [2]. This algorithm uses smoothness to compute some arithmetic functions with logarithmic depth and a large number of processors. Starting with the randomization step of Section 2.1, the main idea is to assume that the value  $y = x \cdot r^a \mod p$  is B-smooth when lifted to the integers, *i.e.* it only has prime factors smaller than B, for some bound B.

Preliminaries. We use  $\pi(x)$  to denote the prime counting function  $\pi(x) = \#\{p \le x \mid p \text{ is prime}\}$ . According to the prime number theorem [38, Theorem 6.9], we have  $\pi(x) \approx x/\ln(x)$ .

We use the following result by Dickman to estimate the probability of a random n-bit number to be B-smooth:

**Theorem 1 ([38, Theorem 7.2], [21]).** Let  $\psi(x,y)$  be the number of positive integers not exceeding x composed entirely of prime numbers not exceeding y, and let  $\rho(u)$  be [the Dickman function]. Then, for any  $U \ge 0$  we have

$$\psi(x, x^{1/u}) = \rho(u)x + \mathcal{O}\left(\frac{x}{\log(x)}\right)$$

uniformly for  $0 \le u \le U$  and all  $x \ge 2$ .

In particular, the probability that an *n*-bit number is *B*-smooth is approximately  $\rho(n/\log_2(B))$ .

Finally we use the following result, with Q(x) the number of square-free integers not exceeding x:

Theorem 2 ([38, Theorem 2.2]). Far all  $x \ge 1$

$$Q(x) = \frac{6}{\pi^2} x + \mathcal{O}(x^{1/2})$$

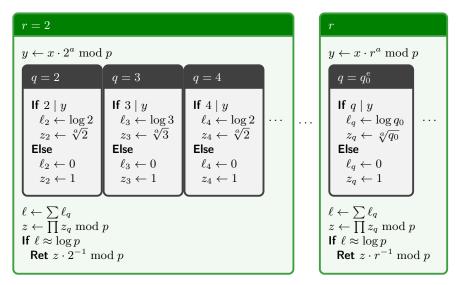

The algorithm works as follows:

#### Precomputation.

- Compute  $\sqrt[a]{q}$  for all small primes  $q \leq B$

- Compute  $r^a, r^{-1}$  for a set of R random values r

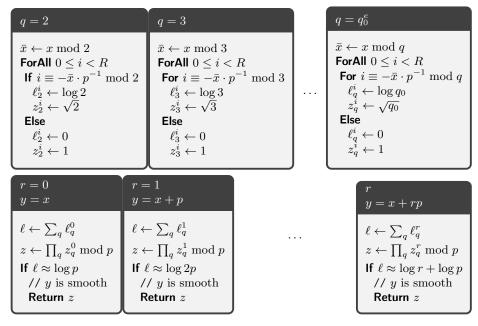

Online phase. Given a challenge x, R groups of processors (each group of size  $\pi(B)$ ) will do the following in parallel (steps 4 and 5 use  $\pi(B)$  processors, and the other steps use a single processor):

- 1. Pick one of the randomly generated r (one value per group)

- 2. Compute  $y = x \cdot r^a \mod p$

- 3. Lift y to the integers

- 4. Perform trial division of y by all primes  $q \leq B$ , in parallel. Denote  $\{q_i\}$  the set of primes that divide y

- 5. Compute  $z = \prod \sqrt[q]{q_i} \cdot r^{-1} \mod p$  (all terms are precomputed)

- 6. If  $z^a = x$  return z

The algorithm succeeds if the value y at step 2 is B-smooth and square free. In this case  $y = \prod q_i$ , hence  $\sqrt[q]{x} = \sqrt[q]{y} \cdot r^{-1} = \prod \sqrt[q]{q_i} \cdot r^{-1}$ . The probability of y being B-smooth and square-free can be approximated as  $\rho(256/\log_2(B)) \times 6/\pi^2$  by heuristically assuming that B-smoothness and being square-free are independent; therefore we choose  $R \gg \pi^2/6\rho(256/\log_2(B))$ , and we obtain a high probability of success, thanks to the randomization done in step 1. Note that the required heuristic can be greatly weakened by the optimization of allowing square factors discussed below and we successfully tested the heuristic for the parameters of interest (cf. the discussion on page 12).

This algorithm is similar to the index calculus one to compute discrete logarithms. Its complexity is sub-exponential. We now discuss some optimizations to make the algorithm closer to usable in practice.

Allowing Square Factors in y. For a prime q with  $q^e \leq B < q^{e+1}$ , we do trial division with  $q, q^2, \dots q^e$ , and each trial adds a copy of q to the set  $\{q_i\}$  if it is successful. With this tweak, the algorithm succeeds as long as y is B-powersmooth, i.e. all prime powers  $q^{\nu}$  dividing y satisfy  $q^{\nu} < B$ . There is no simple formula to evaluate the complexity of this variant, but with the parameters we use, the probability of being B-powersmooth is essentially the same as being B-smooth; therefore we increase the success rate by a factor  $\pi^2/6 \approx 1.64$  (the inverse probability of being square-free) with a very small increase in the number of processors.

Avoiding the Final Test. The purpose of the final test, computing  $z^a$ , is to verify if y is B-smooth. In order to avoid the latency of computing this, we can check if the  $q_i$  factors are enough and we are missing no bigger ones by precomputing an approximation of  $\log(q_i)$  and check if  $\sum \log(q_i) \approx \log(y) \approx \log(p)$  to detect when y is B-smooth. Note that the approximation does not need to be very good: on failure,  $z^a$  differs from y by at least some prime factor that was not found, which is at least 2 (and for square-free y, at least B). We can improve this and rule out missing very small prime factors q by testing divisibility by  $q^{\nu}$  for larger  $\nu$  up to  $q^{\nu} < p$  rather than  $q^{\nu} < B$  for very small q at a very small increase in the number of processors.

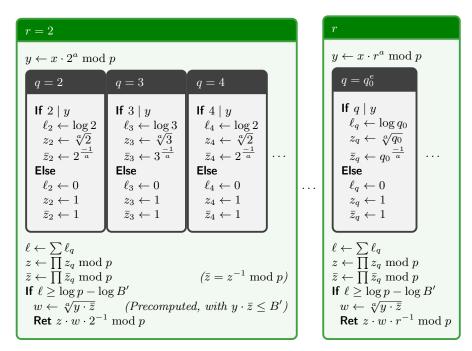

Finally, we obtain the Algorithm of Figure 4, where black boxes represent processors and green boxes represent groups of processors. For simplicity, we assume that a single group of processors will succeed and return a value. The latency is one multiplication, one trial division, and the final multiplication of several terms. We assume that the multiplication circuit can efficiently deal with empty factors and the complexity depends on the number of non-unit terms in the product.

Using precomputed Discrete Logarithms. In case it is not practical to build a multiplication circuit dealing only with the non-empty terms, we propose an alternative approach. Instead of having each processor returning  $z_i = \sqrt[q]{q_i}$ , we precompute the discrete logarithm of  $z_i$  in  $\mathbb{F}_p$  using a generator g. If we denote the logarithm as  $\nu_i$  with  $z_i = g^{\nu_i}$  (and  $\nu_i = 0$  for empty factors) we can replace the product  $z = \prod z_i \mod p$  by a sum  $\nu = \sum \nu_i \mod p - 1$  and an exponentiation  $z = g^{\nu}$ . Using the assumptions of Section 1.2, the sum of  $\pi(B)$  terms has latency only  $\log_2(\pi(B))/8$ . To compute the exponentiation with low latency, we split  $\nu$  into 32 bytes, and use table lookups for each byte followed by a multiplication tree with latency 5.

Concrete Parameters for  $log_2(p) \approx 256$ . Parameters that minimize the total complexity can be chosen as:

$$B = 2^{35}$$

$R = 2^{24}$

With those parameters, there are  $2^{24}$  groups of processors, and each group has roughly  $\pi(2^{35})\approx 2^{30.5}$  processors to do trial division in parallel (a total of  $2^{54.5}$  processors). This succeeds with high probability because the probability that a 256-bit number is  $2^{35}$ -smooth can be approximated as  $\rho(256/35)\approx 2^{-21.6}\gg 1/R$ , and we assume than the probability of being  $2^{35}$ -powersmooth is the same.

To verify this estimate, we performed experiments with Bach's algorithm to generate factored random numbers [7]. Out of  $2^{30}$  random 256-bit numbers, we observed 367  $2^{35}$ -smooth numbers (a fraction of  $2^{-21.5}$ ); all of them are also  $2^{35}$ -powersmooth, and 169 of them are square-free (a fraction of  $2^{-22.6}$ ). This closely matches the theoretical estimation. In order to deal with factors  $q^{\nu} < B$ , we actually need slightly more than  $\pi(B)$  processors but the increase is negligible  $(2^{30.5} + 2^{14.1})$ .

Fig. 4. Algorithm using B-smooth numbers

Assuming that we can neglect the communication time, the latency of this algorithm is one multiplication, one trial division, and about 4 multiplications at the end (assuming there are at most 15 primes in the decomposition of y), for a total latency of 6 units. This algorithm does not use any table lookup, each processor only uses a single hard-coded value for  $\sqrt[a]{q_0}$ ,  $r^a$ , and  $r^{-1}$ .

# Algorithm 2: Using smoothness to evaluate $\sqrt[a]{x}$ $T_{\rm general} = 6 \text{Mul}$ $T_{\rm MinRoot} = 6 \qquad \#CPU = 2^{54.5} \qquad M = 0^a \qquad \text{speedup}: 42$ $\overline{^a \text{We write } M = 0 \text{ because there are no table lookups in this algorithm, but each processor uses a constant amount of memory, resulting in <math>2^{54.5}$ memory cells in total.

Alternatively, parameters can be chosen to minimize the latency:

$$B = 2^{64}$$

$R = 2^{10}$

With those parameters the total number of processors is somewhat higher at  $2^{68.5}$  but we expect fewer factors  $q_i$  so that the final multiplication only has latency 3 (assuming at most 7 primes), and the total latency is 5 units.

## 3 Optimizing the Smoothness Algorithm

In this section we present several ideas that allow us to reduce the number of CPUs needed in the smoothness algorithm. Our aim is to make our algorithm as close to practical as possible, and for doing this we will reduce the speedup provided by the algorithm in the previous section and provide different trade-offs. When combined, we are able to reduce the number of processors required below  $2^{30}$  (with a 256-bit prime). This has allowed us to run experiments on the full algorithm (the code is available as supplementary material  $1^{12}$ ).

#### 3.1 Using Almost-Smooth Numbers

Our first improvement relaxes the constraint of y being B-smooth to allow a single medium-size factor, in addition to an arbitrary number of small ones. Formally, we say that an integer is (B, B')-almost-smooth (with B' > B) if all its prime factors are smaller than B', and at most one factor is larger than B. It will require a large precomputed table to deal with the bigger factor, but this will allow to increase the probability of y verifying the condition for similar values of B, reducing B and the overall number of processors needed.

After doing trial division, we detect that y is almost-smooth by checking the magnitude of the rough part after removing all factors smaller than B. Since we are mostly interested in cases with  $B' < B^2$ , if the rough part is smaller than B' then there is a single prime factor between B and B' (or none if y is B-smooth). We precompute the roots of all prime numbers between B and B' and the processor that finds an almost-smooth y will make a table lookup to recover it.

In practice, we modify the algorithm to compute  $z^{-1}$  in parallel with the computation of z, using precomputed tables of  $q_i^{-1/a} = 1/\sqrt[a]{q_i}$ . We evaluate  $z^{-1}$  as  $\bar{z} \leftarrow \prod q_i^{-1/a} \mod p$ , and we compute the rough part as  $y \cdot \bar{z}$ . The resulting algorithm is shown as Figure 5.

We know no simple analytic way to compute the probability of almostsmoothness, but we could estimate it from experiments.

Concrete Parameters for  $log_2(p) \approx 256$ . Good parameters can be chosen as:

$$B = 2^{32} B' = 2^{65} R = 2^{20}$$

Experimentally, the probability of a 256-bit number to be  $(2^{32}, 2^{65})$ -almost-smooth is about  $2^{-18}$ ; this is a significant increase compared to the probability of begin  $2^{32}$ -smooth  $(\rho(256/32) \approx 2^{-24.9})$ . Therefore with  $R = 2^{20}$  there is a high probability of success.

The latency increases because of the table-lookup. Using our assumptions, this has a latency of 6; we obtain a latency of one multiplication, one trial division, 4 multiplications to compute  $y \cdot \prod \bar{z}_q$ , one table lookup, and one final multiplication.

<sup>12</sup> https://github.com/Cryptosaurus/VDF\_cryptanalysis\_code

This algorithm requires a huge amount of memory, but we stress that the memory is not accessed simultaneously by all processors; for each computation of  $\sqrt[a]{x}$  only a few processors succeed (those that get an almost-smooth y) and only one of them needs to make a memory access.

#### Algorithm 3: Using smoothness to evaluate $\sqrt[a]{x}$ , with a medium-size factor

```

T_{\rm general}=6{\rm Mul}+{\rm Mod}+{\rm Table}(M) T_{\rm MinRoot}=13 \qquad M=2^{59.5} \qquad \#CPU=2^{48} \qquad {\rm speedup}:20

```

Fig. 5. Improved algorithm using (B, B')-almost-smooth numbers

#### 3.2 Pre-filtering

We observe that the randomizing step  $(y \leftarrow x \cdot r^a \mod p)$  uses only one processor per group, so that many processors sit idle during this step. To optimize the algorithm, we can try several values r in each group, and keep the value  $y = x \cdot r^a \mod p$  that seems more promising in each group. For instance, with a

smoothness bound  $B=2^{32}$  as above, each group has  $\pi(B)\approx 2^{27.6}$  processors. We can pick  $2^{27.6}$  random r's in each group and keep the smallest value  $y=x\cdot r^a \mod p$ ; we expect y to be of size  $256-27.6\approx 228$  bits which increases the probability of smoothness.

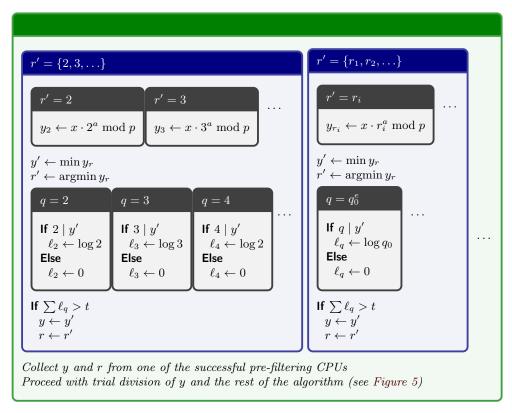

For a more advanced filtering, we do a smoothness test with a smaller bound  $B_0 < B$ , and we keep the candidate y with the largest  $B_0$ -smooth part (or, we keep candidates with a  $B_0$ -smooth part larger than some threshold t). This filtering requires  $\pi(B_0)$  processors, so we can chain it with a first step that keep the smallest y out of  $\pi(B_0)$  candidates. Figure 6 shows this pre-filtering algorithm.

Concrete Parameters for  $log_2(p) \approx 256$ . Parameters can be chosen as:

$$B = 2^{32}$$

$B' = 2^{65}$   $B_0 = 2^{20}$   $t = 2^{76}$   $R = 2^{12}$

Experimentally, the probability of having a  $2^{20}$ -smooth part larger than  $t=2^{76}$  is about  $2^{-9.3}$  for a 256-bit value. With the parameters above, we consider  $\pi(B)/\pi(B_0) \approx 2^{11.3}$  candidates y in each group, therefore with high probability one of them will pass the filter. After filtering those candidates, the probability that they are  $(2^{32}, 2^{65})$ -almost-smooth is about  $2^{-11}$ .

Using the initial filter the size of y is reduced by 10 bits; this increases the probability to roughly  $2^{-9.5}$ .

Algorithm 4: Using smoothness to evaluate  $\sqrt[a]{x}$ , with medium-size factor and pre-filter

$$T_{\rm general} = 7 {\rm Mul} + {\rm Mod} + {\rm Table}(M)$$

$$T_{\rm MinRoot} = 14 \qquad M = 2^{59.5} \qquad \#CPU = 2^{40} \qquad {\rm speedup}: 18$$

#### 3.3 Exploiting the Shape of p

The prime used in MinRoot has a special shape:  $p=2^{32}q+1$ . Therefore, the low 32-bits of a product  $x\cdot y \mod p$  with  $y<2^{32}$  only depend on the lowest and highest 32 bits of x (and y). We use this property to improve our algorithm, by precomputing values r with  $r^a<2^{32}$  that generate a product  $x\cdot r^a$  with zeros in the least significant bits, given the low and high bits of x. This will allow to reduce R for similar parameters.

To take advantage of this, we modify the online algorithm to perform two steps of randomization: first with an arbitrary  $r_0$ , then with the precomputed value  $r_1$ :

**Precomputation.** Initialize table  $\mathcal{T}$ :

- For all

$$x_{\text{low}} < 2^{32}$$

,  $x_{\text{high}} < 2^{32}$ , consider  $x = x_{\text{low}} + 2^{224}x_{\text{high}}$

Fig. 6. Pre-filtering step (only one CPU group shown)

- For all  $y < 2^{32}$ , if  $LSB_{32}(x \cdot y \mod p) = 0$ , set  $\mathcal{T}[x_{low}, x_{high}] \leftarrow \sqrt[q]{y}$  Online phase. Given a challenge x:

- 1. Pick one of the randomly generated  $r_0$

- 2. Compute  $y_0 = x \cdot r_0^a \mod p$

- 3. Recover the precomputed value  $r_1 = \mathcal{T}[LSB_{32}(y_0), MSB_{32}(y_0)]$

- 4. Compute  $y_1 = y_0 \cdot r_1^a \mod p$

This produces a value  $y_1$  that is a multiple of  $2^{32}$ , therefore the effective length for the smoothness test is reduced by 32 bits.

Concrete Parameters for MinRoot. We keep the same smoothness parameters as above, but we reduce the number of groups needed:

$$B = 2^{32}$$

$B' = 2^{65}$   $B_0 = 2^{20}$   $t = 2^{76}$   $R = 2^{8}$

By reducing the size of y by an extra 32 bits, we obtain 214-bit values; after filtering candidates with a  $2^{20}$ -smooth part larger than  $t=2^{76}$ , the probability that they are  $(2^{32}, 2^{65})$ -almost-smooth is about  $2^{-6}$ , corresponding to a gain of 3.5 bits.

# Algorithm 5: Using smoothness to evaluate $\sqrt[a]{x}$ , with medium-size factor, pre-filter, and the special shape of p

$$T_{\rm general} = 8 {\rm Mul} + {\rm Mod} + 2 {\rm Table}(M)^a$$

$$T_{\rm MinRoot} = 21 \qquad M = 2^{64} \qquad \# CPU = 2^{36} \qquad {\rm speedup}: 12$$

However this variant requires a memory access to the table  $\mathcal{T}$  from each processor doing the initial randomization, therefore this is unlikely to be an improvement in practice with a huge table. Trade-offs with a smaller table (controlling fewer bits of y) might be more practical; for instance, we can use tables of size  $2^{32}$  to control 16 bits of y (each processor could hold a copy of table). We obtain 230-bit values, and the probability that they are  $(2^{32}, 2^{65})$ -almost-smooth after filtering is about  $2^{-7.6}$ .

In the end, this technique produces small improvements, and cannot be used together with the techniques proposed in the following sections.

#### 3.4 Rational Reconstruction

Rational reconstruction takes an element x in  $\mathbb{F}_p$  and writes it as a fraction:  $x = \alpha/\beta$  with  $\alpha, \beta \in \mathbb{F}_p$ . Wang proposed an algorithm that finds a solution with  $\alpha \approx \beta \approx \sqrt{p}$ , based on the extended Euclidean algorithm [58]. Indeed, running the extended Euclidean algorithm on x and p generates a series of relations  $u_i \times x + v_i \times p = w_i$ . Each relation defines a rational reconstruction:  $x \equiv w_i/u_i \mod p$ . During the extended Euclidean algorithm, the magnitude of  $(u_i)$  and  $(v_i)$  are increasing while  $(w_i)$  is decreasing; if we stop after half the number of iterations we obtain  $u_i \approx w_i \approx \sqrt{p}$ .

The online algorithm can be improved as follows using rational reconstruction:

- 1. Pick one of the randomly generated r

- 2. Compute  $y = x \cdot r^a \mod p$

- 3. Reconstruct a fraction  $y = \alpha/\beta$

- 4. Lift  $\alpha$  and  $\beta$  to the integers

- 5. Do trial division of  $\alpha$  and  $\beta$

If  $\alpha$  and  $\beta$  are both smooth, we easily deduce  $\sqrt[a]{x}$  from precomputed tables:

$$\sqrt[a]{x} = \prod \sqrt[a]{q_j'} \cdot \prod q_i^{\frac{-1}{a}} \cdot r^{-1} \quad \text{if } \beta = \prod q_i \text{ and } \alpha = \prod q_j'$$

Since  $\alpha$  and  $\beta$  are of the order of  $\sqrt{p}$ , they are significantly more likely to be smooth and we can use a smaller bound B. The smoothness test for  $\alpha$  and  $\beta$  is done in parallel, using  $2 \times \pi(B)$  processors.

$<sup>^{</sup>a}$  This algorithm also requires a precomputation of  $2^{96}$  roots

Latency of Rational Reconstruction. In practice, variants of the binary GCD algorithm (such as the plus-minus algorithm of Brent and Kung [14]) should have a lower latency than the Euclidean algorithm because they only use addition and subtractions. Extended versions of the binary GCD algorithm produce relations of the form  $u_i \times x + v_i \times p = w_i \times 2^{z_i}$ , that can also be used in our case.

A recent work [51] studies low-latency implementation of extended GCD algorithms. They describe an ASIC built on 16nm that performs extended GCD of 256-bit integers with latency 89 ns in constant time. For rational reconstruction, only half the rounds are necessary. Moreover, the constant-time circuit uses more rounds than required on average to maintain a constant time, and the circuit uses 16 nm technology while the Supranational implementation of MinRoot uses 12 nm technology. Therefore, we estimate that the regular extended GCD algorithm for n-bit numbers has latency  $\mathsf{EGCD}(n) = \frac{5}{16}n$ , and thus rational reconstruction would have a latency of roughly 40 time units.

To reduce the latency further, some GCD algorithms use precomputed tables to reduce the number of iterations, such as the right-shift k-ary algorithm of Sorenson [50], with only  $\mathcal{O}(\log(n)/k)$  iterations using tables of size k. Further work would be needed to evaluate the latency of such algorithms when a massive number of processors and precomputation is available.

Concrete Parameters for  $log_2(p) \approx 256$ . We combine rational reconstruction with the pre-filtering step: we consider many fractions  $\alpha/\beta$ , and we only keep fractions where  $\alpha$  and  $\beta$  both have a large  $B_0$ -smooth factor. Parameters can be chosen as:

$$B = 2^{24}$$

$B' = 2^{45}$   $B_0 = 2^{16}$   $t = 2^{28}$   $R = 2^{13}$

Experimentally, the probability of having a  $2^{16}$ -smooth part larger than  $t=2^{28}$  is about  $2^{-2.9}$  ( $2^{-5.8}$  for a pair  $(\alpha, \beta)$ ). With the parameters above, we consider  $\pi(B)/\pi(B_0) \approx 2^{7.4}$  candidates  $y = \alpha/\beta$  in each group, therefore with high probability one pair  $(\alpha, \beta)$  will pass the filter. After filtering those candidates, the probability that they are  $(2^{24}, 2^{45})$ -almost-smooth is about  $2^{-5.5}$  ( $2^{-11}$  for a pair  $(\alpha, \beta)$ ).

# Algorithm 6: Using smoothness to evaluate $\sqrt[a]{x}$ , with medium-size factor, pre-filter, and rational reconstruction

$$T_{\rm general} = 0.5 {\rm EGCD}(p) + {\rm Table}(M) + 7 {\rm Mul} + {\rm Mod}$$

$$T_{\rm MinRoot} = 54 \qquad M = 2^{40} \qquad \# CPU = 2^{34} \qquad {\rm speedup}: 4.7$$

#### 3.5 Parallel Smoothness Test

We propose here another idea that can be used to reduce the latency, at the expense of more communication. Instead of randomizing with  $y \leftarrow x \cdot r^a \mod p$

for random r until the value y is smooth when lifted to the integers, we can compute  $y \leftarrow x + r \cdot p$  over the integers, for small  $r \in \{0, 1, \dots R\}$ . We obtain slightly larger integers, but again if one of them is smooth we can compute  $\sqrt[q]{y} \mod p$  and deduce  $\sqrt[q]{x} \mod p = \sqrt[q]{y} \mod p$ .

The advantage of this approach is that we can test all candidates y for smoothness simultaneously. Indeed, we don't have to do trial division for all  $x+r\cdot p$  and all small prime powers  $q_i$ . We just have to compute  $x \bmod q_i$ , and we directly know the values of r for which  $x+r\cdot p$  is divisible by  $q_i$ : those with  $r \equiv -x\cdot p^{-1} \bmod q_i$ . Since p is prime, it is always invertible mod  $q_i$  and  $p^{-1} \bmod q_i$  can be precomputed. Figure 7 shows this algorithm.

In a model with free communication (e.g. with a parallel RAM that can be accessed simultaneously by each processor), this should be quite efficient: each processor doing trial division just has to send a list of candidates r such that  $x + r \cdot p$  is divisible by  $q_i$ , and one processor per candidate r will merge the data (with a parallel RAM: each processor writes the factor found in a region dedicated to a given candidate r).

The main factor for the complexity of this algorithm is the number of messages to send; on average it is equal to  $\sum_{q^{\nu} < B} \frac{R}{q^{\nu}}$ . In order to minimize latency, we use multiple processors for small factors  $q_i$ , so that each processor has a single message to send; therefore, the number of processor is  $\sum_{q^{\nu} < B} \lceil \frac{R}{q^{\nu}} \rceil$ . When taking communication into account, there will be some cost to pay to

When taking communication into account, there will be some cost to pay to route the messages. Using a hypercube topology (each processor is connected to  $\log(n)$  other processors), n processors can route n messages in probabilistic time  $\mathcal{O}(\log(n))$  [56].

Concrete Parameters for  $log_2(p) \approx 256$ . This idea can be combined with the use of almost-smoothness, but not with pre-filtering because we consider many values of y simultaneously. We consider the following parameters:

$$B = 2^{32}$$

$B' = 2^{45}$   $R = 2^{26}$

With those parameters, the number of processors for trial division is  $\sum_{q^{\nu} < B} \left\lceil \frac{R}{q^{\nu}} \right\rceil = 2^{28.8}$ , and the average number of messages to route is  $\sum_{q^{\nu} < B} \frac{R}{q^{\nu}} = 2^{28}$  (slightly higher than  $\pi(B) \approx 2^{27.6}$ ). Each candidate y is a 256 + 26 = 282-bit number. The probability that they are  $(2^{32}, 2^{45})$ -almost-smooth is about  $2^{-24}$ , so that the algorithm succeeds with high probability.

# Algorithm 7: Using smoothness to evaluate $\sqrt[q]{x}$ , with medium-size factor, and parallel smoothness test

$$T_{\rm general} = {\sf Table}(M) + 6{\sf Mul} + {\sf Mod}$$

$$T_{\sf MinRoot} = 13 \qquad M = 2^{40} \qquad \#CPU = 2^{29} \qquad \text{speedup}: 20$$

**Fig. 7.** Parallel smoothness test. We use a for "**ForAll** i" loop in the algorithmic description, but a real implementation will directly iterate over values of i such that  $i \equiv -\bar{x} \cdot p^{-1} \mod q$ .

#### 3.6 Parallel Smoothness Test and Rational Reconstruction

Finally, we combine the ideas of rational reconstruction and the parallel smoothness test. First, we use rational reconstruction on x, to obtain two different fractions  $x = \alpha/\beta \mod p = \gamma/\delta \mod p$ . Using intermediate values from the extended Euclidean algorithm, we just keep two consecutive steps, and we expect  $\alpha$ ,  $\beta$ ,  $\gamma$ , and  $\delta$  to be slightly larger than  $\sqrt{p}$ . We observe that for any r we have (assuming  $\beta + \delta \cdot r \not\equiv 0 \mod p$ ):

$$\frac{\alpha + \gamma \cdot r}{\beta + \delta \cdot r} \equiv \frac{\beta \cdot x + \delta \cdot x \cdot r}{\beta + \delta \cdot r} \bmod p \equiv x \bmod p$$

Therefore, we consider a series of fractions  $\frac{\alpha+\gamma\cdot r}{\beta+\delta\cdot r}$  for small  $r\in\{0,1,\ldots R\}$  and deduce  $\sqrt[\alpha]{x}$  when  $\alpha+\gamma\cdot r$  and  $\beta+\delta\cdot r$  (integers of magnitude roughly  $R\cdot\sqrt{p}$ ) are simultaneously smooth. As in the previous section, we obtain the divisibility information on all candidates  $(\alpha+\gamma\cdot r)$  or  $\beta+\delta\cdot r$ ) with a single modular reduction.

Concretely, when doing trial division of  $\alpha + \gamma \cdot r$  by  $q_i$ , we have  $\alpha + \gamma \cdot r \equiv 0 \mod q_i \iff r \equiv -\alpha \cdot \gamma^{-1} \mod q_i$ . Therefore each processor must compute  $\alpha \mod q_i$  and  $\gamma^{-1} \mod q_i$ ; this differs from Section 3.5 where  $p^{-1} \mod q_i$  was precomputed. We note that  $\gamma$  is not necessarily invertible in  $\mathbb{Z}_{q_i}$ , but having a non-invertible value is relatively rare and we neglect it to simplify the analysis (this only introduces some false negatives).

There are several possibilities to compute  $\gamma^{-1} \mod q_i$ : we can precompute a table of inverses in  $\mathbb{Z}_{q_i}$ , or can compute it on the fly using either the extended Euclidean algorithm or as  $\gamma^{\varphi(q_i)-1} \mod q_i$  using Euler theorem. Using the assumptions of Section 1.2, the fastest approach is a precomputed table, with latency 6 units, but it requires a large amount of memory.

Concrete Parameters for  $log_2(p) \approx 256$ . We consider the following parameters:

$$B = 2^{27} B' = 2^{45} R = 2^{21}$$

With those parameters, the number of processors for trial division is  $\sum_{q^{\nu} < B} \lceil \frac{R}{q^{\nu}} \rceil = 2^{23.9}$  ( $2^{24.9}$  to do trial division of  $\alpha + \gamma \cdot r$  and  $\beta + \delta \cdot r$  in parallel), and the average number of messages to route is  $\sum_{q^{\nu} < B} \frac{R}{q^{\nu}} = 2^{23}$  ( $2^{24}$  when considering both the numerator and denominator). Each candidate y is a 128 + 21 = 149-bit number. The probability that they are ( $2^{27}, 2^{45}$ )-almost-smooth is about  $2^{-9.2}$ , so that the algorithm succeeds with high probability after  $2^{21}$  attempts.

We assume that  $\gamma^{-1} \mod q_i$  is computed on the fly (using precomputed tables would require a memory of size  $2^{48.8}$ ). Following the latency estimate for the extended GCD algorithm in Section 3.4, we assume that computing inverses in  $\mathbb{Z}_{q_i}$  has latency  $\frac{5}{16} \log_2(q_i)$ , which we round up to  $\log_2(q_i)/2 \approx 14$  units.

Algorithm 8: Using smoothness to evaluate  $\sqrt[a]{x}$ , with medium-size factor, rational reconstruction, and parallel smoothness test

$$\begin{split} T_{\rm general} &= 0.5 {\sf EGCD}(p) + {\sf EGCD}(B) + {\sf Table}(M) + 7 {\sf Mul} + {\sf Mod} \\ T_{\sf MinRoot} &= 68 \qquad M = 2^{40} \qquad \# CPU = 2^{25} \qquad \text{speedup}: 3.7 \end{split}$$

We have implemented (a serialized version of) this algorithm in practice with those parameters, and it succeeds with probability more than 99% (2 failures out of 1000 trials). When working with a 128-bit prime p (as in Veedo), the attack requires only  $2^{13}$  processors and  $2^{40}$  memory (with  $B=2^{14}$ ,  $B'=2^{45}$ ,  $R=2^9$ ), which might be implementable in practice (as a reference, the largest GPUs today have more than  $2^{14}$  cores and some motherboards support 12TB of memory). The code is available as supplementary material  $1^{12}$ .

#### 4 Relation with Discrete Logarithm

We observe that the algorithms in Sections 2 and 3 are very close to classical algorithms for the discrete logarithm problem: Section 2.1 is similar to the baby-step giant-step algorithm [47], and Section 2.2 is similar to index calculus [1]. In Appendix A.1 we describe another algorithm similar to the Pohlig-Hellman algorithm [40].

#### 4.1 Advanced logarithm methods

It is natural to consider more advanced discrete logarithm algorithms in the context of low-latency computation of roots.

Using ECM. The elliptic curve method [34] (ECM) is a factorization algorithm that is particularly efficient to find small factors. It could be used instead of trial division for smoothness tests in the index calculus type attacks. The idea would be to precompute some curves so that the value you want has smooth order. But it is unclear how to make this work, or whether the amount of computation for doing ECM would end up being within the desired constraints.

Using NFS-type algorithms. The complexity of index calculus for the discrete logarithm problem is in the class L[1/2]. There are more efficient algorithms known, with complexity in the class L[1/3], such as the Number Field Sieve [26]. Unfortunately, these algorithms seem to have an intrinsically sequential structure. Further work is needed to evaluate the potential of these ideas, but the apparent sequentiality is a serious obstacle in the context of low-latency algorithms.

#### 4.2 Reduction to parallel discrete logarithm

On another hand, we show that a large class of attacks on algebraic VDFs, which includes all our attacks, is reducible to the parallel discrete logarithm computation. Informally, an attack that computes roots by precomputation and low-latency multiplications may be used to compute the discrete log.

**Definition 1.** We call an algorithm  $\mathcal{A}$  algebraic w.r.t. precomputed memory  $\mathsf{C} = [c_1, c_2, \dots, c_k]$  if on input x it outputs a result in the form

$$\mathcal{A}(x;\mathsf{C}) \to (y,d_1,d_2,\ldots,d_k,d') \tag{1}$$

such that

$$y = c_1^{d_1} c_2^{d_2} \cdots c_k^{d_k} x^{d'} \tag{2}$$

It is easy to see that all algorithms from Section 3 are algebraic: the result is always a product of some powers of stored values, which in our case are numbers with known roots.

**Theorem 3.** Let p be a prime, and let DL be an algorithm that computes the discrete logarithm in  $\mathbb{F}_p$  with computational cost  $T_{DL}(p)$ . Let A be a parallel algebraic algorithm that computes the power function

$$f(x) = x^d \bmod p$$

using D processors and memory in online time (latency) L and precomputation time T and produces a result in the form (2), where d-d' is coprime with p-1. Then there exists a parallel algorithm B that computes the discrete logarithm in  $\mathbb{F}_p$  (using base g) in time  $L' = L + \log_2 k$  using D processors and memory and precomputation time  $T + D \cdot T_{DL}(p)$ .

*Proof.* We construct such an algorithm as follows. For each precomputed memory element we precompute its discrete logarithm in time  $T_{DL}(p)$  spending the total of at most  $D \cdot T_{DL}(p)$  precomputation and store it together with the value  $c_i$ .

In the online phase we run A as a subroutine for x and obtain

$$x^d = c_1^{d_1} c_2^{d_2} \cdots c_k^{d_k} x^{d'}$$

Given  $\{c_i, d_i\}, d'$  we retrieve the log of each  $c_i$  from the memory and compute

$$\log_g x = \frac{\sum d_i \log_g c_i}{d - d'}$$

in time  $\log_2 k$  using k processors. This ends the proof.

Therefore, any algebraic attack implies a parallel discrete logarithm computation with the same online latency and the same online computational complexity. Given that the latter problem has received some public scrutiny [49,18,48] (and impacts the real-world security of Diffie-Hellman [3]), we may guess that a further progress in low-latency attacks on algebraic VDFs, in particular the reduction in the CPU number D, would require a non-algebraic approach.

## 5 Application to VDF Constructions

The previous algorithms break the sequentiality of several VDF constructions, such as MinRoot [29], VeeDo [52] and Sloth++ [11]. An attacker with a large number of processors can compute the round function several times faster than a legitimate user, if we neglect communication and memory cost.

In particular, it contradicts the security claims of MinRoot: for instance, using the algorithm of Section 3.5, an attacker with  $2^{29}$  processors can compute the round function about 20 times faster than a legitimate user.

#### 5.1 Optimization for Iterated MinRoot

We can save the latency of the initial multiplication used by  $r'^a$  in the next round if the processor that succeeds broadcasts the factors to be multiplied ( $\{\sqrt[a]{q_i}\}$  and  $r^{-1}$ ) rather than the final reduced result. Then each processor would compute the randomized input for the next round as:

$$\begin{split} (u'+v') \cdot {r'}^a &= (\sqrt[a]{u+v} + (u+i)) \cdot {r'}^a \\ &= \prod \sqrt[a]{q}_i \cdot {r}^{-1} \cdot {r'}^a + (u+i) \cdot {r'}^a \end{split}$$

This results in a product with one more term, but it does not affect the latency if the number of terms was not a power of two. The term  $(u+i) \cdot r'^a$  is added using a multiply-and-add operation at the end, so that the latency of a MinRoot round is still just the latency of the a-th root.

#### 5.2 Application to Sloth++

Sloth++ uses square roots in  $\mathbb{F}_{p^2}$ . The precomputation attack from Section 2.1 can be applied directly, but attacks from Section 2.2 and 3 rely on smoothness and there is no direct way to apply it in  $\mathbb{F}_{p^2}$ . Instead, we show how to reduce the computation of square roots in  $\mathbb{F}_{p^2}$  to square roots in  $\mathbb{F}_p$ .

We assume that  $\mathbb{F}_{p^2}$  is constructed as  $\mathbb{F}_p[X]/(X^2+\alpha)$ . An element b of  $\mathbb{F}_{p^2}$  is a polynomial  $b_0+b_1X$ . The square root  $z=z_0+z_1X$  of  $b=b_0+b_1X$  satisfies:

$$z^{2} = b$$

$$(z_{0} + z_{1}X)^{2} = b_{0} + b_{1}X$$

$$z_{0}^{2} - \alpha z_{1}^{2} + 2z_{0}z_{1}X = b_{0} + b_{1}X$$

$$\begin{cases} 2z_{0}z_{1} &= b_{1} \\ z_{0}^{2} - \alpha z_{1}^{2} &= b_{0} \end{cases}$$

$$\begin{cases} z_{0} &= b_{1}/2z_{1} \quad (\text{assuming } z_{1} \neq 0) \\ \frac{a_{1}^{2}}{4z_{1}^{2}} - \alpha z_{1}^{2} &= b_{0} \end{cases}$$

We denote  $u = z_1^2$  and we obtain a quadratic equation in u:

$$\frac{b_1^2}{4u} - \alpha u = b_0 \qquad \qquad \frac{b_1^2}{4} - \alpha u^2 = b_0 \cdot u$$

We solve this equation by computing a square root in  $\mathbb{F}_p$ , and deduce  $z_0$  and  $z_1$  using another square root operation in  $\mathbb{F}_p$ , an inverse and a few multiplications. The inverse in  $\mathbb{F}_p$  can be computed with the low latency algorithms of Sections 2 and 3.

#### 5.3 Bigger moduli

It is natural to ask how our attacks scale with modulus size. Given the relation with discrete logarithm computation (Section 4), we expect that the number of CPUs needed for the attack becomes less feasible with moduli of 1024 bits and higher, as it happens with the RSA/DSA security. As different applications may be okay with the number of CPUs above a certain threshold, we provide attack complexity estimates for moduli sizes up to 2048 bits in Table 2.

Due to the space limit, we do not list the latency numbers and speedups in the table. However we note that the speedup in our model actually grows as the modulus increases. This is due to the fact that the plain root computation grows linearly with the modulus size, whereas, for example, the memory access cost is sublinear in it as long as the memory itself grows slower than prime p.

#### 6 Low-latency Evaluation of Low-degree Exponentiation

We now consider a different problem: how to compute  $x^d$  with a *small* d in parallel faster than with the standard square and multiply. This can be directly

**Table 2.** Scalability of smoothness-based attacks. The numbers are given in  $\log_2$  and assume an attack with success rate  $1 - \exp(-1)$  (lower than the rates in Section 3). The code to compute these numbers is available at https://github.com/Cryptosaurus/VDF/tree/master/code/alt\_code.

|                | Algorithm |          |      |          |      |          |      |

|----------------|-----------|----------|------|----------|------|----------|------|

|                | Sec. 2.2  | Sec. 3.1 |      | Sec. 3.5 |      | Sec. 3.6 |      |

| Modulus (bits) | #CPU      | M        | #CPU | M        | #CPU | M        | #CPU |

| 96             | 27        | 34       | 22   | 29       | 13   | 27       | 11   |

| 128            | 33        | 36       | 28   | 30       | 17   | 29       | 14   |

| 192            | 43        | 41       | 38   | 40       | 22   | 34       | 19   |

| 256            | 51        | 51       | 47   | 41       | 27   | 40       | 23   |

| 384            | 67        | 57       | 62   | 49       | 34   | 44       | 30   |

| 512            | 80        | 63       | 75   | 59       | 41   | 53       | 36   |

| 768            | 102       | 78       | 98   | 65       | 53   | 62       | 47   |

| 1024           | 121       | 92       | 117  | 74       | 62   | 69       | 57   |

| 1536           | 154       | 108      | 150  | 91       | 79   | 87       | 72   |

| 2048           | 184       | 105      | 180  | 108      | 94   | 102      | 85   |

applied if the round function uses  $x^e$  with small e rather than  $\sqrt[q]{x}$  with small a. Moreover, those techniques can be used to reduce the latency of the root computation in a VDF: an algorithm to compute  $x^d$  with latency smaller than  $\log_2(d)$  squarings can speed up computing  $x^e$  with arbitrary e by replacing the square and multiply algorithm by a d-th power and multiply algorithm; if done naively, each step now requires up to d-1 multiplications, but those can be parallelized and do not affect the latency much.

#### 6.1 Algorithm Using Shares and LUTs

Let us consider that we split each field element into a sum of s shares from a smaller domain, say, s=2. We then have that  $x \in \mathbb{F}_p$  is equal to  $x=\ell+h$ , where for instance  $\ell$  corresponds to the lowest bits and h to the highest bits of x. The overall idea consists in precomputing some monomials in order to speed up the computation of the VDF primitive we consider.

In general, we have that (with operations in  $\mathbb{F}_p$ )

$$(\ell+h)^d = \sum_{i=0}^d \binom{d}{i} \ell^i h^{d-i}$$

Suppose that an adversary has precomputed  $\binom{d}{i}\ell^i$  and  $k^i$  for all values of i, and for all possible  $\ell$  and k (recall that  $\ell$  and k live in spaces that are much smaller than  $\mathbb{F}_p$ ). Assume also that they have access to several parallel processors, then it is possible to compute  $(\ell+h)^d$  with a latency of 1 lookup, 1 multiplication, and whatever is needed for additions and reduction mod p. After optimizing away 2 trivial tables for i=0 and i=d, overall, 2d processors are needed for this to work (to access 2d LUTs in parallel).

If  $d \leq 4$  such a technique turns out not to be too interesting. However, as the degree d increases, this technique becomes more interesting since the latency does not change when d increases, only the number of processors needed (and the number of tables). Overall, in order to evaluate  $(h + \ell)^d$ , we need:

- -2d parallel processors,

- -2d tables of size roughly  $p^{1/2}$ ,

- a latency of 1 lookup, 1 multiplication, and many additions.

This can be generalized to a higher number s of shares, in which case the numbers above become (without optimizing away some trivial tables)

- $-s\binom{d+s-1}{d} = s\binom{d+s-1}{s-1}$  parallel processors,

- tables of size roughly  $p^{1/s}$ ,

- a latency of 1 lookup,  $\log_2(s)$  multiplications (since we don't have to do them sequentially), and many additions.

Again, while the overall complexity (and in particular the latency) increases with s, the latency does not depend on d. Thus, this technique can be become interesting when the degree is higher, in particular if d is much bigger than s.

Concrete Parameters for  $\log_2(p) \approx 256$ . For instance, with  $d=2^{16}$  and s=4, we obtain a circuit to evaluate  $x^{2^{16}}$  using  $4 \times 2^{46} = 2^{48}$  parallel processors, each using a table of size  $2^{64}$ , with a latency of 1 lookup, 2 multiplications and a modular sum of  $2^{46}$  terms. Using the assumptions in Section 1.2, the tables would be stored in RAM with an access latency of 6 units, and the sum of  $2^{46}$  terms has a latency of 6 (using a tree with 6 levels where each level adds 256 terms). This corresponds to a latency of 6+2+6=14, which is smaller than a direct evaluation with latency 16.

However the memory requirements of this algorithm are prohibitive, with  $sd = 2^{18}$  tables of size  $2^{64}$ , and a total of  $2^{48}$  accesses to the tables.

## Algorithm 9: Using shares and LUTs to evaluate $x^{2^{16}}$

$$T = 14$$

# $CPU = 2^{48}$   $M = 2^{82}$  speedup:  $16/14$

#### 6.2 Extensions

The above method can be applied to directly compute r consecutive applications of a VDF round function. Furthermore, we observe the bottleneck is the large tables of size  $\sqrt[s]{p}$  for maps of the form  $x\mapsto C\cdot x^i$  each. However, the functions computed by those tables are amenable to the very same technique and we can use the technique recursively with l layers by splitting the shares into sub-shares. We refer to Appendix A.3 for more details. The results are given in Table 3.

**Table 3.** Comparison of highly parallel low latency computation with standard VDF (only counting the multiplications in the latency).

| Metric                          | Compressed                             | Recursive with $l$ layers                 | Standard VDF                      |

|---------------------------------|----------------------------------------|-------------------------------------------|-----------------------------------|

| Tables (in bits)                | $e^r 2^{\frac{\log_2 p}{s}} \log_2 p$  |                                           | 0                                 |

| Processors                      | $\binom{e^r+s-1}{s-1}\frac{e^{2r}}{2}$ | $\binom{e^r+s-1}{s-1}^l \frac{e^{2r}}{2}$ | 1 or 2                            |

| Latency (in $\log_2 p$ bit MUL) |                                        | $2 + l\lceil \log_2(s) \rceil$            | $\lceil \log_2(e) \rceil \cdot r$ |

#### 7 Practical Issues

The previous sections mostly consider ideal implementations of VDF from an algorithmic point of view. In this section we briefly discuss some practical issues, such as the communication cost.

#### 7.1 Dealing with Errors

The algorithms given in this paper are probabilistic. Since we consider only the round function  $\sqrt[a]{x}$ , and VDFs use a large number of iterations (typically  $2^{40}$  for MinRoot), we need a very high success rate in order to successfully compute the full VDF function.

However, it is easy to deal with rare erroneous computations, because the computations can be efficiently checked (if  $y = \sqrt[a]{x}$  then  $y^a = x$ ). One option is to repeat the algorithm when it fails; this increases the latency but if the failure rate is small, the average latency stays small. Another option is to run the standard implementation in parallel to the attack. If the attack succeeds we have the result with low latency, and if it fails we wait until the standard algorithm succeeds. If the failure rate is small, the average latency is still small.

#### 7.2 Communication Cost

The analysis above essentially neglects communication costs. In practice, this is likely to be an important bottleneck, because communication between millions of CPUs takes time, and requires a large communication network; this is likely to dominate the cost of the machine [60]. The setting is quite different from usual cryptanalytic attacks, often embarrassingly parallel and not requiring communication between the processors (e.g. brute-force key search). Since our attacks target the round function, all cores must synchronize at least after each round, to collect the result from the core that succeeded and broadcast it to other cores (some algorithms might require even more communication). In this section, we briefly discuss how to implement those communications, and how practical this might be.

Massive Communication Network. In many of the discussed settings with high available parallelism it is necessary to broadcast a short input (e.q. 256 bits) with

very low latency to a large set of processors and later to collect short outputs from a small random subset of "successful" processors.

With more than  $2^{20}$  processors, this would probably require too long wires for such broadcast and retrieval. Alternatives could be broadcasting wirelessly or even over the optical domain. Indeed the speed of optics might make it possible to flash with low latency the common input to the field of processors and later, with a few receiving detectors to retrieve outputs from a handful of lucky processors. There is ongoing research on integrating optical elements into existing chip design [6], and the hypothetical Twinkle factoring device by Shamir also used in optics for finding B-smooth numbers [45].

#### 7.3 Physical Constraints

Speed of light. We want the attack to be faster than the standard implementation. Taking the Supranational implementation of MinRoot as a benchmark, the attack must have a latency of at most 230 ns; during this time light can only travel 70 meters; if we aim for an attack twice as fast as the standard implementation, light can only travel 35 meters. This limits the physical size of the machine that runs the attacks: it should be within a sphere of diameter 35 meters. Assuming that each processor has a volume of  $0.025\,\mathrm{mm}^2$ , at most  $\frac{\pi}{6}35\,\mathrm{m}^3/0.025\,\mathrm{mm}^2\approx 2^{50}$  processors can communicate within one round.

Cooling limit. Assuming each core consumes 1 W of power, the limit above would result in a power density of  $50 \frac{GW}{m^3}$ , far exceeding the power density of a nuclear reactor.

The largest nuclear reactor in the world is the Taishan EPR, rated at  $1.66\,\mathrm{GW}$ , and  $4.59\,\mathrm{GW}$  of thermal capacity. This is a major constraint on building nuclear power plants leading us to claim that it is near impossible to build a system dissipating more than  $100\,\mathrm{GW}$  of thermal power in one location on land. Adding an "engineering safety factor of 10" gives a limit of  $1\,\mathrm{TW}$ , leading to a limit of about  $2^{40}$  cores in a single machine.

Practical engineering constraints. Practical engineering constraints are very likely to lead to much lower limits than any of the above. It completely ignores power supply, cooling, and space for interconnect for communications, which will far exceed the size of the cores. However, the point of designing for "128 bit security" is to account for future improvements by adding safety margins, and so it is unclear how much practical engineering problems should influence this if they can't be translated into clear physical limits.

#### 8 Conclusion

In this paper we propose several algorithms to compute roots in a finite field  $\mathbb{F}_p$  with low latency. Even though it is not clear how efficient those algorithms would be if implemented in practice, they clearly show that computing roots is not a

sequential operation, breaking an assumption used in several VDF constructions. In particular, MinRoot is a VDF candidate that was proposed as a randomness beacon in the core layer of the Proof-of-Stake Ethereum protocol, but this project has been put on hold following our results [28].

Possible Tweaks. In order to limit the impact of these results, we considered some options to construct a VDF that would plausibly not be affected by the attacks. We have not looked into these alternatives in detail, and we do not claim that they are secure, but they could offer ideas for further analysis.

Using a low degree round function. Our strongest attacks (in Sections 2 and 3) compute  $\sqrt[a]{x}$  with low latency. This breaks the VDF property because the standard implementation requires about  $\log_2(p)$  squarings to compute the root. An option could be to use  $x^e$  with small e in the round function instead of  $\sqrt[a]{x}$ : this reduces the latency of the standard implementation and the algorithms of Section 2 are no longer competitive.

However, the algorithms of Section 6 show that a low-degree round function can also be sped up to a smaller extend using parallel computation.

Using a larger prime p. All the algorithms that we proposed have a complexity (number of processors) that is at best sub-exponential in p: the number of processors required to obtain a given advantage increases with p. If p is chosen large enough, it might be possible to achieve a sufficient security level. However, further work is required to gain confidence on the non-existence of better attacks, because the field has been barely explored.