# High performance fully vertical GaN on Silicon PIN diodes for next generation power devices

Youssef Hamdaoui, Sondre Michler, Katir Ziouche, Christophe Detavernier, F

Medjdoub

## ► To cite this version:

Youssef Hamdaoui, Sondre Michler, Katir Ziouche, Christophe Detavernier, F Medjdoub. High performance fully vertical GaN on Silicon PIN diodes for next generation power devices. 15th Topical Workshop on Heterostructure Microelectronics, Aug 2024, Sendai, Japan. hal-04762081

# HAL Id: hal-04762081 https://hal.science/hal-04762081v1

Submitted on 6 Nov 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### High performance fully vertical GaN on Silicon PIN diodes for next generation power devices

Youssef Hamdaoui<sup>1</sup>, Sondre Michler<sup>2</sup>, Katir Ziouche<sup>1</sup>, Christophe Detavernier<sup>3</sup> and Farid Medjdoub<sup>1</sup>

<sup>1</sup>Institute of Electronics, Microelectronics and Nanotechnology, CNRS-IEMN, Lille, France

<sup>2</sup>Department Innovation Management Siltronic AG, München, Germany

<sup>3</sup>Ghent University, Ghent, Belgium.

\*e-mail: youssef.hamdaoui@iemn.fr;

The existing Silicon- and Silicon carbide-based devices do not fulfill all the needs for next generation power generation due to physical limits and high cost of fabrication, respectively. On the other hand, Gallium nitride grown on silicon substrate offers superior physical properties and low fabrication cost. However, despite outstanding lateral GaN-on-Silicon HEMT (high electron mobility transistors) technology development within the last 20 years, the complexed heteroepitaxy, the rather large device dimensions, some remaining reliability issues partially due to the 2DEG proximity with the surface and the absence of avalanche capability still plague its market penetration for medium and high voltage applications. In this frame, vertical GaN-on-Silicon based configuration has been proposed [1]. Theoretically, this technology could show robust performances with avalanche capability and small fingerprint owing to a uniform vertical transport, which has recently been experimentally demonstrated at 800 V [2]. In many cases, pseudo vertical GaN-on-Si devices are used as a test vehicle, for which no backside processing is required. However, this device design suffers from a severe degradation of the on-state resistance (Ron) increasing linearly with the anode size due to the so-called current crowding effect. Fully vertical devices can be achieved by accessing the n+ bottom layer from the backside by means of local substrate and buffer removal using DRIE and ICP, respectively. Some of the device fabrication challenges include 1) the mechanical robustness of the resulting membranes subsequent to the silicon and buffer etching, 2) both p-type and n-type high contact quality to ensure proper on-state performance, 3) the implementation of a heat sink close to the junction enabling high current spreading. At the epitaxy level, as the breakdown voltage scales with the drift layer thickness, both material quality and low bow should be maintained. In this work, we demonstrate high performance fully vertical GaN-on-Silicon PIN diodes with state-of-the-art blocking voltage above 1200 V and low Ron on large diodes resulting in high current spreading close to 12 A.

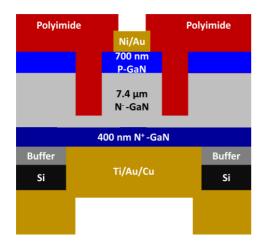

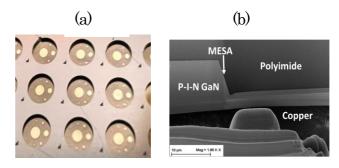

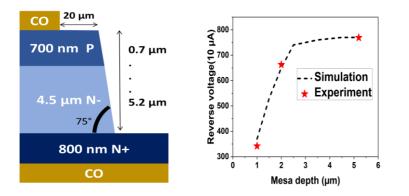

The growth of PIN diodes was performed by MOCVD on 6-inch Silicon substrate by using an optimized buffer as transition layers [3]. The structure contains a 500 nm thick N<sup>+</sup>-bottom layer with a Si-doping of  $5 \times 10^{18}$  cm<sup>-3</sup>, a 7400 nm N-drift layer with a Si- doping of  $9 \times 10^{15}$  cm<sup>-3</sup> (net ionized doping) and a 700 nm of P-top layer with a Mg-doping of  $3 \times 10^{17}$  cm<sup>-3</sup> (active doping) (Fig. 1). The processing started with an optimized deep ICP mesa etching (supported by TCAD simulation), used as edge termination to reduce leakage current (Fig. 3). After mesa etching, a thick polyimide passivation is added to fill in the trenches and enhance the membrane robustness. Then, the Silicon and buffer layers are locally removed using DRIE and ICP tools. Prior to Ti/Au backside metallization, an HCl wet treatment is applied on the n<sup>+</sup> N-face GaN layer to remove the native oxide, which is followed by a thick Copper electroplating of about 100 µm (Fig. 2).

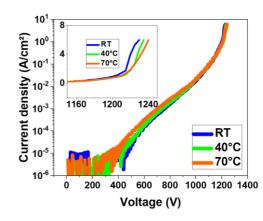

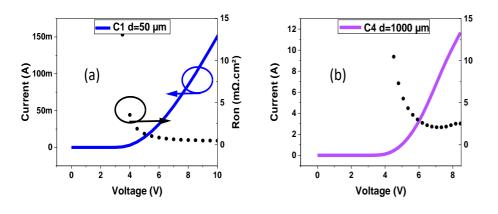

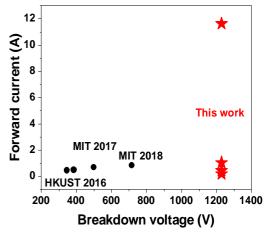

The fabricated diodes show a high breakdown voltage above 1200 V with indication of avalanche signature as seen from off-state temperature measurements (Fig. 4). On-state characteristics show a threshold voltage of about 4V and high current spreading with low Ron (< 0.5 m $\Omega$ .cm<sup>2</sup>) on small diodes. On larger diodes using 1 mm anode radius, the Ron increased to 1.7 m $\Omega$ .cm<sup>2</sup>, which is attributed to thermal management issues that can still be further optimized. Nevertheless, a high on-state current close to 12 A is achieved for the first time with fully vertical GaN-on-Si devices (Fig. 5 and 6). These results translate to a high Baliga figure of merit of 3 GW.cm<sup>-2</sup> and clearly show the potential of this technology for cost-effective high performance next-generation power devices.

### References

- [1] Y. Zhang et al, IEEE Electron Device Lett. Vol. 35, No. 6, (2014)

- [2] Y. Hamdaoui et al, Appl. Physics Express 17, 016503 (2024)

- [3] S. Michler et al, Phys. Status Solidi B 2400019 (2024)

### Acknowledgments

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 101007229. The JU receives support from the European Union's Horizon 2020 research & innovation programme and Germany, France, Belgium, Austria, Sweden, Spain, Italy. This work was also supported by the French RENATECH Network.

Fig. 1 Schematic cross section of the fabricated fully vertical PIN diodes

Fig. 2 (a) Backside image after local substrate and buffer removal (front side contact can be seen by transparency)(b) Focused ion beam image of a fully vertical PIN diode

Fig. 3 Experimental and simulation reverse voltage at 10 µA of 100 µm anode radius PIN diodes showing the benefit of deep mesa etching

Fig. 4 Off-state measurement at various temperature of the fabricated diodes indicating avalanche signature

Fig. 5 On-state measurements of 50  $\mu m$  (a) and 1000  $\mu m$  (b) anode radius of the fully vertical GaN-on-Silicon PIN diodes

Fig. 6 Benchmark of vertical GaN-on-Silicon PIN diodes