## Compact frequency multiplexed readout of silicon quantum dots in monolithic FDSOI 28nm technology

Quentin Schmidt, Baptiste Jadot, Brian Martinez, Thomas Houriez, Adrien Morel, Tristan Meunier, Gaël Pillonnet, Gérard Billiot, Aloysius Jansen, Xavier Jehl, et al.

#### ▶ To cite this version:

Quentin Schmidt, Baptiste Jadot, Brian Martinez, Thomas Houriez, Adrien Morel, et al.. Compact frequency multiplexed readout of silicon quantum dots in monolithic FDSOI 28nm technology. ES-SERC 2024 - IEEE European Solid-State Electronics Research Conference, IEEE, Sep 2024, Bruges, Belgium. pp.157-160, 10.1109/ESSERC62670.2024.10719580 . hal-04752390

### HAL Id: hal-04752390 https://hal.science/hal-04752390v1

Submitted on 24 Oct 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Compact frequency multiplexed readout of silicon quantum dots in monolithic FDSOI 28nm technology

Quentin Schmidt<sup>1</sup>, Baptiste Jadot<sup>1</sup>, Brian Martinez<sup>1</sup>, Thomas Houriez<sup>1</sup>, Adrien Morel<sup>6</sup>, Tristan Meunier<sup>3,4</sup>, Gaël Pillonnet<sup>1</sup>, Gérard Billiot<sup>1</sup>, Aloysius Jansen<sup>2</sup>, Xavier Jehl<sup>2</sup>, Yvain Thonnart<sup>5</sup>, Franck Badets<sup>1</sup>

<sup>1</sup>Univ. Grenoble Alpes, CEA, Leti, <sup>2</sup>Univ. Grenoble Alpes, CEA, IRIG, Pheliqs, <sup>3</sup>Univ. Grenoble Alpes, CNRS, Institut Néel, <sup>4</sup>Quobly, <sup>5</sup>Univ. Grenoble Alpes, CEA, List, F-38000 Grenoble, <sup>6</sup>Univ. Savoie Mont Blanc, SYMME, F-74000 Annecy, France E-mail: quentin.schmidt@cea.fr

Abstract—This paper demonstrates the first on-chip frequency multiplexed readout of two co-integrated single-electron transistors without the need for bulky resonators. We characterize single electron dynamics in both single electron transistors at 4.2K before validating their simultaneous readout within 2.2µs, achieving a 99.9% fidelity with a 1MHz frequency spacing. This experimental demonstration paves the way towards resonator-free large-scale quantum-classical architectures that would be required for future universal and reprogrammable quantum computers.

Keywords—cryo-CMOS, spin qubits, semiconductor qubits, quantum-classical, TIA, transimpedance amplifier, single electron transistors.

#### I. INTRODUCTION

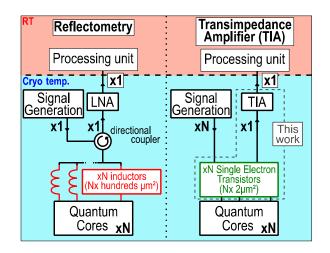

Quantum computers will require hundreds of thousands of physical qubits that will need to be biased, addressed, and read. As for readout, silicon spin qubits must achieve >99.9% fidelity combined with a µs readout time (Ti) while maintaining the total power consumption below 1W to remain compatible with cryogenic (<1K) operation. Furthermore, for quantum error correction, fault-tolerant qubit networks preferably need to be read simultaneously [1]. The integration of cryogenic circuits (Cryo-CMOS) appears as an effective answer for large-scale multiplexed readout, as it could address the restricted wiring capability of cryostats [1-5]. A few parallel readout architectures based on reflectometry have already been proposed in literature, but they require one bulky inductorbased resonator per qubit, making them hard to scale up to the future required number of qubits, Fig. 1 [1-5]. An alternative approach consists in using single electron transistors (SETs) in order to convey state information into nA-range current, followed by an amplification stage made of a single cryogenic transimpedance amplifier (TIA). However, previous implementations [6, 7] do not meet the bandwidth requirements for fast and multiplexed readout, limiting their use to an individual device readout. In [8, 9], integrator-based architectures have been introduced as an alternative achieving fast readout. However, these solutions do not enable the parallel readout of multiple quantum devices and only allow a sequential time multiplexing technique. Recently, [10] proposed a wide bandwidth capacitive feedback TIA (CTIA) operating at 4.2K. Leveraging on this CTIA, this paper

Fig. 1. Block diagram of an envisioned large-scale reflectometry readout compared to the proposed architecture.

demonstrates the first simultaneous measurement of two cointegrated FDSOI SETs using frequency multiplexing without additional bulky resonator, achieving a fidelity of 99.9% for a 2.2µs integration time.

#### II. MULTIPLEXED CHARGE READOUT ARCHITECTURE

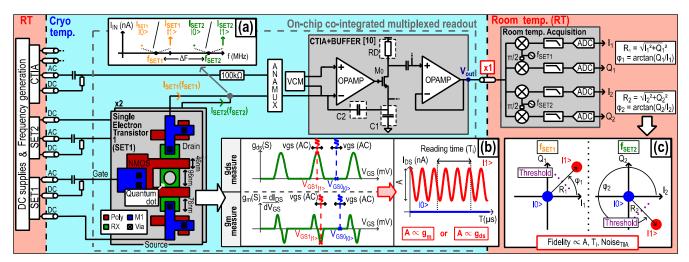

In the envisioned implementation shown in Fig. 1, each qubit is capacitively coupled to a SET, such that a change in the qubit's spin will induce shifts in both SET's transconductance g<sub>m</sub> and output conductance g<sub>ds</sub>. Compared to reflectometry, which relies on inductors, by only using SETs, whose size is comparable to the quantum core itself, the system footprint is minimized, as illustrated in Fig. 1. By modulating respectively the gate or the source with the help of a carrier signal, the g<sub>m</sub> or gds variations could be sensed through the SETs output current amplitude by the readout circuit at the carrier frequency [11]. The proposed measurement setup is illustrated in Fig. 2 and consists in SETs, co-integrated and followed by a single CTIA and a buffer designed in ST28nm FDSOI technology. The DC biases and frequencies generation are brought from room temperature (RT) and the buffer output signal is sent to RT to an on-the-shelf I/Q demodulator. The SETs are made from NMOS FDSOI dual-gate devices with shorted top-gates. FDSOI technology allows high voltage back-biasing (V<sub>bg</sub>=4V) that helps in forming a single dot between both top-gates [12].

Fig. 2. Single electron transistors (SETs) geometry and block diagram of the proposed frequency multiplexed TIA-based readout. (a) Input signal frequency representation. (b) Illustration of the different measurable parameters. (c) Depiction of the thresholding algorithm for I/Q signals.

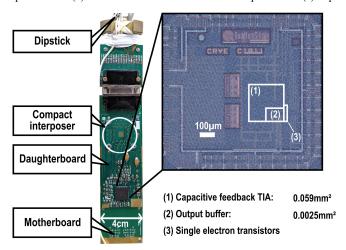

Fig. 3. Picture of PCB and die micrograph.

As illustrated in Fig. 2, the proposed multiplexed readout is based on modulating the voltage of either SET's top-gate or source at distinct frequencies in order to extract respectively the g<sub>m</sub> or g<sub>ds</sub> information of both SETs at the same time. The currents drawn from each SET (IDS) are summed and amplified by the cryogenic CTIA, then sent to RT via the co-integrated buffer through a single wire. At RT, the signal that contains information on both SETs is demodulated at each frequency using parallel I/Q demodulation schemes and digitized to recover the gm or gds of each SET. We define the signal information as the g<sub>m</sub> or g<sub>ds</sub> amplitude difference between states |1> and |0>. As shown in Fig. 2b, state |0> is taken arbitrary as the noise floor, i.e. where no DC current pass through the SET (Coulomb blockade), while the SET is tuned so that the state charge of |1> creates a local maximum in g<sub>m</sub> or g<sub>ds</sub>, i.e. where a DC current I<sub>DS</sub> is flowing through the SET. As illustrated in Fig. 2c, the resulting IQ constellations consist in two amplitude levels that are similar to On-Off Keying (OOK) modulation. Furthermore, the frequency multiplexing technique is alike frequency division multiple access (FDMA), where multiple channels are distributed within the system bandwidth. A digital

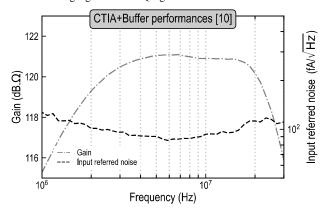

Fig. 4. Standalone cryogenic gain and noise of the proposed amplification

threshold based on the closest mean value is then used to discriminate the parallel measured states, resulting in the readout fidelity and bit error rate (BER).

#### III. MEASUREMENT RESULTS

Figure 3 shows a micrograph of our 1x1mm<sup>2</sup> chip, along with the placement of the CTIA, buffer, and SETs. The mother and daughter PCB boards offer flexibility for various testing setups within a compact layout that is constrained by the cryostat.

The standalone cryogenic performance of the CTIA has been first characterized through a  $100k\Omega$  co-integrated input resistor that emulates an on-chip current source. As it could be seen in Fig. 4, a  $121dB.\Omega$  gain, 25MHz bandwidth and an input referred noise of  $90fA/\sqrt{Hz}$  have been measured for a  $428\mu W$  power consumption. The analog multiplexer (ANAMUX) illustrated in Fig. 2 allows the characterization of the two co-integrated SETs with the help of the CTIA.

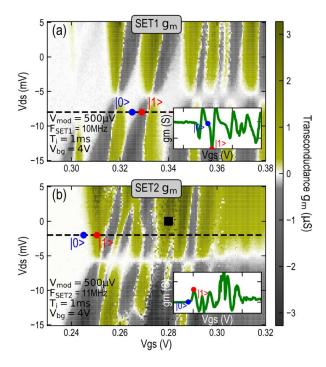

Figure 5 illustrates simultaneous measurement of  $g_m$  for both SETs as a function of  $V_{gs}$  and  $V_{ds}$ , using the proposed gate modulation scheme. Each plot illustrates positive/negative signal-patterns that are consistent with the derivative of Coulomb diamond with respect to the gate voltage, as

Fig. 5. Frequency multiplexed transconductance  $(g_m)$  maps for (a) the first and (b) the second SET. The insets of the data traces along the dashed lines illustrate the blue and red bias points for the qubit state readout.

illustrated in Fig. 2b. The asymmetry observed between the two diagrams, e.g. the shape of the Coulomb diamonds as well as the  $V_{\rm gs}$  range where they are located, are attributed to the geometrical variability between quantum dots. Additionally, the characteristic of SET2 appear particularly sensitive to at least one two-level fluctuator from its immediate environment, as evidenced by the noise at the black square in Fig. 5b [13]. This validates the ability of SETs to sense their electrostatic environment, and thus offers promising perspectives for future qubit state measurements [11].

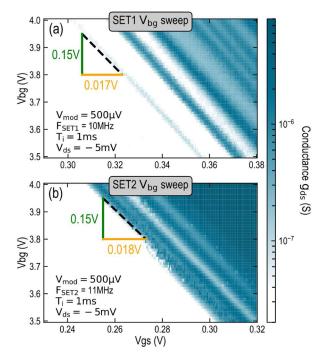

The architecture allows another approach based on source modulation and g<sub>ds</sub> measurement that is illustrated in Fig. 6. As depicted in Fig. 5 and Fig. 6, both measurement techniques lead to the same Coulomb diamond characteristics. As both approaches could present an architectural advantage depending on the selected quantum core network architecture, it confirms the versatility of the proposed readout scheme. In Fig. 7, the conductance  $g_{ds}$  is plotted as a function of  $V_{gs}$  and  $V_{bg}$  for  $V_{ds}$ =-5mV. A constant slope in the entire characteristics is observed for both SETs as a function of the common back-gate voltage V<sub>bg</sub>. We measured a coupling ratio of approximatively 8.5 between the top-gate and the back-gate, which is in the range of typical characteristic values of forward back-biased ST28nm FDSOI NMOS devices, considering the presence of potential impurities [14]. Therefore, it confirms that the observed characteristics are effectively due to the measured quantum devices.

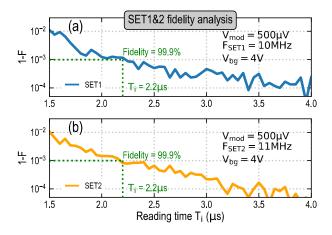

We emulated qubits states measurement with our two SETs by defining specific  $V_{gs}$  and  $V_{ds}$  bias couples, as illustrated in Fig. 5 by the red and blue dots in both SETs  $g_m$  maps. Using these emulated states, Fig. 8 details the fidelity achieved during

Fig. 6. Frequency multiplexed conductance  $(g_{ds})$  maps for (a) the first and (b) the second SET.

Fig. 7. Frequency multiplexed conductance  $(g_{ds})$  maps as a function of the back-gate voltage  $V_{be}$  and  $V_{gs}$  for (a) the first and (b) the second SET.

a simultaneous 2-channel readout as a function of the integration time  $T_i$ . For both SETs, we obtain a 99.9% fidelity (BER=10<sup>-3</sup>) in  $T_i$ =2.2 $\mu$ s, compatible with the aforementioned spin qubit readout requirements. With a frequency separation between channels of  $\Delta F$ =1MHz, no channel overlap was

Fig. 8. SETs fidelity (F) as a function of  $T_{\rm i}$  achieved for a simultaneous gate modulation of both SETs.

observed, as predicted by [10], considering that we are well further the theoretical orthogonally frequency-division multiplexing (OFDM) limit in term of frequency separation ( $\Delta F > 1/Ti$ ).

Table I. presents the comparison of our experimental realization with the existing state-of-the-art of cryo-CMOS readout architectures that were demonstrated with quantum devices. Previous studies based on charge readout [7] have already presented fully integrated architectures. However, the achieved bandwidths were not compatible with the readout time requirements of spin qubits and no parallel readout solution was proposed. Therefore, using charge readout techniques only one QD readout at a time has been demonstrated so far. In [1] a frequency-multiplexed reflectometry-based readout of two QDs, coupled with a time-multiplexing technique, was proposed and achieved the requirements for spin qubits readout. However, the use of bulky inductors raises issues for future large-scale architectures, particularly in terms of space occupation within the cryostat.

#### IV. CONCLUSION

This paper presents a parallel measurement of two SETs at 4.2K, highlighting typical Coulomb diamond characteristics. A frequency spacing of 1MHz with no channel overlap has been demonstrated. The sensing of g<sub>m</sub> and g<sub>ds</sub> were validated by the extracted coupling ratio of 8.5 between the top-gate and backgate, consistent with the typical value for NMOS FDSOI transistors. Both characteristics exhibit expected asymmetry attributed to geometrical variabilities during fabrication. Additionally, the results confirm a particular sensitivity to the nearby electrostatic environment, which is consistent with the charge measurement capabilities of SETs. Finally, this work demonstrate the first fully integrated frequency multiplexed readout of several quantum devices that requires no additional resonators. Moreover, the achieved reading time of 2.2µs with a fidelity of 99.9% meets the requirements for spin qubit readout. This constitutes a first step toward large-scale compatible TIA-based readout architectures that could be integrated into fault-tolerant quantum computers.

TABLE I. EXPERIMENTAL REALIZATION OF QUANTUM DEVICES READOUT WITH CRYO-CMOS

|                                                | ISSCC20 [7]       | Nature22 [1]         | This work          | Unit |

|------------------------------------------------|-------------------|----------------------|--------------------|------|

| Reading type                                   | Charge readout    | Reflectometry        | Charge<br>readout  | -    |

| Architecture                                   | Direct I/Q        | Q-C SM <sup>b</sup>  | Direct I/Q         | -    |

| IC Temperature                                 | 0.11              | 0.05                 | 4.2                | K    |

| Technology                                     | FDSOI 28nm        | Bulk 40nm            | FDSOI 28nm         | -    |

| Off-chip components at cryogenic temp.         | No                | Dir. Coupler,<br>LNA | No                 | -    |

| Demonstrated<br>Multiplexing                   | No                | Time and frequency   | Frequency          | -    |

| Simultaneously<br>evaluated quantum<br>devices | 1 QD <sup>d</sup> | 2 QDs <sup>d</sup>   | 2 QDs <sup>d</sup> | -    |

| Footprint                                      | 0.01              | $0.44^{a,c}$         | 0.06               | mm²  |

| Power consumption                              | 0.001             | -                    | 0.428              | mW   |

| Operating frequency                            | 0.001             | 6,000-8,000          | 1.5-25             | MHz  |

a Reported data that doesn't consider discrete cryogenic electronics.

d Quantum Dot

#### **ACKNOWLEDGMENTS**

This work is supported by the French National Research Agency under the program "France 2030" (PEPR PRESQUILE - ANR-22-PETQ-0002). Electronic PCBs were supplied by CEA test engineers as part of the European Qu-test project.

#### REFERENCES

- Ruffino et al. "A cryo-CMOS chip that integrates silicon quantum dots and multiplexed dispersive readout electronics", Nat Electron 5, 2022.

- [2] Y. Peng et al., "A cryo-CMOS wideband quadrature receiver with frequency synthesizer for scalable multiplexed readout of silicon spin qubits," JSSC, vol. 57, 2022.

- [3] J. Park et al., "A fully integrated cryo-CMOS SoC for state manipulation, readout, and high-Speed gate pulsing of spin qubits," JSSC, vol. 56, 2021.

- [4] B. Prabowo et al., "13.3 A 6-to-8GHz 0.17mW/qubit cryo-CMOS receiver for multiple spin qubit readout in 40nm CMOS technology," ISSCC, 2021.

- [5] A. Nagulu et al., "Sub-mW/qubit 5.2-7.2GHz 65nm cryo-CMOS RX for scalable quantum computing applications," CICC, 2023.

- [6] M. L. V. Tagliaferri et al., "Modular printed circuit boards for broadband characterization of nanoelectronic quantum devices," TIM, vol. 65. 2016.

- [7] L. L. Guevel et al., "19.2 A 110mK 295μW 28nm FDSOI CMOS quantum integrated circuit with a 2.8GHz excitation and nA current sensing of an on-chip double quantum dot," ISSCC, 2020.

- [8] H. Fuketa et al., "A cryogenic CMOS current comparator for spin qubit readout achieving fast readout time and high current resolution," VLSI Technology and Circuits, 2022.

- [9] M. Castriotta *et al.*, "Fully integrated cryo-CMOS spin-to-digital readout for semiconductor qubits," SSCL, vol. 6, 2023.

- [10] Q. Schmidt et al., " A 7.4μW and 860μm² per channel cryo-CMOS IC for 70-channel frequency-multiplexed μs-readout of semiconductor qubits," CICC, 2024.

- [11] Yang *et al.*, "Operation of a silicon quantum processor unit cell above one kelvin", Nature 580, 2020.

- [12] L. Le Guevel *et al.*, "Low-power transimpedance amplifier for cryogenic integration with quantum devices", Applied Phy. Rev., vol. 7, 2020.

- [13] C. Spence et al., "Probing low-frequency charge noise in few-electron CMOS quantum dots", Phys. Rev. Appl., vol. 19, 2023.

- [14] L. Le Guevel et al., « Impedancemetry of multiplexed quantum devices using an on-chip cryogenic complementary metal-oxide-semiconductor active inductor », Chip, vol. 2, 2023

b Quantum-classical Switch Matrix. c Estimate

<sup>&</sup>lt;sup>c</sup> Estimated from chip micrograph <sup>d</sup>