# Reading reliability in 1S1R OTS+PCM devices based on Double-Patterned Self-Aligned structure

Renzo Antonelli, Guillaume Bourgeois, Valentina Meli, Zineb Saghi, Théo Monniez, Simon Martin, Niccoló Castellani, Mathieu Bernard, Leila Fellouh, Antoine Salvi, et al.

#### ▶ To cite this version:

Renzo Antonelli, Guillaume Bourgeois, Valentina Meli, Zineb Saghi, Théo Monniez, et al.. Reading reliability in 1S1R OTS+PCM devices based on Double-Patterned Self-Aligned structure. ESREF 2024 - 35th European Symposium on Reliability of Electron Devices, Failure Physics and Analysis, Sep 2024, Parme, Italy. hal-04717271

### HAL Id: hal-04717271 https://hal.science/hal-04717271v1

Submitted on 1 Oct 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Reading reliability in 1S1R OTS+PCM devices based on Double-Patterned Self-Aligned structure

R. Antonelli<sup>a,b</sup>, G. Bourgeois<sup>a</sup>, V. Meli<sup>a</sup>, Z. Saghi<sup>a</sup>, T. Monniez<sup>a</sup>, S. Martin<sup>a</sup>, N. Castellani<sup>a</sup>, M. Bernard<sup>a</sup>, L. Fellouh<sup>a</sup>, A. Salvi<sup>a</sup>, S. Gout<sup>a</sup>, F. Andrieu<sup>a</sup>, A. Souifi<sup>b</sup>, G. Navarro<sup>a,\*</sup>

<sup>a</sup> CEA-Leti, Univ. Grenoble Alpes, 38000 Grenoble, France <sup>b</sup> Univ. Grenoble Alpes, CNRS, LTM, 38054 Grenoble, France \* Email: gabriele.navarro@cea.fr

#### Abstract

This study investigates the reliability of the reading operation in 1S1R devices based on Ovonic Threshold Switching (OTS) selector and Phase-Change Memory (PCM) co-integrated in a Double-Patterned Self-Aligned (DPSA) structure targeting Crossbar applications. Upon reading, the SET state can face a threshold voltage ( $V_{th}$ ) increase of more than 20% dependently on the reading current and on the number of reading operations, which can lead to a soft failure. We separate the contributions to this increase coming respectively from OTS and PCM, finally providing an assessment protocol for the reading reliability. We show how the reading performances allow to determine the maximum Crossbar array size depending on the target voltage Read Window Margin and current Memory Window.

#### 1. Introduction

The 1S1R cell (one selector, one resistor), co-integrating at the same time the memory and the selector device and used as main block of 3D Crossbar arrays, is considered an excellent solution for high-density Back-End-of-Line (BEOL) memories [1, 2]. The 1S1R implemented by combining Phase-Change Memory (PCM) and Ovonic Threshold Switching (OTS) selector, demonstrated its high potential in Storage Class Memory (SCM) and cache replacement [3]. PCM is the most mature among emerging memory technologies, offering a small footprint, and non-volatility [4] making it suitable for embedded applications [5]. The OTS selector provides low leakage current, fast switching speed, and stackability in the BEOL of the integration [6, 7]. The significant advantage of integrating OTS with PCM is the possibility to implement a self-aligned integration approach, reducing lithographic mask requirements and enhancing overall yield [8]. In this study, we based our analyses on a Double Patterned Self-Aligned (DPSA) OTS+PCM device [9]. We investigate the impact of the reading operation, critical for OTS+PCM devices reliability. We propose a protocol based on consecutive reading operations, at different reading currents and durations, to assess the reduction of the effective voltage Read Window Margin (RWM) and current Memory Window (MW). When the PCM is programmed in the SET state (i.e. crystalline phase), a repeated reading is responsible for an increase of the threshold voltage ( $V_{th}$ ) up to more than 20% with respect to the starting SET threshold voltage ( $V_{th,SET}$ ), leading to possible soft failures.

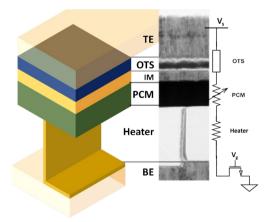

Fig. 1. 3D scheme and Transmission Electron Microscopy (TEM) image of a DPSA 1S1R OTS+PCM device, with a simplified circuit scheme of the device on the right.

By comparing the results obtained from 1S1R, 1S OTS and 1R PCM devices, we are able to study the different contributions to the  $V_{th}$  increase. We find a correlation between the  $V_{th}$  shift, the SET read current ( $I_{read,SET}$ ) and the number of reading cycles, showing that the RWM reduction (soft bit fail) is caused by repeated reading of the cell, independently from the value of the read current. Finally, we show how the reading reliability in 1S1R cells, without considering smart reprogramming strategies, can affect the choice of the maximum Crossbar array size based on the target MW and RWM.

#### 2. OTS+PCM device reading reliability protocol

#### 2.1. ISIR DPSA device

The DPSA device structure is depicted in Fig. 1 and previously described in detail in [9]. The cell is fabricated through two patterning ("Double-Patterned"), allowing at the same time the PCM alignment with the heater element and the definition of the OTS dimensions ("Self-Aligned"). The phase-change material considered in our study is Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, and the OTS selector is based on a GeSbSeN alloy [7]. The OTS layer was integrated between two thin carbon layers to hinder intermixing with electrodes. The Top Electrode (TE), Bottom Electrode (BE), Intermediate Metal (IM), and heater are made of titanium nitride (TiN). We tested devices integrated in kb arrays, with critical dimensions ranging from 80 nm up to 300 nm.

#### 2.2. Reading reliability test protocol

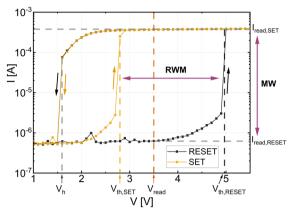

When PCM is co-integrated with a two-terminal nonlinear selector as the OTS, the read current (I<sub>read</sub>) depends on the state of the memory and the voltage partition between the two [10]. The common 1S1R reading principle involves the switching of the device to exploit its high Ion/Ioff current ratio (Fig. 2). If the PCM device is in the low resistance state (SET), the reading voltage (V<sub>read</sub>) chosen inside the RWM allows the switching of the OTS and a significant current flow in the device (I<sub>read,SET</sub>). If the PCM device is in the high resistance state (RESET) both the OTS and the PCM do not reach the threshold condition and the device does not switch providing a low current flow (I<sub>read,RESET</sub>) that depends on both PCM and OTS resistances. Therefore, the reading relies on the current MW that is defined as the ratio between I<sub>read,SET</sub> and I<sub>read,RESET</sub>. A reading fail can be generated if the cell does not switch at V<sub>read</sub> due to an unwanted increase of the V<sub>th,SET</sub> (SET failure), or if the cell switches at V<sub>read</sub> when programmed in the RESET state (RESET failure).

Fig. 2. Typical IV curves of a DPSA 1S1R OTS+PCM in SET and RESET states. The main electrical parameters are highlighted. The MW is calculated as the ratio  $I_{\rm read,SET}/I_{\rm read,RESET}$  and the RWM as the difference between the  $V_{\rm th}$  when the device is programmed in the RESET state ( $V_{\rm th,RESET}$ ) and the SET state ( $V_{\rm th,RESET}$ ). The curve is obtained as the median of about 300 devices.

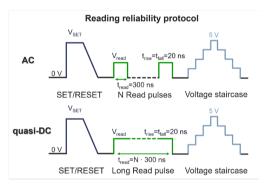

Fig. 3. AC and quasi-DC protocols description.

We devised two test protocols to investigate the impact and reliability of the reading (**Fig. 3**). The *AC* protocol consists of a programming pulse (SET or RESET), followed by a fast sequence of multiple reading pulses of duration  $t_{read} = 300$  ns each. The *quasi-DC* protocol involves the same programming pulse, with a subsequent long read pulse of duration equivalent to N· $t_{read}$ , where N corresponds to the number of read cycles performed in the *AC* protocol. In both cases, a staircase-up sequence records the IV curve of the device and detects its  $V_{th}$ . We selected a  $V_{read}$  of 3.5 V and a  $I_{read,SET}$  ranging from 60  $\mu$ A up to 400  $\mu$ A. The  $I_{read,SET}$  is limited by a series NMOS transistor.

#### 3. 1S1R reading reliability

#### 3.1. RESET state reading

The PCM in RESET state is highly resistive with a  $V_{th}$  close to 2 V, in series with the OTS  $V_{th}$  of 3 V, resulting in an overall  $V_{th,RESET}$  of approximately 5 V. When employing the *quasi-DC* protocol, the  $I_{read}$  is

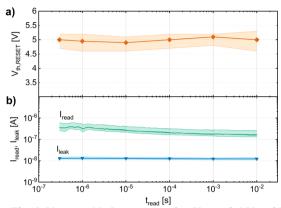

Fig. 4.  $V_{th,RESET}$  (a);  $I_{read}$  measured at  $V_{read} = 3.5$  V and  $I_{leak}$  at 1.75 V (b) for different read pulse duration  $t_{read}$  during *quasi-DC* protocol (*AC* showed equivalent results). The graphs report the median values and the Interquartile Ranges (IQR) of about 150 1S1R devices.

sampled during the read pulse, followed by the measurement of the leakage current ( $I_{leak}$ ) at  $V_{read}/2$  and of the  $V_{th}$ . Fig. 4a presents the median  $V_{th}$  over multiple  $t_{read}$  intervals.  $V_{th,RESET}$  remains constant independently from the reading pulse duration and no switching occurs. Indeed,  $I_{read}$  remains below 1  $\mu$ A (Fig. 4b).  $I_{leak}$  is more than one order of magnitude lower than  $I_{read}$  confirming the good preservation of the OTS selecting performances. The RESET state confirms to be stable under the reading protocols used, with no failures detected during our tests.

#### 3.2. SET state reading

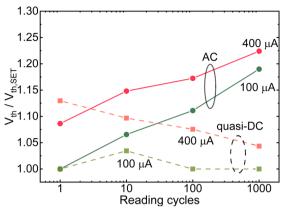

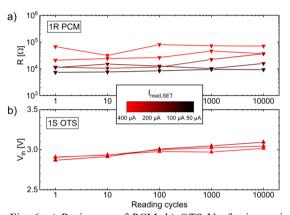

By applying the AC protocol to the device in the SET state, the threshold voltage increases (Fig. 5) shifting from the as-programmed V<sub>th,SET</sub>. There is both a marked dependency on the number of reading cycles as well as on I<sub>read,SET</sub>. Performing the test on a 1R PCM cell (Fig. 6a) highlights a direct link between the resistance of the PCM cell and the SET read current. On the other hand, in the OTS alone there is no apparent trend linked to the read current amplitude while the number of cycles produce a threshold increase of more than 200 mV (Fig. 6b). Comparing the results of the AC and quasi-DC protocols on 1S1R cell (Fig. 5), V<sub>th</sub> significantly increases in AC reading protocol, up to more than 20% (i.e. ~0.4 V), while with the quasi-DC protocol, as the width of the pulse increases, we observe a first increase of V<sub>th</sub> followed by a decrease down to the initial V<sub>th,SET</sub>. We correlate such difference to the number of the switching events, which occur at each reading pulse in the AC, and once in the *quasi-DC*. In both protocols, the shift increases

We approximate the  $V_{th}$  evolution along the AC reading cycles number with the following empirical relation:

Fig. 5. Vth over  $V_{\text{th,SET}}$  as a function of the applied reading pulses in 1S1R devices for AC (solid lines) and quasi-DC (dashed lines) protocols at different  $I_{\text{read,SET}}$ . The median values are obtained from about 200 1S1R devices.

Fig. 6. a) Resistance of PCM. b) OTS  $V_{th}$  for increasing number of reading cycles at multiple  $I_{read}$ . Median from 30 devices each.

$$V_{th}(N) \approx V_{th0} + log_{10}(N) \cdot \Delta V_{th-N}$$

(1)

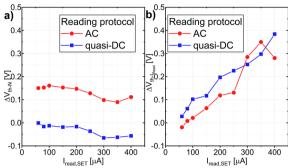

Here the slope  $\Delta V_{th-N}$  represents the increase in threshold voltage due to the total number of cycles (i.e. number of switches), while the intercept  $V_{th0}$  corresponds to the starting  $V_{th}$  (i.e. after the first reading). Fig. 7a reports  $\Delta V_{th-N}$  as a function of the reading current. The  $V_{th}$  shift wrt  $V_{th,SET}$  is almost independent from  $I_{read,SET}$  and it is constant at about 150 mV for the AC protocol and about zero in quasi-DC case. The intercept  $V_{th0}$  appears linearly correlated to  $I_{read,SET}$ , describing  $\Delta V_{th-Iread}$  as the increment over  $V_{th,SET}$  due to reading (Fig. 7b):

$$\Delta V_{\text{th-Iread}} = V_{\text{th0}} - V_{\text{th,SET}} \propto I_{\text{read,SET}}$$

(2)

The obtained results show that  $\Delta V_{th\text{-N}}$  depends only on the switching events of the selector (Fig. 5, 6, 7a). Such a shift is attributable to the evolution of the OTS material induced by the current density spike happening at the switching event. Indeed, it can lead

Fig. 7. a)  $\Delta V_{th\text{-N}}$  as a function of  $I_{read,SET}$  in agreement with (1). b)  $\Delta V_{th\text{-Iread}}$  shift as a function of  $I_{read,SET}$  in agreement with (2). The median values are obtained from about 200 1S1R devices.

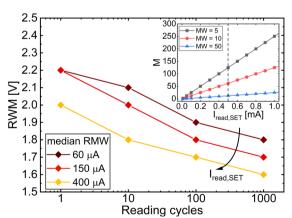

to an increase in the localization of defects in the conductive path, thereby increasing the resulting  $V_{th}$  [11]. On the other hand,  $\Delta V_{th\text{-Iread}}$  increase can be correlated to a partial PCM amorphization due to an increasing  $I_{read,SET}$ , approaching a programming condition, independently from the number of reading cycles N. Both  $I_{read,SET}$  and N decrease the RWM (Fig. 8). Limiting  $I_{read,SET}$  may not be sufficient to avoid SET soft failures when multiple readings are performed without reprogramming, due to the switching event effects on OTS. A possible strategy to mitigate  $\Delta V_{th\text{-Iread}}$  could be to increase the read pulse fall time (i.e. re-programming).

In light of these findings, it is possible for Crossbar design to select the appropriate density of an M×M matrix which maximizes the RWM, MW, and N before refresh (inset of Fig. 8) considering the worst-case MW ( $I_{leak}$  when all unselected cells are in SET):

$$MW = \frac{I_{read,SET}}{2(M-1) \cdot I_{leak} + I_{read,RESET}}$$

(3)

Fig. 8. Voltage RWM evolution over repeated reading cycles for different I<sub>read,SET</sub>. The inset shows the maximum number of rows (cols) in a M×M matrix for different MWs calculated from (3). The dashed line in the inset separates the reading and the programming current regions.

#### 4. Conclusions

In this article we assess the impact of reading operations on the reliability of the programmed states in DPSA 1S1R OTS+PCM devices. RESET state showed high stability to reading, while SET state faces a V<sub>th</sub> increase up to more than 20% of the starting V<sub>th,SET</sub>. We evidence a double dependency of V<sub>th</sub> shift: a gradual increase due to the switching event generated during the reading operations into the OTS device (ΔV<sub>th-N</sub>); and a constant increase proportional to the reading current  $I_{read,SET}$  ( $\Delta V_{th-Iread}$ ) likely related to the PCM partial amorphization. By reducing I<sub>read SET</sub> the number of allowed reading cycles increases (before triggering a first SET soft failure), and the SET V<sub>th</sub> shift decreases, enabling a higher voltage RWM. However, a high I<sub>read,SET</sub> is important to preserve the reading current MW, therefore we justify how in Crossbar array design it should be carefully selected in order to maximize RWM, MW and the number of possible reading cycles.

#### Acknowledgments

Thanks to C. De Camaret for the fruitful discussions. This work has been partially supported by Univ. Grenoble Alpes through LabEx Minos ANR-10-LABX-55-0, partially by the European Commission and French State through ECSEL-IA 101007321 project StorAIge, and partially supported by the French Public Authorities within the frame of France 2030 as part of the IPCEI Microelectronics and Connectivity.

#### References

- [1] D. Kau et al., IEEE International Electron Devices Meeting, pp. 1-4, 2009.

- [2] T. Kim and S. Lee, IEEE Trans. Electron Devices, vol. 67, p. 1394-1406, 2020.

- [3] H. Y. Cheng et al., J. Phys. D: Appl. Phys., vol. 52, p. 473002, 2019.

- [4] F. Arnaud et al., IEEE International Electron Devices Meeting, p. 24.2.1-24.2.4, 2020.

- [5] P. Cappelletti et al., J. Phys. D: Appl. Phys., vol. 53, p. 193002, 2020.

- [6] H. Y. Cheng et al., IEEE International Electron Devices Meeting, pp. 37.3.1-37.3.4, 2018.

- [7] A. Verdy et al., IEEE International Memory Workshop, pp. 1-4, 2018.

- [8] T. Kim et al., IEEE International Electron Devices Meeting, p. 37.1.1-37.1.4, 2018.

- [9] G. Bourgeois et al., 7th IEEE Electron Devices Technology & Manufacturing, pp. 1-3, 2023.

- [10] M. Alayan et al., IEEE International Electron Devices Meeting, pp. 2.3.1-2.3.4, 2017.

- [11] S. Ban et al., IEEE Electron Device Letters, vol. 41, no. 3, pp. 373-376, 2020.