## Low-Voltage Schottky p-GaN HEMT Properties under Extreme Repetitive Short-Circuit Operation Conditions: 2DEG Pinch-off, Stability, Aging, Robustness and Failure-Modes Analysis [Abstract]

Frédéric Richardeau, Lucien Ghizzo, David Trémouilles, Sébastien Vinnac

#### ▶ To cite this version:

Frédéric Richardeau, Lucien Ghizzo, David Trémouilles, Sébastien Vinnac. Low-Voltage Schottky p-GaN HEMT Properties under Extreme Repetitive Short-Circuit Operation Conditions: 2DEG Pinchoff, Stability, Aging, Robustness and Failure-Modes Analysis [Abstract]. 35th European Symposium on Reliability of Electron Devices, Failure Physics and Analysis - ESREF 2024, Sep 2024, Parma, Italy. hal-04713127

### HAL Id: hal-04713127 https://hal.science/hal-04713127v1

Submitted on 3 Oct 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Low-Voltage Schottky p-GaN HEMT Properties under Extreme Repetitive Short-Circuit Operation Conditions: 2DEG Pinch-off, Stability, Aging, Robustness and Failure-Modes Analysis [Abstract]

F. Richardeau<sup>a,\*</sup>, L. Ghizzo<sup>b</sup>, D. Trémouilles<sup>c</sup>, S. Vinnac<sup>a</sup>

<sup>a</sup> LAPLACE University of Toulouse, CNRS, INPT, UPS, Toulouse, France

<sup>b</sup> THALES SIX France SAS, Toulouse, France

<sup>c</sup> LAAS-CNRS, University of Toulouse, CNRS, Toulouse, France

#### **Abstract**

The authors proposed in-depth experimentation and physical analysis showing the extreme robustness capability of low-voltage GaN HEMT in single and repetitive short-circuit. A 2DEG pinch-off behavior is analyzed depending on  $V_{DS}$  voltage and charges' trapping / de-trapping relaxation time. A new drain-gate leakage-current mechanism at turn-off is suggested to explain the ultimate thermal-runaway failure-mechanism.

#### 1. Context and purpose of the article

Power lateral GaN HEMT with low voltage (LV) rating are gaining popularity for various new applications. The main ones are future 48 V DC-link automotive power distribution and power electromobility like torque assistance for electric bikes and motor control for light e-scooters and e-motorcycles [1-3]. LV GaN HEMT devices are also increasingly preferred for space applications as a substitute for expensive and limited Rad-Hard silicon MOSFET [4]. So far, except for specific cases like multilevel converters [5], LV GaN HEMT device has not been a significant part of the power conversion stages in power-chain. These are typically the high-voltage network side stage, also named "Active Front-End Converter (using Power Factor Controller)", and the motor-inverter side stage, also named "Active Back-End Converter". These two conventional power stages require at least medium voltage (MV) or high voltage (HV) devices and must endure harsh environmental and operational conditions such as short-circuits (SC) events. Hence the LV GaN HEMT devices have not been extensively studied in extreme operation than their MV and HV counterpart. However, with the anticipation of future 48V power applications and the importance of "embedded distribution and actuator" applications, it appears crucial to explore the specific properties of LV GaN HEMT in SC events with the same attention as for MV counterparts. Ref. [6] in 2013, is probably the first on SC-LV GaN HEMT but no physical analysis were included, and repetitive SC was not performed. Today in 2024, the bibliography appears limited: partial and nonexhaustive data are available in manufacturer reliability reports [7] and seem to show a higher level of robustness than MV/HV devices rating. Over the past two years, however, two articles have caught our attention in repetitive SC-100 V GaN HEMT: [8] focuses on the AlGaN barrier - p-GaN stack interface defects impact on the drift - recovery behavior under 48 V-70 V bias stress and [9] investigates the possible hot-electron induced permanent defects at high electric field (60 V-70 V bias stress). This submission presents our contribution from dedicated intensive in-depth experimentation protocol "on-line stress - off-line monitoring on curves tracer" and physical analysis. The abstract is organized as follows: section II covers the dedicated test bench and the LV DUTs used; in section III the special 2DEG pinch-off property is analyzed in low energy SC; in section IV the 2DEG drifts will be depicted for repetitive long-time pulse and high energy SC including the special transient drain-gate leakage current at turn-off; in this last section a thorough analysis of the de-trapping charges relaxation-time and possible aging effect using a dedicated single ultrashort-pulse SC is presented; finally in Section V, destructive operations and failure-mechanisms are investigated in ultra-long-time pulse / high energy proving the exceptional robustness capability of LV GaN HEMT in all short-circuit conditions.

#### 2. Test bench, DUT stressed, and Protocol used

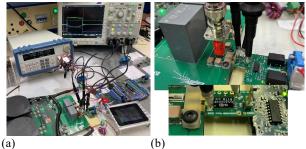

Fig. 1 (a) shows an overview of the designed "easy-touse modular plug-in" boards to perform SC: a generic motherboard includes the film capacitors bank and the

F.Richardeau *et al.*, Low-Voltage Schottky p-GaN HEMT Properties under Extreme Repetitive Short-Circuit Operation Conditions: 2DEG Pinch-off, Stability, Aging, Robustness and Failure-Modes Analysis.

35<sup>th</sup> European Symposium on Reliability of Electron Devices, Failure Physics and Analysis, ESREF'2024, 23-26 September 2024, Parma, Italy. Accepted Authors Abstract for presentation in conference: https://hal.science/Full paper to be published in journal: Microelectronics Reliability, Special Issue 2025.

electronic fuse-breaker safety stage, a daughter board was designed to reduce the stray inductance of the downstream switching loop using ceramic capacitors and including a wide bandwidth / current range sensor  $(10 \text{ m}\Omega/2 \text{ GHz})$ . DUTs are soldered on a dedicated plug-in board as shown in Fig. 2 (b), including measurement vias for the scope on the top side and leads on the bottom side for off-line and off-bench measurements using a B1505A curve tracer. The gatedriver board and DUT's board are soldered edge-to-edge using two metalized half-cut vias on each board. DUTs ref. are recent 100 V-7 mΩ@25 °C commercial devices, enhancement-mode Schottky p-GaN gate-type and mains features/gate drive parameters are depicted in Tab. 1. Note that main stresses are performed at 2/3 x  $BV_{DSSmin}$  (100 V) = 67 V as is commonly specified by end-users and/or datasheet for SC practical qualification test.

Fig. 1 (a) SC test bench overview, (b) modular easy-to-use and singleuse DUT PCB plug-in with gate-driver for Ref. A (below) and B (above).

Table 1 DUTs description (a dozen of each are used, Ref. B are divided into two sets: first and second set)

| DUT                   | Ref. A (1)                                           | Ref. B (2)                  |

|-----------------------|------------------------------------------------------|-----------------------------|

| I <sub>D</sub> (25°C) | 90 A                                                 | 16 A                        |

| Active area           | 7.32 mm <sup>2</sup>                                 | 3.75 mm <sup>2</sup>        |

| Case type             | Epoxy-based PCB material                             | Naked die with solder bumps |

| Gate voltage          | +6 V/-3 V                                            | +5 V/0 V                    |

| Gate resistors        | $R_{GON}\!/R_{GOFF\text{-SSD}}:10~\Omega/100~\Omega$ |                             |

Note: SSD is an acronym of (SC) Soft-Shut-Down

# 3. 2DEG pinch-off property in low-energy single-pulse SC (abstract)

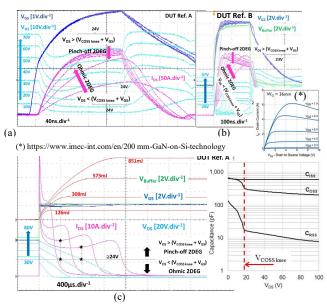

Preliminary, to avoid thermal influence and to guarantee safe testing, a 200 ns short-time pulse under incremental drain–source voltage bias is performed in Fig. 2 (a) and (b) for DUT ref. A and B. A 2DEG pinch-off effect is highlighted depending on  $V_{\rm DS}$  bias : the SC current decreases for higher  $V_{\rm DS}$ . In Fig. 2 (c), to confirm this original property, a permanent pulse is applied under low energy storage and a continuously decreasing drain–source voltage. The 2DEG pinch-off depending on  $V_{\rm DS}$   $\geq$  ( $V_{\rm COSS\ knee}$  +  $V_{\rm GS}$ ) is clearly visible, just like the transition to the quasi-ohmic conduction for  $V_{\rm DS}$  < ( $V_{\rm COSS\ knee}$  +  $V_{\rm GS}$ ), leading to a stronger 2DEG current

density as a bell-like shape as seen in quasi-static I<sub>DS</sub>(V<sub>DS</sub>) curve [8]. In Fig. 2 (c) the device's self-heating cannot be neglected given the long-pulse used, however our background analysis regarding the pinch-off effect is preserved as graphically marked in dashed-line on I<sub>DS</sub>(t) waves. Finally, the 2DEG pinch-off intensification caused by the lateral-field plate HEMT structure at high drain-source voltage bias tends to mitigate the power density and then the temperature rise. As long as the p-GaN gate stack edge is protected from the electric field peak, this behavior appears to be favourable overall for LV GaN robustness, as it will be presented in §5. This property is clearly opposed to what is known for classical vertical power devices. In addition, the high current rise through the stray inductance of the switching loop at turn-on leads to a strong relative value drain-source voltage drop which reduces the local transient power density and the thermal stress in LV GaN much more than in the case of HV Si, SiC and GaN power devices in same operation conditions. This property contributes to avoiding early thermal runaway, as will be illustrated in §5.

Fig. 2 2DEG's pinch-off transient behavior in SC operation, under (a) 200 ns short-pulse for DUT ref. A [6.2 kA. $\mu$ s<sup>-1</sup>, 1.7 kW.mm<sup>-2</sup>], (b) 200 ns short-pulse for DUT ref. B [8.8 kA. $\mu$ s<sup>-1</sup>, 3.8 kW.mm<sup>-2</sup>] and (c) permanent-pulse with low energy storage on the motherboard (the external DC power supplied is disconnected). Note:  $V_{COSS\ knee\ ref.\ A\ and\ B} \cong 18\ V\ and\ from\ the\ datasheet,\ then\ from\ Tab.\ 1\ giving\ the\ gate\ voltage\ drive,\ V_{COSS\ knee\ +}\ V_{GS} \cong 24\ V\ for\ DUT\ ref.\ A\ and\ V_{COSS\ knee\ +}\ V_{GS} \cong 23\ V\ for\ DUT\ ref.\ B.$

# 4. 2DEG drift and de-trapping relaxation delay-time, aging and drain-gate transient leakage under long-time high-energy repetitive-pulse SC (abstract)

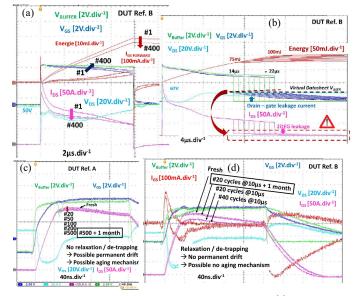

Single and repetitive pulses under long-time SC ( $\sim 10~\mu s$ ) at high-energy operation conditions are now analyzed in Fig. 3 (a) and (b). The saturation current exhibits a strong decrease caused by the electrons'

F.Richardeau *et al.*, Low-Voltage Schottky p-GaN HEMT Properties under Extreme Repetitive Short-Circuit Operation Conditions: 2DEG Pinch-off, Stability, Aging, Robustness and Failure-Modes Analysis.

35<sup>th</sup> European Symposium on Reliability of Electron Devices, Failure Physics and Analysis, ESREF'2024, 23-26 September 2024, Parma, Italy. Accepted Authors Abstract for presentation in conference: https://hal.science/

mobility decrease at high-temperature rise and amplified by the source-contact ohmic drop-voltage of the lateral structure. In addition, a strong Metal/p-GaN Schottkybarrier gate leakage-current arises, leading to a slight gate-source voltage-drop through the external gateresistor and then reinforcing the decrease of the saturation current. The power-density and temperature self-limiting properties lead to an impressive SC withstand time capability (T<sub>SCW</sub>) higher than the 10µs standard value:  $T_{SCW REF.A | 67V} > 300 \mu s$ ,  $E_{critical REF.A} >$ 6.8 J.cm<sup>-2</sup> and  $T_{SCW REF.B SET 1 | 67V} = 22 \mu s$ ,  $E_{critical}$ REF.B SET 1 ≅ 2.7 J.cm<sup>-2</sup>. Such extreme SC robustness can also be obtained for an HV device as long as the first transient power-peak over the first few hundred ns analyzed in §3 is withstanded [11]. This condition is not required for LV devices. Note that the extreme robustness of Ref. A can also be explained in part by its Epoxy-based PCB material case where internal copper layers and vias act as thermal spreaders. In addition, gate-leakage monitoring provides a relevant thermal diagnosis [12] and a means of SC detection [13].

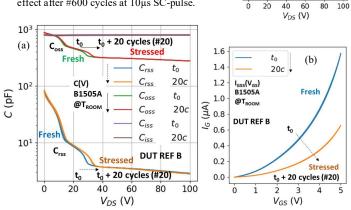

Repetitive SC-pulses reveal a continuous decrease of the 2DEG conductivity, probably caused by bulk electrons trapping, leading to a further decreased saturation current clearly visible at the beginning of the SC after the 2DEG peak but just before the temperature effect becomes dominant. To confirm this hypothesis, a  $C_{OSS\text{-RSS}}(V_{DS})_{\mid VGS=0}$  curve in the off-bench is suggested in Fig 4 (a) for Ref. B, highlighting a positive drift of the V<sub>COSS 2nd knee</sub> (24 V to 27 V) with a field-plate influence, which could be caused by a trapping effect around the AlGaN gate-region. I<sub>DSS</sub>(V<sub>DS</sub>) curve shows a spectacular leakage decrease by repetitive SC annealing-effect (Fig. 3 (e),  $I_{DSS} > \mu A$  to nA at 100 V) for Ref. A.  $I_{GSS}(V_{GS})$ curve highlights also a hole injection decrease in Fig. 4 (b) for Ref. B, as in Fig. 3 (a) and confirmed in [8]. In the full paper, the authors will show that trapping and leakage signatures are not regular as a function of the number of SC cycles: it occurs essentially after the first cycles, probably rapidly saturating traps.

In Fig. 3 (c) and (d), re-using an SC ultra short-time single-pulse to avoid thermal influence as in §3, it is interesting to realize that a quasi-complete device restoring by de-trapping effect can be performed on Ref. B after a 1 month relaxation time at V<sub>GS</sub>=V<sub>DS</sub>=0 V and at T<sub>ROOM</sub>, as analyzed in [8]. In contrast, Ref. A does not exhibit restoring, which leads us to believe that the 2DEG pinch-off drift could be more attributed to an aging mechanism caused by hot-electron under high electric field [11] and not directly to a trapping effect as Ref. B. In Fig. 3 (a), it can also be seen a gate-source leakage decrease. As suggested by [8], channel electrons are captured but the Metal/p-GaN/AlGaN interface defects, elevating the potential barrier and reducing the gate-stack hole injection, leading to a slight reduction of the transient gate leakage-current.

Finally, a last important property is now visible at the SC turn-off: a drain-gate transient leakage-current tail over some tens us is clearly visible in Fig. 3 (b) for a long-time SC-pulse and at high energy. This leakage could come from the p-GaN/AlGaN PIN diode reverse conduction under the electric-field peak, gate's fieldplate side, at high-temperature conditions. Deeper analyses are in progress. This reverse gate-current flows from the gate to the source electrodes across the external gate-resistor and leads to a gate-source voltage increase which tends to maintain the 2DEG not fully pinched-off with a residual drain – source leakage (some amps): 0 V +  $R_{GOFF}$ . $|I_{GS}(t)| \cong V_{GSTH}$  or  $> V_{GSTH}$ . As it will be seen in §5, this mechanism can initiate a fatal thermal runaway of the device at the SC turn-off.

SC Cycling

B1505A (600 cycles) @T<sub>ROOM</sub>

DUT 6; 600 #

DUT 7: 600 #

DUT 9; 600 ft

Idss[A] (e) Fig. 3 2DEG behavior under long-time repetitive-pulse at high-energy (a) DUT Ref. B 10-5 2DEG pinch-off drift from #1 to #400 cycles at 10-6  $8\;\mu s$  medium-time pulse SC (b) DUT Ref. B incremented SC-pulse and drain-source 10leakage at turn-off (c) DUT Ref. A probable 10-8 aging effect (no de-trapping relaxation after DUT 6: t<sub>0</sub> #500 cycles at 10 µs SC-pulse) (d) DUT Ref. B DUT 7; to de-trapping relaxation after #20-40 cycles at 10-10 DUT 8; t<sub>0</sub> 10μs SC-pulse (e) DUT Ref. A SC annealingeffect after #600 cycles at 10µs SC-pulse. 20

Fig. 4 DUT Ref. B curve tracer signatures from #0 (t0) to #20 cycles at 10 μs SC-pulse (a) all C(V) behavior (b) gate-source leakage I<sub>GSS</sub>(V<sub>GS</sub>).

F.Richardeau et al., Low-Voltage Schottky p-GaN HEMT Properties under Extreme Repetitive Short-Circuit Operation Conditions: 2DEG Pinch-off, Stability, Aging, Robustness and Failure-Modes Analysis.

<sup>35</sup>th European Symposium on Reliability of Electron Devices, Failure Physics and Analysis, ESREF'2024, 23-26 September 2024, Parma, Italy. Accepted Authors Abstract for presentation in conference: https://hal.science/ Full paper to be published in journal: Microelectronics Reliability, Special Issue 2025.

# 5. Robustness and failure-modes in ultra-long-time or permanent-pulse SC (abstract)

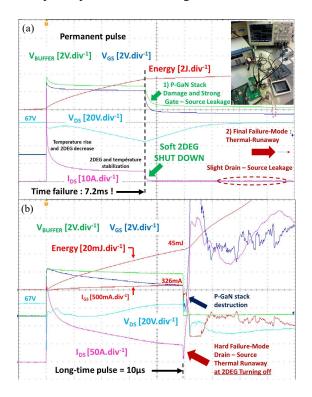

Finally, SC in ultra-long-time (ms range) or permanentpulse is performed and analyzed in Fig. 5, including possible destructive modes. In Fig. 5 (a), Ref. A is specifically stressed in permanent-pulse mode due to its extreme SC energy robustness, as seen in §4. This device exhibits hard gate-damage at 7.2ms, leading to a current overload of the gate-driver's auxiliary supply and the gate-source voltage collapse below the threshold: a spectacular 2DEG soft and self-turn-off appears. Unfortunately, this 2DEG secure pinch-off effect is not fully performed, and a residual drain-source leakage leads to a delayed thermal runaway and the destruction of the device. Future work is planned to isolate the self-turn-off property and to perform gateregion failure analysis. In Fig. 5 (b), Ref. B (second-type set stressed) is now stressed with an incremented ultralong-time to reach its T<sub>SCW</sub> and to reveal the failuremode. As it will be discovered previously in §4 at the SC turn-off, a strong transient drain-gate leakagecurrent maintains the gate-source voltage near the threshold ( $R_{GOFF} = R_{SSD} = 100 \Omega$ ) and does not provide a uniform and effective 2DEG cut-off, leading to a quick thermal runaway and the final destruction of the device. Using a lower  $R_{GOFF}$  value ( $R_{GOFF} \le 100 \Omega$ ) this failuremode could probably be delayed but with an unacceptable practical over-voltage at the SC turn-off.

Fig. 5 Failure-modes analysis in high-energy SC (a) DUT Ref. A permanent pulse showing hard gate-damage and soft self 2DEG turn-off at 7.2 ms afterward, giving a residual drain-source gate leakage and a delayed final destructive thermal runaway (b) DUT Ref. B quick and hard thermal runaway at turn-off by drain-gate transient leakage.

#### 6. Conclusion (abstract)

Intensive in-depth experimentation and physical analysis demonstrate the extreme SC robustness capability of LV HEMT GaN in single and repetitive SC operation conditions mainly performed at  $2/3 \times BV_{DSSmin}$  on a dedicated, modular and integrated test bench. The 2DEG pinch-off behavior, depending on the  $V_{COSS \, knee}$  value and the electrons trapping, was studied using the  $C_{OSS}(V_{DS})_{|VGS=0}$  curve in off-bench. A drain–gate transient leakage-current tail is also highlighted at SC turn-off, maintaining the gate-voltage near the threshold, leading to the 2DEG not fully cut-off and a destructive quick thermal-runaway failure-mode.

#### References

[1] A. Kempitiya et al., "100V GaN for Highly Efficient 1kW Motor Drive Applications," 2022 IEEE 9th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Redondo Beach, CA, USA, 2022, pp. 238-241, doi: 10.1109/WiPDA56483.2022.9955272. [2] Lei Kou et al., "Advantages of 100V GaN in 48V Applications", Bodo's Power Systems, September 2020, pp. 36 – 39. [3] "Premium Motor Drive Performance at Low Cost for e-bikes, Drones, and Robotics with GaN FETs", Robotics Tomorrow, Online Robotics Trade Magazine, Industrial Automation, Robots and Unmanned Vehicles, 2022.

[4] J.-B. Sauveplane *et al.*, "Heavy-Ion Testing Method and Results of Normally OFF GaN-Based High-Electron-Mobility Transistor," in *IEEE Transactions on Nuclear Science*, vol. 68, no. 10, pp. 2488-2495, Oct. 2021, doi: 10.1109/TNS.2021.3109990.

[5] L. Horowitz et al., "High Power Density Flying Capacitor Multilevel Inverter for Electric Aircraft with a Stacked PCB Interleaved Hybrid Commutation Loop Design," 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 2023, pp. 1065-1069, doi: 10.1109/APEC43580.2023.10131394. [6] C. Abbate et al., "Thermal instability during short circuit of normally-off AlGaN/GaN HFETs", Microelectronics Reliability, Volume 53, Issues 9–11, 2013, Pages 1481-1485, https://doi.org/10.1016/j.microrel.2013.07.119.

[7] EPC Efficient Power Conversion, Reliability Report - Phase 15, 2023, pp. 9 – 12.

[8] M. Wang et al., "Recoverable Current Collapse Effect of p-GaN HEMTs Under Short Circuit Stress," 2023 IEEE 2nd International Power Electronics and Application Symposium (PEAS), Guangzhou, China, 2023, pp. 141-144, doi: 10.1109/PEAS58692.2023.10395456. [9] N. Yang et al., "Study of the Short-Circuit Capability and Device Instability of p-GaN Gate HEMTs by Repetitive Short-Circuit Stress,' in IEEE Transactions on Power Electronics, vol. 39, no. 2, pp. 2247-2257, Feb. 2024, doi: 10.1109/TPEL.2023.3332663.

[10] Andrea Minetto et al., "Hot electron effects in AlGaN/GaN HEMTs during hard-switching events", Microelectronics Reliability, Volume 126, 2021, https://doi.org/10.1016/j.microrel.2021.114208. [11] M. Landel et al., "Study of short-circuit robustness of p-GaN and cascode transistors", Microelectronics Reliability, Volume 138, 2022, https://doi.org/10.1016/j.microrel.2022.114695. [12] A. Borghese et al., "Gate Driver for p-GaN HEMTs with Real-

[12] A. Borghese et al., "Gate Driver for p-GaN HEMTs with Real-Time Monitoring Capability of Channel Temperature," 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 2021, pp. 63-66, doi: 10.23919/ISPSD50666.2021.9452317.

[13] Y. Barazi et al., "p-GaN HEMT Hard Switching Fault Type Short-Circuit Detection Based on the Gate Schottky-Barrier Leakage Current and Using a Dual-Channel Segmented CMOS buffer Gate-Driver," 2023 35th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Hong Kong, 2023, pp. 64-67, doi: 10.1109/ISPSD57135.2023.10147669.