### ERTS 2024 - 12th European Congress on Embedded Real Time Software and Systems

Mohamed Kaâniche, Philippe Cuenot, Kevin Delmas, Jean Marc Gabriel, Adrien Gauffriau, Christophe Grand, Eric Jenn, Christine Rochange, Marie de Roquemaurel

#### ▶ To cite this version:

Mohamed Kaâniche, Philippe Cuenot, Kevin Delmas, Jean Marc Gabriel, Adrien Gauffriau, et al.. ERTS 2024 - 12th European Congress on Embedded Real Time Software and Systems. 12th European Congress on Embedded Real Time Software and Systems (ERTS 2024), pp.1–489, 2024. hal-04643654

### HAL Id: hal-04643654 https://hal.science/hal-04643654v1

Submitted on 10 Jul 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

EMBEDDED REAL TIME SYSTEMS

# ERTS 2024

11-12 JUNE, TOULOUSE - FRANCE DIAGORA CONGRESS CENTER

ORGANIZED BY

#### Editors

Mohamed Kaaniche LAAS-CNRS

Philippe Cuenot Continental Automotive Marie de Roquemaurel Airbus Defence & Space

Kevin Delmas Onera

Jean-Marc Gabriel Ampere Software Technology

Adrien Gauffriau Airbus Christophe Grand Onera

Eric Jenn IRT St Exupéry

Christine Rochange IRIT

## **Contents**

| Progran  | n Committee                                                                                                                                                  | 7        |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|          | - ML/AI Embedded                                                                                                                                             | 9        |

| (        | Real-Time Semantic Segmentation of Aerial Images Using an Embedded U-Net: A Comparison of CPU, GPU, and FPGA Workflows                                       | 11<br>23 |

| Tu.1.B - | - Realtime System 1                                                                                                                                          | 33       |

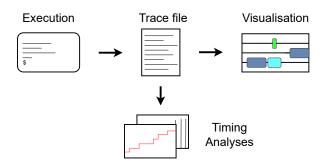

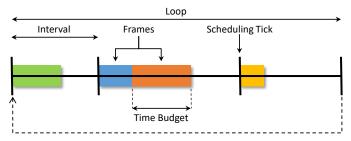

| ]        | Runtime Performance Evaluation of a Non-Preemptive Cooperative Multithreading Framework Through Tracing                                                      | 35       |

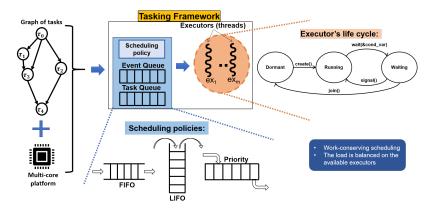

|          | A Novel Heuristic Framework for Offline IMA Schedule Generation for Multicore Platforms                                                                      | 45       |

| Tu.1.C - | - Network                                                                                                                                                    | 57       |

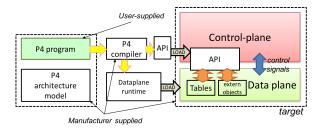

| <b>(</b> | Specifying network switches using the P4 language: lessons learned                                                                                           | 59       |

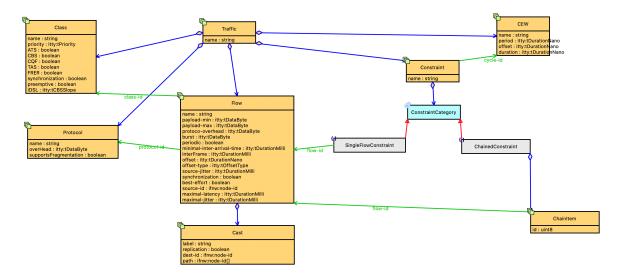

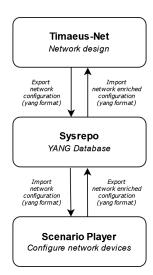

|          | Yet another experience on TSN tools interoperability for critical embedded networks                                                                          | 67       |

| Tu.2.Po  | - Poster overview                                                                                                                                            | 77       |

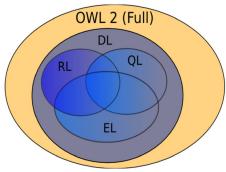

|          | Acceleration of Embedded Reasoning in Symbolic AI                                                                                                            | 79       |

|          | How to efficiently handle real world ECU traffic in MICROSAR Adaptive                                                                                        | 83       |

|          | 1                                                                                                                                                            | 89       |

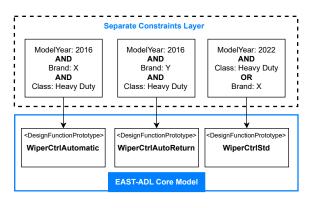

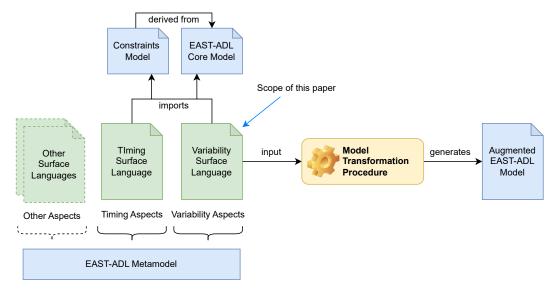

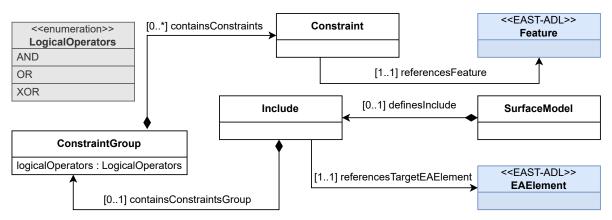

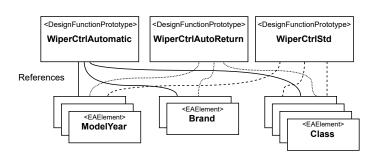

| ]        | Towards Compact Surface Languages for Specific Modelling Aspects in EAST-ADL Development and Evaluation of a Prototyping Platform for the Simulation, Trans- | 95       |

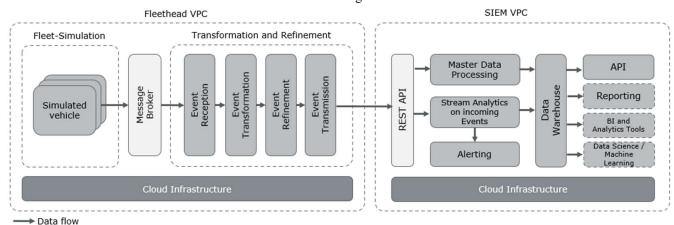

|          | mission, and Real-Time Analysis of Realistic AUTOSAR Security Event Traffic                                                                                  | 99       |

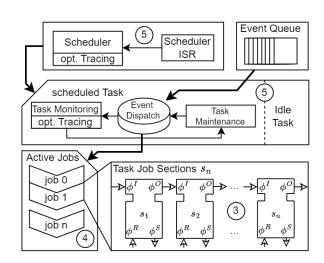

|          | Timing Architecture Model for Embedded Systems Anomaly Detection                                                                                             | 103      |

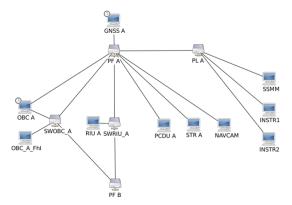

| 8        | aeronautic environment                                                                                                                                       | 109      |

|          |                                                                                                                                                              | 113      |

|          | y y                                                                                                                                                          | 119      |

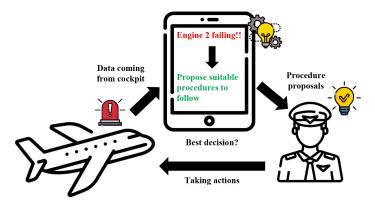

|          | Integrating operator's cognitive profile for dynamic and human-centric adaptation                                                                            | 125      |

| (        | of industrial processes                                                                                                                                      | 129      |

| Tu.3.A   | - ML/AI Certification 1                                                                                                                                      | 133      |

|          | ı v                                                                                                                                                          | 135      |

|          | A study of an ACAS-Xu exact implementation using ED-324/ARP6983 On the Feasibility of EASA Learning Assurance Objectives for Machine Learning                | 147      |

|          | ·                                                                                                                                                            | 159      |

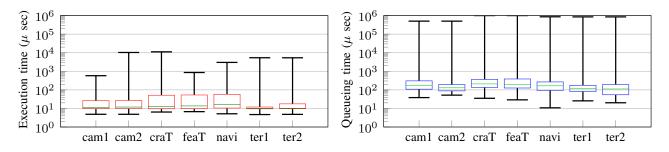

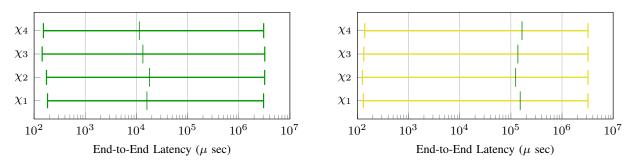

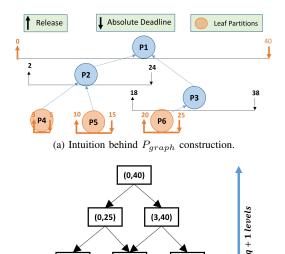

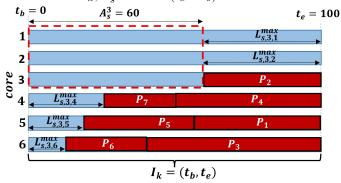

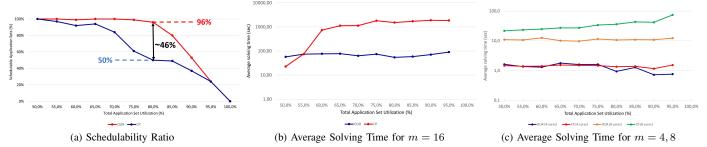

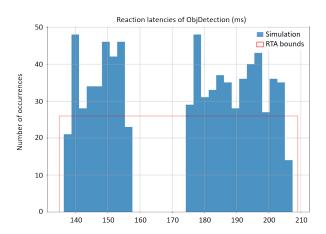

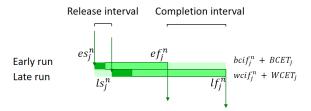

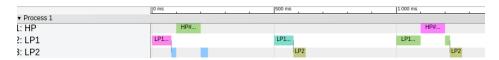

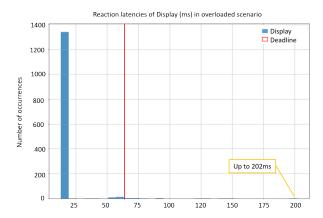

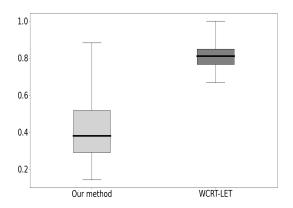

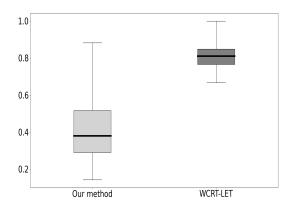

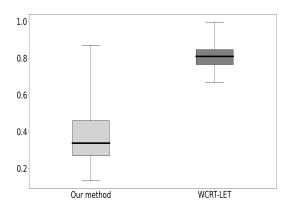

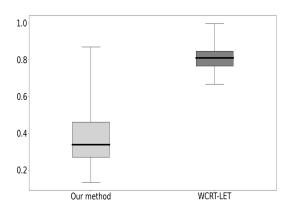

| Tu.3.B                                  | <ul> <li>Realtime System 2</li> <li>Performance and confidence in feasibility analysis of real-time multi-core distributed</li> </ul>                                                                                                                                                         | 171                                           |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|                                         | systems                                                                                                                                                                                                                                                                                       | 173<br>183                                    |

|                                         | wate Accelerators through I ML                                                                                                                                                                                                                                                                | 100                                           |

| Tu.3.C                                  | <ul> <li>Hardware Security</li> <li>Onchip Traffic Injection to Counteract Timing Side-Channel Attacks</li> <li>Approach for High-Performance Random Number Generators for Critical Systems</li> <li>Considering the Aeronautics Cyber-Security Standards for Multi-Core Platforms</li> </ul> | 195<br>197<br>207<br>217                      |

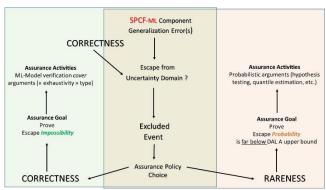

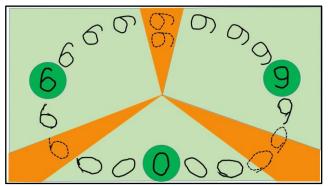

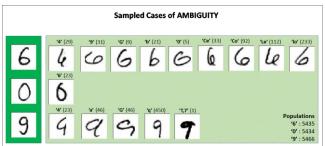

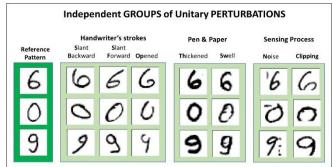

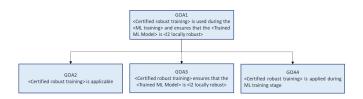

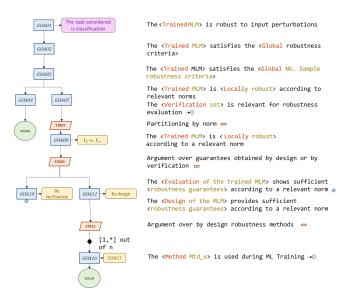

| Tu.4.A                                  | <ul> <li>Assurance Case for ML</li> <li>Assurance Cases to face the complexity of ML-based systems verification</li> <li>Uncertainty in Assurance Case Template for Machine Learning</li> </ul>                                                                                               | 229<br>231<br>243                             |

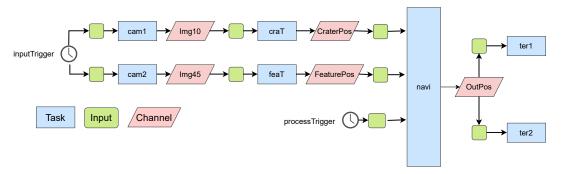

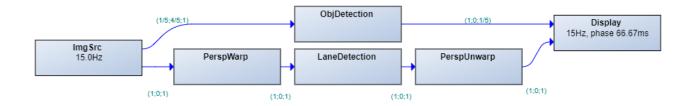

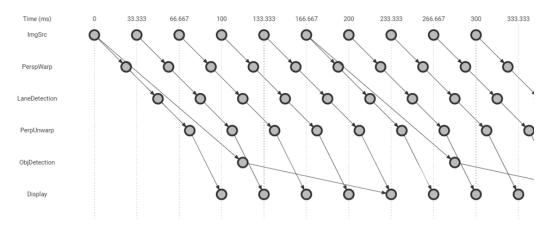

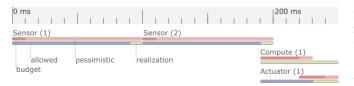

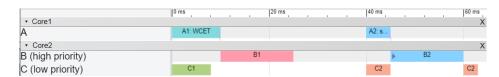

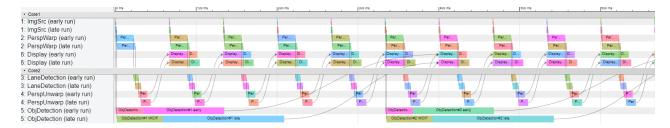

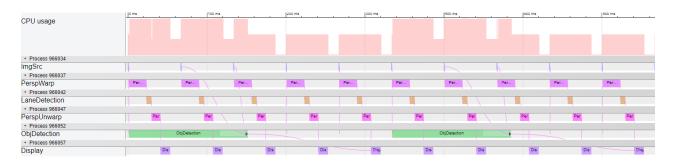

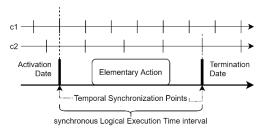

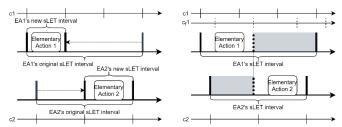

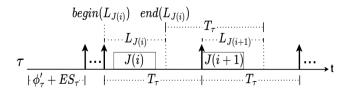

| Tu.4.B                                  | - Logical Execution Time  Separation of functional and time interferences concerns for efficient AMC 20-193 compliance                                                                                                                                                                        | <ul><li>253</li><li>255</li><li>265</li></ul> |

| Tu 4 C                                  | - Security                                                                                                                                                                                                                                                                                    | 275                                           |

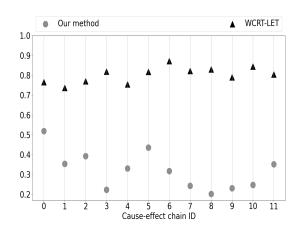

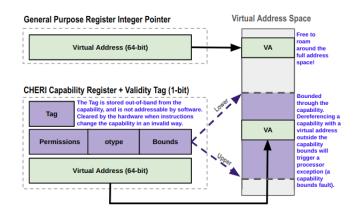

| 1u.4.0                                  | Security by Default - CHERI ISA Extensions Coupled with a Security-Enhanced Ada Runtime                                                                                                                                                                                                       | 277<br>291                                    |

| We.1.A                                  | - ML/AI for Critical System 1                                                                                                                                                                                                                                                                 | 303                                           |

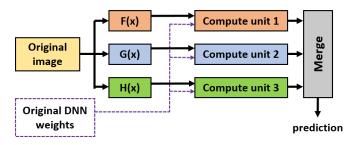

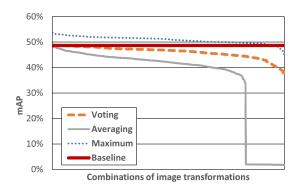

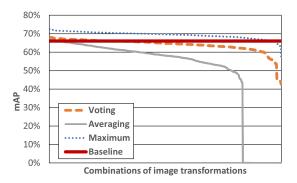

|                                         | Software-Only Semantic Diverse Redundancy for High-Integrity AI-Based Functionalities                                                                                                                                                                                                         | 305<br>315                                    |

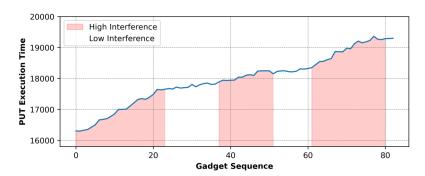

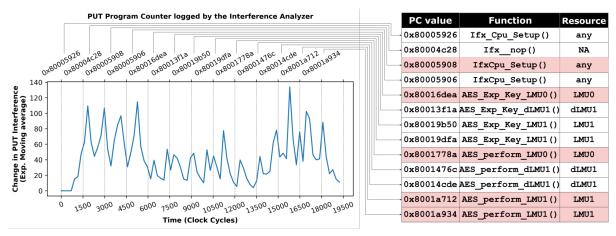

| We.1.B                                  | - Realtime Interference                                                                                                                                                                                                                                                                       | 325                                           |

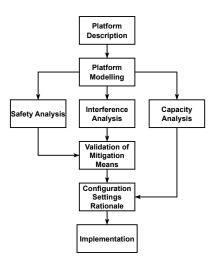

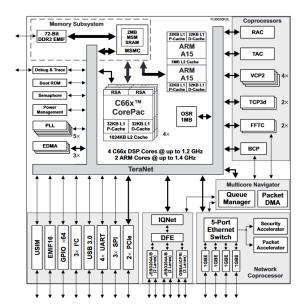

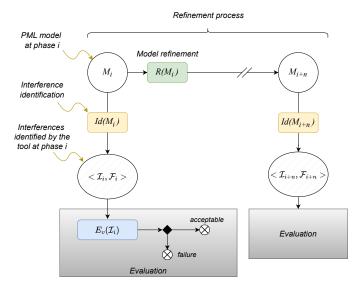

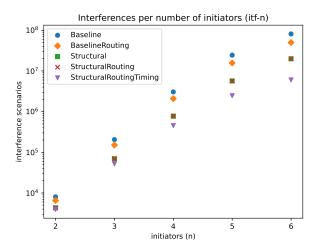

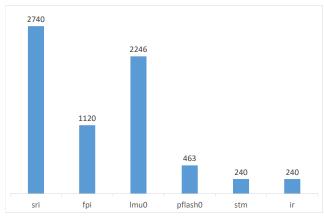

| ,,,                                     | A Refinement Method for Interference Analysis using the PHYLOG Modeling Language                                                                                                                                                                                                              | 327<br>337                                    |

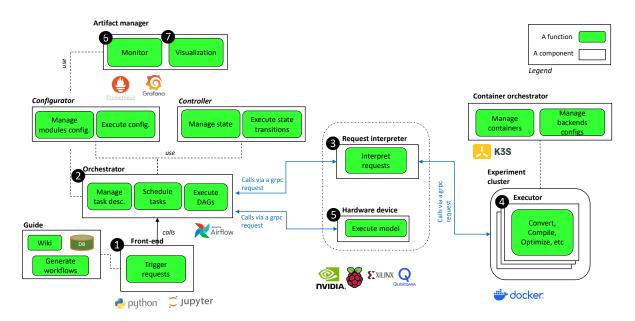

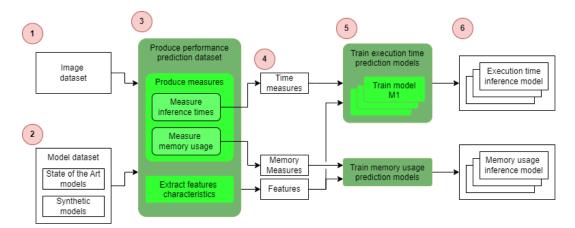

| We 1.C                                  | - Benchmarking                                                                                                                                                                                                                                                                                | 347                                           |

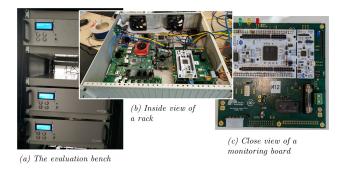

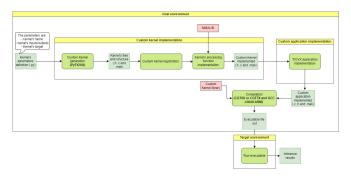

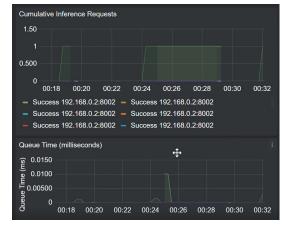

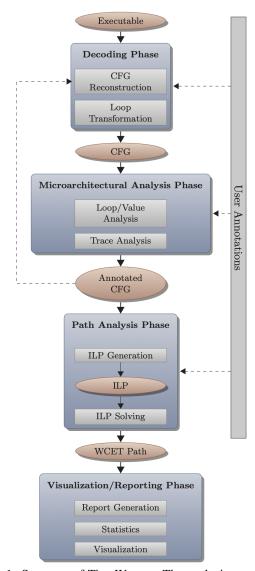

| ,,,,,,,,,                               | An Evaluation Bench for the Exploration of Machine Learning Deployment Solutions on Embedded Platforms                                                                                                                                                                                        | 349<br>359                                    |

| We.4.A                                  | - Autonomous Sytem & Digital Twins                                                                                                                                                                                                                                                            | 369                                           |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Digital twin for embedded software. State of art in industry and deployment at Renault Group for powertrain                                                                                                                                                                                   | 371                                           |

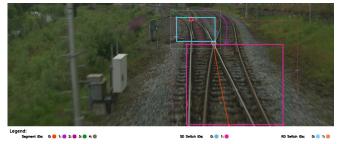

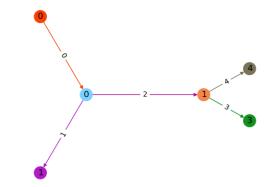

|                                         | Towards safe obstacle detection for autonomous train operation: Combining track and switch detection neural networks for robust railway ego track detection Partially trustworthy action planning thanks to an easily certified plan validator .                                              | 379<br>389                                    |

| We.4.B                                  | - Testing                                                                                                                                                                                                                                                                                     | 399                                           |

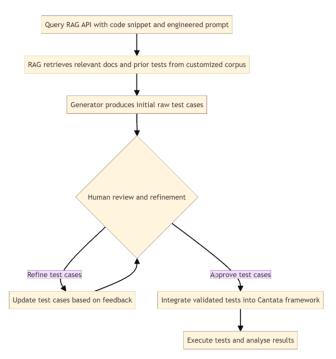

|                                         | Design by contract formal verification for automotive embedded software robustness Automated Test Suite Augmentation using Language Models: Applying RAG to Improve Robustness Verification                                                                                                   | 411<br>423                                    |

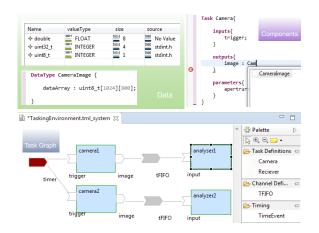

| We.4.C – Model Driven Development                                                 | 433  |

|-----------------------------------------------------------------------------------|------|

| Large legacy systems design maintainability through modeling                      | 435  |

| Coupling optimization using Design Structure Matrices (DSM) and Genetic Algorithm | 1445 |

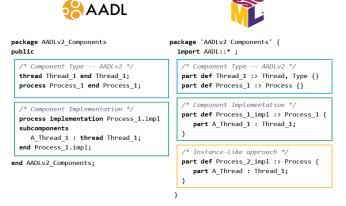

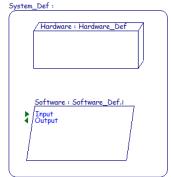

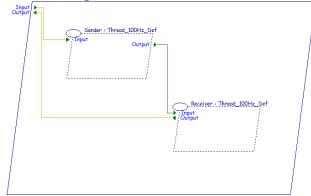

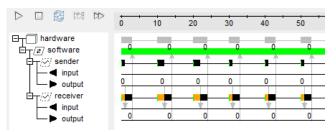

| Specializing SysMLv2 for Real-Time Safety- Critical Systems – an Experiment with  |      |

| AADLv2                                                                            | 455  |

| We.5.A – ML/AI for Critical System 2                                              | 465  |

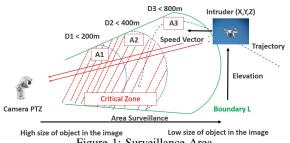

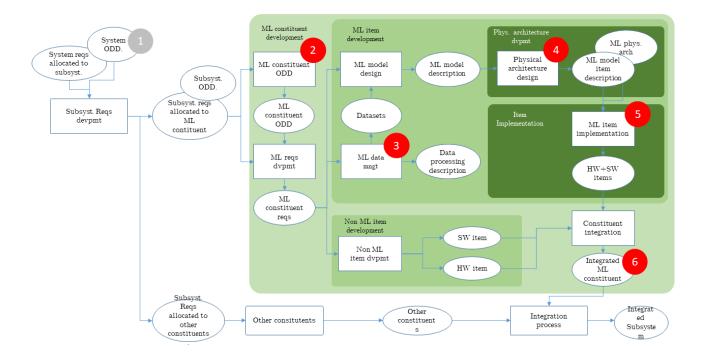

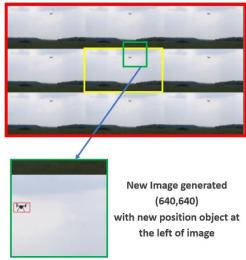

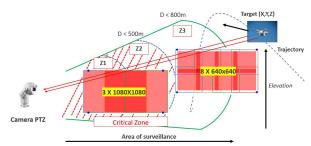

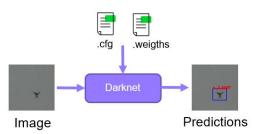

| Certified ML Object Detection for Surveillance Missions                           | 467  |

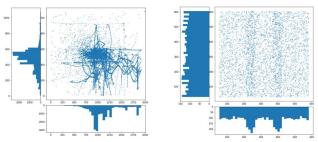

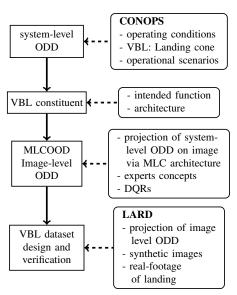

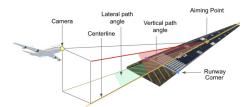

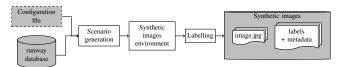

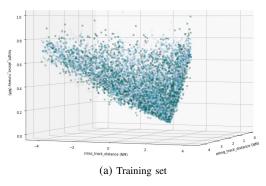

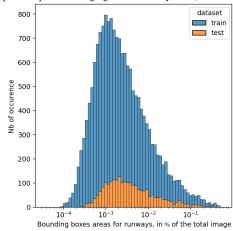

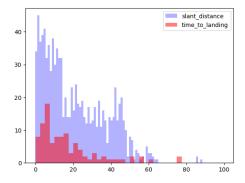

| How to design a dataset compliant with a ML-based system ODD?                     | 477  |

| Authors index                                                                     | 487  |

### **Program Committee**

Ahiad, Samia VALEO

Anguenot, Yves Aerospace Valley

Armengaud, Eric Armengaud Innovate GmbH

Barrilado, Andres NXP

Baufreton, Philippe Safran Electronics & Defense

Belmonte, Fabien Alstom Transport SA

Boyer, Marc ONERA

Braband, Jens Siemens AG

Bruguier, Florent LIRMM

Cazorla, Francisco J Barcelona Supercomputing Center

Christofi, Nikolena IRT Saint Exupery

Claraz, Denis Vitesco Technologies France SAS

Cuenot, Philippe Continental

Delmas, Kevin ONERA

Dreiseitel, Stefan Draexlmaier

Faucou, Sebastien Université de Nantes

Florent, Meurville Valeo Frezouls, Benoit CNES Gabriel, Jean-Marc Renault

Gallina, Barbara Mälardalen University

Gauffriau, Adrien Airbus

Gimenez, Pierre-François CentraleSupelec

Gogniat, Guy Université de Bretagne Sud - UEB

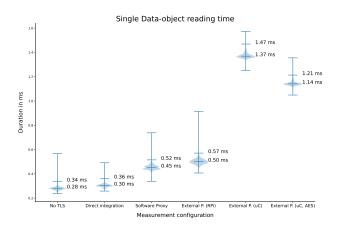

Grand, Christophe ONERA

Guerin, Joris Université de Montpellier

Guiochet, Jérémie LAAS-CNRS

Habli, Ibrahim University of York

Heckmann, Reinhold AbsInt GmbH

Jan, Mathieu CEA LIST

Jean-Louis, Boulanger certifer

Jenn, Eric Thales Avionics

Johnson, Chris Queen's University Belfast

Kaaniche, Mohamed LAAS-CNRS Le Calvez, Gilles VALEO Lecomte, Thierry CLEARSY

Leconte, Bertrand Airbus Operations SAS

Ledinot, Emmanuel THALES Research & Technology

Lonn, Henrik Volvo Group

Mader, Ralph Vitesco Technologies GmbH

Maillet-Contoz, Laurent STMicroelectronics

Malenfant, Jacques Sorbonne Université – LIP6

Mamalet, Franck IRT Saint Exupery

Mekki-Mokhtar, Amina ANSYS Morgan, Benoît IRIT Mraidha, Chokri CEA LIST

Métayer, Natacha Institut VEDECOM Navet, Nicolas University of Luxembourg

Niemetz, Michael OTH Regensburg

Pagetti, Claire ONERA Pautet, Laurent ENST Picard, Celia ENAC

Pinot, Frédéric Hitachi rail STS Pons, Philippe Aerospace Valley Prof. Dr. Mottok, Juergen  $LaS^3$ , OTH Regensburg

Quere, Philippe Stellantis

Rochange, Christine IRIT - Université de Toulouse

Ruiz, Jose AdaCore Shagdar, Oyunchimeg Renault

Stea, Giovanni University of Pisa

Thomas, Carsten HTW Berlin

Totel, Eric Supelec

Troubitsyna, Elena KTH

Verdier, Damien EasyMile

Vigouroux, David IRT Saint-Exupery

Voget, Stefan Continental Automotive GmbH

Warns, Timo Airbus

Wartel, Franck AIRBUS Defence and Space de Roquemaurel, Marie Airbus Defence & Space

# Session Tu.1.A ML/AI Embedded

Tuesday 11th June

11:30

Auditorium

# Real-Time Semantic Segmentation of Aerial Images Using an Embedded U-Net: A Comparison of CPU, GPU, and FPGA Workflows

Julien Posso\*, Hugo Kieffer<sup>†‡</sup>, Nicolas Menga<sup>†§</sup>, Omar Hlimi<sup>†</sup>, Sébastien Tarris<sup>†‡</sup>,

Hubert Guerard<sup>¶</sup>, Guy Bois\*<sup>¶</sup>, Matthieu Couderc<sup>†§</sup>, Eric Jenn<sup>†</sup>

\* École Polytechnique de Montréal

<sup>†</sup> IRT Saint Exupéry

<sup>‡</sup> Viveris Technologies

<sup>§</sup> Airbus Defence and Space

<sup>¶</sup> Space Codesign Systems

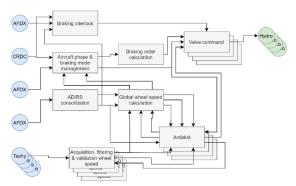

Abstract—This study introduces a lightweight U-Net model optimized for real-time semantic segmentation of aerial images, targeting the efficient utilization of Commercial Off-The-Shelf (COTS) embedded computing platforms. We maintain the accuracy of the U-Net on a real-world dataset while significantly reducing the model's parameters and Multiply-Accumulate (MAC) operations by a factor of 16. Our comprehensive analysis covers three hardware platforms (CPU, GPU, and FPGA) and five different toolchains (TVM, FINN, Vitis AI, TensorFlow GPU, and cuDNN), assessing each on metrics such as latency, power consumption, memory footprint, energy efficiency, and FPGA resource usage. The results highlight the trade-offs between these platforms and toolchains, with a particular focus on the practical deployment challenges in real-world applications. Our findings demonstrate that while the FPGA with Vitis AI emerges as the superior choice due to its performance, energy efficiency, and maturity, it requires specialized hardware knowledge, emphasizing the need for a balanced approach in selecting embedded computing solutions for semantic segmentation tasks.

Index Terms—Deep Learning, Neural Networks, Computer Vision, Semantic Segmentation, Inference, Embedded Systems, Aerospace, CPU, GPU, FPGA, MPSoC

#### I. INTRODUCTION

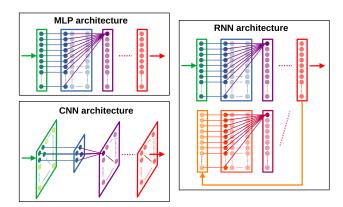

The advent of deep neural networks, especially Convolutional Neural Networks (CNNs), has revolutionized computer vision [13], introducing advanced capabilities for embedded systems in areas such as autonomous navigation [29] and earth observation [7], [16], [20]. Efficient hardware acceleration is vital for leveraging this technology, involving CPUs, GPUs, ASICs, FPGAs [27], and neural network compilers that bridge the gap between high-level Python libraries and hardware accelerators [5]. These topics have recently gained significant attention, as discussed in Section II. However, prior research has predominantly focused on image classification networks, specific hardware platforms, and compilers.

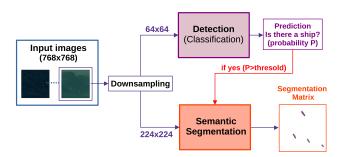

In this article, we present a pioneering, comprehensive, transversal study on the optimized implementation of image segmentation tasks for UAVs (Unmanned Aerial Vehicles) and satellites: specifically, the semantic segmentation of aerial images. We have enhanced a U-Net model for improved

embeddability, reducing its parameters and MAC (Multiply-Accumulate) operations by a factor of 16 while maintaining accuracy. We evaluate and compare five implementation schemes (workflows) across three COTS (Commercial Off-The-Shelf) embedded computing platforms (GPU, CPU, FPGA), assessing them using metrics such as IoU (Intersection over Union), accuracy, power, throughput, energy efficiency, and memory footprint. We also consider engineering metrics like workflow maturity, usability, documentation, and community support. This study addresses key practical challenges and provides valuable insights for those looking to integrate deep neural networks into real-world applications.

The structure of this paper is organized as follows: Section II reviews the literature pertinent to our research, providing foundational context. Section III details our computer vision task, specifically focusing on the semantic segmentation of aerial images using a lightweight U-Net to enhance its suitability for embedded systems. Section IV discusses the embedded computing platforms and examines the five workflows employed for implementing the neural network on these platforms. Section V synthesizes the main results, compares the workflows, and discusses the limitations of our study. Finally, Section VI summarizes the study, highlighting the effectiveness of the workflows and the suitability of the hardware selections for our specific application domain.

#### II. RELATED WORKS

The quest for hardware accelerators is crucial for enabling real-time neural network inference. Central to this acceleration are technologies such as CPUs, GPUs, ASICs, and FPGAs [27]. The role of compilers in bridging the gap between hardware capabilities and neural network performance is well-documented [5]. Additionally, there is a noticeable shift in the embedded sector towards the adoption of Commercial Off-The-Shelf (COTS) computers [24].

Zhao et al. [35] and Li et al. [14] meticulously review prevalent neural network compilers, including TVM, focusing

primarily on their optimization mechanisms and their impact on the speedup of state-of-the-art image classification networks. Xing et al. [33] provide an in-depth analysis of throughput, energy efficiency, and user-friendliness of six compilers, including TVM, aligning closely with our research. However, their analysis is confined to image classification networks such as ResNet50 and SqueezeNet, and they overlook potential quality degradation in neural network output due to the compilation and optimization processes.

Mittal et al. [18] provide a detailed survey of Nvidia Jetson GPUs within the context of embedded systems, including their application in semantic segmentation networks. Abdelouahab et al. [1] and Guo et al. [9] review designs for neural network accelerators, with a particular emphasis on enhancing FPGA inference within image classification networks. Reuther et al. [27] offer a comprehensive yet succinct survey of machine learning accelerators, focusing on performance and energy efficiency. Peccerillo et al. [26] examine approximately 100 accelerators, exploring their diverse workflows.

Comparative studies on FPGA and GPU inference performance and energy efficiency for standard image classification networks are detailed by Nurvitadhi et al. [22]. Feng [8] compares FPGA and GPU inference, focusing solely on semantic segmentation networks on GPUs, notably excluding FPGAs. Li et al. [15] highlight a performance comparison between FPGA and GPU inferences of binarized neural networks, revealing a trade-off between throughput and energy efficiency.

In the embedded domain, Dimitrovski et al. [7] review neural network architectures for aerial imagery, primarily focusing on image classification accuracy while neglecting real-time inference capabilities. Wang et al. [31] and Wu et al. [32] propose new neural network architectures for real-time semantic segmentation of aerial images, yet their deployment on embedded hardware remains unexplored. Moreover, existing research often limits its focus to single COTS platforms and toolchains for real-time inference [18], [30].

The literature exhibits significant limitations, predominantly focusing on image classification networks, which are less relevant for earth observation via UAVs and satellites. Furthermore, the research largely relies on benchmark datasets (e.g., ImageNet) and often restricts its experimental scope to single COTS platforms and toolchains. Studies encompassing multiple hardware targets or compilers are typically classified as surveys rather than experimental research.

In contrast, our research stands out due to its comprehensive approach in several key areas:

- A focus on semantic segmentation, an essential task for analyzing imagery from UAVs and satellites, diverging from the common focus on image classification.

- The adoption of a U-Net architecture for image segmentation, which includes both down-sampling (encoder) and up-sampling (decoder) paths, contrasting with the solely down-sampling nature of image classification networks. This approach exposes unique challenges in certain workflows that previous studies have not addressed.

- The utilization of the *Inria Aerial Image Labeling Dataset* for real-world applications, moving away from the conventional use of benchmark datasets like ImageNet.

- A comprehensive evaluation involving multiple workflows and hardware targets, providing a holistic view of their performance and limitations.

### III. EMBEDDABLE U-NET-BASED SEMANTIC SEGMENTATION OF AERIAL IMAGES

#### A. Semantic Segmentation of Aerial Images

Our research is situated within the context of earth observation, focusing primarily on two application domains: satellites and UAVs. These platforms are pivotal in acquiring high-resolution terrestrial imagery, offering spatial resolutions ranging from 0.2 to 10 meters, which are critical for numerous remote sensing applications [7], [16], [20]. The primary limitation lies in the downlink capacity, as satellites and UAVs lack the capability to transmit all captured images to ground stations. Consequently, on-board analysis becomes essential to ensure that only relevant data is transmitted to Earth, optimizing both bandwidth and data relevance [10].

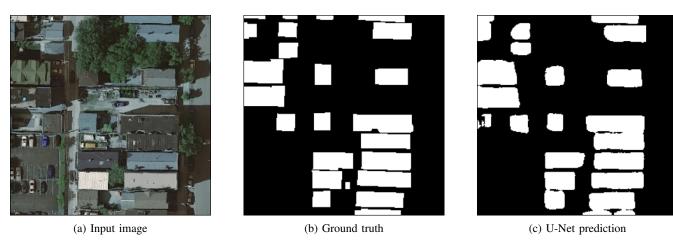

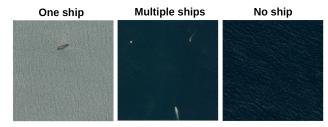

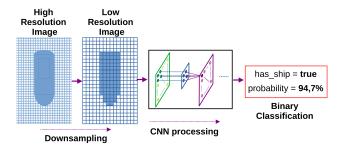

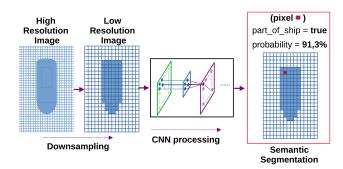

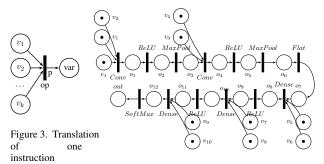

In this context, semantic segmentation is indispensable as it enables precise on-board analysis of the high-resolution imagery acquired by satellites and UAVs. We employ the Inria Aerial Image Labeling Dataset provided by Inria, renowned for its utility in benchmarking the generalization capabilities of semantic segmentation methodologies [17]. This dataset includes 180 colored satellite photographs, each measuring 5000x5000 pixels (25 Megapixels). The primary task of the dataset involves semantic segmentation, which entails classifying each pixel of an input image into a specific category; in our case, this means distinguishing every pixel as either 'building' or 'not building'. This classification results in a segmentation map. Figure 3 illustrates this process. To optimize for training and model embeddability, we dissect these images into smaller segments of 256x256 pixels, maintaining slight overlaps. These segments are subsequently merged to reconstruct the original 5000x5000 segmentation map postinference.

#### B. U-Net Architecture

We selected a U-Net architecture for our workflow comparison. The U-Net [28], initially proposed for biomedical image segmentation, has since become a widespread neural network architecture. It features a low number of parameters, a small memory footprint, and fewer MAC operations compared to other semantic segmentation networks, while still maintaining high accuracy. Additionally, it is designed to be trained with a limited amount of data, a common scenario in the embedded domain. These characteristics make the U-Net an ideal candidate for an embedded neural network.

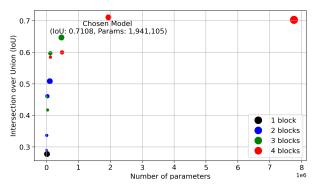

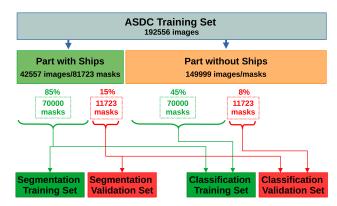

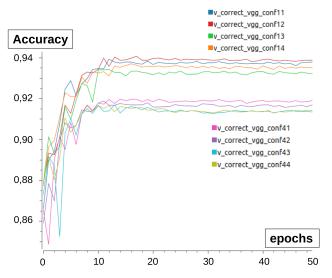

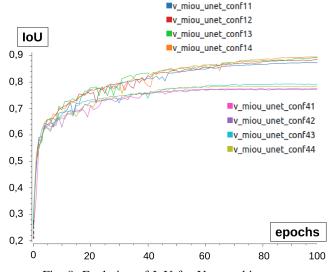

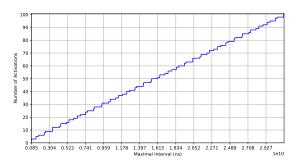

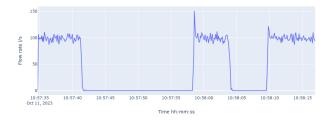

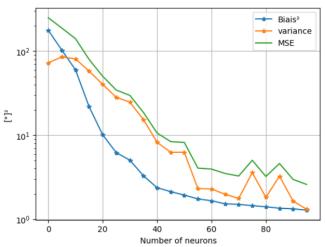

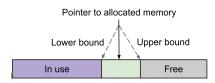

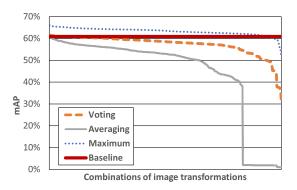

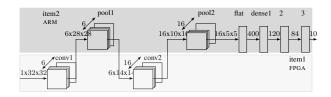

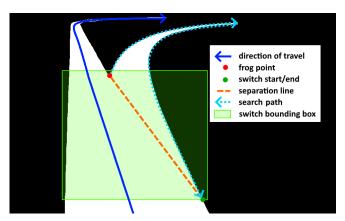

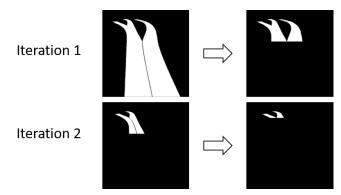

However, we modified the U-Net to enhance its embeddability. We trained multiple versions of the U-Net, varying the number of layers and channels per layer. Figure 1 demonstrates the necessity of this process in an embedded context. In the down-sampling path of the U-Net, each block contains two

convolutional layers and one max pooling layer. Similarly, in the up-sampling path, each block includes one transposed convolution and two convolutional layers. We adjusted the number of channels on each layer from 1/32 to 1/2 of the original U-Net and varied the number of blocks (*i.e.* the number of layers) from one to four, while maintaining symmetry between the down-sampling and up-sampling paths of the U-Net.

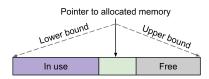

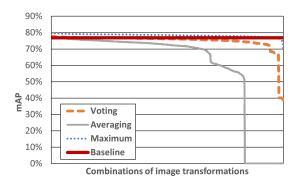

Fig. 1: IoU on the validation set vs. the number of parameters of the U-Net. Circle size represents the number of channels.

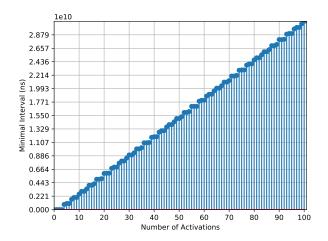

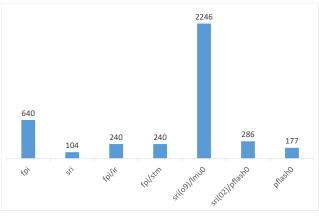

We preserved the core structure of the original U-Net, which consists of four blocks, but reduced the number of channels per layer to one-fourth of the original. This adjustment significantly decreased the number of parameters (from 31 million to 1.9 million) and MAC (Multiply-Accumulate) operations (from 55 billion to 3.4 billion) required to process a single 256x256 image, while still maintaining accuracy on the Inria Aerial Image Labeling Dataset. The number of parameters and MAC operations is proportional to the square of the number of channels, underscoring the importance of adapting neural network architectures to new datasets, especially in embedded contexts. Figure 2 provides a detailed view of the U-Net architecture, showing the distribution of MAC operations and the number of parameters across the down-sampling (encoder), middle, and up-sampling (decoder) paths. Notably, the two middle layers of the U-Net contain almost half of the parameters, while the majority of MAC operations occur in the up-sampling path. This path is crucial for reconstructing the feature maps back to the original image size, explaining the higher number of MAC operations required for accurately generating the output segmentation map. The inclusion of transposed convolutions in the up-sampling path, not present in state-of-the-art image classification neural networks, introduces unique challenges in some workflows.

#### C. Training Details

We trained our U-Net on an Nvidia RTX 3070 GPU, using Keras and TensorFlow 2.6, on the *Inria Aerial Image Labeling Dataset*, as detailed in Section III-A. Training began with random initial Float32 weights and utilized the Adam optimization algorithm [11] with TensorFlow's default parameters and a learning rate of  $1.0 \times 10^{-4}$  over 108 epochs. Training

was halted after 15 epochs without improvement in the Intersection over Union (IoU) computed on the validation set. We employed the Binary Cross Entropy (BCE) loss function, which is effective for binary segmentation tasks. To enhance the model's robustness and reduce sensitivity to overfitting, we normalized the input images to a range between 0 and 1 and applied data augmentation techniques using OpenCV 2.5. These techniques included random rotations (multiples of 90 degrees) and horizontal and vertical flipping.

#### D. U-Net Evaluation

Table I presents the evaluation of our lightweight U-Net, compared with the same data, task, and evaluation metrics used by the Inria team [17]: the IoU of the building class and pixel accuracy. The Inria team employed a FCN (Fully Convolutional Network) followed by a MLP (Multi-Layer Perceptron). Additionally, they discuss the general training process but lack in-depth technical specifics about the architecture configurations, such as the number of parameters and layers. Nevertheless, the evaluations demonstrate that our lightweight U-Net outperforms the Inria team's neural network. The lightweight U-Net serves as a baseline for evaluating the five workflows explored in this paper.

TABLE I: Evaluation metrics of our lightweight U-Net on the validation set

| Model                    | IoU    | Accuracy |

|--------------------------|--------|----------|

| Lightweight U-Net (ours) | 0.7108 | 0.9546   |

| FCN + MLP (Inria) [17]   | 0.6467 | 0.9442   |

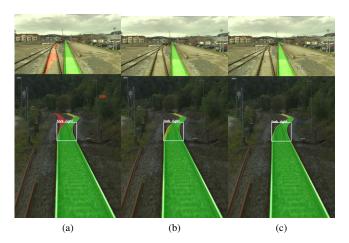

Figure 3 shows an example of our U-Net's prediction quality compared to the ground truth on a 256x256 image. The buildings are generally well-predicted by the neural network, even if the contours of the predicted buildings are somewhat blurred, a similar effect was noticed in the original Inria publication [17].

#### IV. PLATFORMS AND WORKFLOWS

#### A. Platforms for Real-Time Inference

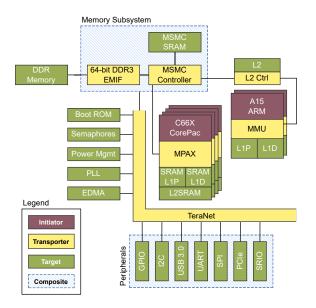

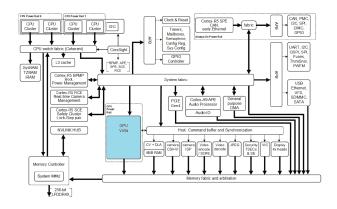

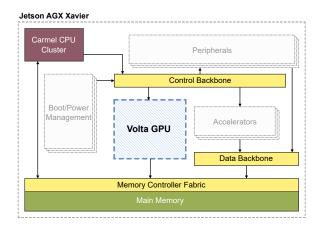

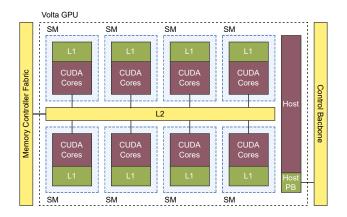

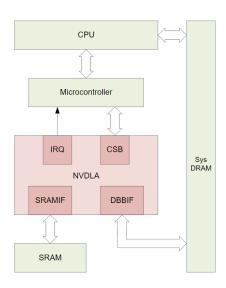

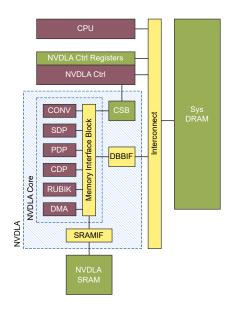

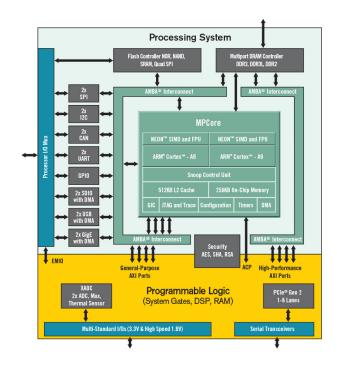

We selected two COTS platforms, specifically designed for embedded applications, to deploy our U-Net model. The Xilinx Zynq UltraScale+ MPSoC, equipped with four ARM Cortex-A53 processor cores and programmable logic (commonly referred to as an FPGA), has proven effective in both UAV [12] and space domains [24]. For our implementation, we utilized three Xilinx Zynq UltraScale+ boards—Ultra96, ZCU102, and ZCU104—each equipped with the same processor but featuring varying FPGA sizes, to host the hardware accelerators. Nvidia Jetson platforms have also emerged as strong contenders for real-time inference of neural networkbased vision algorithms, demonstrating applicability in UAV [30] and space domains [2]. Specifically, we employed the Nvidia Jetson AGX Xavier System on Module, which boasts eight ARM Cortex-A57 processor cores and an integrated GPU, enhancing the acceleration of neural network inference.

| Path     | Block                        | Layer type      | Input<br>channels | Output channels | Kernel<br>size | Output<br>width | Number of parameters | Number<br>of MAC<br>(million) | Number of parameters | Number<br>of MAC<br>(million) | Number of parameters (%) | Number<br>of MAC<br>(%) |

|----------|------------------------------|-----------------|-------------------|-----------------|----------------|-----------------|----------------------|-------------------------------|----------------------|-------------------------------|--------------------------|-------------------------|

|          | D4                           | Convolution     | 3                 | 16              | 3              | 256             | 448                  | 29.4                          |                      |                               |                          |                         |

|          | D1                           | Convolution     | 16                | 16              | 3              | 256             | 2,320                | 152.0                         |                      |                               |                          |                         |

|          | D2                           | Convolution     | 16                | 32              | 3              | 128             | 4,640                | 76.0                          |                      |                               |                          |                         |

| D        | D2                           | Convolution     | 32                | 32              | 3              | 128             | 9,248                | 151.5                         | 202 520              | 062.7                         | 15 10/                   | 25.00/                  |

| Down     | D3                           | Convolution     | 32                | 64              | 3              | 64              | 18,496               | 75.8                          | 293,520              | 862.7                         | 15.1%                    | 25.0%                   |

|          | D3                           | Convolution     | 64                | 64              | 3              | 64              | 36,928               | 151.3                         |                      |                               |                          |                         |

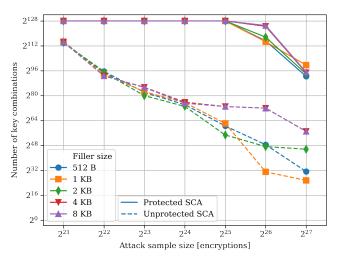

|          | D4                           | Convolution     | 64                | 128             | 3              | 32              | 73,856               | 75.6                          |                      |                               |                          |                         |

|          | υ4                           | Convolution     | 128               | 128             | 3              | 32              | 147,584              | 151.1                         |                      |                               |                          |                         |

| Middle   | M1                           | Convolution     | 128               | 256             | 3              | 16              | 295,168              | 75.6                          | 005 340 0            | 226.6                         | 45.6%                    | 6.6%                    |

| ivildale | IVII                         | Convolution     | 256               | 256             | 3              | 16              | 590,080              | 151.1                         | 885,248.0            | 226.6                         | 45.6%                    | 6.6%                    |

|          |                              | Transpose conv. | 256               | 128             | 2              | 32              | 131,200              | 134.3                         | -                    |                               |                          |                         |

|          | U1                           | Convolution     | 256               | 128             | 3              | 32              | 295,040              | 302.1                         |                      |                               |                          |                         |

|          |                              | Convolution     | 128               | 128             | 3              | 32              | 147,584              | 151.1                         |                      |                               |                          |                         |

|          |                              | Transpose conv. | 128               | 64              | 2              | 64              | 32,832               | 134.5                         |                      |                               |                          |                         |

|          | U2                           | Convolution     | 128               | 64              | 3              | 64              | 73,792               | 302.3                         |                      |                               |                          |                         |

| Up       |                              | Convolution     | 64                | 64              | 3              | 64              | 36,928               | 151.3                         | 762 220              | 2 25 4 7                      | 20.20/                   | 60.20/                  |

| Ор       |                              | Transpose conv. | 64                | 32              | 2              | 128             | 8,224                | 134.7                         | 762,320 2,354.7      | 39.3%                         | 68.3%                    |                         |

|          | U3                           | Convolution     | 64                | 32              | 3              | 128             | 18,464               | 302.5                         |                      |                               |                          |                         |

|          |                              | Convolution     | 32                | 32              | 3              | 128             | 9,248                | 151.5                         |                      |                               |                          |                         |

|          |                              | Transpose conv  | 32                | 16              | 2              | 256             | 2,064                | 135.3                         |                      |                               |                          |                         |

|          | U4                           | Convolution     | 32                | 16              | 3              | 256             | 4,624                | 303.0                         |                      |                               |                          |                         |

|          |                              | Convolution     | 16                | 16              | 3              | 256             | 2,320                | 152.0                         |                      |                               |                          |                         |

|          | Final convolution 16 1 1 256 |                 |                   | 256             | 17             | 1.1             | 17                   | 1.1                           | 0.0%                 | 0.0%                          |                          |                         |

|          | Total                        |                 |                   |                 | 1,941,105      | 3,445.2         | 1,941,105            | 3,445.2                       | 100.0%               | 100.0%                        |                          |                         |

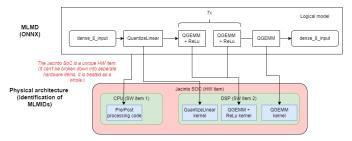

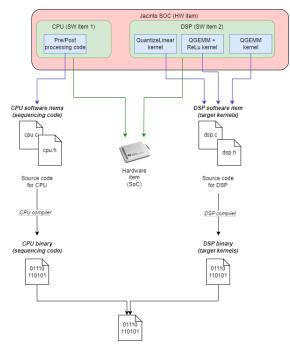

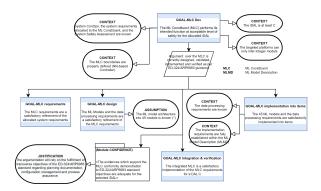

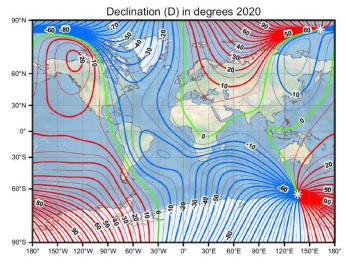

Fig. 2: Detailed architecture of the U-Net model

Fig. 3: Qualitative evaluation of our Float32 Keras lightweight U-Net on a 256x256 image of the validation set

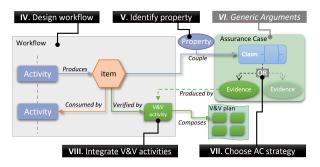

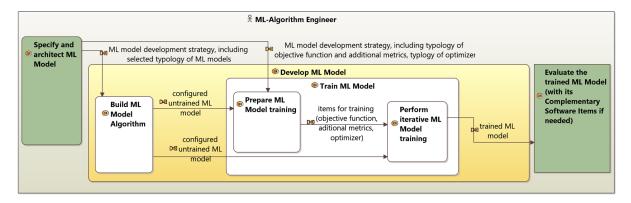

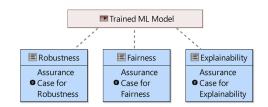

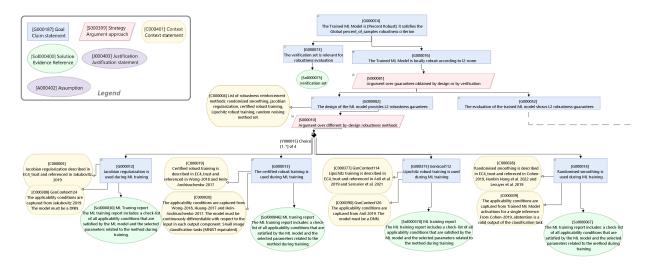

#### B. Workflows Overview

We evaluated various workflows to implement our U-Net on CPU, GPU, and FPGA platforms. On the GPU side, we first assessed the straightforward TensorFlow implementation, comparing it with the more complex but optimized Nvidia cuDNN library to understand the trade-offs between ease of use and performance. For the CPU, we utilized TVM, which is renowned for supporting major Python frameworks and offering the best speedup among neural network compilers [5], further enhanced by its auto-scheduling feature. For the

FPGA, we explored both the open-source FINN framework and Xilinx's commercial DPU within the Vitis-AI toolchain. Although Vitis-AI is considered more mature, FINN offers experimental yet highly optimized options for creating optimized dataflow implementations [3]. The following sections will delve into the details of each workflow.

#### C. GPU Implementation with TensorFlow

1) Workflow Overview: Figure 4 presents the workflow used to deploy our model on the Nvidia Jetson AGX Xavier

using TensorFlow 2.6. This workflow is straightforward, starting with the training of a Float32 model using Keras, serving as our baseline for evaluating GPU workflows. Notably, the model remains in Float32 format throughout, since quantization is only available in TensorFlow Lite. Our aim was to evaluate the most direct method for deploying a neural network on a Jetson GPU. Furthermore, the Jetson GPU efficiently processes Float32 operations on its CUDA (Compute Unified Device Architecture) cores. The trained model is exported in HDF5 format and then loaded onto the Nvidia Jetson AGX Xavier development kit. Onboard inference is conducted through a Python script, representing the simplest deployment method on the Nvidia Jetson platform, which operates on a Linux-based system with a Python stack, including Tensor-Flow.

Fig. 4: GPU workflow from Keras/TensorFlow training to Nvidia Jetson AGX Xavier inference using TensorFlow

2) Quantitative Evaluation: Table II presents the evaluation metrics measured on the validation set throughout the TensorFlow workflow. The first row shows the results following training with Keras and TensorFlow in a Float32 format. Subsequent rows detail these metrics when the model is deployed on an Nvidia Jetson AGX Xavier board. The consistency observed between the standard computing environment and the embedded deployment is expected because the underlying model remains unchanged between the training and deployment stages.

TABLE II: Evaluation metrics along the TensorFlow workflow

| Model                 | IoU    | Accuracy |

|-----------------------|--------|----------|

| Float32 Keras         | 0.7062 | 0.9594   |

| Jetson implementation | 0.7062 | 0.9594   |

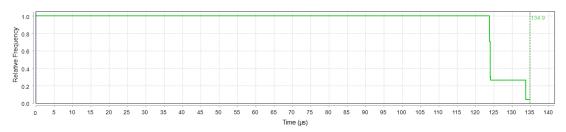

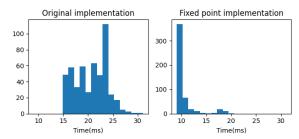

Table III summarizes the implementation metrics measured on the Jetson AGX Xavier. In this experiment, we varied the batch size to analyze its impact on the implementation metrics. Increasing the batch size to eight proved beneficial for improving throughput and energy efficiency while maintaining a reasonable memory footprint. The memory footprint includes the space needed for the model weights and activation functions, the batch of images, and additional Python libraries such as TensorFlow. Further increases in batch size did not yield significant benefits and resulted in an increased memory footprint, making a batch size of eight an optimal tradeoff. A batch size of one is deemed beneficial only when memory footprint or latency is prioritized over throughput or energy efficiency. During the experiments, we noticed some variability in execution time, particularly for the first inference. The first inference with a batch of eight images took 238

milliseconds, while the subsequent inferences averaged around 107 milliseconds (plus or minus 10 milliseconds). The table also reports the average throughput for the entire validation set. The observed variability was consistent across all batch sizes, highlighting the importance of also considering the Worst Case Execution Time (WCET) in embedded systems where it is a critical factor.

TABLE III: Implementation metrics on the Nvidia Jetson AGX Xavier with TensorFlow

| Batch<br>size | Throughput (FPS) | Power (W) | Energy<br>efficiency<br>(mJ/image) | Memory<br>(GB) |

|---------------|------------------|-----------|------------------------------------|----------------|

| 1             | 61.6             | 13.65     | 221.6                              | 1.7            |

| 8             | 74.6             | 14.56     | 195.2                              | 2.2            |

| 16            | 78.6             | 14.56     | 185.2                              | 5.05           |

| 32            | 75.8             | 14.56     | 192.1                              | 5.3            |

3) Qualitative Evaluation: The TensorFlow workflow targeting the Nvidia Jetson GPU is mature, straightforward, and well-documented, supported by an active community with numerous users, examples, and online tutorials. However, optimization of the neural network is limited within this framework. The high memory footprint presents significant concerns for embedded systems, which are often resource-limited compared to typical desktop or server environments. Furthermore, this high memory footprint could impact performance, energy efficiency, cost, and system stability, especially when the hardware is required to manage multiple applications simultaneously.

#### D. GPU Implementation with CuDNN

- 1) Workflow Overview: Figure 5 illustrates the workflow used to deploy our model on the Nvidia Jetson AGX Xavier utilizing the Nvidia cuDNN 8.4.1 library. Initially, we train a Float32 version of the model using Keras and export the trained parameters. Similar to the previous workflow, the model remains in Float32 format because quantization is only supported in TensorFlow Lite. The Jetson GPU is capable of efficiently processing Float32 operations on its CUDA cores. Subsequently, the neural network must be manually implemented in C++ with calls to the cuDNN library to execute operations on the GPU. The neural network is then cross-compiled for an ARM target using g++ and NVCC (Nvidia CUDA Compiler), resulting in an executable that is deployed on the Nvidia Jetson AGX Xavier, which operates a Linux-based system with the cuDNN library installed.

- 2) Quantitative Evaluation: During the evaluation, we encountered challenges, particularly due to the lack of a cuDNN implementation for the transposed convolution in the upsampling path of the U-Net, as well as for the nearest neighbor upsampling operation. A feasible solution could have been to implement these layers in a custom CUDA program; however, due to limited time and inadequate support on the Nvidia forum, this approach was not viable. We successfully implemented the down-sampling path and the middle convolution of the U-Net using cuDNN. The implementation's accuracy was

Fig. 5: GPU workflow from Keras/TensorFlow training to Nvidia Jetson AGX Xavier inference with cuDNN

validated by comparing the intermediate tensor outputs from the middle convolution produced by cuDNN with those from TensorFlow, finding them equivalent within an absolute tolerance of 1e-8. Thus, we conclude that the cuDNN workflow is unlikely to alter the evaluation metrics significantly.

Table IV presents the evaluation metrics measured on the validation set for the implemented down-sampling path and middle convolution of the U-Net using cuDNN. We estimated the full U-Net implementation performance by considering that the down-sampling path and middle convolutions comprise 31.6% of the MAC operations, and we scaled the measured latency accordingly to estimate the total latency. Similarly, since these components represent 60.7% of the parameters and intermediate feature maps, we adjusted the memory footprint to estimate the total memory usage. These estimates should be interpreted with caution.

TABLE IV: Measured and estimated implementation metrics on the Nvidia Jetson AGX Xavier with cuDNN

| Model                       | Latency<br>(ms) | Power (W) | Energy<br>efficiency<br>(mJ/image) | Memory<br>(MB) |

|-----------------------------|-----------------|-----------|------------------------------------|----------------|

| Partial U-Net<br>(measured) | 5.82            | 5.61      | 32.6                               | 795            |

| U-Net (esti-<br>mated)      | 18.4            | 5.61      | 103.3                              | 1310           |

3) Qualitative Evaluation: The cuDNN workflow for targeting Nvidia-embedded GPUs is mature yet intricate. cuDNN is primarily designed for developers of deep neural network (DNN) frameworks such as PyTorch or TensorFlow [4]. Consequently, it is more complex than other libraries and lacks extensive examples. Additionally, the absence of certain neural network layers necessitates a proficiency in CUDA programming, which is considerably more complex than using cuDNN alone. We also encountered discrepancies between the documentation and the actual implementation, which compounded the difficulty. The level of community activity is low; for instance, some queries on the Nvidia forums, particularly concerning transposed convolutions, have remained unanswered for over a year. While cuDNN is the optimal choice for achieving an optimized GPU implementation, especially where the memory footprint is a concern, this advantage requires a significantly greater development effort, particularly for neural networks that include layers not supported by the library.

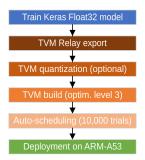

#### E. CPU Implementation with TVM

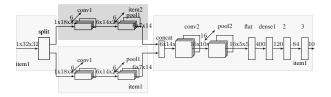

1) Workflow Overview: Figure 6 presents the workflow used to deploy our model on an ARM processor. We began by training a Float32 model with Keras, then utilized TVM 0.8 to export the model to Relay, TVM's intermediate graph representation. At this stage, quantization of the neural network is optional, which we discuss further in section IV-E2. We compiled the model using an optimization level of 3, which in our experiments achieved the best trade-off between optimization and neural network accuracy. Subsequently, we employed TVM's auto-scheduling, conducting 10,000 trials to optimize the scheduling of the inference on the CPU. The model was then ready for deployment on the ARM-A53 target, operating under a Linux-based system with the TVM runtime installed.

Fig. 6: CPU workflow from Keras/TensorFlow training to ARM CPU inference with TVM

2) Quantitative Evaluation: Table V shows the evaluation metrics obtained on a subset of the validation set, consisting of 1500 images, used in the TVM workflow, as the full validation set execution time was prohibitively slow on board. To ensure consistency, we maintained the same sub-validation set from the Keras evaluation through to the onboard evaluation. The table initially reports the metrics following Float32 training with Keras and TensorFlow. Subsequent rows display the metrics obtained when deploying the neural network on an Ultra96 board. The TVM workflow, without quantization, preserved the quality of the neural network's output. In further experiments, we quantized every weight and activation function to eight bits, except for the first convolutional layer. We found that post-training quantization with TVM had a negligible impact on the evaluation metrics, minimally affecting both IoU and accuracy.

TABLE V: Evaluation metrics along the TVM workflow

| Model         | IoU    | Accuracy |

|---------------|--------|----------|

| Float32 Keras | 0.7170 | 0.9546   |

| Float32 TVM   | 0.7170 | 0.9546   |

| Int8 TVM      | 0.7007 | 0.9518   |

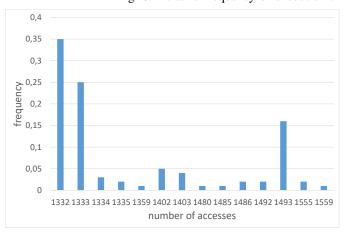

Table VI summarizes the performance metrics measured on the Ultra96 and ZCU104 boards. The ZCU104 demonstrated approximately ten percent faster execution than the Ultra96, attributable to its faster DDR memory. However, latency on both boards was significant, limiting real-time inference of semantic segmentation neural networks on these CPUs. Power consumption averaged 1.1W at thermal equilibrium, which is relatively low and was consistent across both boards and quantization levels, as the ARM cores were fully utilized under all conditions. Quantization increased the execution time threefold, possibly due to a bug in the version of TVM used, suggesting that the auto-scheduling functionality may not be fully compatible with the quantized version of our network. Energy efficiency was slightly better on the ZCU104, but the difference was minimal, except with the quantized version, which showed a significant increase. The memory footprint was reduced further with quantization.

TABLE VI: Implementation metrics on the Xilinx Zynq Ultrascale+ boards with TVM

| Board   | Quanti-<br>zation | Latency<br>(ms) | Power (W) | Energy<br>efficiency<br>(J/image) | Memory<br>(MB) |

|---------|-------------------|-----------------|-----------|-----------------------------------|----------------|

| Ultra96 | No                | 540.7           | 1.05      | 0.568                             | 68.4           |

| Ultra96 | Yes               | 1687            | 1.05      | 1.77                              | 39.5           |

| ZCU104  | No                | 489.2           | 1.11      | 0.543                             | 78.7           |

3) Qualitative Evaluation: The TVM workflow for targeting ARM CPUs is well-established, yet it is not without limitations, particularly due to a quantization bug encountered during our evaluations. This issue can be circumvented by utilizing the quantization functionalities of Keras/TensorFlow. The workflow benefits from being user-friendly, supported by extensive documentation and numerous examples. The versatility of the TVM stack allows for deployment on any ARM CPU that operates a Linux-based system, including smartphones and Raspberry Pi devices. Switching the target CPU requires altering only a single line of Python code. The community behind TVM is highly active, annually hosting TVMCon, a conference that fosters collaboration between academia and industry on neural network compilation. TVM's fully automated build and auto-scheduling processes facilitate the deployment and optimization of state-of-the-art convolutional neural networks, rendering the TVM workflow exceptionally adaptable.

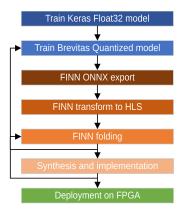

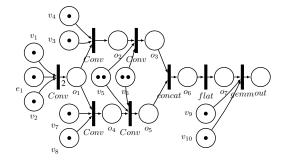

#### F. FPGA Implementation with FINN

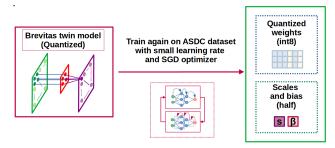

1) Workflow Overview: Figure 7 presents the workflow utilized to deploy our model on an FPGA using the FINN library. As FINN is incompatible with Keras or TensorFlow, we re-implemented the U-Net model using PyTorch 1.7.1 and Brevitas 0.6.1. Brevitas is a quantization library designed to facilitate Quantization Aware Training (QAT) with PyTorch and to support deployment through FINN [25]. Initially, we trained a Float32 version of the U-Net using Keras and exported the weights to the PyTorch/Brevitas version of the U-Net. We then proceeded with training a quantized version of the U-Net using QAT in PyTorch/Brevitas, starting from the Float32 weights to significantly reduce QAT duration. Brevitas

supports mixed-precision quantization, enabling layer-wise bitwidth parametrization for both weights and activation functions. After training, the model was exported to the ONNX format, which is compatible with FINN. At this stage, the model is transformed into a graph that contains only FINN HLS-compatible nodes. Subsequently, we defined the folding configuration for each graph node to set the parallelism, aiming to match the target latency without exceeding the FPGA's available resources. If the folding configuration exceeded the FPGA resources, it required returning to the bitwidth parametrization step and reiterating the QAT phase or adjusting the target latency. FINN's built-in functions facilitate the invocation of Vitis HLS to synthesize each node independently, integrate them, and then implement the combined solution as a Vivado 2022.1 project deployed on the FPGA. FINN also offers rapid prototyping capabilities using the Pynq library.

Fig. 7: FPGA workflow from PyTorch/Brevitas training to FPGA inference using FINN

2) Quantitative Evaluation: Table VII displays the evaluation metrics measured on the validation set throughout the FINN workflow. The initial row recalls the metrics after Float32 training with Keras. The final row presents the metrics for the quantized U-Net post-training, employing binary weights and 4-bit activation functions across all layers. Despite aggressive quantization, the accuracy and IoU only showed a slight decrease. Due to a suspected bug in the FINN library, we could not perform onboard inference to directly measure the evaluation metrics, a limitation we will discuss further in section IV-F3.

TABLE VII: Evaluation metrics along the FINN workflow

| Model              | IoU    | Accuracy |

|--------------------|--------|----------|

| Float32 Keras      | 0.7108 | 0.9531   |

| Quantized Brevitas | 0.6837 | 0.9488   |

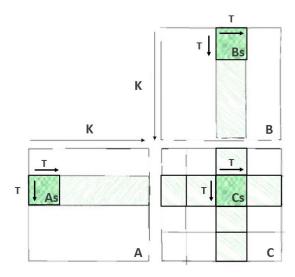

While onboard inference execution was not possible, we derived certain results from the Vivado project, synthesis, and implementation reports. Table VIII summarizes these findings and estimations. The latency was derived from the synthesis reports, considering the highest latency across all graph nodes

(786,432 cycles) as the accelerator's initiation interval. With a clock frequency of 100 MHz, we estimated the accelerator's latency to be 7.86 milliseconds, corresponding to a throughput of 127 images per second. The on-chip power consumption, estimated at 5.5 Watts, was obtained from the FINN-generated Vivado project. The estimated energy efficiency is noteworthy, given the implementation of a low-bit quantized U-Net, although these results are provisional and should be approached with caution.

TABLE VIII: Estimation of the implementation metrics on the Xilinx ZCU104 with the FINN workflow

| Board  | Throughput (FPS) | Power (W) | Energy<br>efficiency<br>(J/image) | Memory<br>(MB) |

|--------|------------------|-----------|-----------------------------------|----------------|

| ZCU104 | 127.2            | 5.46      | 0.043                             | N/A            |

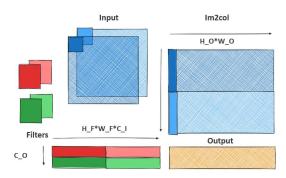

Table IX provides a summary of FPGA resource utilization based on the post-implementation report generated by Vivado, highlighting LUTs (Lookup Tables) as the primary limiting factor. The LUTs are predominantly utilized for the convolution computations, namely the im2col algorithm and the matrix-vector multiplication unit. Notably, the multi-threshold layers, representing the quantized activation functions, also consume a substantial number of LUTs, proportional to the square of the bit-width of the activation functions. We chose binary weights and 4-bit activations as an optimal balance between accuracy and estimated throughput. This approach also eliminated the need for DSPs, reducing the resource demands significantly. Our experience has shown that the FPGA resource estimations provided by FINN's Python script were found to be unreliable.

TABLE IX: FINN FPGA resource usage on ZCU104 board

| FPGA resource | Post-<br>implementation<br>utilization | FINN Python estimation | Available |

|---------------|----------------------------------------|------------------------|-----------|

| LUT           | 205,249 (89%)                          | 155,905                | 230,400   |

| LUTRAM        | 43,498 (43%)                           | Not Available          | 101,760   |

| Flip-Flop     | 235,448 (51%)                          | Not available          | 460,800   |

| BRAM          | 96 (31%)                               | 233                    | 312       |

| DSP           | 0 (0%)                                 | 0                      | 1,728     |

3) Qualitative Evaluation: The Brevitas library for training quantized neural networks targeting FINN implementations is mature and user-friendly, closely mimicking the PyTorch experience, albeit lacking in examples. Conversely, the FINN library is still under development. We encountered and locally fixed several source code bugs during our experiments. While some of these issues have been addressed recently, indicating active development, the community remains relatively small compared to other libraries. The absence of certain HLS backend templates, such as transposed convolution, posed challenges. We circumvented this by substituting with a nearest neighbor upsampling layer followed by a convolution, which did not alter the U-Net's parameter count or MAC operations.

Utilizing the FINN library can be challenging, particularly during the transformation phase, which requires users to

meticulously determine the appropriate transformations and their sequence. Often, modifications to the network architecture and quantization scheme are necessary to remove non-HLS compatible nodes. We had to develop two custom transformations not present in FINN to synthesize the U-Net effectively. A significant issue related to the U-Net's shortcuts prevented us from implementing the neural network on the FPGA. This issue could stem from a problem with our custom transformations, a bug in FINN's handling of concatenation layers, or FINN's algorithm not allocating sufficiently large FIFOs to store the activation functions of the down-sampling path, thereby hampering the up-sampling path's ability to perform its convolutions. Additionally, the documentation, spread across various websites and GitHub pages, is fragmented and challenging to navigate.

The FINN library holds significant potential for energy-constrained applications and is poised to mature into a highly energy-efficient method for executing neural network inference on FPGAs. As it develops, FINN's approach, with its capacity for mixed-precision quantization and configurable folding, will enable tailored optimization for each layer's bit-width, accuracy, resource usage, and latency.

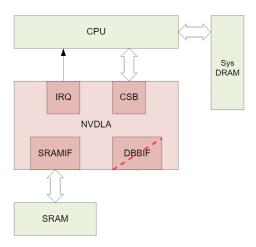

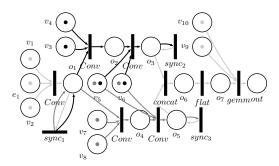

#### G. FPGA Implementation with Xilinx Vitis-AI

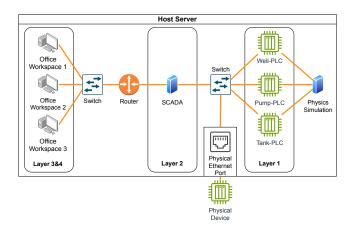

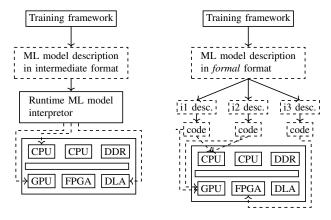

1) Workflow Overview: Figure 8 outlines the workflow used to deploy a neural network on a Xilinx Zynq Ultrascale+MPSoC using the Vitis-AI framework. This approach, distinct from rapid prototyping, is focused on actual embedded deployment. The process begins with training a Float32 model using Keras, followed by exporting it through the Vitis-AI toolkit version 2.0. Deployment on the MPSoC involves four primary activities:

- Configuring the DPU (Deep Learning Processor Unit) accelerator and generating the FPGA bitstream. This includes selecting the number of DPU cores and their size, which dictates the operations per clock cycle.

- Generating the application code in C++ to orchestrate model execution using the VART (Vitis AI Runtime).

- Compiling the model using 8-bit quantization with the Vitis-AI tools.

- Creating the Board Support Package (BSP) for the ZCU102 board.

Following these steps, the model is executed on the MPSoC, with the DPU on the FPGA handling most of the network operations. However, the CPU may process some layers, particularly when specific functions like the sigmoid activation at the end are not supported by the Vitis-AI quantization.

2) Quantitative Evaluation: Table X presents the evaluation metrics obtained from the validation set using the Vitis-AI workflow, with the initial line providing a baseline from Float32 training with Keras. Following the model's quantization to 8-bit using Vitis-AI, no loss in accuracy was observed, thanks to the toolkit's effective calibration function. The quantized model was subsequently deployed on the Xilinx DPU on the ZCU102 board, where no degradation in performance was noted, suggesting a possible regularization effect.

Fig. 8: FPGA workflow from Keras/TensorFlow training to FPGA/CPU inference using Vitis-AI

TABLE X: Evaluation metrics along the Vitis-AI workflow

| Model         | IoU    | Accuracy |

|---------------|--------|----------|

| Float32 Keras | 0.7108 | 0.9531   |

| Int8 Vitis    | 0.7156 | 0.9542   |

| Int8 DPU      | 0.7263 | 0.9583   |

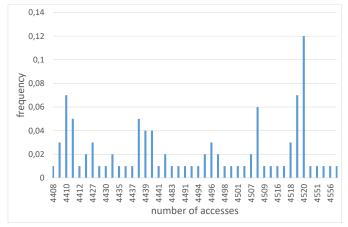

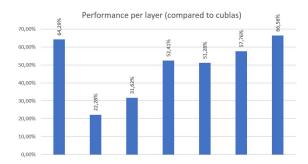

Table XI summarizes the implementation metrics on the Xilinx ZCU102 board, measured on the validation set. The configuration uses three DPU cores, each capable of 4096 operations per clock cycle at 100 MHz. This setup was determined to be the best trade-off for embedded inference, balancing throughput and power consumption for optimal energy efficiency.

TABLE XI: Implementation metrics on the Xilinx ZCU102 with the Vitis-AI workflow

| Board  | Throughput (FPS) | Power<br>(W) | Energy<br>efficiency<br>(J/image) | Peak mem-<br>ory (MB) |

|--------|------------------|--------------|-----------------------------------|-----------------------|

| ZCU102 | 46.9             | 2.51         | 53.5                              | 31                    |

Table XII shows the FPGA resource utilization, with DSPs and BRAMs being the primary limiting factors due to their roles in MAC operations and storage of weights and intermediate feature maps, respectively. LUTs, LUTRAMs, and Flip-Flops still have available capacity, providing potential for future increases in the size or number of DPU cores.

TABLE XII: Vitis-AI FPGA resource usage with 3-core DPU on ZCU102 board

| FPGA resource | Post-implementation utilization | Available   |

|---------------|---------------------------------|-------------|

| LUT           | 133,425 (49%)                   | 274.080     |

| LUTRAM        | 17,027 (12%)                    | 144.000     |

|               | 1 ` ` ′                         | , , , , , , |

| Flip-Flop     | 297,576 (54%)                   | 548,160     |

| BRAM          | 771 (84%)                       | 912         |

| DSP           | 2,070 (82%)                     | 2520        |

3) Qualitative Evaluation: The Vitis-AI workflow is robust, demonstrating significant maturity, particularly with toolchain updates in versions 2.0 and 2.5 that resolved previously encountered bugs. This versatile workflow supports a wide array of neural network layers, and users can incorporate custom IP blocks to introduce new operations. Xilinx provides comprehensive documentation and end-to-end examples through the Vitis-AI Model Zoo. The community surrounding Vitis-AI has grown rapidly, although the learning curve remains steep

due to the complexity of integrating various components such as BSP, Vivado, PetaLinux, and Vitis-AI tools. Additionally, while most components of Vitis AI are open source, some elements, such as the Vitis AI Compiler, remain proprietary, and certain tools within the Xilinx ecosystem require a commercial license.

#### V. SYNTHESIS

#### A. Synthesis and Workflow Comparison

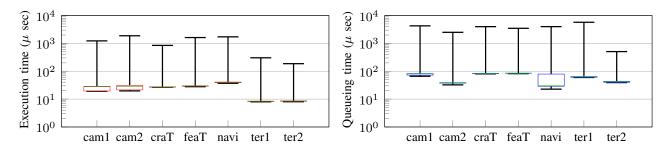

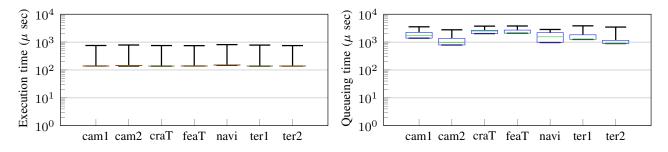

Table XIII synthesizes the evaluation and implementation metrics results across the five workflows. As discussed in Section IV, onboard implementation was not achievable for the cuDNN and FINN workflows. Consequently, the implementation results from these workflows are estimates and should be interpreted with caution. Quantization is employed only when the hardware target does not support Float32 operations. The CPU and GPU workflows maintain the neural network's output quality, thus achieving the same accuracy and Intersection over Union (IoU) as their respective baselines. The FINN workflow causes a slight degradation in accuracy and IoU, which is minimal considering the use of low-bit quantization. Conversely, the Vitis-AI workflow marginally improves the evaluation metrics on the validation set due to its quantization and calibration mechanisms, introducing a regularization effect. All workflows are compared at isoaccuracy levels. Nevertheless, there are significant differences in throughput and power consumption across the platforms and workflows. As expected, the CPU exhibits the lowest throughput, resulting in poor energy efficiency. The FPGA workflows, utilizing FINN or Vitis-AI, demonstrate superior energy efficiency. Both FINN and Vitis-AI enable the creation of customizable neural network accelerators, allowing for tailored FPGA resource usage, which in turn affects throughput and power consumption. Additionally, the use of quantization contributes to reduced power consumption. In contrast, GPU workflows and platforms have a considerably higher memory footprint compared to CPU and FPGA workflows and targets, presenting potential challenges in an embedded context.

Table XIV synthesizes the engineering metrics across the five workflows. Overall, TensorFlow and TVM stand out in the comparison. Both are open-source, mature, user-friendly, well-documented, and supported by large, active communities. Close behind, the Vitis-AI workflow exhibits similar positive attributes but is more challenging to use due to its incorporation of proprietary components and a requirement for hardware engineering expertise. Nevertheless, it offers greater customization capabilities than the TVM and TensorFlow workflows. The post-training 8-bit quantization in Vitis-AI, while adding complexity and development time, enhances energy efficiency. The cuDNN workflow is primarily designed for developers of deep neural network frameworks, such as PyTorch and TensorFlow, reflecting its maturity but also its limited suitability for embedded inference. Furthermore, the absence of certain operators, like transposed convolution and nearest neighbor upsampling, necessitates intricate and laborintensive development. At the bottom of our comparison is

TABLE XIII: Synthesis of the evaluation and implementation metrics of the five workflows

| Platform                       | Nvidia GPU |         | Xilin     | + MPSoC     |                 |

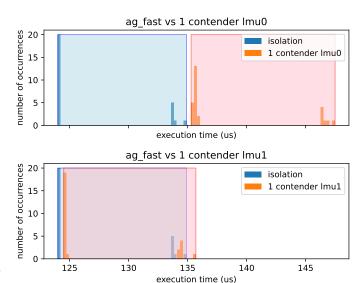

|--------------------------------|------------|---------|-----------|-------------|-----------------|

| Board                          | Jetson AGX | Xavier  | ZC        | U104        | ZCU102          |

| Workflow                       | TensorFlow | cuDNN   | TVM (CPU) | FINN (FPGA) | Vitis-AI (FPGA) |

| Implementation                 | Yes        | No      | Yes       | No          | Yes             |

| Numeric precision              | Float32    | Float32 | Float32   | W1A4        | Int8            |

| Accuracy change (vs. baseline) | 0%         | 0%      | 0%        | -0.43%      | +0.52%          |

| IoU change (vs. baseline)      | 0          | 0       | 0         | -0.0271     | +0.0155         |

| Throughput (FPS)               | 74.6       | 54.3    | 2.04      | 127         | 46.9            |

| Power (W)                      | 14.6       | 5.61    | 1.11      | 5.46        | 2.51            |

| Energy efficiency (mJ/image)   | 195        | 103     | 543       | 43.0        | 53.5            |

| Memory (MB)                    | 2200       | 1310    | 78.70     | N/A         | 31              |

TABLE XIV: Synthesis of the engineering metrics of the five workflows. Metrics are quantified as high, medium, and low.

| Platform                   | Nvidia Jetson AGX GPU |        | Xilinx Zynq UltraScale+ MPSoC |             |                 |

|----------------------------|-----------------------|--------|-------------------------------|-------------|-----------------|

| Workflow                   | TensorFlow            | cuDNN  | TVM (CPU)                     | FINN (FPGA) | Vitis-AI (FPGA) |

| Maturity                   | High                  | High   | High                          | Low         | High            |

| Ease of Use                | High                  | Low    | High                          | Low         | Medium          |

| Documentation and Examples | High                  | Medium | High                          | Medium      | High            |

| Community Support          | High                  | Low    | High                          | Low         | High            |

the FINN workflow. Its current maturity level is low, with identified bugs, and it presents significant usability challenges. The need to develop custom transformations not available in the FINN library further complicates its usage. Although the community is active, it is relatively small compared to the others. Documentation and examples exist but are dispersed across various websites and GitHub repositories, which complicates the comprehension process. Additionally, FINN's lack of support for certain operators, such as transposed convolution, necessitates alterations in the neural network architecture.

#### B. Limitations and Future Works

The conclusions presented in this paper reflect observations from 2021 to 2023. Nevertheless, the field of neural networks is rapidly evolving, and significant changes in these frameworks are anticipated in the near future. For instance, during the course of our project, we observed maturation in both the FINN and Vitis-AI workflows.

On the GPU front, our research focused on the high-level TensorFlow and the low-level cuDNN workflows. Nvidia's TensorRT, an intermediate, open-source workflow for DNN inference, represents a potential area for future research [23]. Future investigations should also explore quantization to fully leverage the capabilities of Nvidia's Tensor Cores in embedded GPUs, potentially narrowing the energy efficiency gap with FPGAs.

Further research should evaluate the use of more powerful CPUs, such as those based on Intel x86 architectures, with compilers like TVM or Intel nGraph that have shown effectiveness on these processors [14]. Due to time constraints, this study did not explore ASICs for neural network inference, such as Google's Edge TPU or Intel's Movidius VPUs [27], which appear to be promising for embedded applications and warrant future evaluation.

Lastly, the embedded domain poses unique challenges regarding robustness and explainability, aspects not covered in this paper. These topics are currently active research areas

in both academic [21], [34] and industrial spheres [6], [19], deserving attention in future studies.

#### VI. CONCLUSION

This paper has demonstrated the necessity of adapting advanced neural network architectures to novel datasets within an embedded framework. We introduced a lightweight U-Net that achieves the same accuracy with 16 times fewer parameters and Multiply-Accumulate (MAC) operations, validated on an aerial image segmentation dataset [17]. Furthermore, this study provided an extensive evaluation and comparison of various methods for real-time semantic segmentation of aerial images, employing three contemporary Commercial Off-The-Shelf (COTS) embedded computers across five distinct workflows.

The FPGA target, utilizing Vitis-AI, emerged as the superior choice due to its performance, energy efficiency, and system maturity. However, its implementation necessitates specialized hardware expertise. The ARM CPU target, leveraging TVM, is notable for its user-friendliness and maturity, yet its relatively low energy efficiency and throughput pose significant challenges for embedded system applications. The GPU target, utilizing TensorFlow, is acknowledged for its maturity and ease of use but is more appropriate for rapid prototyping than for actual embedded solutions. Conversely, the GPU target employing cuDNN is better aligned with embedded deployment but suffers from complexity and a lack of support for various neural network layers. Lastly, the FPGA target using FINN shows high potential for energy-constrained applications but necessitates additional development to become a practical option.

#### VII. ACKNOWLEDGEMENTS

This work was conducted within the SPOC project at the French Institute of Technology (IRT) Saint Exupéry. Funding was provided by the French Research Agency (ANR) and by the industrial partners of the IRT Scientific Cooperation Foundation (FCS).

#### REFERENCES

- K. Abdelouahab, M. Pelcat, J. Serot, and F. Berry. Accelerating CNN inference on FPGAs: A Survey, May 2018. arXiv:1806.01683 [cs].

- [2] C. Adams, A. Spain, J. Parker, M. Hevert, J. Roach, and D. Cotten. Towards an Integrated GPU Accelerated SoC as a Flight Computer for Small Satellites. In 2019 IEEE Aerospace Conference, pages 1–7, Mar. 2019. ISSN: 1095-323X.

- [3] M. Blott, T. B. Preußer, N. J. Fraser, G. Gambardella, K. O'brien, Y. Umuroglu, M. Leeser, and K. Vissers. FINN- R: An End-to-End Deep-Learning Framework for Fast Exploration of Quantized Neural Networks. ACM Transactions on Reconfigurable Technology and Systems, 11(3):1–23. Dec. 2018.

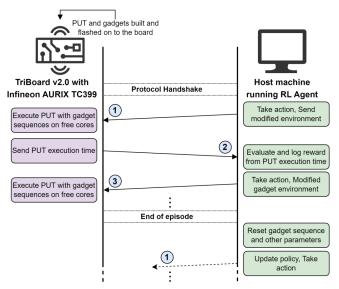

- [4] L. Brown. Accelerate Machine Learning with the cuDNN Deep Neural Network Library, Sept. 2014.