## Engineering Thin HZO Ferroelectric Layers: From Material Study to 3D Integration for Vertical Gate-All-Around FeFETs

K. Moustakas<sup>1\*</sup>, L. Cancellara<sup>1</sup>, N. Pezzato<sup>1</sup>, A. Lecestre<sup>1</sup>, T. Mikolaijk<sup>3</sup>, J.Trommer<sup>2</sup>, G.Larrieu<sup>1</sup>

<sup>1</sup>Laboratory For Analysis And Architecture Of Systems (LAAS -CNRS) – Toulouse (France) <sup>2</sup> Namlab gGmbH - Dresden (Germany) <sup>2</sup> Technische Universität (TU), Chair for Nanoelectronics - Dresden (Germany)

The demand for higher computational efficiency and lower energy consumption in semiconductor devices has led to the exploration of non-traditional computing architectures. One promising direction is the integration of logic and memory into a single device or cell, potentially overcoming the limitations of the Von Neumann architecture. This paradigm is now within reach thanks to the introduction of CMOS compatible ferroelectric materials, such as hafnium oxide (HfO<sub>2</sub>), known for its reversible residual polarization under the effect of external electric fields[1].

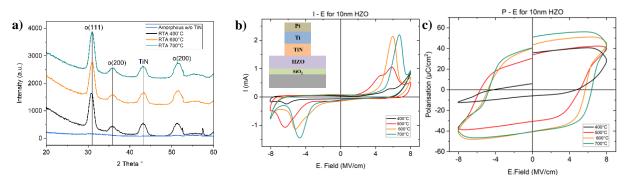

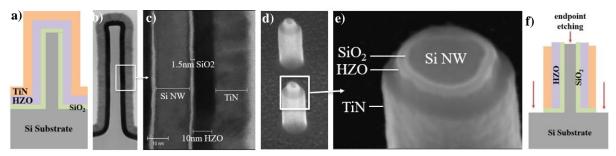

This study presents a thorough investigation of the Hf-Zr (Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> - HZO) layer and the subsequent steps towards its integration into 3D gate-all-around devices [2], currently targeted for the next technology nodes in logic architecture. Fig.1 shows planar MIS devices, with a 10nm HZO layer, that display through GIXRD the successful crystallization of HZO with annealing temperatures starting as low as 400°C. The ferroelectricity and thus the orthorhombic crystalline phase of HZO is verified through pulsed electrical measurements which exhibit a robust (P-E) hysteresis loop. Integration on vertical nanostructured channels has been successfully demonstrated (Fig. 2) with a perfect conformity of the layer. In a 3D nanoscale configuration, identifying the proper ferroelectric phase with classical approaches (such as GIXRD) used in planar structures is not feasible. So, we developed a novel approach that couples 4DSTEM imaging and python based data processing to perform a full mapping of the grains and crystalline phases of our HZO layer.

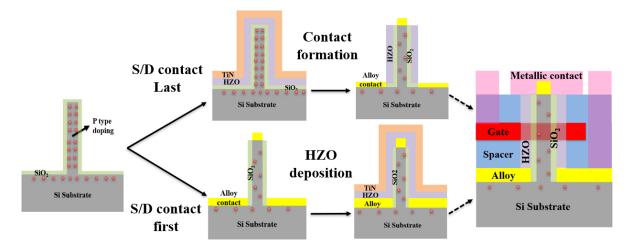

Furthermore, we investigate the challenges related to integrating the HZO layer into 3D nanostructures, particularly selective and anisotropic etching steps, to maintain the integrity of the HZO layer (see Fig. 2). This ensures the removal of unwanted layers from our nanostructures while preserving the surrounding HZO layer, facilitating the subsequent formation of alloy contacts. Additionally, considering the opportunities and possible limitations of fabrication parameters, we explore different process routes in parallel (S/D contact first/last) for the 3D integration of HZO in gate all-around FeFETs (see Fig. 3), discussing the pros and cons of each configuration (metallurgy stability of the contacts, doping segregation at the interfaces etc).

## References

[1] T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, *Applied physics letters*, vol. 99, no. 10, pp. 102903-102903–3, 2011, doi: 10.1063/1.3634052.

[2] Y. Guerfi and G. Larrieu, Nanoscale research letters, vol. 11, no. 1, pp. 210–210, 2016, doi: 10.1186/s11671-016-1396-7.

<sup>\*</sup> Corresponding author: email: <u>kmoustakas@laas.fr</u> / glarrieu@laas.fr

Figure 1: (a) GIXRD verification of the crystalline nature and identification of the orthorhombic phase on our planar samples. The electrical measurements were conducted on a stack of 1.5nm of SiO<sub>2</sub> on Si substrate followed by 10nm of HZO, 13nm of TiN and a total of 35 nm of Ti/Pt as top contact. Results of I vs  $E_{field}$  (b) and P vs  $E_{field}$  (c) demonstrate the evolution of polarization and Ec for different HZO activation annealing temperatures.

Figure 2 : (a)Schematic of the vertical HZO/TiN deposition. (b) TEM from vertical nanowire with crystalized SiO2/HZO/TiN multistack with a (c) zoomed view on the critical sidewall. (d)birds view SEM plasma etched vertical nanowires where TiN/HZO have been removed from (e) top and bottom with the corresponding 2D sketch(f)

Figure 3 : The two different fabrication approaches process flow of a Vertical Nanowire GAA FeFET (S/D contact first/last). The red dotes demonstrate the p type doping. The stabilization and integrity of the formation of the alloy contact is critical in order to ensure good electrical properties of the transistor.

This work was supported by European Union's H2020 program through the FVLLMONTI project (No101016776) and the Renatech French national network