# HIGH VOLTAGE AND SPECIFIC POWER SILICON CARBIDE DEVICES

Dominique Planson, Marie-Laure Locatelli, Mihai Lazar, Christophe Raynaud, Jean-Pierre Chante, Pierre Brosselard, Samir Zelmat, D. Tournier

# ▶ To cite this version:

Dominique Planson, Marie-Laure Locatelli, Mihai Lazar, Christophe Raynaud, Jean-Pierre Chante, et al.. HIGH VOLTAGE AND SPECIFIC POWER SILICON CARBIDE DEVICES. 10ème colloque Electronique de Puissance du Futur, Sep 2004, Toulouse, France. hal-04621819

# HAL Id: hal-04621819 https://hal.science/hal-04621819v1

Submitted on 24 Jun 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### HIGH VOLTAGE AND SPECIFIC POWER SILICON CARBIDE DEVICES

D. Planson<sup>1</sup>, M.L. Locatelli<sup>2</sup>, M. Lazar<sup>1</sup>, C. Raynaud<sup>1</sup>, J.P. Chante<sup>1</sup>, P. Brosselard<sup>1</sup>, S. Zelmat<sup>2</sup>, D. Tournier<sup>3</sup>

<sup>1</sup>CEGELY, INSA de Lyon, Bât. L. De Vinci, 69621 Villeurbanne Cedex <sup>2</sup>LGET, Université Paul Sabatier, 31062 Toulouse Cedex <sup>3</sup>CNM/Barcelona. ES-08193 Bellaterra. Spain

Corresponding author: dominique.planson@insa-lyon.fr Tel: 04 72 43 87 24, Fax: 04 72 43 85 30

#### **ABSTRACT**

High voltage bipolar diodes with a single periphery protection by JTE (Junction Termination Extension) have been realised and show breakdown voltages as high as 4.8 kV. Optical Beam Induced Current (OBIC) measurements have shown that the JTE are efficient. Thyristors with breakover voltage ~3.9 kV have been fabricated. In both case, the performance of the structures are limited by the dielectric rigidity of the ambient environment. Specific component have also been realised. i) current fault limiter have been able to block 800 V; ii) SiCOI Schottky diodes and MESFET have been processed, which is a first step towards integrated power systems.

#### 1. INTRODUCTION

Thanks to its excellent physical properties, SiC will make a breakthrough in power and high temperature electronics in the near future. 1200 V/ 10 A SiC Schottky diodes are already in the market, and samples of high voltage 1200 V JFET are now commercially available [1]. Numerous demonstrators of SiC devices have been realised in lab, and only the high voltage components are now reviewed, a 19 kV SiC bipolar diode [2], a 7 kV thyristor [3], 5.5 kV JFET [4] and 10 kV MOSFET [5].

The aim of this paper is to show the results obtained at CEGELY for Silicon Carbide power devices. Results are divided in three parts: high voltage bipolar diodes, high voltage switches (thyristor and JFET) and finally specific devices. Specific devices (current limiter and SiCOI Schottky diode) appear like a new research activity during the last four years. Interesting results give evidence of the good properties of SiC (even for 600 V applications). Our results will be compared with published data.

LGET laboratory is in charge of the study for dielectric materials used to passivate and insulate the SiC dies. These components must sustain higher electric field constraints than Si ones, and also higher temperatures (up to 350°C). The work of LGET consists in defining the theoretical features of optimised materials, and in the characterisation

of commercially available materials that are potential candidates for passivation.

#### 2. HIGH VOLTAGE BIPOLAR DIODES

This aim of this study is to show potentialities of silicon carbide for high voltage power systems. Test vehicles are SiC bipolar diodes able to sustain 1.3 kV and 5 kV. Emitter and periphery protection (JTE) are realised by ion implantation of Aluminium in epitaxial n-type layer grown on commercial substrate.

The efficiency of the diodes with respect to the breakdown voltage ( $V_{br}$ ) is defined as the ratio of device  $V_{br}$  on the theoretical  $V_{br}$ . The number of devices, which exhibit efficiency > 84% has been improved during the last four years. Indeed, 70 % of the diodes 1.3 kV with an implanted emitter at 300°C exhibit a breakdown voltage higher than 1100 V (up to 1300 V) (anode diameter 160  $\mu$ m) and long JTE length (120  $\mu$ m) without any impact of the ambient (air or SF<sub>6</sub> gas or dielectric liquid). The ambient impacts breakdown voltage only for diodes with short JTE length (50  $\mu$ m) [6].

OBIC set-up [7] allows experimental analysis at room temperature for the efficiency of periphery protections.

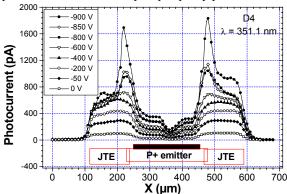

Figure 1 : OBIC measurements realised on  $p^+n$  diode for different reverse biases. (Emitter diameter  $\emptyset=250~\mu m$ , JTE length = 120  $\mu m$ ).

As an example, Fig. 1 shows OBIC analysis on 1.3 kV JTE diodes. For low voltage (<600 V), optical currents stretch over the total JTE length. For higher voltage, a peak appears at the edge of the emitter. At 900 V, a peak seems to appear at the edge of JTE. This proves that JTE are efficient. According to the simulations results, it means that doping level of JTE is slightly too small with respect to the optimal value for this structure (epitaxial layer thickness 10  $\mu$ m, doping level  $10^{16}$  cm<sup>-3</sup>).

These results show in the same time that post-implantation annealing realised in our furnace [8] allows a full activation of dopants in JTE. In forward state, current densities and efficiency have been improved (200 A/cm² @ 5 V at room temperature) also due to the improvement of metallisation step and succeeding annealing at IMM Bologne [9]. Results of good ohmic contacts on highly doped P<sup>+</sup> zones are comparable with other results given in literature.

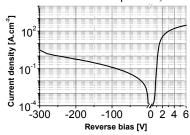

Fig 2: Reverse I-V characteristics of 5 kV bipolar diodes measured in three different ambients: air, galden® and  $SF_6$ . Active area = 0.05 mm<sup>2</sup>.

As it can be observed in Fig. 2, CEGELY is now able to present results of breakdown voltage in the range of 4 kV, with a maximum of 4.8 kV with low reverse current density in fluoride ambient (Galden® and SF<sub>6</sub>) [10]. Without passivation, breakdown voltage is only 1.3 kV for these devices with a JTE length of 250  $\mu$ m (optimised with respect to the semiconductor properties). This clearly proves the need to passivate in order to fully take benefit of SiC properties for high voltage applications.

Theoretical interest to use passivation materials with high dielectric permittivity ( $\epsilon$ ) in order to reduce electric field outside SiC have been shown using simulation software MEDICI on bipolar 5 kV diode protected by JTE. For a given structure, only a sufficiently high  $\epsilon$  value allows to reduce electric field peaks both at emitter and JTE borders, by stretching space charge region outside the JTE [11]. Another advantage to use a high  $\epsilon$  material is to significantly

reduce the sensitivity on breakdown voltage with respect to the optimal dose of JTE. From the technological point of view, choice of such material (with high  $\epsilon$ ) and a compatible deposition method remain to be solved before obtaining experimental results.

Among available and practical insulating materials, polyimide materials specifications exhibit good dielectric together with good thermal properties under usual conditions. Thus an experimental characterisation using MIM and MIS structures has been launched in order to quantify their effective characteristics within an extended temperature range. For high voltage (up to 50 kV) and high temperature (up to 500°C) measurements, a specific set-up has to be developed [11].

#### 3. HIGH VOLTAGE SWITCHES

#### 3.1 Thyristor (5 kV breakdown voltage)

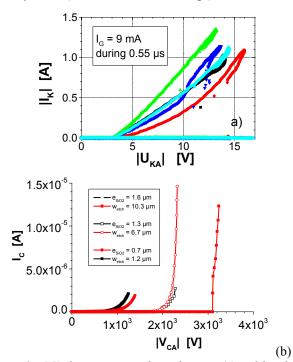

Figure 3: I-V characteristics of switching on (a) and breakover voltage in forward blocking mode (b). Active device surface is 0.25 mm<sup>2</sup>.

A first step allowed to define the features of the four layers, required to realise a thyristor able to sustain a forward blocking voltage of 5 kV [12]. Electrothermal simulations show that the structure can deliver one-shot of very high current pulse of 1 ms. Then main effort was concentrated on periphery protection using several types: MESA, Etched Guard Rings (EGR) and a combination of MESA and JTE [13]. All kind of structures were realised in collaboration either with IBS society or with Institute Saint Louis. In any case, the P<sup>-</sup> type epilayer is 35 μm thick with a doping of 5×10<sup>14</sup> cm<sup>-3</sup> and SiO<sub>2</sub> layer is used as passivation layer. Both kinds of electrical characterisations have been performed with our probe station: forward blocking state and switching-on triggered from AC.

Breakover voltage ( $V_{bo}$ ) was obtained in the 3.4-3.9 kV range (efficiency 56-66%) by testing in Galden<sup>®</sup>. The higher value 3.9 kV is obtained for the devices with mesa structure with the highest etching depth and the thickest oxide layer. In the mesa-JTE structure the lower  $V_{bo}$  (a maximum of 3.5 kV) is compensated by a more homogeneous distribution on the whole wafer of the devices with a  $V_{bo}$  greater than 3kV. Like for the bipolar diodes, the  $V_{bo}$  value seems to be limited by the dielectric rigidity of the ambient environment, that is not adapted to device structures that were optimised only for the SiC.

#### 3.2 JFET Transistor (8 kV breakdown voltage)

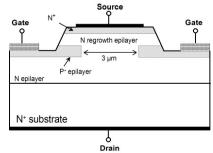

Theoretically less suitable than the thyristors to support high energies, unipolar devices should be able to deliver higher di/dt but with higher voltage drop. All geometrical and technological parameters of the JFET have been optimised for 8 kV taking into account technological feasibility at CEA/LETI. Cross sectional view of the structure is presented in Fig 4. The thick and low doped n-type layer (60  $\mu m$  /  $8\times10^{14}$  cm $^{-3}$ ) is responsible for the high Vbr. Considerable efforts were focused on epilayer growths. Moreover, the small width of the channel (3  $\mu m$ ) implies a delicate epitaxial regrowth of n-type layer between the walls formed by RIE in the p-type layer.

Fig 4: cross-section of the 8 kV VJFET transistor.

#### 4. SPECIFIC DEVICES

### 4.1 Fault current limiter for serial protection application

As the 600 V Schottky diode (first SiC device commercially available in 2000), a fault current limiter for domestic applications presents a real commercial impact, because the target market is large and silicon devices can not challenge in this field (due to their strong thermal limitation).

Two different structures, based on vertical JFET, have been designed by CEGELY, and realised with CNM. First experimental characterisations have validated the basic principle of the current limitation. Current density of 800  $A.\mbox{cm}^{-2}$  was demonstrated under 30 V, with a serial resistance of only 14  $m\Omega.\mbox{cm}^2$  for  $V_{br}$  of 600 V [14].

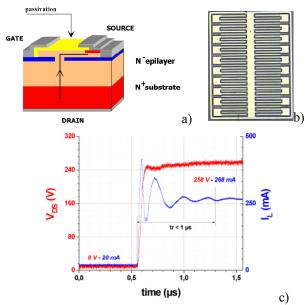

The second structure [15] was improved with an extra gate electrode described in Figure 5 a-b. This three terminals device allows to control the fault limited current, aiming to reduce the losses and therefore the self-heating during default appearance.

Figure 5: (a) Cross sectional view of the current limiter with gate electrode. (b) Micrography of the interdigitated structure, total area is 1.18 mm<sup>2</sup>. (c) Transient characteristic response to a short-circuit on resistive load.

Device was encapsulated to study short circuit switching on resistive load. A 2 mm thick aluminium substrate, with an area of 16 cm<sup>2</sup> has played the role of cooling system. As it can be seen in Fig. 5-c, there is no over-voltage and a very short response time. Short-circuit was held during several minutes, and the steady state temperature was only 77°C.

Compatibility of VJET technology to MESFET fabrication have been shown allowing to integrate the control of fault current, and moreover on the same die (monolithic integration) [16].

Bi-directional current limiting function has been obtained by head to tail association. Details of different ways of connecting gates are given in [17]. This device can sustain a breakdown voltage of 800 V.

#### 4.2 Devices realised on SiCOI material

CEA/LETI together with SOITEC have optimised the « Smart-cut » process to SiC. The resulting material is a sandwich of a thin layer of SiC, upon an insulating layer, upon a Si substrate. The advantages of this material is double: it allows to be handled with standard production equipments and to theoretically reduce the cost for the basic material. However, the constraint is to design lateral devices. From the point of view of the integrated power system, SiCOI material allows to take benefit of the good SiC properties, and an easier galvanic insulation.

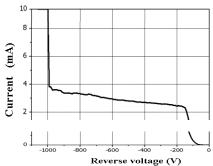

The first step was to design and realise Schottky diodes, with the following features: a Vbr of 600 V and a forward current of 1 A. The SiCOI material was with a thin SiC layer (0.5  $\mu m$ :  $2\times10^{17}$  cm<sup>-3</sup>) [18]. Typical electrical I-V characteristic is shown in Fig 7. Despite a very leaky reverse behaviour, this curve proves the feasibility of such devices on SiCOI material. MESFET transistors have also been

realised in the same time, they are functional with a measured transconductance of 200  $\mu$ S/mm).

Fig. 7: I-V characteristics of a Schottky SiCOI diode at 300 K in forward and reverse bias.

Then, the opportunity to add an SiC epilayer on the reported SiCOI material was developed. It allows to obtain a thicker active layer with a controlled doping and therefore, a new run of Schottky diode was launched. To keep the benefit of the RESURF effect, the reported SiC layer was transferred from a semi-insulating wafer. The breakdown voltage was strongly improved up to 1000 V. (see Fig 8) thanks to [19].

Fig. 8: Reverse characteristics of the Schottky diode on SiCOI with a regrowth epilayer (3  $\mu$ m thick and  $5 \times 10^{15}$  cm<sup>-3</sup> doping).

#### 5. CONCLUSION

5 kV bipolar diodes with JTE periphery protection were designed and realised. 3.9 kV breakover voltage thyristors were fabricated. In both cases, the main difficulty for high voltage devices remains passivation layer and then the packaging. Remaining works must be done before to obtain high voltage discrete components.

For specific devices, fault current limiters have shown their ability to sustain 600 V and to act as a serial protective device. Schottky SiCOI diodes and MESFET were fabricated. These devices are an important step towards the realisation of integrated power systems.

Results given in this paper are not so high as those found in literature, but are comparable.

## 6. ACKNOWLEDGEMENTS

The authors would like to thank the different technological centres that were used to realise demonstrators namely Institute Saint-Louis, LETI, IBS, CNM, IMM, CIME. Authors are also grateful for the financial support of GIRCEP and more specifically to DGA.

#### 7. REFERENCES

[1] internet web site : http://www.infineon.com

- [2] Y. Sugawara, D. Takayama, K. Asano, R. Singh, J. Palmour, 19 kV 4H-SiC pin diodes with low power loss" ISPSD 2001, Osaka, Japan, p. 27

- [3] S.V. Campen, A. Ezis, J. Zingaro, G. Storaska, R.C. Clarke, V. Temple, M. Thompson, T. Hansen "7 kV 4H-SiC GTO thyristors", Proc. MRS Fall Meeting, Symp. K, Boston, MA, USA, 2002

- [4] K. Asano, Y. Sugawara, S. Ryu, R. Singh, J. Palmour, T. Hayashi, D. Takayama, "5.5 kV normally-off low RonS 4H-SiC SEJFET", ISPSD 2001, Osaka, Japan, p. 23.

- [5] S. Ryu, A. Agarwal, S. Krishnaswami, J. Richmond, J. Palmour, "Development of 10kV 4H-SiC Power DMOSFETs", Mater. Sci. Forum, Vol. 457-460, 2004, p. 1385-1388.

- [6] C. Raynaud, S.R. Wang, D. Planson, M. Lazar, J.P. Chante.

- "OBIC analyses on 1.3 kV 6H-SiC  $p^+$ n planar bipolar diode protected by junction termination extension". Diamond and Rel. Mater., Vol. 13, 2004, p. 1697-1703.

- [7] K. Isoird, "Etude de la tenue en tension des dispositifs de puissance en carbure de silicium par caractérisations OBIC et électriques", PhD thesis, INSA Lyon, 2001.

- [8] M. Lazar, "Etude du dopage par implantation ioniques d'Aluminium dans le carbure de silicium pour la réalisation de composants de puissance", Ph-D thesis, INSA Lyon, 2002.

- [9] M. Lazar, G. Cardinali, C. Raynaud, A. Poggi, D. Planson, R. Nipoti, J.P. Chante, "The role of the ion implanted emitter state on 6H-SiC power diodes behaviour. A statistical study", Mater. Sci. Forum, Vol. 457-460, 2004, p.1025-1028.

- [10] C. Raynaud, M. Lazar, D. Planson, J.-P. Chante, Z. Sassi, "Design, fabrication and characterisation of 5 kV 4H-SiC p<sup>†</sup>n planar bipolar diodes protected by junction termination extension", Mater. Sci. Forum, Vol. 457-460, 2004, p. 1033-1036. [11] M.L. Locatelli, K. Isoird, S. Dinculescu, V. Bley, T. Lebey, D. Planson, E. Dutarde, M. Mermet-Guyennet, "Study of suitable dielectric material properties for high electric field and high temperature power semiconductor environment", EPE'03

- [12] N. Arssi, "Conception d'un Thyristor 5 kV en carbure de silicium pour assurer la génération d'impulsions de forte énergie", Ph-D thesis, INSA Lyon, 2002.

conference, 2-4 Sept 2003, Toulouse, France.

- [13] P. Brosselard, V. Zorngiebel, D. Planson, S. Scharnholz, J.P. Chante, E. Spahn, C. Raynaud, M. Lazar, "Influence of different peripheral protections on the breakover voltage of a 4H-SiC GTO thyristor", Mater. Sci. Forum, Vol. 457-460, 2004, p.1129-1132.

- [14] F. Nallet, P. Godignon, D. Planson, C. Raynaud, J.P. Chante, "Very low Ron measured on 4H-SiC accu-MOSFET high power device", 2002 ISPSD June 5-9, Santa Fe, New Mexico (USA)

- [15] D. Tournier, "Conception, réalisation et caractérisation d'un composant limiteur de courant commandé en carbure de silicium et son intégration système", Ph-D thesis, INSA Lyon, 2003.

- [16] D. Tournier, P. Godignon, J. Montserrat, D Planson, JP Chante, F Sarrus, "Compatibility of VJFET technology to mesfet fabrication and its interest to system integration" Mater. Sci. Forum, Vol. 389-393, 2002, p.1403-1406.

- [17] D. Tournier, Ph. Godignon, J. Millan, J.P.Chante, D. Planson, F. Sarrus, J.F de Palma "A multi current ratings SiC current limiter" in this Proc. SAAEI-EPF04

- [18] N. Daval, "Etude de la faisabilité de Composants de Puissance sur substrat en carbure de silicium sur isolant (SiCOI)", PhD thesis, INSA Lyon, 2002.

- [19] F. Templier, N. Daval, L. Di Cioccio, D. Bourgeat, F. Letertre, D. Planson, J-P Chante, T. Billon

- "A new process for the fabrication of SiC power devices and systems on SiCOI (Silicon Carbide On insulator) substrates". MRS Fall Meeting, Boston, Massachusetts, 2-6 Dec. 2002.