## Conception d'un transistor JFET 5 kV en SiC-4H

Pierre Brosselard, Dominique Planson, Léa Di Cioccio, Thierry Billon, Sigo Scharnholz, Mihai Lazar, Christophe Raynaud, Emil Spahn, Jean-Pierre Chante

## ▶ To cite this version:

Pierre Brosselard, Dominique Planson, Léa Di Cioccio, Thierry Billon, Sigo Scharnholz, et al.. Conception d'un transistor JFET 5 kV en SiC-4H. 10ème colloque Electronique de Puissance du Futur, Sep 2004, Toulouse, France. hal-04621465

HAL Id: hal-04621465

https://hal.science/hal-04621465

Submitted on 24 Jun 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### CONCEPTION D'UN TRANSISTOR JFET 5 kV EN SiC-4H

Pierre BROSSELARD<sup>1,2</sup>, Dominique Planson<sup>1</sup>, Léa DICIOCCIO<sup>3</sup>, Thierry BILLON<sup>3</sup>, Sigo SCHARNHOLZ<sup>2</sup>, Mihai LAZAR<sup>1</sup>, Christophe RAYNAUD<sup>1</sup>, Emil SPAHN<sup>2</sup> et Jean Pierre CHANTE<sup>1</sup>

<sup>1</sup>CEntre de Génie Electrique de LYon (CEGELY) INSA-LYON, UMR 5005 CNRS, Bat. Léonard de Vinci, 20 av. Albert Einstein, F-69621 Villeurbanne, France

<sup>2</sup>Institut Franco-Allemand de Recherche de Saint Louis (ISL), 5 rue du Général Cassagnou, F-68301 Saint Louis, France

<sup>3</sup>CEA / LETI, 17 rue des Martyrs F-38054 Grenoble Cedex 9, France

## **ABSTRACT**

Un travail de conception d'un transistor JFET en carbure de silicium possédant une tenue en tension de 5 kV a été réalisé. Le début de l'étude s'est articulé autour du choix de la structure et sur l'architecture du canal qui a aboutit à un JFET à grille enterrée de type triode. Ensuite, les caractéristiques du matériau tels que le type, le dopage et l'épaisseur ont été déterminées grâce à l'utilisation de la finis. En simulation par éléments l'enchaînement des étapes technologiques a été développé en étroite interaction avec le centre technologique. La protection périphérique a fait l'objet d'une étude à part. La réalisation du canal et de la couche de source du JFET repose sur une technologie de pointe peu développée, la reprise d'épitaxie.

#### 1 INTRODUCTION

Aujourd'hui, le carbure de silicium est un matériau semiconducteur connu pour ses potentialités dans le domaine de l'électronique de puissance [1]. Grâce à ses propriétés physiques (champ électrique critique, énergie de bande interdite, coefficient de conductivité thermique...), le carbure de silicium permet le développement de composants possédant une tension de blocage et une densité de courant élevées ainsi qu'une température de fonctionnement pouvant atteindre 400°C. De grand fondeurs tels que Infineon, Microsemi, APT, Fairchild ont commercialisé des diodes Schottky SiC possédant des tensions de claquage de 600 et 1200 V pour des calibres en courant allant jusqu'à 10 A [2]. La tenue en tension de ce type de composants en silicium est limitée à 200 V. Avec l'association d'un interrupteur de type MOSFET ou JFET en SiC, une cellule de commutation tel qu'un demi-bras d'onduleur pourra fonctionner à des fréquences plus élevées que son homologue en silicium [3]. Le but de ce papier est de montrer la conception d'un transistor JFET vertical.

La première partie de ce papier est une introduction au logiciel MEDICI<sup>TM</sup> qui sera à la base de l'étude. La deuxième partie résumera les résultats des simulations qui ont permis de déterminer les caractéristiques des

différentes couches du matériau. La troisième partie sera consacrée à la périphérie du composant.

#### **2 SIMULATION**

Le logiciel MEDICI<sup>TM</sup> fait partie des simulateurs à éléments finis [4]. Afin de déterminer le comportement physique et électrique d'une structure, nous devons passer par une étape de création d'un maillage. En chaque point de la cellule, le calculateur résout les trois équations décrites ci-dessous, pour les deux types de porteurs si besoin est :

$$-\Delta V = \operatorname{div} \vec{E} = -\frac{q}{\epsilon} (N_D - N_A + p - n)$$

Poisson (1)

$$\boldsymbol{J}_{n,p} = \boldsymbol{q} \times \boldsymbol{\mu}_{n,p} \times (n,p) \times \boldsymbol{E} \pm \boldsymbol{q} \times \boldsymbol{D}_{n,p} \times \frac{d\boldsymbol{n}}{d\boldsymbol{x}} \text{ Continuit\'e (2)}$$

$$\frac{1}{e_{n,p}} \times \frac{dJ_{n,p}}{dx} = R - G + \frac{dn}{dt}$$

Génération/Recombinaison (3)

(où V est le potentiel appliqué à la structure, E le champ électrique,  $N_D$  et  $N_A$  les concentrations des dopants (donneurs et accepteurs respectivement), n et p la concentration des électrons et trous, q charge élémentaire, J la densité de courant,  $\mu_{n,p}$  la mobilité des électrons et trous,  $\epsilon$  la permittivité du SiC,  $D_{n,p}$  coefficient de diffusion des électrons et des trous, R et G les coefficients de recombinaison et génération des porteurs)

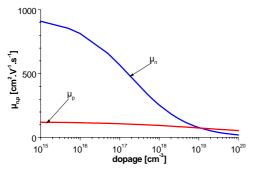

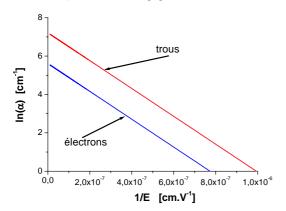

Pour les différentes grandeurs physiques (mobilité, gap...), il faut choisir le modèle que l'on veut utiliser. Ensuite, il faut saisir les paramètres du modèle qui seront utilisés par le simulateur. Les équations 4, 5 et 6 illustrent les modèles de mobilité et des coefficients d'ionisation utilisés [5]. Les figures n°1 et 2 montrent les variations de mobilité en fonction du dopage et des coefficients d'ionisation en fonction du champ électrique. Le modèle de mobilité illustré par l'équation n°4 est utilisé pour des simulations de mise en conduction. Pour la recherche de la tension de blocage, c'est le modèle de la mobilité à fort champ qui s'ajoute au modèle précédent. Dans toutes les simulations, la durée de vie est égale à 500 ns pour les électrons et les trous.

$$\mu_{\text{0n,p}} = \text{MUN,P.MIN} + \frac{\text{MUN,P.MAX} \left(\frac{T}{300}\right)^{\text{NUN,P}} - \text{MUN,P.MIN}}{1 + \left(\frac{T}{300}\right)^{\text{XIN,P}} \left(\frac{N_{\text{total}}(x,y)}{\text{NRFFN P}}\right)^{\text{ALPHAN,P}}}$$

(4)

$$\mu_{n,p} = \frac{\text{mun,p0}}{\left[1 + \left(\frac{\text{mun,p0.E}_p}{V_{\text{satn n}}}\right)^{\text{Betan,p}}\right]^{\frac{1}{\text{Betan,p}}}}$$

(5)

$$\alpha_{n,p} = (n, p.ioniza).exp\left(-\frac{E_{cn,p}}{E_{p}}\right)$$

(6)

Fig.1 : Variation de la mobilité parallèle (à la conduction des électrons et des trous) en fonction du dopage de la couche étudiée

Fig. 2 : Variation du coefficient d'ionisation en fonction de l'inverse du champ électrique

De plus, il faut préciser si le type de composant est unipolaire ou bipolaire. En conduction, il est nécessaire de préciser un modèle pour la génération et la recombinaison des porteurs, et pour cela nous utilisons la statistique de Schokley-Read-Hall. Son expression est :

$$U_{SRH} = \frac{pn - n_{ie}^2}{\tau_{p} \cdot \left[ n + n_{ie} exp(\frac{E_{trap}}{kT}) \right] + \tau_{n} \cdot \left[ p + n_{ie} exp(\frac{-E_{trap}}{kT}) \right]}$$

(7)

Pour toutes les simulations réalisées dans ce travail, nous supposons l'ionisation complète des dopants.

#### 3 JFET

#### 3.1. Fonctionnement du JFET

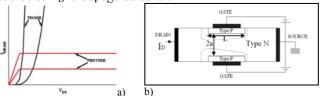

Le principe de fonctionnement d'un transistor JFET repose sur la modulation de la résistivité d'un barreau de semi-conducteur à l'aide de la modulation de la zone de charges d'espace d'une jonction PN. Il existe deux grandes familles de JFET, un de type pentode et un autre

de type triode. Une représentation sommaire des différentes caractéristiques électriques est illustrée par la figure n°3 [6].

Pour un rapport L/2a faible, les caractéristiques électriques sont de type triode. Il n'existe pas de saturation en courant. Par contre pour L/2a grand, le courant est limité par un effet 'entonnoir', c'est la raison pour laquelle les JFET ont des caractéristiques électriques avec une saturation du courant. La tension de pincement  $(V_{\rm pi})$  est définie par la relation :

$$V_{\rm pi} = qN_{\rm D}a^2/2\varepsilon_{\rm r}\varepsilon_0 - V_{\rm bi}$$

où  $V_{bi}$  est la tension de diffusion de la jonction grille source et  $N_D$  le dopage du canal.

Fig. 3 : Formes des caractéristiques électriques des JFET (a) et vue en coupe d'un transistor JFET élémentaire (b) avec ses paramètres L, 2a et la limite de charge d'espace

#### 3.2. Structure JFET en SiC:

Le cahier des charges est de réaliser un transistor JFET en SiC-4H possédant une tension de blocage égale à 5 kV et une densité de courant à l'état passant égale à 2 kA.cm<sup>-2</sup>. La configuration triode sera retenue pour ce cas. Le CEA/LETI est le centre technologique qui réalisera les composants.

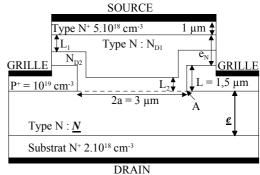

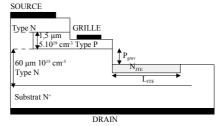

La structure de base (figure  $n^{\circ}4$ ) a été déterminée de façon à utiliser uniquement les techniques d'épitaxie pour l'obtention des couches.

Fig. 4: Structure de la cellule élémentaire du JFET simulée

#### 3.3. Optimisation de la couche de drift :

Tout d'abord, des simulations ont été réalisées pour déterminer l'épaisseur (e) et le dopage (N) de la couche de dérive. Une étude est faite sur la tension de blocage et le régime passant. Les paramètres sont :

| 2a   | L    | $N_{D2}$            | $L_2$ | $N_{D1}$            | $e_N$ |

|------|------|---------------------|-------|---------------------|-------|

| [µm] | [µm] | [cm <sup>-3</sup> ] | [µm]  | [cm <sup>-3</sup> ] | [µm]  |

| 3    | 1,5  | $10^{16}$           | 0,25  | $5 \times 10^{15}$  | 2     |

TABLEAU 1: PARAMETRES DU JFET POUR LA SIMULATION

L'influence de ces paramètres sera étudiée dans les prochains paragraphes.

La tension de blocage est obtenue pour une tension de commande  $V_{GS}$  égale à -50~V et la densité de courant à l'état passant est donnée pour une tension  $V_{DS}$  de 100~V.

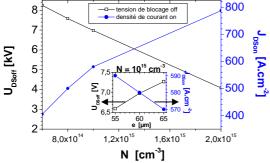

Fig. 5 : Tension de blocage et densité de courant en fonction de N. L'encart représente la même variation en fonction de e

La figure 5 montre que si le dopage  $\bf N$  augmente, la tension de blocage diminue mais par contre la densité de courant  $\bf J_{\rm DSON}$  augmente. L'évolution de la tenue en tension et de la densité de courant en fonction de l'épaisseur  $\bf e$  est illustrée par l'encart de la figure 5. La sensibilité de la tenue en tension (~5%) à la variation de  $\bf e$  est beaucoup plus grande que celle de la densité de courant (3%). En effet, la tenue en tension est proportionnelle à l'épaisseur de la zone de dérive  $\bf e$  alors que la résistance du composant à l'état passant dépend surtout de la résistance du canal. Les paramètres retenus pour cette zone sont un dopage de  $8\times10^{14}$  cm<sup>-3</sup> ainsi qu'une épaisseur de 60  $\mu$ m.

#### 3.4. Optimisation de la couche de grille (type P)

Un nouveau groupe de simulations a été réalisé pour déterminer les caractéristiques de la couche P (L pour l'épaisseur et P pour le dopage). Les autres paramètres sont définis dans le tableau 1 avec  $\mathbf{e} = 60~\mu m$  et  $\mathbf{N} = 10^{15}$  cm<sup>-3</sup>.

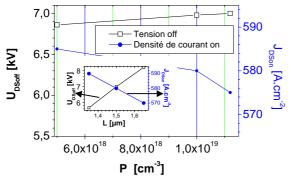

Fig. 6 : Tension de blocage et densité de courant en fonction de N et e

La figure 6 montre l'évolution de  $U_{DSoff}$  et  $J_{DSon}$  en fonction du dopage et de l'épaisseur (en encart de la figure 6) de la zone P. La sensibilité de  $U_{DSoff}$  et  $J_{DSon}$  est beaucoup moins importante pour le dopage que pour l'épaisseur car la pénétration de la zone de charge d'espace dans la zone P est faible compte tenu des fortes valeurs de dopage. Par contre, l'influence de la longueur du canal (L) sur la tension de blocage et de la densité de courant n'est pas négligeable car la résistance du canal est proportionnelle à L. Pour L égal à 1,35  $\mu$ m, la tension de blocage est égale à la tenue en tension de la jonction PN (grille/drain). Si L continue à augmenter, la tension de blocage n'évoluera plus mais  $J_{DSon}$  diminuera. Les valeurs

retenues pour cette couche sont un dopage de  $10^{19}$  cm<sup>-3</sup> et une épaisseur de 1,5  $\mu$ m.

#### 3.5. Gravure du canal :

Le canal du transistor est obtenu par une gravure de la zone de type P et par une reprise d'épitaxie d'une zone N puis N<sup>+</sup>. Le carbure de silicium étant un matériau dur, sa gravure se fait uniquement par plasma, et l'obtention de flancs raides est très difficile. Il est absolument nécessaire pour le fonctionnement du transistor que la profondeur de gravure de la couche épitaxiée P<sup>+</sup> soit supérieure à l'épaisseur de cette couche de type P. Les simulations montrent que si la gravure est plus profonde, la tension de blocage ainsi que la densité de courant ne sont pas modifiées.

| P                   | L    | e    | N .                 | $L_2$ | $e_N$ | $N_{D1}$            |

|---------------------|------|------|---------------------|-------|-------|---------------------|

| [cm <sup>-3</sup> ] | [µm] | [µm] | [cm <sup>-3</sup> ] | [µm]  | [µm]  | [cm <sup>-3</sup> ] |

| $10^{19}$           | 1,5  | 60   | $10^{15}$           | 0     | 2     | $5 \times 10^{15}$  |

TABLEAU 2: PARAMETRES DU JFET POUR LA SIMULATION

Des simulations sont réalisées pour montrer l'influence de l'angle de gravure. Les paramètres de la structure pour les simulations sont représentés dans le tableau 2.

Si la largeur du canal augmente de 0,3 μm par rapport à 3 μm nominal, la tension de blocage diminue de 2,1 kV. Ce résultat implique que l'ensemble des étapes de photo-lithographie, ouverture du masque et gravure plasma doit être très précis. Si la largeur du canal **2a** diminue de 0,3 μm, la tension de blocage est égale à la tenue en tension de la jonction Grille/Drain + Grille/Source (8,8 kV). Mais par contre la densité de courant passe de 580 à 440 A.cm<sup>-2</sup> ce qui s'explique par l'augmentation de la résistance du canal.

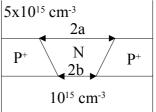

Fig.7 : Schéma du canal d'un JFET pour la détermination de l'angle de gravure

| 2a [μm]                               | 3    | 3    | 3,26 |

|---------------------------------------|------|------|------|

| 2b [μm]                               | 3    | 2,54 | 3    |

| $V_{br}$ [kV] à $V_{GS} = -50$ V      | 6,98 | 8,38 | 5,35 |

| $J_{DS} [A.cm^{-2}] a V_{DS} = 100 V$ | 580  | 460  | 580  |

TABLEAU 3: RESULTATS DE SIMULATIONS POUR DIFFERENTS

Deux configurations sont possibles pour la gravure du canal. L'ensemble des résultats est présenté dans le tableau 3. Un exemple de gravure en pente est représentée par la figure 7, l'angle de gravure est égal à 80° (2b < 2a). La tension de blocage est améliorée au détriment de  $J_{\rm DSon}$ . Si 2b > 2a,  $J_{\rm DSon}$  ne varie pas car c'est 2a qui limite le courant. Par contre  $U_{\rm DSoff}$  diminue. Lors de la conception du masque, l'ouverture du canal sera égale à 2,5  $\mu m$ . De plus, des composants de différentes largeurs de canal seront réalisés sur le jeu de masques.

# 3.6. Détermination des caractéristiques des couches réépitaxiées :

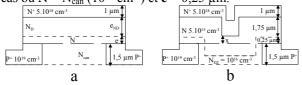

Des simulations complémentaires sont réalisées pour montrer l'influence du dopage du canal. La structure étudiée est représentée par la figure 8(a). Pour e = 0,  $N_D$  =  $10^{15}$  cm<sup>-3</sup> et  $e_{ND}$  = 2  $\mu$ m, le dopage du canal n'influence pas la tenue en tension. En effet, seule la résistance du canal diminue lorsque le dopage augmente.

Les caractéristiques électriques sont invariantes dans le cas où  $N = N_{can} (10^{16} \text{ cm}^{-3})$  et  $e = 0.25 \mu m$ .

Fig. 8 : Structures JFET simulées pour déterminer le dopage du canal et au dessus la grille (a) et pour la prise en compte de la non planarisation (b)

| A                                        |           |           |  |  |

|------------------------------------------|-----------|-----------|--|--|

| $N_D [cm^{-3}] e_{ND} = 2 \mu m$         | $10^{15}$ | $10^{16}$ |  |  |

| $V_{br}$ [kV] à $V_{GS} = -50 \text{ V}$ | 8,40      | 2,92      |  |  |

| $J_{DS} [A.cm^{-2}] à V_{DS} = 100 V$    | 740       | 1380      |  |  |

| В                                        |           |           |  |  |

| $e_{ND} [\mu m] N_D = 10^{15} cm^{-3}$   | 2         | 3,5       |  |  |

| $V_{br}$ [kV] à $V_{GS} = -50$ V         | 8,40      | 8,40      |  |  |

| $J_{DS} [A.cm^{-2}] à V_{DS} = 100 V$    | 740       | 733       |  |  |

TABLEAU 4 : RECAPITULATIF DES CARACTERISTIQUES ELECTRIQUES EN FONCTION DE  $e_{\text{ND}}\left(A\right)$  ET  $N_{\text{D}}\left(B\right)$

Le tableau 4 montre l'influence de  $N_D$  et  $e_{ND}$  sur la tension de blocage et la densité de courant. Si le dopage augmente, la tenue en tension diminue. En effet, pour  $V_{br} = 8,4~kV$  le claquage a lieu à la jonction grille/drain alors que pour  $V_{br} = 2,9~kV$  le claquage a lieu à la jonction grille/source. L'augmentation de l'épaisseur n'influence pas la tenue en tension car le claquage est due à la jonction grille/drain.

Des simulations sont réalisées en prenant en compte la non planarisation des couches (figure 8b). C'est le paramètre  ${\bf x}$  qui joue sur la tenue en tension. Plus il diminue plus la tenue en tension est faible, due au non pincement du canal. Pour  ${\bf x}$  allant de 0,5 à 1  $\mu$ m, la tension de blocage passe de 4,8 à 7,3 kV.

En résumé, les caractéristiques du JFET sont un substrat de type  $N^+$  puis une première épitaxie N dopée à  $8x10^{14}$  cm<sup>-3</sup> sur  $60~\mu m$ , une épitaxie P dopée à  $10^{19}$  cm<sup>-3</sup> sur  $1,5~\mu m$ , une première couche réépitaxiée dopée à  $5\times10^{15}$  cm<sup>-3</sup> dont le paramètre  $\mathbf{x}$  est supérieure à  $1~\mu m$  et une deuxième réépitaxie dopée à  $5\times10^{18}$  cm<sup>-3</sup> sur  $1~\mu m$  qui permettra la diminution de la résistance de contact de source.

#### 3.7 Périphérie :

Le but de cette partie est de déterminer les paramètres pour la protection périphérique des composants. Les simulations réalisées précédemment ne font pas apparaître les problèmes liés à la périphérie de la jonction grille/drain. Le choix s'est orienté autour d'une combinaison de deux types de protection, mesa (utilisant la technique de gravure) et JTE (Junction Termination Extension) développé à partir d'une implantation ionique.

La structure simulée est représentée par la figure 9. Trois paramètres sont à optimiser : profondeur de gravure  $(P_{grav})$ , longueur de la poche  $(L_{JTE})$  et dopage de la poche  $(N_{ITE})$ .

Fig. 9 : Structure JFET simulée avec périphérie

Des simulations ont été réalisées et ont permis de déterminer les paramètres optimaux qui sont une dose de poche égale à  $1,2\times10^{13}$  cm<sup>-2</sup>, une profondeur de gravure supérieure à 1  $\mu$ m et une longueur de poche supérieure à 150  $\mu$ m.

#### 4. CONCLUSION

Ce papier a montré les résultats essentiels de la conception d'un JFET. Les simulations ont pris en compte au mieux les difficultés technologiques. Le transistor relèvera plusieurs défis tels que la réalisation sur des épitaxies épaisses et peu dopées provenant du LETI et la formation du canal repose sur la technique de la réépitaxie, technologie peu développée aujourd'hui. Prochainement, nous espèrerons caractériser ce composant et vous faire part des résultats dans une prochaine communication.

#### **5 REFERENCES**

- [1] Y. Sugawara, "Recent Progress in SiC Power Device Developments and Application Studies," *ISPSD*, Cambridge, pp. 10-18, 2003.

- [2] Produits Infineon http://www.infineon.com

- [3] Technology Modeling Associates, Inc. MEDICI: Two dimensionnal semiconductor device simulation, Version 2001.2.0, Vol. 1 et Vol. 2, 2001

- [4] D. Planson, S. Margenat, F. Nallet, H. Morel, M.L. Locatelli, J.P. Chante, "Estimation des pertes d'une cellule de commutation en utilisant la méthode des éléments finis pour des convertisseurs à base de composants en silicium et carbure de silicium", *EPF*, Lille, pp. 171-176, 29 novembre/1 décembre 2000

- [5] F. Nallet, A. Sénès, D. Planson, M.L. Locatelli, J.P. Chante, D. Renault, "Electrical and electrothermal 2D simulations of a 4H-SiC high voltage current limiting device for serial protection applications", *ISPSD*, Toulouse, pp. 287-290, 22/25 Mai 2000.

- [6] D. Planson, "Contribution à l'étude de composants de puissance haute température en carbure de silicium", Thèse de Doctorat, Lyon, INSA, 1994