## Error Correction Codes, from Communication to Cryptography... Two sides of one *chip*

Dr. Cvrille CHAVET - Dr. Bertrand LE GAL

Pr. Philippe COUSSY, Mael TOURRES, Syed FAHIMUDDIN ALAVI

June 12, 2024

ECC & Cryptography vs RISC-V A brief history of ECC & Cryptography

June 12, 2024

June 12, 2024

ECC & Cryptography vs RISC-V A brief history of ECC & Cryptography

June 12, 2024

2/31

## Once upon a time...

- Efforts to create a secure voice system had existed since the 1920s

- During World War II, C. Shannon works on SIGSALY, the first Secure Digital Voice Communications

- Mathematical definition of information and encrypted transmission over a noisy channel

- Shannon's paper "A Mathematical Theory of Communication1" is considered as the founding work of information theory

- Error Correction Codes are an integral part of encryption

## Agenda

- A brief history of ECC & Cryptography

- Face of the chip Error Correction Codes

- Tails side of chip Cryptographic algorithms

- Conclusion

Once upon a time...

SIGSALY2 was a digital speech encryption system, developed by Bell Telephone Laboratories

Shannon, C. E. (1948). A mathematical theory of communication. The Bell System. Technical Journal, 27(3), 379-423; and the second part, in The Bell System Technical Journal, 27(4), 623-656. ECC & Cryptography vs RISC-V

A brief history of ECC & Cryptography

In our everyday lives

## Face of the chip - Error Correction Codes Error Correction Codes Principles

- The world's most important asset is information

- Protecting information is crucial to ensure a trusted global economy (E-commerce, online banking, social networking or emailing, online medical results, mobile phone communications, stock exchange...)

- These constraints generate two huge challenges:

- . Ensuring the same quality of information for any communication channel ⇒ Error Correction Codes

ECC & Cryptography vs RISC-V

- Ensuring the security of information for any communication channel ⇒ Cryptography

- For a "reasonable" cost

- · Error detection/correction on digital communications channels · Two types of encoding methods

- - . Block encoding Each codeword is generated from one block of k message symbols Convolutional encoding - Each codeword is generated from several

- consecutive message blocks

ECC & Cryptography vs RISC-V

Face of the chip - Error Correction Codes Some typical Error Correction Codes

Face of the chip - Error Correction Codes

June 12, 2024

## Some typical Error Correction Codes

- Hamming

- Reed-Salomon

C. Chavet & B. Le Gal

- Goppa

- McFliecce

- LDPC

- Turbo-Codes

- NR-I DPC

- Polar codes

- ...

- Hamming

- Reed-Salomon

- Goppa

- McFliecce

- LDPC

- Turbo-Codes

- NR-I DPC

- Polar codes

- ...

June 12, 2024

## Some typical Error Correction Codes

- Hamming

- Reed-Salomon

- Goppa

- McFliecce

- LDPC<sup>a</sup>

- Turbo-Codes

- NB-LDPC

- Polar codes

V. Pignoly et al., "Fair comparison of hardware and software LDPC decoder implementations for SDR space links". Int. Conf. ECS. 2020

SW LDPC - Intel XEON GOLD 6148

| LDPC code      | #cores | favg     | Throughput | Latency | Power |  |

|----------------|--------|----------|------------|---------|-------|--|

| (16384, 4096)  | - 1    | 3403 MHz | 0.48 Gbps  | 34 µs   | 169 W |  |

| (16384, 4096)  | 40     | 2194 MHz | 11.25 Gbps | 60 µs   | 343 W |  |

| (64800, 29160) | - 1    | 3484 MHz | 0.32 Gbps  | 201 μs  | 173 W |  |

| (64800, 29160) | 40     | 2194 MHz | 7.60 Gbps  | 345 µs  | 370 W |  |

| (22528, 6144)  | - 1    | 3485 MHz | 0.35 Ghps  | 64 µs   | 173 W |  |

| (22528, 6144)  | 40     | 2194 MHz | 7.55 Gbps  | 122 µs  | 345 W |  |

| HW        | LDPC -   | Xilinx | Ultrasc | ale+) | CZU9  | EG-3FF  | VB1156E |       |

|-----------|----------|--------|---------|-------|-------|---------|---------|-------|

| LDPC code | - Acores | FPGA   | DISPOS. | fm    | s The | perhoss | Latency | Power |

| LDPC code      | #cores | PPGA usage | fmax    | Throughput | Latency | Power   |

|----------------|--------|------------|---------|------------|---------|---------|

| (16384, 4096)  | - 1    | 17%        | 274 MHz | 2.34 Obps  | 7.7 px  | 3.29 W  |

| (16384, 4096)  |        | 78%        | 274 MHz | 11.65 Gbps | 7.7 pcs | 13.80 W |

| (64800, 29160) | - 1    | 22%        | 271 MHz | 1.36 Gbps  | 47.5 µs | 4,74 W  |

| (64800, 29160) | 3      | 68%        | 270 MHz | 4.08 Gbps  | 47.7 µs | 12.92 W |

| (22528, 6144)  | - 1    | 31%        | 273 MHz | 4.02 Gbps  | 6.1 ps  | 3.63 W  |

|                |        |            |         |            |         |         |

Performance Comparison of the Proposed GPU-Like Decoder Vs GPU-Based

Decoders

**GPU-like**

**GPU-like**

8800-GTX

**GPU-like**

8800-GTX

**GPU-like**

**GPUJik**

GPU-like

Wang et al. 2011a

our work

(Falcae et al. 2011a

Some typical Error Correction Codes

- Hamming Reed-Salomon

- Goppa

- McEliecce

- LDPCab

- Turbo-Codes

- NB-LDPC

- Polar codes

- <sup>a</sup>V. Pignoly et al., "Fair comparison of hardware and software LDPC decoder implementations for SDR space links", Int. Conf. ECS, 2020

- <sup>b</sup>B. Le Gal and C.Jégo, "GPU-Like On-Chip System for Decoding LDPC Codes" ACM TECS, 2014

C. Chavet & B. Le Gal

Face of the chip - Error Correction Codes

ECC & Cryptography vs RISC-V

$9904 \times 1152$

$4000 \times 2000$

$4896 \times 2448$

8000 × 4000

8000 × 4000

$648 \times 328$

June 12, 2024

307.4

78.94 11.55 0.007

0.004

28.29

0.055

1300

1350

1350

1150 107.8

ECC & Cryptography vs RISC-V Face of the chip - Error Correction Codes

June 12, 2024 10/31

Some typical Error Correction Codes

# Some typical Error Correction Codes

- Hamming Reed-Salomon

- Goppa

- McFliecce

- LDPC<sup>ab</sup>

- Turbo-Codes

- NB-LDPC

- Polar codes

- V. Pignoly et al., "Fair comparison of hardware and software LDPC decoder implementations for SDR space links". Int. Conf. ECS. 2020

- <sup>b</sup>B. Le Gal and C.Jégo, "GPU-Like On-Chip System for Decoding LDPC Codes".ACM TECS. 2014

- Hamming Reed-Salomon

- Goppa

- McFliecce

- LDPC

- Turbo-Codes

- NB-LDPC

- Polar codes

- ...

## Some typical Error Correction Codes

## Hamming Reed-Salomon

Goppa

McFliecce

LDPC

Turbo-Codes<sup>a</sup>

NR-I DPC Polar codes

B. Le Gal and C. Jégo, "Low-latency and gh-throughput software turbo decoders on multi-core architectures". Annals of Telecommunications. 2019

|      | radem               | or 5M | Chr  | Mbps | ж     | Mbps. | INDC | nJ   |

|------|---------------------|-------|------|------|-------|-------|------|------|

| [22] | GTX 550Ti           | 6     | 1.90 | 85   | 72*   | 47    | 1.5  | 227  |

| [23] | GTX 580             | 16    | 1.54 | 4    | 1660  | 1     | 0.0  | 1099 |

| [24] | GTX 480             | 15    | 1.40 | 123  | 50°   | 35    | 1.1  | 339  |

| (25) | GTX 680             | 8     | 1.01 | 37   | 2657  | 27    | 0.1  | 878  |

| [26] | GTX 580             | 16    | 1.54 | 107  | 230*  | 22    | 0.7  | 458  |

| [25] | 17-37700C           | 4     | 3.50 | 76   | 323   | 33    | 4.1  | 168  |

| [27] | 17-4960890          | 4     | 3.20 | 143  | 2731  | 67    | 4.2  | 41   |

| [27] | 2.E5-2680v3         | 24    | 2.50 | 716  | 3293  | 67    | 4.2  | 41   |

| (27) | 17-4960EIQ          | 4     | 3.20 | 51   | 7693  | 24    | 1.5  | 114  |

| [27] | 2.E5-2690v3         | 24    | 2.50 | 237  | 9971  | 24    | 1.5  | 169  |

| [27] | 17-4960 <b>89</b> Q | 4     | 3.20 | 51   | 7693  | 24    | 0.7  | 114  |

| 27   | 2.25-2699v3         | 24    | 2.50 | 457  | 10312 | 46    | 1.4  | 87   |

| LeG  | 17-4960BQ           | 4     | 3.20 | 238  | 103   | 112   | 7.0  | 25   |

| LeG  | 2.E5-2680v3         | 24    | 2.50 | 908  | 162   | 91    | 5.7  | 44   |

| LeG  | 17-4960000          | 4     | 3.20 | 225  | 105   | 105   | 6.6  | 26   |

| LeG  | 2.E5-2680v3         | 24    | 2.50 | 894  | 165   | 89    | 5.6  | 45   |

| LeG  | 17-4960890          | 4     | 3.20 | 466  | 52    | 218   | 6.8  | 13   |

| LeG  | 2.E5-2680v3         | 24    | 2.50 | 1735 | 84    | 174   | 5.4  | 23   |

NThe = (The × hers) / (Freq × Cores) TNDC = (Thr. × Bero) / (Cones × Freq. × SIMD)  $E_d = [TDP/(Thr. \times hers)] \times 10^5$

C. Chavet & B. Le Gal Face of the chip - Error Correction Codes

ECC & Cryptography vs RISC-V

June 12, 2024

13 / 31

# PhD thesis of Mael Tourres<sup>3</sup> (2019-2024)

- Director: Pr. P. Coussy

- Advisors: C. Chavet and B. Le Gal.

- · Propose an approach to generate processor ISA extension dedicated to ECC

- Selected ECC for experiences: LDPC, Turbo-Codes, NB-LDPC and Polar Codes

- Objectives

- Taking advantage of both worlds ASIC for speed and consumption, and CPU/GPU for adaptability Taking advantage of data parallelism, to further enhance performance

- · Preserve the clock frequency

- . Do not degrade final chip area and power consumption

M. Tourres et al., "Extended RISC-V hardware architecture for future digital communication systems", 2021 IEEE 4th 5G World Forum (5GWF) 14/31

C. Chavet & B. Le Gal ECC & Cryptography vs RISC-V June 12, 2024 Face of the chip - Error Correction Codes

New Instruction Design Flow

# Architectural target

Selected RISC-V cores: PicoRV32, RISCY, IBEX and SCR1 (and CVA6 from OHG)

## Last Experimental Results to be published4

| inter-transe |                 |                                  | LDPC   | sc     | Polatre<br>F-SC | LDPC-NB<br>MS | Turbo   |

|--------------|-----------------|----------------------------------|--------|--------|-----------------|---------------|---------|

| lutif        | O Barcino       | cyclos                           | 90800  | 454637 | 239292          | 1715625       | 1565623 |

| latif_total  | @ ISA 28        | system                           | 61443  | 273854 | 215509          | 1292853       | 1651247 |

| (32 bits)    | • ISA 38.       | eyder                            | 54827  | 200978 | 162066          | 969990        | 804477  |

|              | Gala (00)       | cyclox                           | 41928  | 351959 | 72150           | 745635        | 781350  |

|              | Gala (0-0)      | (%)                              | 43.7%  | 35.6%  | 30.2%           | 43.5%         | 49.25   |

|              | Gain (0-0)      | system                           | 7416   | 81176  | 48414           | 322963        | 200779  |

|              | Gold (0-+0)     | (%)                              | 12.0%  | 21.7%  | 22.4%           | 25.0%         | 23.49   |

|              | Disk 0          | Kbita/s                          | 341    | 200    | 1711            | 7             | 20      |

|              | Dilair 6        | Kbits/s                          | 885    | 4382   | 7602            | 29            | 2354    |

|              | Deka •          | Khita/s                          | 1006   | 5598   | 5805            | 52            | 3871    |

| bs8.1×8      | 0 ISA 28        | cycles                           | 57998  | 349229 | 242388          | 3359196       | 120772- |

| (64 bits)    | <b>0</b> ISA 38 | system                           | 525-06 | 335632 | 213560          | 3015731       | 163596  |

|              | Clair (0-0)     | system                           | 43409  | 11960S | 29732           | 699954        | \$49656 |

|              | Grin (0-10)     | (%)                              | 45.2%  | 26.3%  | 10.8%           | 40.8%         | 31.65   |

|              | Gain (9-+9)     | cycles                           | 5352   | 53388  | 39428           | 343455        | 17176   |

|              | Gala (0-0)      | (%)                              | 9.2%   | 11.7%  | 12.4%           | 25.7%         | 14.29   |

|              | Dillik 0        | Khitajis                         | 141    | 900    | 2711            |               | 29      |

|              | Doka o          | Khitaja                          | 1879   | 8440   | 13.630          | 25            | 4300    |

|              | Dibit. 0        | Kbita/s                          | 2870   | 5780   | 15343           | 100           | 4783    |

| Arcibination |                 |                                  |        |        |                 |               |         |

|              | • → •           | 32 bits                          | 7.1×   | 6.2×   | 5.7×            | 7.1×          | 7.55    |

|              | 0 → 0           | 64 bits                          | 14.6×  | 10.5×  | 9.0×            | \$3.5×        | 12.2>   |

|              | 0 → 0           | $32 \rightarrow 64 \text{ hits}$ | 2.1×   | 1.7×   | 1.6×            | 1.9 x         | 1.65    |

- <sup>4</sup>M. Tourres et al., "Specialized Scalar and SIMD instructions for Error Correction Codes Decoding on RISC-V processors", ECC & Cryptography vs RISC-V June 12, 2024

- Tails side of chip Cryptographic algorithms

# Classical Cyphers

- · Symmetric cyphering: DES, ΔFS

- · Asymmetric cyphering: PGP, SSL. RSA Elliptic Curve cyphering:

- **ECDSA** Signature: MD5/SHA1, SHA2,

- SHA3-Keccak

ECC & Cryptography vs RISC-V Example of an AES extension on a RISC-V6

# Standardization of RISC-V Cryptographic Extensions<sup>5</sup>

## Scalar Cryptography

- Bit manipulation, Data independent execution, AES enccryption/decryption, SHA2...

- Public review ended in Oct.17<sup>th</sup>, 2021

- Ratified

## Vector Cryptography

- Same algorithms, but for element that are group of scalars

- Public review ended last year

- Ratified

- 32-bit architectures

- · Byte-wise round instructions Results on SCARV and Rocket

and 64-bit architectures

Limited area increase - x1.03 vs SCARV

Hardware assisted T-table approach for 32

- and 1.001 vs Rocket

- . SW memory footprint divided by a factor

- Speedup upto x3,6 on SCARV and x2,5 on Rocket

Source: J.Savard, wikipedia

B.Marshall et al.," The design of scalar AES Instruction Set Extensions for RISC-V". https://doi.org/10.46586/tches.v2021.i1.109-136

Tails side of chip - Cryptographic algorithms Tails side of chip - Cryptographic algorithms

## Hypothetical (?) weaknesses

- Mathematical problem that are really complex to solve (prime factorization, log computation...)

- The computing power required to crack them is titanic

- However, the literature is full of side-channel attacks... and wavs of countering them

- CPA, DPA, clock glitching...

- Masking<sup>7</sup>, randomization...

## All this could collapse the day a real quantum computer arrives in the laboratories

Tails side of chip - Cryptographic algorithms

Recent works

- Many studies explore these aspects

- Processor that are able to change between classical and post-quantum cryptography

- Dedicated PQC coprocessors design

- · Definition of PQC extension of ISA (cf. PhD thesis of M. Tourres)

## A solution - Post-Quantum Cryptography

- The advent of post-quantum encryption has seen the return of ECC to favour

- McFliecce

- NTRU MDPC

- Bike

- Crystal Kyber/Dilithium

- Expensive and complex algorithms

- · For small system, a hardware accelerator could be a good option

Tails side of chip - Cryptographic algorithms

ECC & Cryptography vs RISC-V

June 12, 2024

22 / 31

PhD Thesis of Rémy Fumeron (2019-xx)

- Founded by PEC Cyber

- Director: Pr. Philippe Coussy

- Advisors: C. Chavet and K. Martin

- · Subject: Exploring an agile CPU that could handle both generic computation and PQC algorithm - Study of ECC code from the NIST on the Pulp platform

- Research abandoned by the PhD student at the end of 2020

<sup>7</sup>F. Lozachmeur and A. Tisserand, "A RISC-V Instruction Set Extension for Flexible Hardware/Software Protection of Cryptosystems Masked at High Orders", 66th IEEE International Midwest Symposium on Circuits and Systems (MWSCAS 2023) ECC & Cryptography vs RISC-V June 12, 2024

- Founded by PEPR ARSENNE

- Thesis director: Dr Arnaud Tisserand (DR CNRS)

- . Subject: Exploring the design of an architecture that could handle both classical and PQC

ECC & Cryptography vs RISC-V June 12, 2024

25 / 31 Tails side of chip - Cryptographic algorithms

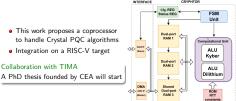

# Master Thesis of Syed FAHIMUDDIN ALAVI TIMA

- Supervisor: Dr. C. Chavet

- Exploring RISCV ISA extension for Post-Quantum Cryptography

- Target architecture: PicoRV32

- Test case: AES for classical cryptography and Crystal and McEliecce for PQC

- The idea is to show that it is possible to extract some complex parts of a PQC algorithm, and to replace it by some dedicated new RISCV instruction

## Tails side of chip - Cryptographic algorithms

Master Thesis of Ivan SARNO

CRYPHTOR8 (CRYstals Polynomial HW acceleraTOR)

8 S. Di Matteo et al., "CRYPHTOR: A Memory-Unified NTT-Based Hardware Accelerator for Post-Quantum CRYSTALS Algorithms", IEEE Access, 2024, DOI:10.1109/ACCESS.2024.3367109

Tails side of chip - Cryptographic algorithms

June 12, 2024

# Master Thesis of Syed FAHIMUDDIN ALAVI TIMA

- Current results

- . For AES, the PicoRV32 with custom instruction is upto twice as faster compared to the reference

- For CRYSTAL Kyber 1024:

- ho  $\sim 8.5\%$  and  $\sim 18.5\%$  of latency improvement in PQC encryption and decryption resp.

- FMAX legacy: 58,27MHz, FMAX custom ext.: 82,85 MHz Area overcost: 6.5% for our enriched PicoRV32

- Paper is coming...

28/31

Conclusion

Conclusion

## Conclusion

- The worlds of error-correcting codes and cryptography are part and parcel of each other

- But, currently 'simple' mathematical problems (compared to ECC) made it possible to guarantee, a level of security that make encryption algorithms virtually unbreakable

- · However, it is possible that in the medium/long term the emergence of quantum machines will disrupt all this

- As part of the NIST competition, ECC have made a comeback in the field of cryptography (McElliecce, NTRU MDPC, Bike...)

- · As it was the case when LDPCs were first discovered, these algorithms offer excellent performance, but at prohibitive cost

- To solve these problems, the solution may once again come from computer engineering...

C. Chavet & B. Le Gal ECC & Cryptography vs RISC-V June 12, 2024

The worlds of error-correcting codes and cryptography are part and parcel of each other But, currently 'simple' mathematical problems (compared to ECC)

made it possible to guarantee, a level of security that make encryption algorithms virtually unbreakable However, it is possible that in the medium/long term the emergence

Conclusion

- of quantum machines will disrupt all this As part of the NIST competition. ECC have made a comeback in the

- field of cryptography (McElliecce, NTRU MDPC, Bike...) As it was the case when LDPCs were first discovered, these

- algorithms offer excellent performance, but at prohibitive cost

- To solve these problems, the solution may once again come from computer engineering...

Thanks

C. Chavet & B. Le Gal

ECC & Cryptography vs RISC-V

June 12, 2024 30 / 31

https://xkcd.com/538 - Security

31/31