## SOI MOS technology for spin qubits

Louis Hutin, Benoit Bertrand, Yann-Michel Niquet, Jean-Michel Hartmann, Marc Sanquer, Silvano de Franceschi, Tristan Meunier, Maud Vinet

### ▶ To cite this version:

Louis Hutin, Benoit Bertrand, Yann-Michel Niquet, Jean-Michel Hartmann, Marc Sanquer, et al.. SOI MOS technology for spin qubits. ECS Transactions, 2019, 93 (1), pp.35-36. 10.1149/09301.0035ecst. hal-04597821

HAL Id: hal-04597821

https://hal.science/hal-04597821

Submitted on 3 Jun 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# SOI MOS technology for spin qubits

Louis Hutin

CEA, LETI, Minatec Campus,

F-38054

Grenoble, France

louis.hutin@cea.fr

Marc Sanquer CEA, INAC-PHELIQS, F-38054 Grenoble, France

marc.sanquer@cea.fr

Benoit Bertrand

CEA, LETI, Minatec Campus,

F-38054

Grenoble, France

benoit.bertrand@cea.fr

Silvano De Franceschi CEA, INAC-PHELIQS, F-38054 Grenoble, France silvano.defranceschi@cea.fr Yann-Michel Niquet CEA, INAC-MEM, F-38054 Grenoble, France yann-michel.niquet@cea.fr

Tristan Meunier CNRS - Institut Néel, F-38042 Grenoble, France tristan.meunier@neel.cnrs.fr Jean-Michel Hartmann CEA, LETI, Minatec Campus, F-38054 Grenoble, France jean-michel.hartmann@cea.f

Maud Vinet

CEA, LETI, Minatec Campus,

F-38054

Grenoble, France

maud.vinet@cea.fr

Abstract— We fabricated Si Quantum Dot (QD) devices using relatively minor adaptations of a standard SOI CMOS process flow. We demonstrated that the spin of confined charges could be controlled via a local electrical-field excitation, owing in the case of electrons to a geometrically-enabled tuning of the valley splitting and inter-valley spin-orbit coupling. We discuss improvement paths such as extending the spin coherence time by using epi-layers of nuclear-spin-free <sup>28</sup>Si (99.992%) as a device template, and developing novel 3D architectures compatible with topological quantum error correction schemes.

#### I. SOI CMOS-DERIVED SPIN QUBITS

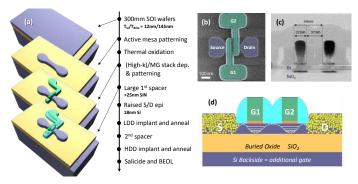

We aim to engineer a device for the coherent manipulation of information encoded as a quantum superposition of basis states, i.e. a quantum bit (qubit). In particular, the qubit state is mapped to the spin of a charged particle confined in a Quantum Dot (QD) [1]. We focus on QDs defined in a silicon lattice [2]. A popular way of isolating charges starts with forming a 2-Dimensional Electron Gas (2DEG) at the interface of a heterojunction (Si/SiGe), and obtain lateral confinement through depletion-mode Field-Effect Gates [3]-[7]. Alternately, charges can be confined at MOS interfaces [8],[9]. In our case (Fig.1), we accumulate holes or electrons below MOS Gates wrapping around mesa-etched Si NanoWires (NW) [10],[11]. In fact, the main difference versus a standard SOI NWFET process flow is the spacer width preventing doping between densely patterned Gates (pitch 65nm), forming 1D arrangements of nearest neighbor-coupled QDs. Coherent control and dispersive readout of hole spin qubits were recently demonstrated in such CMOS-compatible devices [12],[13].

#### II. CORNER DOTS AND SPIN-VALLEY-ORBIT MIXING

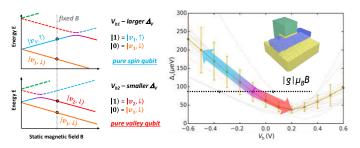

Surprisingly, we also observed spin transitions in MOS Gate-confined electrons using only E-field excitations [14], without resorting to co-integrated micro-magnets [15]. The underlying mechanism is based on the interplay between Spin-Orbit Coupling (SOC) and the multi-valley structure of the Si Conduction Band, and is enhanced by the "Corner Dot" device geometry [16]. By offering the ability to break and restore the confinement symmetry at will, the SOI Back-Gate permits fast programming in valley mode, and information storage in spin mode (Fig. 2) [17].

Fig. 1. (a) Simplified process flow of the SOI MOS QD devices with self-aligned reservoir doping. (b) Top view SEM micrograph and (c) transverse cross-sectional TEM view of a two-Gate device. (d) Potential wells are formed below the field-effect Gates, with the wide spacers protecting the inter-Gate regions from doping, thus enabling to define a potential barrier between the QDs.

Fig. 2. (Left) Energy diagram showing the Zeeman splitting of the two low-lying valleys in two  $V_b$  configurations. Depending on the relative values of the valley splitting  $(\Delta_V)$  and the Zeeman energy  $(E_Z=|g|,\mu_B,B)$  at a given magnetic field B, the qubit can be encoded by a superposition of (long-lived, E-field insensitive) spin or (short-lived, E-field addressable) valley states. (Right)  $\Delta_V$  vs. applied back-Gate voltage  $V_b$  in an SOI corner dot device, including the impact of local surface roughness variability (rms: 0.4nm) [17].

This functionality could alleviate the trade-off between fast manipulation and long coherence time, thereby improving the outlook for compact, scalable and fault-tolerant quantum logic circuits. Considering the valley-splitting-dependent resonance frequency for driving coherent oscillations of the qubit, it is probable that separate back-Gates should be defined in order to calibrate each device to a common operating point.

#### III. ISOTOPICALLY PURE <sup>28</sup>SI THIN FILMS

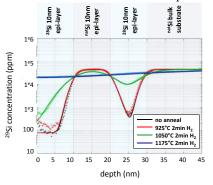

Hyperfine interactions with nuclear spins in the host crystal can limit the coherence time of an electron spin qubit. The most abundant Si isotope (28Si: 92.23%) carries no nuclear spin, but <sup>29</sup>Si (4.67%) does. Increasing the relative <sup>28</sup>Si content by has led to some of the best performing single and two-qubit gates [5],[8],[9]. We have grown epilayers with a <sup>28</sup>Si isotopic purity greater than 99.992% on 300 mm natural abundance silicon (natSi) crystals. The quality of the mono-crystalline isotopically purified epilayer conforms to the same drastic quality requirements as the natural epilayers used in our preindustrial CMOS facility [18]. Fig. 3 shows the <sup>29</sup>Si concentration depth profile in a <sup>28</sup>Si/<sup>nat</sup>Si/<sup>28</sup>Si stack and its diffusion for various annealing conditions, indicating thermal budget restrictions may be needed during device processing (e.g. dopant activation, wafer bonding), in the case where a natSi seed should remain in the top SOI film.

Fig. 3. SIMS data (symbols) and simulation results (lines) of <sup>29</sup>Si concentration depth profile vs. annealing conditions in a <sup>28</sup>Si 10nm / <sup>28</sup>Si 10nm / bulk <sup>28</sup>Si 10nm / bulk <sup>28</sup>Si stack [18].

#### IV. 3D ARCHITECTURES FOR FAULT-TOLERANT COMPUTING

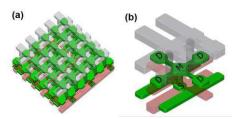

The surface code scheme [19] is nowadays one of the preferred approaches to Quantum Error Correction (QEC) due to its relatively high error threshold. It topologically requires that each individually addressable qubit should be coupled to four adjacent qubits, and hence naturally leads to 2D arrays of coupled QDs. Note that such an arrangement is no longer compatible with a conventional transistor geometry or process flow. Recent architecture proposals have emerged, relying on crossbar addressing of the QDs and tunnel junctions in order to reduce the number of I/Os [20],[21]. Our proposed 3D architecture features two stacked layers of active Si. A large 2D array of QDs is tunnel-coupled by Si pillars to chargesensing QDs on a lower tier, in order to enable fast initialization and readout [22].

Fig. 4. (a) 3D array of coupled Si QDs and (b) 3D elementary cell composed of six dots; four Data Dots, one Measurement Dot and one Sensing Dot connected to the top tier by a crystalline Si pillar. The topology is designed for the implementation of surface code, with an auxiliary bottom tier for sensing and fast initialization of the charge occupancy in the top tier [22].

#### ACKNOWLEDGMENT

The authors acknowledge financial support from the EU under Project MOS-QUITO (No. 688539), and from the French Public Authorities through National Research Agency (ANR) projects IDEX UGA (ANR-15-IDEX-0002) and CMOSQSPIN (ANR-17-CE24-0009), as well as the Carnot Quantique program.

#### REFERENCES

- D. Loss, D. P. DiVincenzo, "Quantum computation with quantum dots", *Phys. Rev. A*, 57, 120, 1998.

- [2] F. Zwanenburg et al., "Silicon quantum electronics", Reviews of Modern Physics, 85, 961-1019, 2013.

- [3] M. Friesen et al., "Practical design and simulation of silicon-based quantum-dot qubits", Phys. Rev. B, 67, 121301, 2003.

- [4] E. Kawakami *et al.*, "Electrical control of a long-lived spin qubit in a Si/SiGe quantum dot," *Nat. Nanotechnology*, vol. 9, pp. 666-670, 2014.

- [5] J. Yoneda et al., "A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%", Nat. Nanotechnol., 13, 102-106, 2018.

- [6] D. M. Zajac et al., "Resonantly driven CNOT gate for electron spins", Science, 359, 439-442, 2018.

- [7] T. F. Watson et al., "A programmable two-qubit quantum processor in silicon", Nature, 555, 633-637, 2018.

- [8] M. Veldhorst et al., "A two-qubit logic gate in silicon," Nature, 526, 410-414, 2015.

- [9] C. H. Yang et al., "Silicon quantum processor unit cell operation above one Kelvin", arXiv:1902.09126, 2019.

- [10] A. Fujiwara et al., "Single electron tunneling transistor with tunable barriers using silicon nanowire metal-oxide-semiconductor field-effect transistor", Appl. Phys. Lett., 88, 053121, 2006.

- [11] M. Hofheinz et al., "Simple and controlled single electron transistor based on doping modulation in silicon nanowires", Appl. Phys. Lett., 89, 143504, 2006.

- [12] R. Maurand et al., "A CMOS silicon spin qubit," Nature Commun., 7, 13575, 2016.

- [13] A. Crippa *et al.*, "Gate-reflectometry dispersive readout of a spin qubit in silicon", *arXiv:1811.04414*, 2018.

- [14] A. Corna et al., "Electrically driven electron spin resonance mediated by spin-valley-orbit coupling in a silicon quantum dot," npj Quantum Information, vol. 4, 6, 2018.

- [15] M. Pioro-Ladrière et al., "Electrically driven single-electron spin resonance in a slanting Zeeman field," Nat. Phys., vol. 4, 10, pp. 776-779, 2008.

- [16] B. Voisin et al., "Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor", Nano Lett., 14, 4, 2014.

- [17] L. Bourdet et al., "All-Electrical Control of a Hybrid Electron Spin/Valley Quantum Bit in SOI CMOS Technology", IEEE Trans. Elect. Dev., 65, 11, 2018.

- [18] V. Mazzocchi et al., "99.992% <sup>28</sup>Si CVD-grown epilayer on 300mm substrates for large scale integration of silicon spin qubits", J. Crystal Growth, 509, 2019.

- [19] A. G. Fowler et al., "Surface codes: towards practical large-scale quantum computation", Phys. Rev. A, 86, 032324, 2012.

- [20] M. Veldhorst et al., "Silicon CMOS architecture for a spin-based quantum computer", Nature Commun., 8, 1766, 2017.

- [21] R. Li et al., "A crossbar network for silicon quantum dot qubits", Science Advances, 4, 7, 2018.

- [22] L. Hutin, S. De Franceschi, T. Meunier, and M. Vinet, "Quantum device with spin qubits," (2018), U.S. Provisional Pat. Ser. No. 15/967778.