# Fully Microstrip Three-Port Circuit Bandpass NGD Design and Test

Blaise Ravelo, Alexandre Douyere, Yang Liu, Wenceslas Rahajandraibe, Fayu Wan, George Chan, Mathieu Guerin

# ▶ To cite this version:

Blaise Ravelo, Alexandre Douyere, Yang Liu, Wenceslas Rahajandraibe, Fayu Wan, et al.. Fully Microstrip Three-Port Circuit Bandpass NGD Design and Test. IEEE Design & Test, 2023, 40 (1), pp.96-104. 10.1109/MDAT.2022.3164337. hal-04475024

HAL Id: hal-04475024

https://hal.science/hal-04475024

Submitted on 23 Feb 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Fully Microstrip 3-Port Circuit Bandpass NGD Design and Test

Blaise Ravelo, *Member*, *IEEE*, Alexandre Douyère, *Member*, *IEEE*, Yang Liu, Wenceslas Rahajandraibe, *Member*, *IEEE*, Fayu Wan, *Senior Member*, *IEEE*, George Chan, *Senior Member*, *IEEE*, and Mathieu Guerin, *Member*, *IEEE*

Abstract-An innovative design and test of three-port distributed circuit exhibiting double bandpass (BP) negative group delay (NGD) effect is investigated. The distributed topology is constituted by resistive transmission lines (TLs) with one input and two output accesses. The BP-NGD specifications are defined. The transfer matrix-based modelling is elaborated. The doublebranch NGD theorization is based on the equivalent model of voltage transfer function (VTF) between Port<sub>1</sub>-Port<sub>2</sub> and Port<sub>1</sub>-Port3. The VTF analytical expressions in function of TL parameters are formulated. Group delay (GD) innovative formulas are derived. The feasibility study is based on the BP-NGD design of 3-port hybrid microstrip prototype implemented on Rogers Duroid-AD1000 dielectric substrate. To validate the concept, the VTF magnitudes and GDs computed with MATLAB® are compared with commercial tool simulation and experimental results. The modelled, simulated and measured three-port circuit results show NGD responses in very good agreement. It was emphasized that the two transmission ways of the tested circuit operate with BP-NGD behavior confirmation. The measured NGD value and bandwidth of about -3.8 ns and 75 MHz at center frequency of about 0.74 GHz are obtained.

Index Terms— Bandpass (BP) negative group delay (NGD), Modelling, Design and test, Three-port microstrip circuit, Transmission line (TL), Voltage transfer function (VTF).

#### I. INTRODUCTION

The TREE structure constitutes topological solution for electronic printed circuit board (PCB) designers against the integration high-density challenge [1-2]. The tree topology optimization enables to reduce the signal transition delays and power consumption [3]. General simulation method based on SPICE model was suggested to predict the multiport component behaviors [4]. But somehow analytical models are necessary for the fast estimation of tree interconnect effect before the electronic circuit design phase. Several constraints as skew effect need to be estimated with interconnect trees [5]. Generic RC-network modeling was proposed to estimate the tree effect

interconnect line delay sensitivity [6-7]. The RC-tree was used to implement different analog and digital electronic circuit technologies as CMOS [8-9]. A slew metric expression of RCtree ramp input was proposed [10-11]. However, with the increase of the signal speed, the inductance effect must be considered to estimate the signal delay [12]. Equivalent model of RLC-tree interconnects was introduced [13-14]. Different topologies of tree interconnects as H-[15-19], T-[20] and YY-[21] shaped structures were suggested as clock and signal distribution networks. The H-shaped distribution network enables to synchronize the clock signal distribution [15]. An efficient design method enables to improve the design method [16,18]. The variations of interconnect parameters on the tree clock distributions were studied [17]. Beyond the RC- [6-12] and RLC- [13-14] networks, more general tree interconnect analytical modelling of microstrip structures was developed based on the transmission line (TL) approach [19-21]. The signal integrity parameters and frequency domain responses of complex tree-interconnects were assessed [19-21]. In difference to the existing tree-interconnect model, the present paper investigates bandpass (BP) negative group delay (NGD) design of 3-port microstrip circuit. So far, the performed research work on BP-NGD microstrip circuit is limited to 2-port topology [22-23]. So far, the BP-NGD circuits are commonly designed with two-port topologies. Because of theorization and design difficulties, few works are performed on BP-NGD 3-port circuit [24]. Most of NGD design researchers are failed because of design difficulties to control simultaneously the GDs through the two ways. To face up this challenge, the present study introduces BP-NGD design of distributed 3-port topology. The paper is organized in three sections. Section II focuses on the analytical modeling based on the double voltage transfer function (VTF) via transfer matrix operation. Section III presents the BP-NGD validation results from 3-port microstrip

signal delay [6-12]. The RC meshes were used to determine the

Manuscript received xxx xx, 2021; revised xxx xx, 2021; accepted xxx xx, 2021. Date of publication xxx xx, 2021.

This research work was supported in part by NSFC under Grant 61971230, and in part by Jiangsu Specially Appointed Professor program and Six Major Talents Summit of Jiangsu Province (2019-DZXX-022) and in part by the Startup Foundation for Introducing Talent of NUIST, in part by the Postgraduate Research & Practice Innovation Program of Jiangsu Province under Grant KYCX20\_0966.

Blaise Ravelo and Fayu Wan are with the Nanjing University of Information Science & Technology (NUIST), Nanjing 210044, Jiangsu, China (E-mail: blaise.ravelo@yahoo.fr, Corresponding author: fayu.wan@nuist.edu.cn).

Alexandre Douyère is with Energy Lab, Network and Telecom Team, University of la Reunion, La Reunion island, France. (E-mail: alexandre.douyere@univ-reunion.fr).

Yang Liu is with Altran, 78140 Vélizy-Villacoublay, France. (E-mail: liuyang2101@gmail.com).

Wenceslas Rahajandraibe and Mathieu Guerin are with the Aix-Marseille University, CNRS, University of Toulon, IM2NP UMR7334, Marseille, France (E-mail: {wenceslas.rahajandraibe, mathieu.guerin}@im2np.fr).

George Chan is with ASM Pacific Technology Ltd., Hong-Kong. (E-mail: george.chan@asmpt.com).

circuit proof-of-concept (POC). Then, Section IV is the final conclusion.

#### II. 3-PORT MICROSTRIP DOUBLE VTF BP-NGD MODEL

After the BP-NGD definition, the 3-port topology under study is introduced. Then, the VTF modeling is elaborated.

#### A. BP-NGD Specifications

By denoting the angular frequency variable,  $\omega$ , the BP-NGD analysis is performed by consideration of VTF magnitude,  $T(\omega) = \left| T(j\omega) \right|$ , and phase,  $\varphi(\omega) = \arg \left[ T(j\omega) \right]$ . The associated GD response is defined by:

$$GD(\omega) = -\partial \varphi(\omega) / \partial \omega$$

. (1)

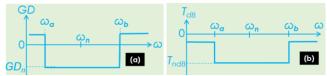

An electric circuit behaves as a BP-NGD function if it presents cut-off frequencies,  $(\omega_a,\omega_b)$ , which are the roots of equation  $GD(\omega)=0$ . The associated NGD bandwidth is given by  $BW=f_b-f_a=(\omega_b-\omega_a)/(2\pi)$ . As illustrated by ideal GD response of Fig. 1(a), the NGD center frequency,  $\omega_n$ , and NGD value can be expressed as  $GD_n=GD(\omega_n)<0$  with negative value. The ideal case of magnitude response is shown by Fig. 1(b) with  $T_n=T(\omega_n)<0$  in the NGD BWs ( $\omega\in BW$ ).

Fig. 1. BP-NGD ideal responses: (a) GD and (b) magnitude.

#### B. Topological Introduction of the 3-Port Structure

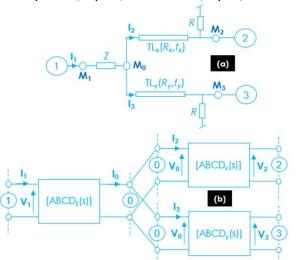

The 3-port topology under study is introduced by Fig. 2(a). It is constituted by input port,  $\oplus$ , referenced by node  $M_1$  connected to series resistor, Z, to the middle node,  $M_0$ . The input current injected at port  $\oplus$  is denoted  $I_1$ . The two output branches,  $M_0M_2$ , to port 2, with TL  $TL_x(R_x,t_x)$  and  $M_0M_3$ , to port 3, with TL  $TL_y(R_y,t_y)$  which are terminated by shunt resistor, R. The TLs are specified by their characteristic impedance,  $R_{x,y}$ , and propagation delay,  $t_{x,y}$ . The input current injected at port 2 (resp. 3) is denoted  $I_2$  (resp.  $I_3$ ).

Fig. 2. (a) 3-port circuit topology under study and (b) its equivalent diagram.

By taking Laplace variable,  $s=j\omega$ , the equivalent model of the 3-port structure introduced by Fig. 2(b) is composed of transfer matrix constituting:

- Input branch,  $M_1M_0$ :  $\begin{bmatrix} ABCD_Z(s) \end{bmatrix} = \begin{bmatrix} 1 & Z \\ 0 & 1 \end{bmatrix}$  (2)

- Output branch,  $M_0M_2$  (with  $x = a \exp(-t_x s)$ ):

$$[ABCD_{x}(s)] = \frac{1}{2a x} \begin{bmatrix} 1 + a^{2}x^{2} & (1 - a^{2}x^{2})/R_{x} \\ R_{x}(1 - a^{2}x^{2}) & 1 + a^{2}x^{2} \end{bmatrix}$$

(3)

• Output branch,  $M_0M_3$  (with  $y = a \exp(-t_y s)$ ):

$$\left[ABCD_{y}(s)\right] = \frac{1}{2a y} \begin{bmatrix} 1 + a^{2}y^{2} & (1 - a^{2}y^{2})/R_{y} \\ R_{y}(1 - a^{2}y^{2}) & 1 + a^{2}y^{2} \end{bmatrix} (4)$$

• And shunt resistor:  $\begin{bmatrix} ABCD_R(s) \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ 1/R & 1 \end{bmatrix}$  (5)

The operation between these transfer matrices enables to determine the ways  $\mathbb{O}$ - $\mathbb{O}$  and  $\mathbb{O}$ - $\mathbb{O}$  VTFs in the following subsection.

## C. VTF Expressions and BP NGD Existence

Let us generalize the transfer matrix of each branch, with  $m=\{2,3\}$ , as:

$$\begin{bmatrix} V_1 \\ I_1 \end{bmatrix} = \begin{bmatrix} ABCD^{1 \to m} \end{bmatrix} \begin{bmatrix} V_m \\ 0 \end{bmatrix}$$

(6)

By definition, the VTFs between input-output port of the structure shown by Figs. 1 are expressed by:

$$TF_{m=\{2,3\}}(s) = V_m(s)/V_1(s) = 1/ABCD_{11}^{1\to m}(s)$$

. (7)

To determine the detailed expression, we can proceed with the transfer matrix product:

$$\begin{bmatrix}

V_1 \\

I_1

\end{bmatrix} = \begin{bmatrix} ABCD_z \end{bmatrix} \begin{bmatrix} ABCD_{Z_y} \end{bmatrix} \begin{bmatrix} ABCD_x \end{bmatrix} \begin{bmatrix} ABCD_x \end{bmatrix} \begin{bmatrix} ABCD_R \end{bmatrix} \begin{bmatrix} V_2 \\ 0 \end{bmatrix}$$

$$\begin{bmatrix} V_1 \\ I_1 \end{bmatrix} = \begin{bmatrix} ABCD_z \end{bmatrix} \begin{bmatrix} ABCD_{Z_x} \end{bmatrix} \begin{bmatrix} ABCD_y \end{bmatrix} \begin{bmatrix} ABCD_y \end{bmatrix} \begin{bmatrix} ABCD_R \end{bmatrix} \begin{bmatrix} V_3 \\ 0 \end{bmatrix}$$

(9)

Transfer matrices  $[ABCD_{Zin\_x}]$  and  $[ABCD_{Zin\_y}]$  represent the generalized expression of parallel input impedances with subscript,  $\zeta = \{x,y\}$ :

$$Z_{\zeta}(s) = \frac{R_{x} \left[ R(1+\zeta^{2}) + R_{x}(1-\zeta^{2}) \right]}{R(1-\zeta^{2}) + R_{y}(1+\zeta^{2})}.$$

(10)

Therefore, we have the VTFs

$$TF_{2}(s) = \frac{2R_{x}R_{y}Rx\left[R_{y}(1-y^{2}) + R(1+y^{2})\right]}{R^{2}(R_{y} - R_{x})(x^{2} - 1)(1+y^{2}) + R_{x}^{2}R_{y}^{2}(x^{2} - 1)(y^{2} - 1)}$$

$$+R\left\{R_{x}^{2}(x^{2} - 1)(1-y^{2}) - R_{x}R_{y}(1+x^{2})(1+y^{2})\right\}$$

$$-R_{y}^{2}(1-x^{2})(1+y^{2})$$

$$TF_{3}(s) = \frac{2R_{x}R_{y}Ry\left[R_{x}(1-x^{2}) + R(1+x^{2})\right]}{R^{2}(R_{x} - R_{y})(y^{2} - 1)(1+x^{2}) + R_{x}^{2}R_{y}^{2}(x^{2} - 1)(y^{2} - 1)}$$

$$+R\left\{R_{y}^{2}(y^{2} - 1)(1-x^{2}) - R_{x}R_{y}(1+x^{2})(1+y^{2})\right\}$$

$$-R_{x}^{2}(1-y^{2})(1+x^{2})$$

$$(12)$$

(12)

The BP-NGD analysis is based on VTF magnitude,  $TF_m(\omega) = \left| TF_m(j\omega) \right|$ , and phase,  $\varphi_m(\omega) = \arg \left[ TF_m(j\omega) \right]$ . The associated GD is determined by:

$$GD_m(\omega) = -\partial \varphi_m(\omega) / \partial \omega$$

. (13)

For the sake of mathematical simplification, the following NGD analysis is performed under the case,  $R_x = R_y = R_0$ . We can demonstrate that at quarter wavelength angular frequencies:

$$\omega_{\rm r} = \pi / (4t_{\rm r}) \tag{14}$$

$$\omega_{v} = \pi / (4t_{v}) \tag{15}$$

The transmission way 0-0 TF magnitude is expressed as:

$$TF_{2}(\omega_{x}) = \frac{\sqrt{2R_{0}R\left[R^{2}(1+\xi^{2})+R_{0}^{2}(1-\xi^{2})\right]}}{\left[R^{2}R+R_{0}^{2}(Z-R)-R_{0}^{3}+2R_{0}RZ+\right]}.$$

$$\xi\left[R_{0}^{3}-R_{0}^{2}R+(R-R_{0})^{2}Z\right]$$

$$+(R-R_{0})^{2}\left[R_{0}^{2}+Z(R_{0}-R)\right]$$

(16)

with  $\xi = \cos(\pi t_y / t_x)$ . The corresponding GD,  $GD_x = GD(\omega_x)$  corresponding to transmission way  $\mathbb{O}$ - $\mathbb{O}$  is given by:

$$\xi^{2}(R^{2} - R_{0}^{2})^{2} \left[ R^{2}Z + R_{0}^{2}(Z - R) \right] +$$

$$R_{0}\xi \begin{cases} ZR^{4} - R^{3} \left[ (R^{2} + Z^{2})t_{x} + Z^{2}t_{y} \right] + R^{2}R_{0}^{2}Z(4t_{x} + t_{y}) \\ -R_{0}^{2}R \left[ (R_{0}^{2} + Z^{2})t_{x} + 3Z^{2}t_{y} \right] + R_{0}^{4}Z(t_{x} + t_{y}) \end{cases}$$

$$+ \left[ \xi(R^{2} - R_{0}^{2}) + R_{0}^{2} + R^{2} \right] \left\{ R^{6}R_{0}Zt_{x} - R_{0}^{4}R^{4}(R + R_{0}) \left[ (R_{0}^{2} + 4Z^{2})t_{x} + 2Z^{2}t_{y} \right] + R^{4}R_{0}^{3}Z(7t_{x} + 2t_{y}) - 2R_{0}^{3}R^{3} \left[ (R_{0}^{2} + 4Z^{2})t_{x} - 2Z^{2}t_{y} \right] \right\}$$

$$GD_{x} = \frac{+R_{0}^{5}R^{2}Z(7t_{x} - 4t_{y}) + R_{0}^{7}Z(t_{x} + 2t_{y})}{\xi(R^{2} - R_{0}^{2}) \left[ (RZ - R_{0}^{2})^{2} - Z^{2}R_{0}^{2} \right] - 2R_{0}^{2}RZ(R^{2} + 3R_{0}^{2})}$$

$$+Z^{2}(R^{4} + 6R^{2}R_{0}^{2} + R_{0}^{4}) + R_{0}^{4}(R^{2} + R_{0}^{2})$$

$$(17)$$

The way ①-③ VTF magnitude is written as:

$$TF_{3}(\omega_{y}) = \frac{\sqrt{2R_{0}R\left[R^{2}(1+\cos(\pi t_{x}/t_{y})^{2})+R_{0}^{2}(1-\cos(\pi t_{x}/t_{y})^{2})\right]}}{R^{2}R+R_{0}^{2}(Z-R)-R_{0}^{3}+2R_{0}RZ+\cos(\pi t_{x}/t_{y})\left[R_{0}^{3}-R_{0}^{2}R+(R-R_{0})^{2}Z\right]} +(R-R_{0})^{2}\left[R_{0}^{2}+Z(R_{0}-R)\right]}$$

(18)

By analogy, the way ①-③ GD can be written by substituting  $t_x$  and  $t_y$  of the last equation. By taking  $\zeta = \cos(\pi t_x / t_y)$ , the GD associated to three-port circuit way ①-③ is given by (19).

To verify the BP-NGD 3-port circuit theory feasibility, PoC, prototyping and experimental investigation will be presented in the next section.

$$GD_{y} = GD(\omega_{y}) = \frac{\left\{ \mathcal{C}^{2}(R^{2} - R_{0}^{2})^{2} \left[ R^{2}Z + R_{0}^{2}(Z - R) \right] + \left[ R_{0}\mathcal{C}^{2}(R^{2} - R_{0}^{2})^{2} \left[ R^{2}Z + R_{0}^{2}(Z - R) \right] + \left[ R_{0}\mathcal{C}^{2}(At_{y} + t_{x}) + R_{0}^{2}Z(4t_{y} + t_{x}) \right] + \left[ R_{0}\mathcal{C}^{2}R \left[ (R_{0}^{2} + Z^{2})t_{y} + 3Z^{2}t_{x} \right] + \left[ R_{0}^{4}Z(t_{x} + t_{y}) \right] + \left[ \mathcal{C}(R^{2} - R_{0}^{2}) + R_{0}^{2} + R^{2} \right] \left\{ R^{6}R_{0}Zt_{y} - R_{0}^{4}R^{4}(R + R_{0}) \left[ (R_{0}^{2} + 4Z^{2})t_{y} + 2Z^{2}t_{x} \right] + R_{0}^{4}R^{2}(2Tt_{y} + 2t_{x}) - 2R_{0}^{3}R^{3} \right] + \left[ (R_{0}^{2} + 4Z^{2})t_{y} - 2Z^{2}t_{x} \right] + R_{0}^{5}R^{2}Z(7t_{y} - 4t_{x}) + R_{0}^{7}Z(t_{y} + 2t_{x}) \right\}$$

$$GD_{y} = GD(\omega_{y}) = \frac{\left\{ \mathcal{C}(R^{2} - R_{0}^{2}) \left[ (RZ - R_{0}^{2})^{2} - Z^{2}R_{0}^{2} \right] + \left[ 2R_{0}^{2}RZ(R^{2} + 3R_{0}^{2}) \right] + R_{0}^{4}R^{2}(R^{2} + R_{0}^{4}) + R_{0}^{4}(R^{2} + R_{0}^{2}) \right\} - 2R_{0}^{2}RZ(R^{2} + 3R_{0}^{2}) \right\}$$

$$(19)$$

#### III. SIMULATED AND EXPERIMENTAL VALIDATIONS

The present section introduces the 3-port microstrip circuit BP-NGD validation. After the PoC description, the calculated, simulated and measured results will be discussed.

## A. PoC Design Description

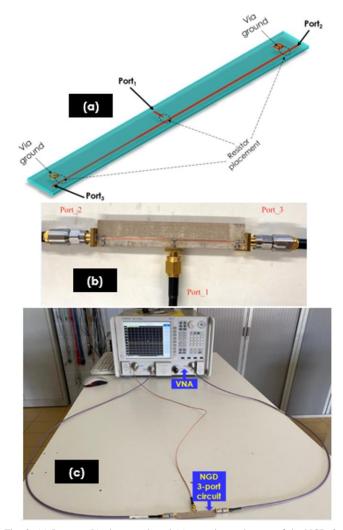

The 3-port circuit prototype was implemented on Cumetalized ARLON AD1000 dielectric substrate in hybrid technology with 0603 SMD resistors. The substrate characteristics are addressed in Table I. The circuit prototype introduced was designed and fabricated with the parameters indicated in the table last row. Fig. 3(a) shows the designed circuit layout from the electronic and RF/microwave circuit simulator ADS® from Keysight Technologies®. Fig. 3(b) shows the corresponding photo.

$\label{eq:Table I} \textbf{CIRCUIT AND SUBSTRATE PHYSICAL PARAMETERS}$

| Structure     | Structure Description    |                   | Values   |

|---------------|--------------------------|-------------------|----------|

|               | Relative permittivity    | $\mathcal{E}_r$   | 10.2     |

| Substrate     | Loss tangent             | $tan(\delta)$     | 0.0023   |

|               | Thickness                | h                 | 762 µm   |

| Metallization | Copper conductivity      | σ                 | 58 MS/s  |

| conductor     | Thickness                | t                 | 35 µm    |

| Access line   | Length                   | d                 | 5 mm     |

| $TL_x$        | Length                   | $d_x$             | 36.2 mm  |

|               | Propagation delay        | $t_x$             | 0.37 ns  |

| $TL_y$        | Length                   | $d_{\mathrm{y}}$  | 32.1 mm  |

|               | Propagation delay        | $t_{\rm y}$       | 0.335 ns |

| All TLs       | Width                    | w                 | 0.68 mm  |

| All ILS       | Characteristic impedance | $R_x = R_y = R_0$ | 50 Ω     |

|               | Resistor                 | R                 | 10 Ω     |

|               | Resistor                 | Z                 | 1 kΩ     |

Fig. 3. (a) Layout, (b) photograph and (c) experimental setup of the NGD 3-port circuit prototype.

The fabricated circuit prototype has physical sizes 77 mm  $\times$  9 mm. The S-parameter measurement is based on recorded in touchstone data as illustrated by the experimental setup illustrated by Fig. 3(c). The test was carried out by using Vector Network Analyzer (VNA) referenced, N5241A PNA-X Microwave Network Analyzer, 10 MHz to 13.5 GHz, with SMA 85052D SOLT calibration kit. The BP-NGD experimental validation is explored in the next subsection.

#### B. Validation Results

We emphasize that the calculated results of the 3-port circuit POC were obtained with MATLAB programming of VTF magnitude established in equations (11) and (12), and GD. The sensitivity analyses with respect to the TL parameters are examined in the following paragraph.

# 1) Sensitivity Analyses with Respect to the TL Characteristic Impedances and Propagation Delays

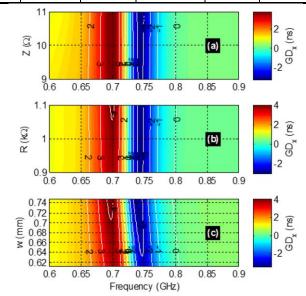

This sensitivity analyses were performed by varying linearly and individually Z, R and w between +/-10% of their nominal values. Fig. 4(a), 4(b) and 4(c) represent the mappings of  $GD_x$  in function of the couple frequency and Z, R and w, respectively. Figs. 5 display the corresponding magnitudes. We can understand from the cartographies that the BP NGD function is still conserved despite the parametric variations. Based on Figs.

4, the GD responses are less sensitive to R and Z variation compared to w. The minimal and maximal values of NGD center frequency, bandwidth, value and the VTF attenuation are addressed by Table II. It can be seen that  $f_n$  is insensitive to Z and R variations. However, the NGD absolute value  $|GD_n|$  decreases when Z, R and w increase.

|     | Parameter | $f_n$ (MHz) | BW (MHz) | $GD_n$ (ns) | $TF_{x}(f_{n})$ (dB) |

|-----|-----------|-------------|----------|-------------|----------------------|

| min | Z         | 744         | 78       | -3.265      | -0.632               |

|     | R         |             |          | -3.245      | -0.199               |

|     | w         | 740         | 76       | -3.511      | -0.543               |

| max | Z         | 744         | 78       | -3.155      | 0.495                |

|     | R         |             | 80       | -3.178      | 0.012                |

|     | w         | 748         | 80       | -2.907      | 0.423                |

Fig. 4.  $GD_x$  mappings versus frequency and (a) Z, (b) R and (c) w.

Fig. 5.  $TF_x$  magnitude mappings versus frequency and (a) Z, (b) R and (c) w.

2) Discussion on Calculated, Simulated and Measured Results

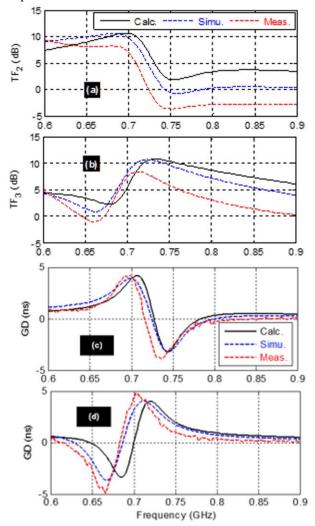

The calculated, simulated, and measured VTF magnitudes of the 3-port circuit prototype through ways  $\mathbb{O}$ - $\mathbb{O}$  and  $\mathbb{O}$ - $\mathbb{O}$  are plotted in Figs. 6(a), and 6(b). It can be seen from these figures

that in the NGD frequency band, the attenuation is higher than

-3 dB through way ①-② and higher than -1 dB through way ①-③. Comparisons between the calculated ("Calc."), simulated ("Simu.") with ADS®, and measured ("Meas.") results were carried out in the frequency band from 0.6 GHz to 0.9 GHz. It can be emphasized that the VTF GDs present a BP-NGD behavior. The corresponding GDs through ways ①-② and ①-③ are displayed by Figs. 6(c) and Fig. 6(d), respectively. It can be pointed out that these comparative results present a very good agreement. The measured NGD center frequency of transmission through ways ①-② and ①-③ are approximately  $f_n$ ○-③=737 MHz and  $f_n$ ○-③=667 MHz. Table III summarizes the differences between the calculated, simulated and measured NGD parameters.

Fig. 6. Comparisons of calculated, simulated, and measured VTF magnitudes through way (a)  $\bigcirc$ - $\bigcirc$  and (b)  $\bigcirc$ - $\bigcirc$ , and GDs through way (c)  $\bigcirc$ - $\bigcirc$  and (d)  $\bigcirc$ - $\bigcirc$  of 3-port BP-NGD prototype.

TABLE III COMPARISON OF BP NGD SPECIFICATION

| COMPARISON OF BP NGD SPECIFICATIONS |     |            |                |             |               |

|-------------------------------------|-----|------------|----------------|-------------|---------------|

| Approach                            | Way | $f_n(MHz)$ | $GD(f_n)$ (ns) | BW<br>(MHz) | $T(f_n)$ (dB) |

| Calc.                               | ①-② | 745        | -3.15          | 56          | 2.07          |

| Simu.                               |     | 745        | -3.21          | 76          | -0.3          |

| Meas.                               |     | 737        | -3.87          | 78          | -3.11         |

| Calc.                               | ①-③ | 687        | -3.35          | 50          | 2.87          |

| Simu.                               |     | 669        | -3.65          | 56          | 1.1           |

| Meas.                               |     | 667        | -4.9           | 64          | -0.63         |

The slight frequency shifts of NGD center frequency are mainly due to the fabrication inaccuracies, substrate effective permittivity tolerance, and losses versus the numerical computation accuracy.

# C. State of the Art About the BP-NGD Performances

The BP-NGD performances of hybrid and distributed 3-port microstrip Y-circuit are, particularly interesting, compared to the other circuits investigated in [22-24]. First of all, the 3-port BP-NGD circuit is designed and investigated in the first time. Table IV recapitulates the comparison between the NGD center frequency, NGD value, bandwidth and reflection attenuation loss at the NGD center frequency.

TABLE IV COMPARISON OF BP NGD PERFORMANCE

| COMPARISON OF BP NGD PERFORMANCES |        |             |                |             |               |

|-----------------------------------|--------|-------------|----------------|-------------|---------------|

| Ref.                              | Type   | $f_n$ (MHz) | $GD(f_n)$ (ns) | BW<br>(MHz) | $T(f_n)$ (dB) |

| [22]                              | 2-port | 1200        | -2.8           | 13          | -2.2          |

| [23]                              | 2-port | 1150        | -2.2           | 15          | -1.93         |

| [24]                              | 3-port | 550         | -18.12         | 1.35        | -2.95         |

| This work                         | 1-2    | 737         | -3.87          | 78          | -3.11         |

|                                   | 1)-3   | 667         | -4.9           | 64          | -0.63         |

It can be pointed out that compared to the NGD circuits designed in [22-24], the proposed Y-circuit allows to achieve: a) the ability to generate BP-NGD function through both ways ①-② and ①-③, b) a very good attenuation showing low attenuation loss especially through way ①-③, and c) the distributed Y-circuit is merely built with a fully distributed circuit without using any reactive lumped elements.

#### D. Discussion on BP-NGD Application

Today, communication circuits [7-23] are victim of delay attacks. Against this bottlenecking issue of modern technology, the NGD function is well-placed as a best candidate. We are currently developing several applications of the BP-NGD circuits [22-24] for the future communication transceiver system. Following the topic of the present study, we can state the following application. For example, thanks to the NGD Y-circuit design possibility, we can develop a multi-way circuit delay effect reduction.

# 1) Brief Description of Skew Reduction NGD Application

Based on the NGD technique introduced in [25], the skew effect of communication circuit can be reduced. The deontological solution consists of cascading the victim circuit by NGD one. It is well-known that under good matching condition, the total TF is ideally equal to the product of cascaded elementary ones. Because of this property, the positive GD and NGDs of cascaded circuits can be cancelled out each other.

Based on the present research work the delay reduction technique can be extended to multi-port circuit with our multi-way NGD topology. Therefore, one of potential future applications of the proposed 3-port circuit is a) the skew compensation and cancellation; b) signal desynchronization against electrical interconnect trees of electronic and communication system; c) delay difference suppression by using a specifically sized three-port BP-NGD topology; and d) solve problem of signal synchronization.

# 2) Brief Description of Jitter NGD Correction

A feasibility study enables to state that NGD circuits can be applied to correct microwave signal distortion [26]. With such

a technique, the Jitter and associated phase noise of high-speed communication devices due to the interconnections can be corrected by using reconfigurable NGD circuits. The distributed topologies are good candidate for this solution because of possibilities to operate at tens GHz.

## 3) Brief Description of Resonance Effect Reduction

Because of integration density, electric and electronic systems are more and more designed and implemented in confined space which generate undesirably dramatic resonance effects. As reported in [27-28], the NGD function is useful in the EMC engineering as approved by the EM resonance reduction feasibility study. Indeed, the BP NGD circuit can equalize the resonance TF. Then, the magnitude peak and also the GD are naturally attenuated.

#### IV. CONCLUSION

An innovative BP-NGD design method of 3-port topology is investigated. The feasibility study to generate BP-NGD effect through the double output branches is performed. The considered topology is essentially constituted by TL elements with output branch terminated by resistor components. After the recall on the BP-NGD specification, an innovative modelling method of the 3-port circuit is developed. The double branch frequency-dependent VTFs are expressed by means of transfer matrix analysis. Afterwards, the GDs through the 3-port topology transmission ways are expressed in function of the TL parameters.

The validation is carried with POC and prototype implemented in hybrid technology. A challenging VTF measurement technique is described. After successful test, it was found that the BP-NGD function is corroborated by analytical calculation, simulation and measurement results in very good correlation. The BP-NGD performances from the present work are compared with the literature [22-24].

The 3-port circuit BP-NGD applications notably for the future communication system are discussed.

#### REFERENCES

- R. H. Ho, K. W. Mai and M. H. Horowitz, "The future of wires," Proc. of the IEEE, vol. 89, no. 4, pp. 490-504, Apr. 2001.

- [2] N. Rakuljic, and I. Galton, "Tree-structured DEM DACs with arbitrary numbers of levels," IEEE Trans. CAS I, vol. 52, no. 2, pp. 313–322, Feb. 2010

- [3] L. Hungwen, S. Chauchin and L. J. Chien-Nan, "A Tree-Topology Multiplexer for Multiphase Clock System," IEEE Trans. CAS I, vol. 56, no. 1, Feb. 2009, pp. 124-131.

- [4] S. Tawfik and V.Kursun, "Clock Distribution Networks with Gradual Signal Transition Time Relaxation for Reduced Power Consumption," Journal of Circuits, Systems and Computers, vol. 17, no. 6, pp. 1173-1191, Dec. 2008.

- [5] V. Rizzoli, A. Costanzo, F. Mastri and A. Neri, "A general SPICE model for arbitrary linear dispersive multiport components described by frequency-domain data," in Proc. 2003 IEEE MTT-S Int. Microwave Symp. Digest, vol. 1, Philadelphia, PA, USA, 8-13 June 2003, pp. 9-12.

- [6] C-W.A. Tsao and C-K. Koh, "A Clock Tree Router for General Skew Constraints," J. ACM TODAES, Vol. 7, No. 3, Jul. 2002, pp. 359-379.

- [7] Jr. J. L. Wyatt and Q. Yu, "Signal delay in RC meshes, trees and lines," in 1984 Proc. of IEEE ICAD, pp. 15-17.

- [8] N. K. Jain, V.C. Prasad and A.B. Bhattacharyyaa, "Delay-Time Sensitivity in Linear RC Tree," IEEE Trans. CAS, Vol. 34, No. 4, 1987, pp. 443-445.

- [9] P.K. Chan and M.D.F. Schlag, "Bounds on Signal Delay in RC Mesh Networks," IEEE Trans. CAD, Vol. 8, 1989, pp. 581-589.

- [10] A.C. Deng and Y.C. Shiau, "Generic Linear RC Delay Modeling for Digital CMOS Circuits," IEEE Trans. CAD, Vol. 9, No. 4, Apr. 1990, pp. 367-376.

- [11] R. Gupta, B. Tutuianu and L.T. Pileggi, "The Elmore Delay as a Bound for RC Trees with Generalized Input Signals," IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, vol. 16, no. 1, pp. 95-104. Jan. 1997.

- [12] C. V. Kashyap, C. J. Alpert, F. Liu, and A. Devgan, "Closed-form expressions for extending step delay and slew metrics to ramp inputs for RC trees," IEEE Trans. CADICAS I, Vol. 23, No. 4, pp. 509-516, Apr. 2004.

- [13] M.A. Azadpour, T.S. Kalkur, "A clock interconnect extractor for multigigahertz frequencies incorporating inductance effect," IEEE Trans. VLSI Systems, vol. 11, no. 6, pp. 1143-1146, 2003.

- [14] Y. I. Ismail, E. G. Friedman and J. L. Neves, "Equivalent Elmore delay for RLC trees," IEEE Trans. CAD, Vol. 19, No. 1, Jan. 2000, pp. 83-97.

- [15] A. B. Kahng and S. Muddu, "An analytical delay model of RLC interconnects," IEEE Trans. Computed-Aided Design Vol. 16, pp. 1507-1514, Dec. 1997.

- [16] M.A. El-Moursy and E.G. Friedman, "Exponentially Tapered H-Tree Clock Distribution Networks," IEEE Trans. VLSI Systems, Vol. 13, No. 8, 2005, pp. 971-975.

- [17] J. Rosenfeld and E.G. Friedman, "Design Methodology for Global Resonant H-Tree Clock Distribution Networks," IEEE Trans. VLSI Systems, Feb. 2007, Vol. 15, No. 2, pp. 135-148.

- [18] I. Chanodia and D. Velenis, "Parameter Variations and Crosstalk Noise Effects on High Performance H-Tree Clock Distribution Networks," Analog. Integr. Circ. Sig. Process., Ed. Springer Netherlands, Vol. 56, 2008, pp. 13-21.

- [19] W.-K. Loo, K.-S. Tan, and Y.-K. Teh, "A Study and Design of CMOS H-Tree Clock Distribution Network in System-on-Chip," in Proc. 8th IEEE Int. Conf. ASIC, Changsha, Hunan, China, Oct. 2009, pp. 411-414.

- [20] B. Ravelo, "Behavioral model of symmetrical multi-level T-tree interconnects," Progress In Electromagnetics Research (PIER) B, Vol. 41, 2012, pp. 23-50.

- [21] B. Ravelo and O. Maurice, "Kron-Branin Modeling of Y-Y-Tree Interconnects for the PCB Signal Integrity Analysis," IEEE Tran. EMC, Vol. 59, No. 2, Apr. 2017, pp. 411-419.

- [22] F. Wan, N. Li and B. Ravelo, "O=O Shape Low-Loss Negative Group Delay Microstrip Circuit," IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 67, No. 10, Oct. 2020, pp. 1795-1799.

- [23] B. Ravelo, F. Wan, N. Li, Z. Xu, P. Thakur, and A. Thakur, "Diakoptics Modelling Applied to Flying Bird-Shape NGD Microstrip Circuit," IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 68, No. 2, Feb. 2021, pp. 637-641.

- [24] F. Wan, Y. Liu, J. Nebhen, Z. Xu, G. Chan, S. Lalléchère, R. Vauche, W. Rahajandraibe and B. Ravelo, "Bandpass Negative Group Delay Theory of Fully Capacitive Δ-Network," IEEE Access, Vol. 9, No. 1, pp. 62430 62445, Apr. 2021.

- [25] F. Wan, X. Miao, B. Ravelo, Q. Yuan, J. Cheng, Q. Ji, and J. Ge, "Design of Multi-Scale Negative Group Delay Circuit for Sensors Signal Time-Delay Cancellation," IEEE Sensors Journal, Vol. 19, No. 19, Oct. 2019, pp. 8951-8962.

- [26] B. Ravelo, W. Rahajandraibe, Y. Gan, F. Wan, N. M.Murad and A. Douyère, "Reconstruction Technique of Distorted Sensor Signals with Low-Pass NGD Function," IEEE Access, Vol. 8, No. 1, Dec. 2020, pp. 92182-92195.

- [27] B. Ravelo, F. Wan, J. Nebhen, W. Rahajandraibe, and S. Lalléchère, "Resonance Effect Reduction with Bandpass Negative Group Delay Fully Passive Function," IEEE Tran. CAS II: Express Briefs, Vol. 68, No. 7, July 2021, pp. 2364-2368.

- [28] B. Ravelo, S. Lalléchère, W. Rahajandraibe, and F. Wan, "Electromagnetic Cavity Resonance Equalization with Bandpass Negative Group Delay," IEEE Tran. EMC, Vol. 63, No. 4, Aug. 2021, pp. 1248-1257.

**Prof. Dr. Blaise RAVELO** (M'09) is currently University Full Professor at NUIST, Nanjing, China. His research interest is on Multiphysics and electronics engineering. He is a pioneer of the negative group delay (NGD) concept. He is member of IET Electronics Letters editorial board as circuit & system subject editor with Google scholar hindex(2022)=24 and i10-index(2022)=75. He is ranked in Top 2% world's scientists based on years (2020-2021). He was research director of 11 PhD students (10 defended), postdocs, research engineers and Master internships.

Address: Blaise RAVELO, N219, Ningliu Rd, Pukou District, Nanjing China, Nanjing University of Information Science and Technology, Electronics and Information Engineering college

Phone: +33 6 45 33 47 22

Email: blaise.ravelo@yahoo.fr

Dr. Alexandre Douyère received received his Ph.D. degrees in electronics and microwaves engineering from the University of La Reunion, Reunion Island, France, in 2008. From 2009, he is an Assistant Professor at the University of La Reunion. He was the scientific responsible of research projects titled FEDER CARERC2... His research interest includes wireless power transfer (WPT) and energy harvesting, nonlinear devices, innovative RF measurements, and low-power microwave and millimeter wave conversion circuits. He is a member of the organizing committee for the IEEE RADIO conference and a member of IEEE SIGHT project named ACTION since 2016.

Address: Alexandre Douyère, LE2P/Energy-Lab, University of la Reunion, 97400 La Reunion Island, France

• Phone: +262 692 18 82 42

Email: alexandre.douyere@univ-reunion.fr

Province, P. R. China. He received the B. Sc. degree in technics of control, measurement and instrumentation from Dalian University of technology, Dalian, P. R. China in July 2004, another B. Sc. degree in electronic engineering from University of Pierre and Marie Curie (UPMC), Paris, France in July 2007, the M. Sc. Degree in electronic engineering from UPMC, France in July 2009 and the Ph. D. degree at IRSEEM/ESIGELEC from University of Rouen, France, in October 2012.

Address: Yang LIU, Altran, 78140 Vélizy-Villacoublay, France

• Phone: +33 6 17 01 04 29

• Email: liuyang2101@gmail.com

Dr. Fayu WAN (M'11, SM'22) received the Ph.D. degree in electronic engineering from the University of Rouen, Rouen, France,

in 2011. From 2011 to 2013, he was a Postdoctoral Fellow with the Electromagnetic Compatibility Laboratory, Missouri University of Science and Technology, Rolla. He is currently a Full Professor with the Nanjing University of Information Science and Technology, Nanjing, China. His current research interests include negative group delay circuits, electrostatic discharge, electromagnetic compatibility, and advanced RF measurement.

- Contact Information: Fayu WAN, N219, Ningliu Rd, Pukou District, Nanjing China, Nanjing University of Information Science and Technology, Electronics and Information Engineering college

- Tel: +86-25-58731332

- Email: fayu.wan@nuist.edu.cn

**Prof. Dr. Wenceslas RAHAJANDRAIBE** is currently professor at the University of Aix-Marseille. He heads the Integrated Circuit Design group of the IM2NP laboratory. His research is focused on the design of Analog and RF IC's for telecommunication systems and for smart sensor ultra-low power IC interfaces. He is an expert for the ANR, the French Agency for Research. He has served on program committees of IEEE NEWCAS and ICECS. He has been and is a reviewer of

contributions submitted to several IEEE conferences and journals such as ISACS, NEWCAS, MWSCAS, ESSCIRC, ESSDERC, RFIC, IEEE Transactions on Circuits and Systems I and II, IET Electronics Letters.

Address: Wenceslas RAHAJANDRAIBE, 60 Rue Enrico Fermi, Bat.Neel, 13453 Marseille, Cedex 13, France

• Phone: (+33)413554026

• Email: wenceslas.rahajandraibe@im2np.fr

Mr. George CHAN (S'06, M'08, SM'18) received the BEng (Hons) degree in Electronic and Communication Engineering from City University of Hong Kong and MSc degree in Electronic and Information Engineering from Hong Kong Polytechnic University. He is a Senior Product Safety Engineer in ASM Pacific Technology Ltd. His research interests include: electromagnetic safety, EMC measurement and EMC management. He has coauthored several technical publications in international journals and conference proceedings. He is a member of IEEE EMC society TC1 on EMC Management. He is also a member of the IEEE International Committee for Electromagnetic safety (ICES) Standards Coordinating Committee (SCC39) and a TC95 subcommittee member. He is an International Electrotechnical Commission (IEC) expert and Committee Member of IEC TC106/PT63184 on Method for the assessment of electric, magnetic and electromagnetic fields associated with human exposure.

Address: George CHAN, ASM Pacific Technology Ltd., 19/F Gateway ts, 8 Cheung Fai Rd, Tsing Yi, Hong Kong

• Phone: +852 2619 2000

• Email: george.chan@asmpt.com

**Dr. Mathieu GUERIN** obtained an engineering degree in Microelectronics and Telecommunications from Polytech Marseille in 2010 and at the same time a Research Master in Integrated Circuits Design from the University of Aix-Marseille. He obtained his PhD degree from the

same institution in 2013. He worked as technical leader of the analog and radio-frequency design team of IDEMIA-StarChip for five years and designed chips embedded in SIM cards and contactless bank cards with biometric recognition. He joined Aix-Marseille University as an Assistant Professor in 2020 and joined the CCSI team of the IM2NP laboratory. His research focuses mainly on the design and synthesis of circuits in digital electronics. He is also working on methods of modelling and characterizing circuits in analog electronics.

Address: Mathieu Guerin, 60 Rue Enrico Fermi, Bat. Neel, 13453 Marseille, Cedex 13, France

• Phone: (+33)413554026

Email: mathieu.guerin@univ-amu.fr