## From low-level fault modeling (of a pipeline attack) to a proven hardening scheme

Sébastien Michelland, Christophe Deleuze, Laure Gonnord

#### ▶ To cite this version:

Sébastien Michelland, Christophe Deleuze, Laure Gonnord. From low-level fault modeling (of a pipeline attack) to a proven hardening scheme. Compiler Construction (CC'24), Mar 2024, Edinburgh (Scotland), United Kingdom. 10.1145/3640537.3641570. hal-04438994v2

### HAL Id: hal-04438994 https://hal.science/hal-04438994v2

Submitted on 28 Jun 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# From Low-Level Fault Modeling (of a Pipeline Attack) to a Proven Hardening Scheme\*

#### Sébastien Michelland

sebastien.michelland@lcis.grenobleinp.fr UGA, Grenoble INP, LCIS Valence, France

#### Christophe Deleuze

christophe.deleuze@grenoble-inp.fr UGA, Grenoble INP, LCIS Valence, France

#### Laure Gonnord

laure.gonnord@grenoble-inp.fr UGA, Grenoble INP, LCIS Valence, France

#### **Abstract**

Fault attacks present unique safety and security challenges that require dedicated countermeasures, even for bug-free programs. Models of these complex attacks are made workable by approximating their effects to a suitable level of abstraction. The common practice of targeting the Instruction Set Architecture (ISA) level isn't ideal because it discards important micro-architectural information, leading to weaker security guarantees. Conversely, including micro-architectural details makes countermeasures harder to model and reason about, creating a new challenge in validating and trusting protections.

We show that a semantic approach to modeling faults makes micro-architectural models workable, and enables precise cooperation between software and hardware in the design of countermeasures. We demonstrate the approach by designing and implementing a compiler/hardware countermeasure, which protects against a state-of-the-art pipeline fetch attack that generalizes multi-fault instruction skips. Crucially, we provide a formal security proof that guarantees faults are detected by the end of every basic block. This result shows that carefully embracing the complexity of low-level systems enables finer, more secure countermeasures.

CCS Concepts: • Software and its engineering  $\rightarrow$  Semantics; Software notations and tools; • Security and privacy  $\rightarrow$  Formal methods and theory of security.

*Keywords:* Compilation, semantics of fault models, security proofs, co-design

#### **ACM Reference Format:**

Sébastien Michelland, Christophe Deleuze, and Laure Gonnord. 2024. From Low-Level Fault Modeling (of a Pipeline Attack) to a

\*This work has been partially funded by the ARSENE project of the "France 2030" government investment plan managed by the French National Research Agency, under the reference ANR-22-PECY-0004.

CC '24, March 2-3, 2024, Edinburgh, United Kingdom

© 2024 Copyright held by the owner/author(s). Publication rights licensed to ACM.

This is the author's version of the work. It is posted here for your personal use. Not for redistribution. The definitive Version of Record was published in *Proceedings of the 33rd ACM SIGPLAN International Conference on Compiler Construction (CC '24), March 2–3, 2024, Edinburgh, United Kingdom*, https://doi.org/10.1145/3640537.3641570.

Proven Hardening Scheme. In *Proceedings of the 33rd ACM SIGPLAN International Conference on Compiler Construction (CC '24), March 2–3, 2024, Edinburgh, United Kingdom.* ACM, New York, NY, USA, 23 pages. https://doi.org/10.1145/3640537.3641570

#### 1 Introduction

An attacker with access to a physical device can perform fault injection attacks. Physical interference such as a clock glitch, a power supply voltage glitch, or an electromagnetic pulse, can cause hardware to behave erroneously [4], sometimes just enough to bypass an application's security. The development of fault injection attacks [30] makes them a tangible threat to modern safety- and security-critical systems. Countering them is uniquely challenging due to the unpredictable effects of low-level interference on high-level security properties — a leap that traditional development tools meticulously avoid by building upon a clean abstraction stack from hardware to programming languages.

In order to conquer the complexity of these attacks, security engineers construct *fault models* by approximating faults' effects to a desired level of abstraction. These span from bit flips in RTL (Register Transfer Level) latches [32] to failures in pipeline forwarding [21] to corrupted ISA registers [7] and branch inversion directly in source code [28]. Countermeasures are then based on these models, so in a sense secure programs resist *fault models* rather than *faults*. The clear trade-off is one of accuracy versus simplicity; low-level descriptions are more true to practical attacks, but high-level approximations make it practical (in many cases *possible*) to reason about and protect against them.

In practice, most existing works study faults at the ISA level, based on mis-executions of assembler programs (instruction skips, wrong jumps, corrupted registers, etc. [18]), with countermeasures as *transformations* of assembler programs. This is a natural choice as assembler is the lowest software abstraction, and dealing with software has benefits such as ease of deployment, board-independence, compiler automation, and the ability to protect only critical sections of programs (compared to fixed costs in e.g. die surface). Hardware protections [19] are less common, but better equipped to deal with local and remote side-channel attacks [31], which share many aspects with fault attacks (see f.i. [35]).

The key issue with ISA-level fault models is that the approximation is quite crude; [22] shows that faulted behaviors often depend on micro-architectural features and cannot be described accurately without including hardware details. Pipeline analysis in [37] further shows that targeted fault attacks can and do defeat many ISA-level countermeasures by exploiting unmodeled low-level effects.

Naturally, using low-level models widens the *abstraction gap* between the attack and the countermeasure (often applied during compilation at an IR or back-end level). This creates a risk that protections could be altered or defeated by the compiler's late stages. These cross-layer concerns (commonly avoided by disabling optimizations or basing security claims on exhaustive injection campaigns) resurface when attempting to formally prove a countermeasure's security.

The issue of proving security for countermeasures at the ISA level or lower has received little attention compared to traditional testing. Works that reach proven levels of security usually focus on specific boards (e.g. RTL model checking in [32]) or high-level languages (e.g. symbolic analysis in [28]). Proving traditional countermeasures would provide an appropriate response to [37] by guaranteeing the absence of attack opportunities, across multiple abstraction layers starting at the micro-architectural level.

This approach contrasts with recent progress in working out sophisticated hardening schemes that combine multiple types of protections or resist multiple consecutive or independent attacks (*multi-fault attacks*) [14, 34]. The applicability of these solutions still hinges on ISA-level fault models adequately capturing faults' effects, which is not guaranteed. To ensure security at a lower abstraction level, we choose to refocus on single but accurate models, which we address with a software/hardware co-design approach.

Contribution summary. We present the first formally-proven countermeasure addressing a low-level fault model. We formalize the fault in an extended assembler language in Section 2, then propose in Section 3 a countermeasure based on a hardware extension and a compile/link-time program transformation. From the formal semantics for the fault, we derive a security theorem in Section 4. We implement the scheme in LLVM and GNU 1d, then evaluate its security with emulated fault campaigns and its performance with processor simulations in Section 5. Finally, we compare this work with recent literature in Section 6, and conclude in Section 7. The long version of this article contains a detailed operational semantics of the extended assembler and the complete proof of the security theorem.

#### 2 Formal Description of Fetch Skips

We protect against a slightly generalized version of the fault model described by [3], adapted for RISC-V<sup>1</sup>. The target system is a 32-bit little-endian RISC-V processor with the "C"

```

int g(int x) { return f(x) + 1; }

g:

# ▼ Push register ra to stack

24: 41 11

c.addi sp, sp, -16

26: 06 c6

C.SW

ra, 12(sp)

# ▼ Call f (linker later inserts address of f)

\# ▼ ra is both target address and return address

28: 97 00 00 00

auipc

ra, 0

jalr

2c: e7 80 00 00

ra, 0(ra)

# ▼ Add 1 to return value a0 of f

30: 05 05

c.addi a0, a0, 1

# ▼ Pop ra from stack and return a0

32: b2 40

c.lw

ra, 12(sp)

34: 41 01

c.addi

sp, sp, 16

36: 82 80

c.ret

24:

C.SW

c.addi

auipc (1/2)

auipc (2/2)

28:

2c:

jalr (1/2)

jalr (2/2)

30:

c.addi

c.lw

34:

c.addi

c.ret

```

**Figure 1.** C code, object code, and memory layout of a simple function g(x) = f(x) + 1.

extension for compressed instructions (such as RV32IC [1]), which means it has a mix of 16-bit and 32-bit instructions.

The instruction set includes the usual arithmetic instructions (add, xor...), memory instructions (lw, sw...), conditional (beq...) and unconditional (j, jal...) branches. All instructions have a 32-bit encoding unless prefixed with "c.", which denotes a 16-bit encoding from the "C" extension.

For brevity, we use "aligned" to mean a multiple of 4 (bytes) and "unaligned" for a multiple of 4 plus 2. We also use the term "line" to refer to 4 bytes of data at an aligned address.

#### 2.1 RISC-V Programs and Their Execution

This section introduces the notions needed to describe the fault and state the security theorem in Section 4.

We model RISC-V programs as collections of *blocks* made of non- or conditionally-branching instructions, terminated by an unconditional branch.<sup>2</sup> Figure 1 shows a function g(x) = f(x) + 1 consisting of two blocks, one that calls f (implicitly forwarding the argument) and one that increments the return value a0 then returns.

We model the execution as a sequence of *execution steps* in which the CPU obtains the next instruction (with a combination of a buffer read and/or a memory fetch), decodes it,

<sup>&</sup>lt;sup>1</sup>RISC-V is an open standard ISA; details can be found at https://riscv.org.

<sup>&</sup>lt;sup>2</sup>These aren't classical basic blocks; not counting conditional branches as terminators works better for this fault. This is of minor importance except in the security proof.

and executes it. For instance, function g in Figure 1 executes in 8 steps (ignoring the call to f), with each step running one instruction and consuming either 2 or 4 bytes of code.

The central behavior of interest in this paper is that *there* is not always one fetch for one step: certain instructions are fetched in advance, and others are read by the CPU over two consecutive fetches. This is because most CPUs always fetch 4 aligned bytes in memory, that is, a line in the memory layout table. For example, the first step in running g fetches the 4 bytes at address 24 and puts them in a decoding buffer, but only consumes the first 2 to execute c.addi. Then, the second step executes c.sw from the buffer without needing another memory fetch.

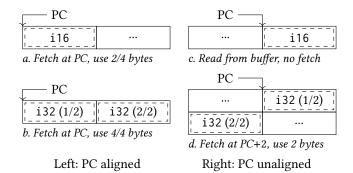

Figure 2 shows all the ways a step may use buffered data and/or fetch from memory when executing one instruction. When PC is aligned (left), the next instruction is on a new line, so a fetch is performed. When PC is unaligned (right), 2 bytes of instruction data are left in the decoding buffer. If they form a 16-bit instruction (case c), the CPU runs it immediately without a fetch. If they form the first half of a 32-bit instruction (case d), a fetch is performed at PC + 2 to obtain the second half and piece together the opcode. Each step then increments PC by 2 or 4, setting up the next cycle.

#### 2.2 Fault Model

We are interested in protecting programs against "fetch skip" attacks described by [3]. Fetch skips refine the traditional instruction skip fault model by analyzing the effect of physical attacks (here, clock glitches) on the micro-architecture rather than on the program only. The proposed fault model captures 80% of the observed behaviors under clock glitches attack ([2]). Because the model is more accurate with respect to physical effects, a countermeasure against fetch skips will be more secure in practice than a countermeasure against plain instruction skip.

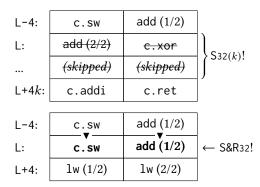

The different types of fetch skips are illustrated in Figure 3. In this model, attempts by the CPU to fetch at an address L may result in:

- **Skip 32 bits**, k times (S<sub>32</sub>(k)): Instead of returning the memory contents at address L, the memory contents at address L + 4k are returned, and PC is incremented by 4k.<sup>3</sup>

- Skip and repeat 32 bits (S&R32): The contents at address L are requested from memory, but due to the short cycle the decoding stage triggers before the response is available. A copy of the previous line (usually at L 4) is returned to the decoder for the current step, and the requested value arrives in the decoding buffer later.

**Figure 2.** Execution step patterns. i16/i32 represent arbitrary 16/32-bit instructions. The dashed region is the next instruction to be run.

**Figure 3.** Effect of fetch skip attacks on fetch requests.

Forged opcode executed by CPU (nonsensical):

add (1/2) lw (1/2)

Figure 4. Forging a 32-bit instruction with a S<sub>32(1)</sub> attack.

We consider a "level N attacker" that can independently attack every fetch with either one S32(k) attack (1  $\leq k \leq N$ ) or one S&R32 attack.<sup>4</sup>

The connection between fetch skips and the memory layout of instructions creates a new effect, which we call **instruction forging** and illustrate in Figure 4, that cannot be captured by the usual "instruction skip" model. Here, PC = L - 2 and the decoding buffer contains the first half of a 32-bit unaligned add instruction. The CPU fetches at L to obtain the second half (Figure 2, case d). Attacking this fetch with S32(1) results in an unrelated 16-bit value (the start of an lw) being used to complete the add, causing the execution of an opcode not originally in the program. This opcode can be "anything" (including illegal). [3] demonstrate

$<sup>^3</sup>$ [3] observes that a the CPU may run a nop during a S32(k) attack; we omit this detail here but account for it in the countermeasure.

$<sup>^4</sup>$ We use these patterns because the behavior of more complex combinations cannot be inferred from [3] without more hardware details.

| Name            | Rule statement                                        |  |  |  |

|-----------------|-------------------------------------------------------|--|--|--|

| NoFault         | $(PC, \rho) \ a \Rightarrow [a] \ (PC, [a])$          |  |  |  |

| S32( <i>k</i> ) | $(PC, \rho) \ a \Rightarrow [a+4k] \ (PC+4k, [a+4k])$ |  |  |  |

| S&R32           | $(PC, \rho) \ a \Rightarrow \rho \ (PC, [a])$         |  |  |  |

**Figure 5.** Short description of fetch rules.

$(PC, \rho)$   $a \Rightarrow d$   $(PC', \rho')$  indicates that the fetch of address a with current PC and  $\rho$  returns value d to the decoder, along with updated state  $PC', \rho'$ . [a] denotes the memory contents at address a.

how this enables new vulnerabilities (e.g. by forging control flow instructions).

Once PC is out of sync, forging can continue without repeated fault injection. Continuing with Figure 4, after running the forged instruction we get PC = L + 6. Now the second half of lw is interpreted as its own 16-bit or (first half of) 32-bit instruction. Thus, the attack carries over to the next line; in the worst case, execution might not resynchronize with the intended sequence of instructions until a jump.

#### 2.3 Program Model

To design and prove a countermeasure against such a low-level attack, it is helpful to reflect the faults' effects into language features, and study the updated language with semantic tools. In this section, we build a language model that captures the memory layout of instructions while ignoring most concrete effects (apart from jumps and select registers).

**Syntax.** A *program* is a collection of *blocks*. A block bb is a sequence of *instructions* bb =  $[i_1, ..., i_{|bb|}]$  where each instruction  $i_j$  is a 16-bit or 32-bit value, representing an assembler instruction encoded as described by the RISC-V ISA (or, as will be described in Section 3.2, a 32-bit "checksum literal"). We write  $\|i\|$  for the size in bytes of instruction i (which is either 2 or 4).

**Program state.** Due to the stateful nature of S&R32, which duplicates the "previous" fetched line, a full description of the program state must include the decoding buffer. We model this state with a 4-tuple  $\langle PC, \rho, \sigma, \alpha \rangle$ , containing:

- The current PC value (always a multiple of 2);

- $\rho$ , the last 4-byte value fetched by the CPU (decoding buffer).  $\rho$  is used to decode at unaligned PCs (Figure 2, right) and replaces the targeted line during a S&R32 attack;

- $\sigma$ , the values of the XCCs registers associated with our countermeasure, whose role is described in Section 3.2;

- $\alpha$ , the rest of the architectural state (other registers, memory...), which we abstract away as an opaque value.

The attacks shown in Figure 3 are formalized in terms of this state in Figure 5. To illustrate alignment dynamics, attacking the fetch at 0x30 during the execution of g (just upon returning from f) produces the following execution:

```

g: # PC >= 0x40000 is a protected region

400e4: 41 11

c.addi

sp, sp, -1

400e6: 06 c6

ra, 12(sp)

C.SW

# ▼ auipc was relocated

400e8: 97 00 00 00

auipc

ra, 0

# ▼ Checksum was set and LSB flipped

400ec: 0b 64 00 00

ccscallb 8

(22, 10)

400f0: e2 75 06 c6

.word

0xc60675e2

(22, 11)

# ▼ jalr was relocated

400f4: e7 80 00 fb

jalr

ra, -80(ra)

400f8: 02 90

c.ebreak # 8 times

(28)

40108: 05 05

c.addi

a0, a0, 1

4010a: b2 40

c.lw

ra, 12(sp)

4010c: 41 01

c.addi

sp, sp, 16

4010e: 01 00

c.nop

(19)

# ▼ Checksum was set, no flip needed

40110: 0b 10 00 00

ccs

(24, 13)

40114: 51 16 b3 40

0x40b31651

.word

(24, 14)

40118: 82 80

c.ret

4011a: 02 90

c.ebreak # 8 times

(28)

```

**Figure 6.** Linked object code for g after hardening (N = 2). Numbers on the right refer to lines of Algorithm 1 that added the instructions.

```

\langle 0 \times 30, \rho_0, \sigma_0, \alpha_0 \rangle

| S_{32(1)}: (0 \times 30, \rho_0) \ 0 \times 30 \Rightarrow [0 \times 34] \ (0 \times 34, [0 \times 34])

| Run instruction: c.addi sp, sp, 16

\langle 0 \times 36, \rho_1 = [0 \times 34], \sigma_1, \alpha_1 \rangle

| No fetch. Run instruction: c.ret

\langle \alpha_1.ra = 0 \times 30, \rho_2 = \rho_1, \sigma_2, \alpha_2 \rangle

```

c.ret jumps to the address stored in register ra, which is still 0x30 because we skipped the load from the stack, later leading to a typical stack corruption crash.

#### 3 A Co-designed Countermeasure

In this section, we propose a software/hardware countermeasure, based on code instrumentation with hardware support.

#### 3.1 Overview

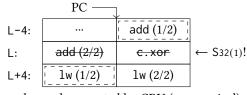

The key ideas of the countermeasure are as follows. Machine code is augmented ("hardened") during compilation with checksum protections that react to a fault attack by forcing execution to trap before the end of the current block. This limits exploits by ensuring a sufficiently tight window between attack and detection (like most countermeasures it doesn't prevent side-effects immediately resulting from the fault, which is inherently difficult due to timing). Figure 6 shows the hardened code for the g function from Figure 1.

Hardware is modified to automatically maintain a running checksum (in fact, a simple *sum*) of every line of instruction data fetched from memory during the execution of a block, independent of instruction alignment. Blocks are compiled so

that every exit is guarded by a ccs instruction (from our ISA extension), which traps if the running checksum is not equal to a reference value computed at compile-time. Blocks thus act as autonomous "jails", in that faulty executions causing the checksum to deviate from its expected value cannot leave their current block.

The co-designed nature of the countermeasure is a result of the cross-checking of information between hardware, whose monitoring produces a trace (checksum) sensitive to fault attacks, and software, which provides reference checksum values to interpret that trace.

Section 3.2 describes the hardware extension that we rely on for the countermeasure. 3.3 details the hardening algorithm. 3.4 highlights the subtleties of implementing the hardening algorithm in LLVM. Finally, 3.5 discusses the design choices in a more general context.

As always, one can attempt to attack the countermeasure itself. The security theorem in Section 4 proves that no attempt at skipping, repeating or forging ccs instructions or jumps can succeed, leading to a strong security guarantee.

#### 3.2 ISA and Hardware Extensions

We support the countermeasure with a custom ISA extension named Xccs for *Code CheckSum*<sup>5</sup>. Throughout this section, all examples refer to Figure 6, and u<sub>N</sub> denotes the type of N-bit unsigned integers.

Xccs introduces four new Control and Status Registers (CSR), which together form the  $\sigma$  field of the program state:

- CCS:  $u_{32}$  is the running checksum for the current block. For example, the region of g from address 40108 through 40114 adds up in little-endian to  $0\times40b20505 + 0\times00010141 + 0\times0000100b = 0\times40b31651$  so the value of CCS at 40114 will be  $0\times40b31651$  if no attack is performed.

- CCSPROT: u<sub>32</sub> indicates the PC value at which a protected instruction (jump) is expected to execute. It is zero most of the time and non-zero for a single step after a checksum is validated. In Figure 6, it is set at 400f4 and 40118.

- CCSD: {E: u<sub>1</sub>, J0: u<sub>5</sub>} holds control information; the *enable* bit (E) indicates whether checksum protection is active for the current block (which currently is whenever PC ≥ 0x40000), and the *jump offset* field (J0) is set by ccscall as described below.

- CCSDS: u<sub>32</sub> ("delay slot") is used to implement the decoding of Xccs instructions' 32-bit checksum arguments.

The meat of Xccs is the addition of four guard instructions whose encoding is shown in Figure 7, all of which are followed by a 32-bit **(checksum)** argument:

• ccs (checksum) compares the CCS register with the provided argument and traps if they differ. Otherwise, it sets CCSPROT = PC + 8 so a jump or function call can execute at the next step. For instance, at 40114 in Figure 6,

| 31 25  | 24 20 | 19 15 | 14 12  | 11 7 | 6 0    |            |

|--------|-------|-------|--------|------|--------|------------|

| funct7 | rs2   | rs1   | funct3 | rd   | opcode |            |

| 0      | 0     | 0     | 001    | 0    | XCCS   | ccs        |

| 0      | 0     | 0     | 010    | N    | XCCS   | ccscall N  |

| 0      | 0     | 0     | 101    | 0    | XCCS   | ccsb       |

| 0      | 0     | 0     | 110    | N    | XCCS   | ccscallb N |

Figure 7. Xccs instructions (32-bit). XCCS is 0001011.

the dynamic value of the CCS register is compared to 0x40b31651. When no faults are injected, these are equal, so execution proceeds to the c.ret instruction.

- **ccscall** N (**checksum**) is similar; it is used before function calls. It sets CCSD.JO = N, which causes the next function call's return address to increase by 2N bytes. For instance, the ccscallb 8 at 400ec changes the return address after the jalr (call) instruction from 400f8 to 40108, skipping over the c.ebreak block.

- ccsb and ccscallb are variations that flip the least significant bit (LSB) of the checksum before comparing it. This is leveraged to ensure that no (checksum) argument decodes as a jump or Xccs instruction, as detailed in Section 3.3. Again with Figure 6, the sum of the first block up to 400f0 is 0xc60675e3, but that decodes as a bltu, creating a vulnerability. The LSB is flipped to avoid this.

All Xccs instructions further trap when run at unaligned PC, which prevents most attempts at forging them. Finally, existing CPU behavior is modified as follows:

- All branch instructions trap if PC ≠ CCSPROT. If a branch occurs, CCS and CCSPROT are reset to 0.

- 2. Every other instruction traps if CCSPROT  $\neq 0$ .

- 3. Every value retrieved from a fetch is added to CCS.

- 4. Call instructions add 2 × CCSD.J0 to the return address and clear CCSD.J0 before jumping.

Hardware support in this countermeasure serves an important dual purpose: it enforces the jail, and it updates the checksum through a system that is not vulnerable to attacks, so that checks of the trusted CCS value can be guaranteed even though the reference (**checksum**) is itself vulnerable.

#### 3.3 Hardening Algorithm

Algorithm 1 shows the hardening process for a single block in pseudocode, with our canonical example in Figure 6. (As all blocks are independent, this algorithm is executed by the compiler for every block in the program.)

The main **for** loop (line 15) iterates over the instructions of the original block. All instructions are copied to the hardened block (line 26). Jump instructions are preceded by a guard, which is ccscall/ccscallb (line 22) for function calls and ccs/ccsb for other jumps (line 24). nops are used to ensure that guards are aligned and jumps are always separated by at least one non-jump instruction, both of which prevent subtle attacks against the countermeasure.

<sup>&</sup>lt;sup>5</sup>The "X" is standard notation for unofficial RISC-V extensions.

$(\ldots)$

auipc

word

ccscall

# push ra

0x00000000

ra, 0

g: e4: 41 11 06 c6

e8: 97 00 00 00

ec: 0b 24 00 00

f0: 00 00 00 00

# ▼ R\_RISCV\_CHECKSUM: g

Calling convention: a0 serves as both argument and return value for f and g. ra is used for function calls and is caller-saved (push/pop omitted).

```

f4: e7 80 00 00

jalr

ra, 0(ra)

g: (...) # push ra to stack

1 g: (...) # push ra

f8: 02 90

c.ebreak # 8 times (2N+4)

PseudoCALL @f

PseudoCALL @f, .LBB1_0

.LCCS_Region_Start0:

# ^a0 forwarded implicitly

PseudoCCSTRAP 2

108: 05 05

a0, a0, 1

c.addi

10a: b2 40 41 01

(\ldots)

# pop ra

5 .LCCS_Region_Start0:

10e: 01 00

# ccs alignment

c.nop

5

a0 = nsw ADDI a0, 1

a0 = nsw ADDI a0, 1

6

110: 0b 10 00 00

ccs

(...) # pop ra

(...) # pop ra from stack

# ▼ R_RISCV_CHECKSUM: .LCCS_Region_Start0

CCS .LCCS_Region_Start0

0x00000000

8

114: 00 00 00 00

.word

PseudoRET $a0

PseudoRET $a0

118: 82 80

9

c.ret

PseudoCCSTRAP 2

10

10

11a: 02 90

c.ebreak # 8 times

(a) Machine IR before back-end pass.

(b) Machine IR after back-end pass.

(c) Object code before linking.

```

**Figure 8.** Stages of hardening the program from Figures 1 and 6 (N = 2) in our LLVM implementation.

The second **for** loop (line 27) adds a barrier of c.ebreak instructions, which raise a distinctive exception when executed. Their role is to prevent control from leaving the block by skipping over the terminator. Up to 2N+4 are needed to address the worst case where control reaches the middle of a checksum whose second half is a 32-bit opcode, in which an attack of a S&R32 followed by a S32(N) would reach 4N+6 bytes past the checksum.

Procedure addToBlock appends instructions to the hardened block while computing the reference checksum value sum by summing instruction's opcodes. This accounts for instructions' alignment with the function

$$\mbox{realign(offset,i)} = \begin{cases} \mbox{i if offset} \equiv 0 \ [4] \\ 2^{16} \mbox{LSH(i)} + \mbox{MSH(i)} \mbox{ otherwise} \end{cases}$$

where LSH, MSH:  $u_{32} \rightarrow u_{16}$  are the Most and Least Significant Halves respectively. This process is equivalent to summing the lines of the final layout table. Finally, addChecksum selects whether to use ccs/ccscall or their -b variants. The -b variants are selected when the checksum value is an "invalid checksum literal", i.e. it decodes as a jump, Xccs instruction or c.ebreak. Such values could be misused as instructions if an attacker were to skip the guard that precedes it. Flipping the LSB ensures that these sensitive values do not appear in code. Our running example in Figure 6 is obtained by executing this algorithm on both blocks of g's original code from Figure 1 and linking it.

#### 3.4 LLVM Implementation

Algorithm 1 cannot be implemented as-is in a single pass in a standard compiler, because reference checksum values depend on the exact bit-level encoding of each instruction, which is not decided until the linker relocates references to globals and functions. See for instance how the call in Figure 8c (before linking) has placeholder zero-offsets but the one in Figure 6 (after linking) has a proper target offset.

We see this as a benign occurrence of a fundamental issue: the progressive lowering that standard toolchains go through is designed around *functional* invariants, not *security* invariants. Encodings are decided late because they don't matter to the compiler, which is only interested in the functional specification of instructions. The addition of a security countermeasure to the compiler breaks this assumption and creates a new concern in *threading the security transform through the abstraction gap of a functional lowering*.

In this case, we are able to implement the algorithm in two steps: a late Machine IR<sup>6</sup> pass followed by an extension to the linker relocation process.

- Machine IR pass: the program's Machine IR representation is first transformed late in the back-end (from Figure 8a to Figure 8b). This pass handles all tasks that *add* code into the program, including:

- Aligning functions and blocks to 4-byte boundaries;

- Adding aligned Xccs instructions before all Machine IR instructions that expand into RISC-V jumps, such as PseudoRET. A label indicates the start of the region that the checksum must cover;

- Adding the trap barrier with the PseudoCCSTRAP N pseudo-instruction, which later expands into a series of 2N + 4 c.ebreak instructions.

At this stage some jumps are still hidden in pseudo-instructions, like the function call in PseudoCALL. This is because far jumps in RISC-V are implemented with a pair of instructions, auipc and a jump, to overcome the limited distance that can be encoded into single jump instructions.

$<sup>^6</sup>$ The back-end intermediate representation used by LLVM, which is aware of the target architecture, not the usual LLVM IR.

#### Algorithm 1 Algorithm: HARDEN

```

Input: A source block [i_1, ..., i_n]

Input: Upper bound N for S32(k) rule (k \le N)

Output: A hardened block hb.

1: hb ← []

2: sum : u_{32} \leftarrow 0

3: offset \leftarrow 0

▶ Blocks are 4-aligned.

4: procedure addToBlock(i)

hb.append(i)

sum \leftarrow sum + realign(offset, u_{32}(i))

6:

offset \leftarrow offset + ||i||

7:

8:

procedure addChecksum(i, ib)

if sum + i is not a valid checksum literal then

9:

10:

addToBlock(ib)

addToBlock(sum \oplus 1)

11:

12:

addToBlock(i)

13:

addToBlock(sum)

14:

for i in [i_1, ..., i_n] do

15:

16:

if i is a jump instruction then

if offset = 0 then

▶ No empty sections.

17:

addToBlock(encode(nop))

18:

else if offset \equiv 2 [4] then \triangleright Force alignment.

19:

addToBlock(encode(c.nop))

20:

if i is a function call then

21:

addChecksum(encode(ccscall (2N+4)),

22:

encode(ccscallb (2N+4)))

▶ Jumps/branches.

23:

else

addChecksum(encode(ccs), encode(ccsb))

24:

offset \leftarrow 0

25:

26:

addToBlock(i)

for j = 1 to 2N + 4 do

▶ Add trap barrier.

27:

28:

addToBlock(encode(c.ebreak))

29: return hb

```

In LLVM, this is expanded later in the code emitter due to limitations in the back-end structure; we count this towards the Machine IR pass for simplicity of exposition. The Machine IR pass is followed by static branch relaxation (the unfolding of far jumps into multi-instruction sequences and converse compaction of near jumps into shorter instructions), which is the main reason why the addition of new code cannot be delayed more; it would break short jumps.<sup>7</sup>

During object file generation, the 8-byte CCS Machine IR instruction is replaced with a 4-byte XCCs opcode and a placeholder zero-checksum. A custom relocation of type R\_RISCV\_CHECKSUM (marked by a comment in Figure 8c) is added to mark the checksum region for the linker.<sup>8</sup>

a custom type to inform the linker of the newly-added ccs in the pair.

• Linking: the linker follows relocation entries to compute checksums and insert them in the provided spaces. The linker script is also updated so that hardened objects are linked to a different virtual address (0x40000) than non-hardened libraries and runtime files (0x10000), which we use as the basis to enable Xccs protection.

#### 3.5 Discussion

We discuss some of our design choices and how the scheme interacts with other micro-architectural features.

Fault's effect on CCS updates. Our countermeasure relies on CCS updates not being vulnerable to attacks. This is a reasonable inference based on the fault model: recall that fetch skips are induced by clock glitches, which are known to cause problems locally along critical signal propagation paths. [3] identify that such paths are mostly in the fetch stage of the pipeline, but CCS can be updated in the execution stage using the realign sum technique, and is thus unlikely to be affected.

Interrupts. Common interrupts and signal handlers (that are invisible from the main thread) would not interfere with Xccs protections (with the only OS support needed being to save Xccs registers, which can be viewed as an extension of PC, to the CPU context structure). However, a non-returning interrupt (such as a signal exiting) would leave the current block without a check. We assume such a no-returning action implies abandoning the critical section where the interrupt occurred; otherwise, there might be a vulnerability.

Effect of faults on complex architectures. The fault model from [3] does not describe hardware responses to fault attacks during speculative or out-of-order execution. The study and design of fault models at the micro-architectural level is already state-of-the-art, and applying it to these complex features is a completely open problem. While Xccs is amenable to speculative execution (mispredictions would not lead to false checksum exceptions because the checksum resets at the beginning of every block) and out-of-order execution (the checksum update is associative-commutative, allowing for reordering within each block) it remains unlikely that clock glitches would affect such complex designs in the same way as the simple processors from which fetch skips are derived.

Possibility of a hardware-only solution. Hardware-only countermeasures against fault attacks present their own challenges [12]. Detecting the clock glitch at the (hardware) source using a *fault detector* [15] creates a performance trade-off between sensitivity and the rate of false alarms, which limits the approach to security-critical systems that can afford the performance loss. Detecting corruption in the instruction stream requires extra hardware logic that risks being itself faulted (increased attack surface). Software/hardware propositions like our XCCs countermeasure have contrasting benefits. We minimize exposure to the fault because the detection only relies on CCS updates (which occur in

<sup>&</sup>lt;sup>7</sup>We disable linker relaxation for simplicity to maintain jumps' alignment, but it could be enabled after adding appropriate alignment relocations. <sup>8</sup>The R\_RISCV\_CALL relocation for auipc/jump pairs is also replaced with

the execution stage, away from disrupted fetch logic) and a checksum check made after the fault's transient effect has subsided. (We carefully discussed the safety of these operations with authors of [3].) We also get the benefits of using more software and less hardware, such as incurring costs only in critical sections and the possibility of implementing hardware support late or during minor hardware revisions.

Specificity of the attack model. Many (mostly early) works in fault literature attempt to protect against *all* program misbehaviors, described as "soft errors". By contrast, we target a single vulnerability, which might appear overly specific. However, the fetch skips model coined by [3] results from extensive physical injection campaigns, where it described the impact of 80-90% of clock glitches on Cortex-M boards [2], making this countermeasure useful against common attack vectors on real boards. In addition, we argue that the lack of a precise definition for soft errors leads to tricky vulnerabilities preventing any proof-based security standard from being met. This is why we focus on fetch skip attacks, for which we can formally prove security.

#### 4 Security Theorem

We now state the security theorem for our countermeasure and the main steps of the proof. We omit some invariants about  $\sigma/\rho$  whose significance is only clear with the full formalization and proof (in the research paper version of this article).

We define a step as a statement

$$s = \langle PC, \rho, \sigma, \alpha \rangle \rightarrow \langle PC', \rho', \sigma', \alpha' \rangle$$

materializing the change in execution state associated with the execution of a single instruction, and an *execution* as a sequence of steps  $[s_0, \ldots, s_n]$  such that the initial state of any  $s_i$  (i > 0) is the final state of  $s_{i-1}$ .

#### Theorem (simplified).

Let  $P = [\mathsf{HARDEN}(\mathsf{bb}_1), \ldots \mathsf{HARDEN}(\mathsf{bb}_{|P|})]$  a program hard-ened by Algorithm 1, and  $e = [s_0, \ldots, s_{|e|}]$  an execution such that

- $s_0$  starts at the top of a block of P;

- $s_{|e|}$  successfully executes a program exit instruction.

Then e can be partitioned into sub-sequences  $(s_{t_i} \ldots s_{b_i})_{1 \leq i \leq m}$  each executing one hardened block HARDEN(bb<sub>i</sub>), such that

- 1. Each  $s_{t_i}$  starts at the top of HARDEN( $bb_i$ );

- 2. Each  $s_{b_i}$  ( $i \neq m$ ) runs a legitimate (non-forged) jump instruction of bb<sub>i</sub>, and  $\sigma_{b_i}$ .CCS is the correct associated checksum;

3. If each segment  $s_{t_i} \ldots s_{b_i}$  contains at most one faulted fetch and the last segment  $s_{t_m} \ldots s_{b_m}$  has none<sup>10</sup>, then the entire execution e contains no faults.

In essence, this theorem says that the countermeasure guarantees the execution of the original sequence of instructions (as witnessed by the checksum) at every control flow edge. The key property is the *local security* at the block level; the security property of passing checksums is checked at every block, and deviations from that property are detected before the block ends. This facilitates both formal analysis (by removing difficulties associated with control flow) and testing (by providing an easy way to detect failures in the countermeasure).

The progression of the argument is as follows:

- 1. Control cannot reach the end of a protected block due to the c.ebreak-based trap barrier;

- Control can only leave a protected block through a jump if it passes the associated checksum;

- 3. Using exactly one faulted fetch in the execution of a block always invalidates the checksum.

The checksum method by itself does not always guarantee that the execution cannot be compromised, as a vulnerable block could contain a *checksum collision*: an unintended execution path, reachable with multiple faults, whose checksum is the same as the intended execution. Such collisions can be detected statically after linking, but they are hard to solve because the linker is unable to add or remove instructions to prevent the collision once it is discovered, as the first could break short jumps and both would change jump offsets thus more checksums. In this case, the toolchain's abstraction stack that we worked around fairly easily in Section 3.4 poses a greater challenge.

Note that the countermeasure still guarantees that checksums must pass even in multi-attack scenarios. Collisions are rare (as showcased in Section 5) despite the apparent weakness of the summing algorithm, mainly because the attacker cannot feed arbitrary inputs to the sum; they can only skip or repeat predetermined inputs. Thus, the scheme retains value as a practical protection mechanism against multi-fault attacks.

#### 5 Implementation Setting and Evaluation

We now describe the implementation and the experimental settings we used to evaluate the countermeasure. We examine functional correctness, security guarantees, and cost.

<sup>&</sup>lt;sup>9</sup>For instance, triplication countermeasures such as SWIFT-R [10] and NEMESIS [13] tend to assume that a single "soft error" only affects one of the three execution streams, but this is not true of e.g. the kind of decoding errors mentioned in [13].

<sup>&</sup>lt;sup>10</sup>We do not protect the exit of the last block because in practice the last instruction is a syscall invocation in the non-hardened libc function exit().

#### 5.1 Implementation and Experimental Setting

We implemented the hardening scheme in LLVM [20] 12.0,<sup>11</sup> linking programs with an off-the-shelf GNU C library using a modified GNU 1d 2.40 linker. The hardware extension Xccs was prototyped in the system emulator QEMU 8.0 [8] and the processor simulator Gem5 22.1 [24]. The implementation is about 1150 lines in LLVM/1d for the countermeasure, and 850 lines in QEMU/Gem5 for evaluation.<sup>12</sup>

We evaluate our countermeasure on programs from the MiBench benchmark suite [16], which is designed to be representative of embedded applications. We do not specifically use a cryptography- or security-oriented benchmark as we protect code at a low enough level that the nature of the program is not significant. Programs were hardened with N=2, i.e. assuming a strong attacker that can inject double-skips every fetch. We perform three types of experiments, on a standard x86–64 GNU/Linux machine:

- Exhaustive single-fault injection campaigns in QEMU;

- Random multi-fault injection campaigns in QEMU;

- No-fault performance simulations in Gem5.

We instrument QEMU to support fault injections by skipping or replacing data during the transpilation step. We take advantage of the locally-correct design of the countermeasure and raise an explicit "countermeasure bypassed" exception at every successful exit of a block where a fault was triggered. This ensures that successful fault attacks are reported and cannot be masked by program logic. We similarly extend Gem5 with the decoding and execution of Xccs instructions, but leave out exceptional conditions since we use it only to evaluate performance without fault injections.

#### 5.2 Functional Correctness

We first assert that hardening preserves the functional behavior of programs when no fault is injected. This is checked by running hardened MiBench programs and comparing their output to a non-cross-compiled x86 build and a non-hardened RISC-V build.<sup>13</sup> All programs pass this test.

#### 5.3 Security Guarantee

We then subject each program to two injection settings, both performed by emulation in QEMU:

- 1. *Single-fault exhaustive injection*: we attack every PC in the protected text segment of the program with single-fault S32(1), S32(2), and S&R32.

- 2. *Multi-fault random injection*: we attack 2000 code intervals of 64 bytes with randomly-selected sequences of 2 to 6 faults in close succession.

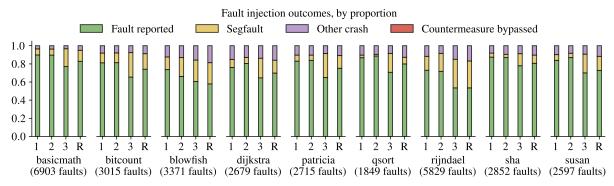

This showcases the guarantees proven in Section 4. Outcomes of injections for which the targeted PC was reached are classified in four categories in Figure 9:

- Fault reported: An invalid checksum, illegal jump, or other Xccs-imposed constraint was violated; or c.ebreak was executed.

- **Segfault**: The program segfaulted from an incorrect memory access as a result of the injected fault.

- Other crash: Illegal instructions being decoded by the CPU (SIGILL) or other rare crashes such as SIGBUS.

- Countermeasure bypassed: The program successfully exited a block after attacking it. This did not happen in any of the tests.

Figure 9 shows that no attack was able to bypass the protection from the countermeasure, which in the multi-fault case means that no checksum collision occurred.

A significant majority of faults that are reached result in Xccs violations, meaning that failing checksums and invalid attempts to jump out of blocks are adequately reported. Because all exits of attacked blocks were guarded with "Countermeasure bypassed" exceptions, which were not reached, every crash we encountered also occurred within the attacked block. This shows that the countermeasure fulfills its goal of containing faults within blocks.

Interestingly, crashes alone do not provide sufficient security: unprotected programs (not depicted) experience  $\sim$ 90% crashes but only  $\sim$ 30% in the block where the fault is injected. So like with instruction skip, a system facing random failures could leave the code unprotected, but the threat of targeted attacks requires a countermeasure like Xccs.

#### 5.4 Performance

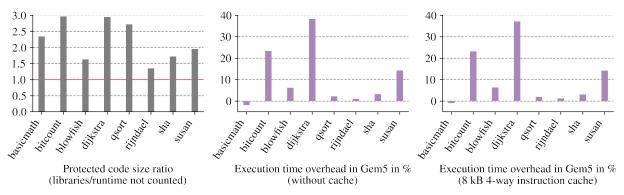

On average, hardening with N=2 increased the size of protected functions (i.e., excluding libraries and runtime files) by a factor of 2.46 (which is large but usual for security applications especially against skips, due to duplication). Individual differences are given in Figure 10; unsurprisingly, programs with longer straight-line sections see less of an increase, while short, loop-intensive programs like dijkstra and bitcount get the largest overhead.

We run Gem5 simulations for each program<sup>14</sup> to estimate the overhead in execution time, also reported in Figure 10. The simulated system mainly consists of a 1-GHz RISC-V core with a 1600 MHz DDR3 controller simulated by Gem5's *timing* model.

The main cost is the execution of Xccs instructions themselves, which incur extra fetch-decode-execute cycles. As expected, programs with denser control flow in hot sections such as dijkstra and bitcount see by far the largest difference. We expected the code size increase to reduce cache

<sup>&</sup>lt;sup>11</sup>All the modified tools used in this paper are publicly available at gricad-gitlab.univ-grenoble-alpes.fr/michelse/fetch-skips-hardening.

$<sup>^{12}\</sup>mathrm{Gem5}$  currently only emulates 64-bit RISC-V instructions; we modified it to support 32-bit instructions for this evaluation.

$<sup>^{13}</sup>$ For some programs, comparison with the native build is skipped due to differences in the precision of the math library.

<sup>&</sup>lt;sup>14</sup>Except patricia, due to a 32- vs. 64-bit compatibility issue related to reused opcodes in the RISC-V ISA.

Figure 9. Outcomes of exhaustive S32(1), S32(2) (bars 1 and 2) and S&R32 (bars 3) single-fault injections, and random multi-fault injections on MiBench programs (bars R). The total number of injected faults is given for each program.

**Figure 10.** Evaluation of the cost of our counter-measure: static and dynamic metrics.

efficiency, and ran simulations with an 8-kB 4-way instruction cache (the median size of hardened sections in our test, which is a lot smaller than the total text segment). This speeds up executions significantly (not pictured) but the ratio of hardened to non-hardened speed remains consistent. The overall performance hit is 10.2%, consistent with the knowledge that MiBench programs average out 6–7 instructions per basic block (keeping in mind that our blocks are longer than traditional basic blocks). Unsurprisingly, cryptographic schemes have the best performance results due to being computation-heavy with long blocks.

Existing countermeasures without hardware support have a comparatively much larger overhead. [14] compare multiple combinations of countermeasures against single- to quadruple-instruction skips on a secure boot program. Only 3 combinations (nZDC + RACFED, NEMESIS + RACFED, and CompaSec) close more than 75% of vulnerabilities, all with space overhead above x4.85 and time overhead above x5.01.

#### 6 Related Work

The contribution of this paper follows the now numerous developments in the area of compilation for security. Recent countermeasure designs have consistently involved compilation tools [5, 29, 35], and issues stemming from cross-layer

abstractions have been raised previously [6]. Our work differs in its deliberate involvement of hardware, whereas existing designs that account for non-ISA details (such as timings in [35]) still end up performing pure assembly transformations.

Countermeasure designs that lay more heavily towards hardware also exist. [25] show how hardware support can improve a classic countermeasure against data corruption which consists in executing instructions multiple times and comparing results. This is traditionally very costly due not only to repeated execution, but also program size, register pressure, and the addition of many branches for comparisons. In this work, the ISA is extended with a new "replay" instruction rpl w n which repeats the next w instructions n times, and compares in hardware with an exception in case of a mismatch. A benefit is that the compiler only needs to mark sensitive instructions, however this shifts more security burden to hardware and increases the effort for hardware qualification/certification compared to a more lightweight extension like Xccs.

Our countermeasure is based on classical redundancy ideas and draws inspiration from previous work on instruction skips [36] and control-flow integrity protections [27, 38]. Complications associated with multi-fault attacks incentivized us to aim for a design that guarantees security *locally*

(at every block) to keep formal reasoning simple. Many countermeasures in security literature (for instance [10, 13, 14]) achieve sophisticated and carefully-balanced compiler transforms, but lack a detailed enough programming and fault model to allow for a formal proof of the security property. We believe that our semantics approach that includes "just enough" details in the programming model, encodes the fault model in the semantics, and encourages formal proofs, could be generalized for other low-level countermeasures.

As for the correctness of securization schemes, apart from manual proofs (in which this work falls), automatic countermeasure verification techniques includes translation validation [9], static analysis [11], and symbolic execution [28]. These usually focus on proving properties of the form "either the attack is detected or the program crashed", as we did here. Another remarkable piece of work in this area is a proof that the C compiler CompCert [23] preserves the constant-time countermeasure when applied to source code [17]. A possible extension of our work would be to further validate through one of these approaches.

#### 7 Conclusion

We have presented a new countermeasure to a micro-architectural fault attack targeting the instruction fetch unit in RISC-V processors. Our approach combines a hardware extension of the RISC-V ISA, dubbed Xccs, and a machine code transformation performed at compile- and link-time. The design process was guided by a specially-tailored semantics that captures just the right set of architectural details to formalize the hardening process and enable a proof of security. We evaluated the scheme's security by emulating both exhaustive single-fault and random multi-fault injection campaigns, and its performance with a processor simulation. To our knowledge, the present contribution is the first example of such a proven countermeasure for a micro-architectural fault model; which notably connects recent security experts' results to compiler back-end techniques.

We believe that this approach is applicable more generally to the design of code hardening schemes that guarantee both security and safety. We implemented this particular countermeasure in the late back-end, which is pretty standard for low-level attacks, and keeps the abstraction gap between the attack and countermeasure fairly small. In future work we wish to explore countermeasures implemented at other (sometime multiple) levels in the compilation flow, widening that gap. This will escalate toolchain integration challenges already raised in this paper, as the compiler's heavy descent in abstraction might break or hinder security properties. Partial solutions such as [33], which advocates for embedding security properties into functional properties, leads us to believe that cleaner, more methodical integration is possible. Similar improvements to the semantic model appear needed to mirror this property preservation in the security proof.

#### **Data-Availability Statement**

An artifact of this work is available for reproduction on Zenodo [26] and includes pre-built tools and reference outputs. Source code and documentation for the tools (LLVM, GNU binutils, QEMU, Gem5) is further available for reuse through the Git repository at gricad-gitlab.univ-grenoble-alpes.fr/michelse/fetch-skips-hardening.

#### References

- [1] 2019. The RISC-V Instruction Set Manual Vol. I.

- [2] Ihab Alshaer. 2023. Cross-Layer Fault Analysis for Microprocessor Architectures (CLAM). Theses. Université Grenoble Alpes [2020-....]. https://theses.hal.science/tel-04417620

- [3] Ihab Alshaer, Brice Colombier, Christophe Deleuze, Vincent Beroulle, and Paolo Maistri. 2022. Variable-Length Instruction Set: Feature or Bug? 2022 25th Euromicro Conference on Digital System Design (DSD). https://doi.org/10.1109/DSD57027.2022.00068

- [4] H. Bar-El, Hamid Choukri, D. Naccache, Michael Tunstall, and C. Whelan. 2006. The Sorcerer's Apprentice Guide to Fault Attacks. *Proc. IEEE* 94, 2 (2006), 370–382. https://doi.org/10.1109/JPROC.2005.862424

- [5] Thierno Barry, Damien Couroussé, and Bruno Robisson. 2016. Compilation of a Countermeasure Against Instruction-Skip Fault Attacks. In Workshop on Cryptography and Security in Computing Systems (Proceedings of the Third Workshop on Cryptography and Security in Computing Systems). vienna, Austria. https://doi.org/10.1145/2858930.2858931

- [6] Thierno Barry, Damien Couroussé, Bruno Robisson, and Karine Heydemann. 2017. Automated Combination of Tolerance and Control Flow Integrity Countermeasures against Multiple Fault Attacks. In European LLVM Developers Meeting. Saarbrücken, Germany. https://hal.sorbonne-universite.fr/hal-01660160

- [7] Gilles Barthe, François Dupressoir, Pierre-Alain Fouque, Benjamin Grégoire, and Jean-Christophe Zapalowicz. 2014. Synthesis of Fault Attacks on Cryptographic Implementations. In Proceedings of the 2014 ACM SIGSAC Conference on Computer and Communications Security (Scottsdale, Arizona, USA) (CCS '14). Association for Computing Machinery, New York, NY, USA, 1016–1027. https://doi.org/10.1145/ 2660267.2660304

- [8] Fabrice Bellard. 2005. QEMU, a Fast and Portable Dynamic Translator. In Proceedings of the Annual Conference on USENIX Annual Technical Conference (Anaheim, CA) (ATEC '05). USENIX Association, USA, 41.

- [9] Matteo Busi, Pierpaolo Degano, and Letterio Galletta. 2022. Towards Effective Preservation of Robust Safety Properties. In Proceedings of the 37th ACM/SIGAPP Symposium on Applied Computing (Virtual Event) (SAC '22). Association for Computing Machinery, New York, NY, USA, 1674–1683. https://doi.org/10.1145/3477314.3507084

- [10] J. Chang, G.A. Reis, and D.I. August. 2006. Automatic Instruction– Level Software-Only Recovery. *International Conference on Dependable Systems and Networks (DSN'06)*, 83–92. https://doi.org/10.1109/DSN. 2006.15

- [11] Maria Christofi, Boutheina Chetali, Louis Goubin, and David Vigilant. 2013. Formal Verification of a CRT-RSA Implementation Against Fault Attacks. *Journal of Cryptographic Engineering* 3, 3 (2013), 157–167. https://doi.org/10.1007/s13389-013-0049-3

- [12] Ruan de Clercq and Ingrid Verbauwhede. 2017. A survey of Hardware-based Control Flow Integrity (CFI). CoRR abs/1706.07257 (2017). arXiv:1706.07257 http://arxiv.org/abs/1706.07257

- [13] Moslem Didehban, Aviral Shrivastava, and Sai Ram Dheeraj Lokam. 2017. NEMESIS: a software approach for computing in presence of soft errors. In Proceedings of the 36th International Conference on Computer-Aided Design (ICCAD '17). IEEE Press, Irvine, California, 297–304.

- [14] Johannes Geier, Lukas Auer, Daniel Mueller-Gritschneder, Uzair Sharif, and Ulf Schlichtmann. 2023. CompaSeC: A Compiler-Assisted Security

- Countermeasure to Address Instruction Skip Fault Attacks on RISC-V. In *Proceedings of the 28th Asia and South Pacific Design Automation Conference* (Tokyo, Japan) (*ASPDAC '23*). Association for Computing Machinery, New York, NY, USA, 676–682. https://doi.org/10.1145/3566097.3567925

- [15] Kamil Gomina, Jean-Baptiste Rigaud, Philippe Gendrier, Philippe Candelier, and Assia Tria. 2014. Power supply glitch attacks: Design and evaluation of detection circuits. In 2014 IEEE International Symposium on Hardware-Oriented Security and Trust (HOST). 136–141. https://doi.org/10.1109/HST.2014.6855584

- [16] M.R. Guthaus, J.S. Ringenberg, D. Ernst, T.M. Austin, T. Mudge, and R.B. Brown. 2001. MiBench: A free, commercially representative embedded benchmark suite. *Proceedings of the Fourth Annual IEEE International Workshop on Workload Characterization. WWC-4 (Cat. No.01EX538)*, 3–14. https://doi.org/10.1109/WWC.2001.990739

- [17] Rémi Hutin. 2021. Verified Secure Compilation against Timing Side-Channels. Ph. D. Dissertation. http://www.theses.fr/2021ENSR0029 Thèse de doctorat dirigée par Blazy, Sandrine et Pichardie, David Informatique Rennes, École normale supérieure 2021.

- [18] Andrea Höller, Armin Krieg, Tobias Rauter, Johannes Iber, and Christian Kreiner. 2015. QEMU-Based Fault Injection for a System-Level Analysis of Software Countermeasures Against Fault Attacks. In 2015 Euromicro Conference on Digital System Design. 530–533. https://doi.org/10.1109/DSD.2015.79

- [19] Ronan Lashermes, Hélène Le Bouder, and Gaël Thomas. 2018. Hardware-Assisted Program Execution Integrity: HAPEI. In Nord-Sec 2018: 23rd Nordic Conference on Secure IT Systems. Oslo, Norway. https://doi.org/10.1007/978-3-030-03638-6 25

- [20] Chris Lattner and Vikram Adve. 2004. LLVM: A compilation framework for lifelong program analysis & transformation. In *International* symposium on code generation and optimization, 2004. CGO 2004. IEEE, 75–86.

- [21] Johan Laurent. 2020. Modélisation de fautes utilisant la description RTL de microarchitectures pour l'analyse de vulnérabilité conjointe matériellelogicielle. Theses. Université Grenoble Alpes. https://tel.archivesouvertes.fr/tel-03167493

- [22] Johan Laurent, V. Beroulle, C. Deleuze, Florian Pebay-Peyroula, and Athanasios Papadimitriou. 2018. On the Importance of Analysing Microarchitecture for Accurate Software Fault Models. (2018), 561– 564. https://doi.org/10.1109/DSD.2018.00097

- [23] Xavier Leroy. 2009. Formal Verification of a Realistic Compiler. Commun. ACM 52, 7 (jul 2009), 107–115. https://doi.org/10.1145/1538788. 1538814

- [24] Jason Lowe-Power, Abdul Mutaal Ahmad, Ayaz Akram, Mohammad Alian, Rico Amslinger, Matteo Andreozzi, Adrià Armejach, Nils Asmussen, Brad Beckmann, Srikant Bharadwaj, et al. 2020. The gem5 simulator: Version 20.0+. arXiv preprint arXiv:2007.03152 (2020).

- [25] Noura Ait Manssour, Vianney Lapôtre, Guy Gogniat, and Arnaud Tisserand. 2022. Processor Extensions for Hardware Instruction Replay against Fault Injection Attacks. In 2022 25th International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS). 26–31. https://doi.org/10.1109/DDECS54261.2022.9770170

- [26] Sébastien Michelland. 2024. Replication package for article: From low-level fault modeling (of a pipeline attack) to a proven hardening scheme. https://doi.org/10.5281/zenodo.10440364

- [27] Tanmaya Mishra, Thidapat Chantem, and Ryan Gerdes. 2022. Survey of Control-Flow Integrity Techniques for Real-Time Embedded Systems. ACM Trans. Embed. Comput. Syst. 21, 4, Article 41 (oct 2022), 32 pages. https://doi.org/10.1145/3538275

- [28] Marie-Laure Potet, Laurent Mounier, Maxime Puys, and Louis Dureuil. 2014. Lazart: A Symbolic Approach for Evaluation the Robustness of Secured Codes against Control Flow Injections. In 2014 IEEE Seventh International Conference on Software Testing, Verification and Validation. 213–222. https://doi.org/10.1109/ICST.2014.34

- [29] Julien Proy, Karine Heydemann, Alexandre Berzati, and Albert Cohen. 2017. Compiler-Assisted Loop Hardening Against Fault Attacks. ACM Trans. Archit. Code Optim. 14, 4, Article 36 (dec 2017), 25 pages. https://doi.org/10.1145/3141234

- [30] Carlton Shepherd, Konstantinos Markantonakis, Nico van Heijningen, Driss Aboulkassimi, Clément Gaine, Thibaut Heckmann, and David Naccache. 2021. Physical fault injection and side-channel attacks on mobile devices: A comprehensive analysis. *Computers & Security* 111 (dec 2021), 102471. https://doi.org/10.1016/j.cose.2021.102471

- [31] Stefan Tillich, Christoph Herbst, and Stefan Mangard. 2007. Protecting AES Software Implementations on 32-Bit Processors Against Power Analysis. In Applied Cryptography and Network Security, 5th International Conference, ACNS 2007, Zhuhai, China, June 5-8, 2007, Proceedings (Lecture Notes in Computer Science, Vol. 4521), Jonathan Katz and Moti Yung (Eds.). Springer, 141–157. https://doi.org/10.1007/978-3-540-72738-5\_10

- [32] Simon Tollec, Mihail Asavoae, Damien Couroussé, Karine Heydemann, and Mathieu Jan. 2022. Exploration of Fault Effects on Formal RISC-V Microarchitecture Models. In 2022 Workshop on Fault Detection and Tolerance in Cryptography (FDTC). 73–83. https://doi.org/10.1109/ FDTC57191.2022.00017

- [33] Son Tuan Vu. 2021. Optimizing Property-Preserving Compilation. Ph. D. Dissertation. http://www.theses.fr/2021SORUS435 Thèse de doctorat dirigée par Heydemann, Karine et Cohen, Albert Henri Informatique Sorbonne université 2021.

- [34] Vincent Werner, Laurent Maingault, and Marie-Laure Potet. 2022. An end-to-end approach to identify and exploit multi-fault injection vulnerabilities on microcontrollers. *Journal of Cryptographic Engineering* (Oct. 2022), 1–17. https://doi.org/10.1007/s13389-022-00292-z

- [35] Hans Winderix, J. Mühlberg, and F. Piessens. 2021. Compiler-Assisted Hardening of Embedded Software Against Interrupt Latency Side-Channel Attacks. (2021), 667–682. https://doi.org/10.1109/ EuroSP51992.2021.00050

- [36] Yuan Yao and Patrick Schaumont. 2018. A Low-Cost Function Call Protection Mechanism Against Instruction Skip Fault Attacks. In Proceedings of the 2018 Workshop on Attacks and Solutions in Hardware Security (Toronto, Canada) (ASHES '18). Association for Computing Machinery, New York, NY, USA, 55–64. https://doi.org/10.1145/3266444.3266453

- [37] Bilgiday Yuce, Nahid Farhady Ghalaty, Harika Santapuri, Chinmay Deshpande, Conor Patrick, and Patrick Schaumont. 2016. Software Fault Resistance is Futile: Effective Single-Glitch Attacks. In 2016 Workshop on Fault Diagnosis and Tolerance in Cryptography (FDTC). 47–58. https://doi.org/10.1109/FDTC.2016.21

- [38] Anthony Zgheib, Olivier Potin, Jean-Baptiste Rigaud, and Jean-Max Dutertre. 2022. A CFI Verification System based on the RISC-V Instruction Trace Encoder. In 2022 25th Euromicro Conference on Digital System Design (DSD). 456–463. https://doi.org/10.1109/DSD57027.2022.00067

*Supplementary material for the CC'24 article:*

From low-level fault modeling (of a pipeline attack) to a proven hardening scheme

#### A Operational semantics

In this appendix, we formalize operational semantics for a minimal, representative subset of 32-bit RISC-V assembly which includes fetch skip attacks and our XCCs extension, and provide a detailed proof of the claims made in Section 4.

Notations. We write  $u_N$  the type of N-bit unsigned integers. We also use structure-like notations  $\{\langle \text{field} \rangle : \langle \text{type} \rangle, ... \}$  and  $\langle \text{struct} \rangle . \langle \text{field} \rangle$  for bit fields and named collections of values.

#### A.1 Program and execution models

**Definition 1** (Instruction, Block, Program).

An **instruction** i is a 16- or 32-bit integer (a  $u_{16}$  or a  $u_{32}$ ) corresponding to a RISC-V opcode.<sup>15</sup> We write  $\|i\|$  the size of an instruction in bytes (2 or 4).

A **block** bb is a nonempty sequence of instructions, along with a 4-aligned address value blockAddr(bb) indicating where it is loaded in memory.

A program P is a collection of non-intersecting blocks.

Since instructions in the same block are loaded contiguously, each block spans the interval

$$\texttt{blockSpan(bb)} = \bigg[ \texttt{blockAddr(bb)}, \, \texttt{blockAddr(bb)} + \sum_{i \in \texttt{bb}} \|i\| \bigg).$$

Programs are assumed to be well-formed, in that no two blocks' spans intersect and every jump points to the blockAddr of some block.

#### **Definition 2** (Program state).

A program state in RISC-V assembler with XCCs and fetch skips is a quadruplet  $\langle PC, \rho, \sigma, \alpha \rangle$ , where

- PC: u<sub>32</sub> is the program counter;

- $\rho$  :  $u_{32}$  is the last row fetched from code memory;

- $\sigma = \{CCS, CCSD, CCSDS, CCSPROT\}$  holds Xccs registers:

- CCS: u<sub>32</sub> the running checksum of the current block;

- CCSD :  $\{E: u_1, J0: u_5\}$  the XCCs status register;

- CCSDS: u<sub>32</sub> the Xccs "delay slot" register;

- CCSPROT: u<sub>32</sub> the protected PC register.

- $\alpha$  :  $u_{32}[32]$  is the architectural state (registers  $\times 0... \times 31$ ).

The program state tracks the progress of execution. For simplicity, we do not include memory, which would be handled like the registers in  $\alpha$ , or side-effects, which could be recorded as a trace whenever a side-effecting syscall is invoked by the ecall instruction. We only consider the final state of registers.

Note that  $\rho$  is a raw 32-bit value which is not necessarily a legal instruction because instructions are not always 32-bit and not always aligned in memory.

#### **Definition 3** (Step, Execution).

A **step** is a statement representing the effect of executing one instruction, written  $\langle PC, \rho, \sigma, \alpha \rangle \rightarrow r$  where r is either a program state or one of two termination reasons:

- ⊥, denoting an exception or crash;

- end( $\alpha$ ), denoting successful completion with final state  $\alpha$ .

An **execution** is a sequence of program states ending with a termination reason, such that all pairs of consecutive elements are related by a step:

$$\langle PC, \rho, \sigma, \alpha \rangle \to \dots \to \langle PC_n, \rho_n, \sigma_n, \alpha_n \rangle \to \begin{cases} \bot \\ \mathsf{end}(\alpha') \end{cases}$$

#### A.2 Fetch and step rules

We can now describe how execution steps are derived from the fetch-decode-execute cycle of the CPU, including fault injections during fetches.

#### **Definition 4** (Fetch).

A **fetch** is a statement  $(PC, \rho)$   $a \Rightarrow d$   $(PC', \rho')$  representing the CPU fetching 32 bits at 4-aligned address  $a : u_{32}$  and getting value  $d : u_{32}$  ("data"), with the PC and  $\rho$  members of the program state being updated in the process.

Each fault attack corresponds to one use of the S32(k) or S&R32 rules. Notice, for example, how rule S32(k) skips over a directly to a+4k. In the following rules, [a] denotes the 32 bits stored in memory at address a.

$$\begin{split} & \frac{\mathsf{NOFAULT}}{(\mathsf{PC},\rho)\; a \Rightarrow [a]\; (\mathsf{PC},[a])} \\ & \frac{\mathsf{S32}(k)}{(\mathsf{PC},\rho)\; a \Rightarrow [a+4k]\; (\mathsf{PC}+4k,[a+4k])} \\ & \frac{\mathsf{S\&R32}}{(\mathsf{PC},\rho)\; a \Rightarrow \rho\; (\mathsf{PC},[a])} \end{split}$$

Figure 11. Fetch rules.

From there, we can formalize execution steps as an optional fetch, then the execution of a decoded instruction. This is shown in Figure 12. The  $[\![\cdot]\!]$  and  $[\![\cdot]\!]_{ccs}$  functions represent the semantics of individual instructions and are specified later. Both are oblivious to  $\rho$  so we re-insert  $\rho$  into their result after-the-fact using the  $\bullet$  function. The functions LSH, MSH :  $u_{32} \rightarrow u_{16}$  extract the least and most significant halves of a 32-bit value.

These inference rules for steps formalize the patterns shown in Figure 2 (ALIGNED-\* is 2.(a) and (b), UNALIGNED-16 is

$<sup>^{15}\</sup>mathrm{There}$  is no risk of type confusion because 16- and 32-bit instructions differ on their low bits.

Figure 12. Step rules.

2.(c) and UNALIGNED-32 is 2.(d)). For instance, in UNALIGNED-32, MSH( $\rho$ ) identifies the two remaining bytes in the previously-fetched line as 32-bit instruction leader, so the rule fetches the next line d at PC + 2 and recombines  $\rho$  with LSH(d) to form the complete 32-bit instruction and run it.

The extra rule Checksum-Delay-Slot describes the special treatment of the 32-bit checksum value following an XCCs instruction, which is triggered by  $\sigma$ .CCSDS  $\neq$  0 and is described later with the semantics of XCCs instructions.

#### A.3 Instruction semantics

We now define instruction semantics through the functions

$$\begin{split} \llbracket \cdot \rrbracket &: (\operatorname{PC}, \sigma, \alpha) &\mapsto \langle \operatorname{PC}', \sigma', \alpha' \rangle \ \textit{or} \perp \textit{or} \operatorname{end}(\alpha') \\ \llbracket \cdot \rrbracket_{\mathit{ccs}} &: (\operatorname{PC}, \sigma, \alpha, d) &\mapsto \langle \operatorname{PC}', \sigma', \alpha' \rangle \ \textit{or} \perp \textit{or} \operatorname{end}(\alpha') \end{split}$$

The two functions are similar in nature;  $[\cdot]_{ccs}$  is used when re-running XCCs instructions after their 32-bit checksum value (passed as 4th argument) has been found.

In the following, we assume a function encode which encodes assembler notation into 16/32-bit values (16-bit for mnemonics starting with "c.", 32-bit otherwise), following

the RISC-V ISA [1]. Unspecified members in the output  $\sigma'/\alpha'$  are implicitly kept from the input  $\sigma/\alpha$ .

Instructions that are not jumps, traps, or XCCs instructions have their natural semantics, with two small changes: they cannot run when CCSPROT is set to a non-zero address, and they update CCS as a side-effect. We illustrate this category with the add and c.add instructions, and the c.nop instruction that we use as padding while hardening.

• i = encode(add r<sub>d</sub>, rs<sub>1</sub>, rs<sub>2</sub>), i = encode(c.add r<sub>d</sub>, rs<sub>1</sub>, rs<sub>2</sub>):

$$\begin{split} [\![\![\!\,i\,]\!](PC,\sigma,\alpha) = \begin{cases} \bot \text{ if } \sigma.\text{CCSPROT} \neq 0 \\ \langle PC + \|i\|,\sigma',\alpha'\rangle \text{ otherwise, with} \\ \sigma'.\text{CCS} = \sigma.\text{CCS} + \text{realign}(PC,u_{32}(i)) \\ \alpha'[r_d] = \alpha[rs_1] + \alpha[rs_2] \end{cases} \end{split}$$

• i = encode(c.nop) :

The CCS update adds the instruction's opcode to the CCS register, adjusted for PC alignment:  $^{17}$

$$\text{realign}(PC, i) = \begin{cases} i \text{ if } PC \equiv 0 \text{ [4]} \\ 2^{16} LSH(i) + MSH(i) \text{ otherwise} \end{cases}$$

Trapping instructions include ebreak/c.ebreak which we treat as non-recoverable, and ecall which invokes a syscall whose number is specified in register a7 (x17). We treat an invocation of syscall \_\_NR\_exit (1) as program termination.<sup>18</sup>

• i = encode(ebreak), i = encode(c.ebreak):

$$[i](PC, \sigma, \alpha) = \bot$$

• i = encode(ecall):

$$[\![i]\!](PC,\sigma,\alpha) = \begin{cases} \operatorname{end}(\alpha) \text{ if } \alpha[17] = 1 \text{ and } \sigma.\mathsf{CCSPROT} = 0 \\ \bot \text{ otherwise} \end{cases}$$

Among standard instructions, jumps are the most heavily affected. We show here the cases of jal (jump-and-link), which in RISC-V is used for unconditional branches and function calls, and beq (branch-if-equal), a representative conditional branch. The extension to jalr (which is used to return from functions) is immediate by replacing the target PC + imm of jal with the value of a register in  $\alpha$ .

• i = encode(jal r<sub>d</sub>, imm):

$<sup>^{16}</sup>$  As per the RISC-V ISA [1], a 32-bit instruction leader is a value  $i: \mathsf{u}_{16}$  such that  $i \equiv 3$  [4] and a 16-bit instruction is any other 16-bit value.

<sup>&</sup>lt;sup>17</sup>Computing the sum of realigned instruction opcodes ends up being equivalent to summing the values returned by fetch rules in the program, see Lemma 3. We choose to update during decoding because of our intuition that a CCS update during the fetch cycle would be impacted by the fault. <sup>18</sup>We provide this exit mechanism to have a reasonable program model, but in practice the exit() function is in the non-protected libc, so we don't actually worry about protecting the last block.

There are two changes compared to traditional jumps: (1) it is only allowed when CCSPROT is set to PC; (2) it accounts for the *jump offset* (J0) field of CCSD to jump over trap barriers after function calls. The jump also prepares the execution of the next block by resetting CCS and other registers to 0. We do not allow the compiler to compress jal into the 16-bit version c. jal to make sure the next block is also aligned.

Conditional branches are similar, except that if the branch is not taken the block continues and in particular CCS is updated rather than reset.

• i = encode(beg rs<sub>1</sub>, rs<sub>2</sub>, imm):

$$\begin{split} \text{[\![i]\!]}(PC,\sigma,\alpha) = \begin{cases} \bot \text{ if } \sigma.\text{CCSPROT} \neq PC \\ \langle PC + \text{imm},\sigma',\alpha\rangle \text{ if } \alpha[\text{rs}_1] = \alpha[\text{rs}_2], \text{ with } \\ \sigma'.\text{CCS} = 0 \\ \sigma'.\text{CCSPROT} = 0 \\ \sigma'.\text{CCSD.JO} = 0 \\ \langle PC + \|\text{i}\|,\sigma',\alpha\rangle \text{ otherwise, with } \\ \sigma'.\text{CCS} = \sigma.\text{CCS} + \text{realign}(PC,u_{32}(\text{i})) \end{cases} \end{split}$$

The last type of instruction is XCCs instructions. Because these have both a 32-bit opcode and a 32-bit argument, they cannot be executed in a single step. A "delay slot" mechanism with  $\sigma$ .CCSDS and the Checksum-Delay-Slot rule is used to solve this issue in two steps. At the first step, the XCCs opcode will be fetched and recorded in  $\sigma$ .CCSDS. At the second step, the checksum value will be fetched, and passed as argument to the appropriate semantics function  $[\![\sigma$ .CCSDS]\_{ccs}.

The first step which records the opcode in CCSDS proceeds as follows:

• i = encode(ccs), i = encode(ccsb), i = encode(ccscall N), i = encode(ccscallb N):

The second step, which always uses the CHECKSUM-DELAY-SLOT rule, reads back from CCSDS and calls the  $[]_{ccs}$  function by passing the checksum d just fetched from memory as an extra 4th argument. All 4 XCCs instructions have similar semantics; the -call variants set CCSD. JO = N and the -b variants flip the least significant bit of the checksum value before comparing. We factor them as follows.

• Checksum step (*d* is a checksum value):

```