# Comparison of Sub-Micron thick AlGaN/GaN and AlN/GaN HEMTs on Silicon for RF applications

Elodie Carneiro, Stéphanie Rennesson, Fabrice Semond, F Medjdoub

### ▶ To cite this version:

Elodie Carneiro, Stéphanie Rennesson, Fabrice Semond, F Medjdoub. Comparison of Sub-Micron thick AlGaN/GaN and AlN/GaN HEMTs on Silicon for RF applications. 46th Workshop on Compound Semiconductor Devices and Integrated Circuits (WOCSDICE 2023), May 2023, Palerme (Italie), Italy. hal-04438164

HAL Id: hal-04438164

https://hal.science/hal-04438164

Submitted on 5 Feb 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Comparison of Sub-Micron thick AlGaN/GaN and AlN/GaN HEMTs on Silicon for RF applications

Elodie Carneiro<sup>1,2\*</sup>, Stéphanie Rennesson<sup>2</sup>, Fabrice Semond<sup>2,3</sup>, and Farid Medjdoub<sup>1</sup>

<sup>1</sup> Institute of Electronics, Microelectronics and Nanotechnology (IEMN), CNRS, Lille, France

<sup>2</sup>EasyGaN SAS, Rue Bernard Grégory 06905 Sophia Antipolis, France

<sup>3</sup>Université Côte d'Azur, CNRS, CRHEA, rue Bernard Grégory, 06905 Sophia Antipolis, France

\*elodie.cameiro@iemn.fr

#### **Abstract**

In this paper, a performance comparison between sub-micron thick AlGaN/GaN and AlN/GaN HEMT devices are reported. Various gate lengths have been employed in order to analyze the impact on DC and RF performances. Electrical characteristics of these structures for 100 nm gate length show a higher maximum drain current, extrinsic transconductance  $G_m$  and RF performance with the AlN barrier as expected. An excellent electron confinement with a low leakage current below  $10\,\mu\text{A/mm}$  is achieved up to  $V_{DS} = 30\,\text{V}$  on both structures and can be combined with low trapping effects despite the thin total growth thickness of less than  $1\,\mu\text{m}$  on silicon. These results demonstrate the interest of sub-micron thick AlN/GaN-on-Si heterostructures for high frequency applications.

#### Introduction

GaN based High Electron Mobility Transistors (HEMTs) have drawn great attention due to their potential for high power millimeter-wave applications [1, 2]. Usually, thick buffer layers (several µm) are used to minimize growth defect/dislocation density due to the large lattice mismatch between GaN and the substrate. However, thick buffer layers degrade the thermal dissipation and increase the epi-wafer cost. Recent results proved that AlGaN/GaN HEMTs with sub-micron total thickness grown on Silicon Carbide (SiC) can show competitive DC and RF characteristics [3]. However, the use of Silicon (Si) substrate would further decrease the cost although more challenging to achieve due to the large thermal expansion mismatch between GaN and Si potentially leading to cracks / defects. Moreover, even though AlGaN/GaN based HEMTs is the most mature technology [4], short channel effects must be mitigated in order to improve their frequency performances while shrinking the device dimensions. Thus, the gate length scaling must be linked to the reduction of the gate to channel distance in order to avoid short channel effects [5]. Ultrathin barrier AlN/GaN heterostructure is promising for mm-wave range because of the possibility to highly scale the epitaxial structure while benefiting from a high current density. In this work, a comparison of device performances of ultrathin sub-micron thick GaN-on-Si HEMT structures using AlGaN versus AlN barrier layer is reported.

#### **Experimental Details**

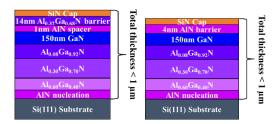

The epitaxial layer structures are based on two sub-micron thick AlGaN/GaN and AlN/GaN heterostructures grown by ammonia-Molecular Beam Epitaxy (NH<sub>3</sub>-MBE) on 4 inch high-resistivity Si(111) substrates ( $\rho > 5$  k $\Omega$ .cm) using a RIBER MBE49 growth reactor. Figure 1 shows the cross section of the HEMT structures. It consists of a high quality, lower than 100 nm, AlN nucleation layer (NL), followed by a three step-graded Al<sub>x</sub>Ga<sub>1-x</sub>N buffer layers (Al<sub>0.08</sub>Ga<sub>0.92</sub>N/Al<sub>0.30</sub>Ga<sub>0.70</sub>N/ Al<sub>0.60</sub>Ga<sub>0.40</sub>N) and a 150 nm thick undoped GaN channel layer. Two different barrier layers of 14 nm thick Al<sub>0.32</sub>Ga<sub>0.68</sub>N and 4 nm thick AlN have been used in order to check the impact on the device performances. Finally, the structures were capped by a SiN layer. The total stack thickness is less than 1  $\mu$ m in both structures. The step-graded Al<sub>x</sub>Ga<sub>1-x</sub>N buffer is used both as a back barrier to enhance the electron

confinement in the 2DEG under high electric field and the breakdown voltage by increasing the overall bandgap.

Device processing started with the formation of the source and drain ohmic contacts. The AlGaN barrier layer was partially etch with BCl<sub>3</sub>/SF<sub>6</sub> plasma in an Inductively Coupled Plasma (ICP) reactor prior to the metallization while the contacts were directly deposit on the AlN barrier. A Ti/Al/Ni/Au metal stack was used and annealed at 800°C for both structures yielding contact resistances of 0.6  $\Omega$ .mm in both cases. The devices were isolated using Nitrogen implantation. Then, Ni/Au T-gates of 100, 150, 250 and 500 nm gate lengths (L<sub>G</sub>) were defined by e-beam lithography. Finally, the devices were passivated with 200 nm PECVD Si<sub>3</sub>N<sub>4</sub> prior to the Ti/Au pads deposition. The 2DEG properties have been extracted at room temperature by Hall effect measurements and showed a charge density of  $1.1\times10^{13}\,\mathrm{cm}^{-2}$  and  $1.7\times10^{13}\,\mathrm{cm}^{-2}$  with an electron mobility of 940 cm²/V.s and 715 cm²/V.s for the AlGaN/GaN and the AlN/GaN structures, respectively.

**Fig. 1.** Sub-micron thick AlGaN/GaN and AlN/GaN HEMTs grown on Si(111) substrate using a step-graded Al<sub>x</sub>Ga<sub>1-x</sub>N buffer layers.

#### **Results and Discussion**

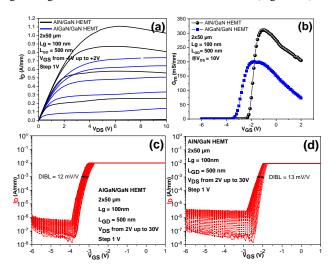

DC measurements have been carried out with a Keysight A2902A static modular and source monitor. Figures 2 and 3 shows typical output and transfer characteristics of  $2\times50~\mu m$  transistors with  $L_{\rm G}$ = 100 nm and a gate-to-drain distance (L<sub>GD</sub>) of 500 nm. The gate source voltage was swept from -6 to +2 V with a step size of 1 V. A maximum drain current I<sub>D,max</sub> of about 0.74 A/mm and 1.0 A/mm have been measured for the AlGaN and AlN barrier, respectively (Figure 2.a) despite the rather limited electron mobility and high contact resistances that still need to be optimized. A pinch-off voltage  $V_{TH} = -3.4 \text{ V}$  for the AlGaN barrier and  $V_{TH} = -2.2 \text{ V}$  for the AlN barrier (shown in Figure 2.c and 2.d) are observed with a drain leakage current lower than 10 µA/mm for both structures. Figure 2.c and 2.d displays the transfer characteristics with a compliance fixed at 150 mA/mm and swept from  $V_{DS} = 2$  to 30 V using a step of 1 V. A low threshold voltage shift as a function of  $V_{DS}$  are observed under high electric field up to 30 V, which confirms a proper electron confinement within the 2DEG reflected by a low drain-induced barrier lowering (DIBL) of 12 and 13 mV/V for the AlGaN and AlN barrier devices, respectively. A transconductance (Gm) of 200 mS/mm for the AlGaN barrier and 311 mS/mm for the AlN barrier have been measured (Figure 2.b). However, these values can be significantly increased by reducing the access resistances and improve the electron mobility.

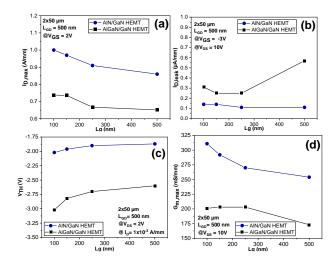

Figure 3 shows some basic DC parameters as a function of the gate length for  $L_{GD} = 500$  nm. As expected, an increase of  $I_{D,max}$  and  $G_{m,max}$  are observed by reducing the gate length (Figure 3.a and

3.d) with about 50% improvement owing to the AlN barrier. As mentioned previously, the leakage current shown in Figure 3.b, is well below 1  $\mu$ A/mm at  $V_{DS}=10$  V for all gate lengths, which reflects the high material and processing quality of both structures. However, the AlGaN barrier shows a higher drop of  $V_{TH}$  when the gate length is shrinked due to short channel effects (Figure 3.c).

**Fig. 2.** (a) Output and (b) extrinsic transconductances characteristic of AlGaN/GaN and AlN/GaN HEMT. Transfer characteristics of a submicron thick  $2\times50~\mu m$  (c) AlGaN/GaN HEMT, (d) AlN/GaN HEMT with  $L_{GD}=500~nm$  and  $L_{G}=100~nm$  up until  $V_{DS}=30~V.$

Fig. 3. (a)  $I_{Dmax}$ , (b)  $I_{Dleak}$ , (c)  $V_{TH}$ , and (d)  $G_{m,max}$  as a function of gate length with  $L_{GD}=500\,$  nm of sub-micron thick  $2\times50\,$   $\mu m$  AlGaN/GaN and AlN/GaN HEMTs.

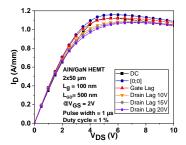

Pulsed  $I_D\text{--}V_Ds$  characteristics revealing the charge trapping effects when using various quiescent bias points are depicted in Figure 4. The open channel DC pulsed measurements are shown at  $V_{GS}=+2$  V with various quiescent drain voltages at room temperature.  $2\times50~\mu m$  transistors with  $L_{GD}$  of 500 nm and  $L_G=100$  nm show low charge trapping effects despite the thin total growth thickness of the AlN/GaN HEMT.

Fig. 4. Open channel pulsed  $I_D\text{-}V_{DS}$  output characteristics of a sub-micron thick  $2\times50~\mu m$  AlN/GaN HEMT with  $L_{GD}=500~nm$  and  $L_G=100~nm$ .

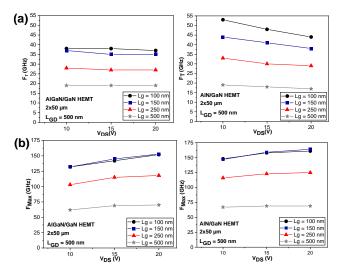

The S-parameters have been measured from 250 MHz to 67 GHz with a Rhode and Schwarz ZVA67GHz network analyser as shown in Figure 5. The current gain extrinsic cut-off frequency  $(F_T)$  is not only higher in the case of AlN but also more scalable for short  $L_{\rm G}$  (shown in figure 5.a) owing to the reduced short channel effects enabled by the ultrathin barrier. The maximum oscillation frequency  $(F_{max})$  increases as function of  $V_{DS}$  for both structures (figure 5.b).  $F_T/F_{max}$  of 37/153 GHz and 44/164 GHz are achieved at  $V_{DS}\!=\!20V$  with  $L_{\rm GD}\!=\!500$  nm and  $L_{\rm G}\!=\!100$  nm for the AlGaN and AlN barrier, respectively. The  $F_{max}/F_T$  ratio close to 4 for the AlN/GaN HEMT is attributed to the highly favourable aspect ratio: gate length / gate-to-channel distance.

**Fig. 5.** (a) Current gain extrinsic cut-off frequency and (b) maximum oscillation frequency of a sub-micron thick  $2\times50~\mu m$  AlGaN/GaN HEMT (left) and AlN/GaN HEMT (right) with  $L_{GD}=500$  nm for various gate lengths.

#### **Conclusions**

In this work, we investigated sub-micron thick AlGaN/GaN and AlN/GaN HEMTs grown on Si(111) substrate for high frequency applications. The MBE grown thin heterostructures show promising and unique features such as low off-state leakage current under high electric field up to 30 V for a gate length of 100 nm combined with high carrier density and low trapping effects. This achievement is attributed to the optimization of the submicron thick step-graded Al<sub>x</sub>Ga<sub>1-x</sub>N buffer layer enabling a high electron confinement under high electric field and a proper surface passivation. Small signal characteristics reveals the benefit of the thin AlN barrier in order to reduce short channel effects and improve the frequency performance. There is a large room for improvement by both reducing the contact resistances and increasing the 2DEG electron mobility. This is part of the future work aiming to demonstrate high RF power performances with ultrathin GaN-on-Si HEMTs in the millimeter-wave range.

#### Acknowledgments

This work was supported by the French RENATECH network, and the French National grant GaNeXT ANR-11-LABX-0014.

#### References

[1] U. Mishra, et al., *Proceedings of the IEEE*, vol. 90, no. 6, 1022-1031, (2002).

[2] K. Harrouche, et al., *IEEE Journal of the Electron Devices Society*, vol. 7, 1145-1150, (2019).

[3] D.-Y. Chen, et al., Phys. Status Solidi A, 2200496, (2022).

[4] Y.-F. Wu, et al., *Device Res. Conf. - Conf. Dig. DRC*, pp. 151–152. (2006).

[5] G. H. Jessen et al., *IEEE Trans. Electron Devices*, vol. 54, no. 10, 2589–2597, (2007)