# Dislocation density reduction for vertical GaN devices on 200 mm Si

Ziyao Gao, Youssef Hamdaoui, Idriss Abid, F Medjdoub, Elke Meissner, Sven Besendörfer, Michael Heuken

#### ▶ To cite this version:

Ziyao Gao, Youssef Hamdaoui, Idriss Abid, F Medjdoub, Elke Meissner, et al.. Dislocation density reduction for vertical GaN devices on 200 mm Si. 14th International Conference on Nitride Semiconductors (ICNS-14), Nov 2023, Nagoya, Japan. hal-04436407

## HAL Id: hal-04436407 https://hal.science/hal-04436407v1

Submitted on 3 Feb 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Dislocation density reduction for vertical GaN devices on 200 mm Si

Z. Gao, <sup>1,\*</sup> C. Kuruoglu, <sup>1</sup> D. Fahle <sup>1</sup>, H. Hahn <sup>1</sup>, Y. Hamdaoui <sup>2</sup>, I. Abid <sup>2</sup>, F. Medjdoub <sup>2</sup>, S. Besendörfer <sup>3</sup>,

E. Meißner<sup>3,4</sup> and M. Heuken<sup>1,5</sup>

<sup>1</sup>AIXTRON SE, 52134 Herzogenrath, Germany

<sup>2</sup>Institute of Electronics, Microelectronics and Nanotechn., 59650 Villeneuve d'Ascq, France <sup>3</sup>Fraunhofer IISB, 91058 Erlangen, Germany

<sup>4</sup>Chair of Electron Devices, FAU University Erlangen-Nürnberg, 91058 Erlangen, Germany <sup>5</sup>Compound Semiconductor Technology, RWTH Aachen University, 52074 Aachen, Germany \*E-Mail: z.gao@aixtron.com

650 V lateral GaN devices penetrate the power-switching market and replace incumbent Si technology. For devices with a 1200 V rating, vertical GaN devices on foreign substrates, such as Si and Sapphire offer significant area and cost reduction potential. With Si substrate backetching or sapphire laser lift-off, the substrate could be separated from GaN buffer afterwards, allowing overall a higher critical electric field in the GaN layer. For vertical GaN devices, the dislocation density is a critical parameter, as certain dislocation types are electrically active.

To obtain a reduction of the dislocation density, we present engineered  $SiN_x$  masking layers that limit dislocations propagation without blocking further epitaxial growth. All experiments were performed in AIXTRON planetary systems on 200 mm Si substrates. Extracted from XRD measurements, reduced dislocation density from  $10^8$  cm<sup>-2</sup> to mid-low  $10^7$  cm<sup>-2</sup> for both screwtype and edge-type after using SiNx masking layer is achieved while the uniformity of the epitaxial layers is maintained through the whole wafer area.

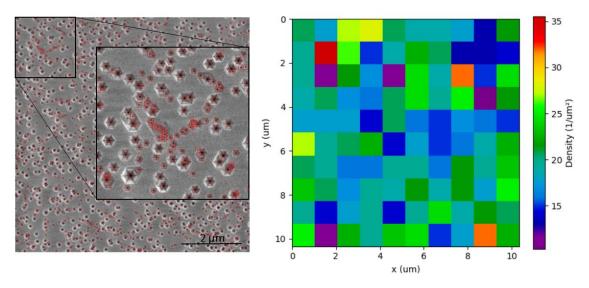

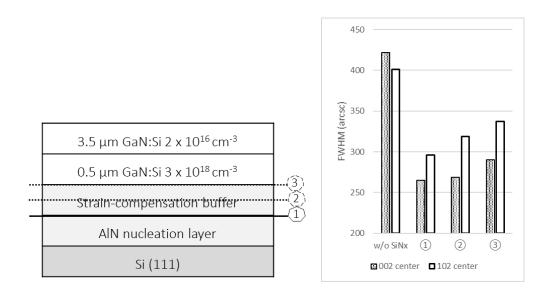

To assess the threading dislocation density, a new dislocation decoration technique has been applied to identify threading dislocation distribution through specific epilayer. Instead of *exsitu* KOH etching or *in-situ* SiH4, here Cl<sub>2</sub> gas is employed for the *in-situ* threading dislocation etch process. Combined with metrology such as XRD, AFM and SEM, profound and comprehensive information about dislocation could be obtained for buffer optimization (Figure S1). On stacks with 0.5 μm drain contact and 3.5 μm low-doped drift layer (Figure S2), FWHM from rocking curves recorded at wafer center varied between 265 and 290 arcsec for the GaN <002> peak and 296 and 337 arcsec for the GaN <102> peak depending on utilization, and position(s) of the SiNx masking layer(s) (Figure S3). There is further room for improvement by SiNx optimization and drift layer scaling.

To assess the electrical performance, vertical p-n diodes were grown on 200 mm Si without and with  $SiN_x$  masking layer. Device fabrication was performed including mesa isolation, ohmic p-contact formation, Si substrate removal and backside ohmic drain contact. I-V characteristics are compared between the samples.

### **Supplementary information**

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 101007229. The JU receives support from the European Union's Horizon 2020 research and innovation program and Germany, France, Belgium, Austria, Sweden, Spain, Italy.

Figure S1 (Left) SEM image of GaN surface (w/o SiNx insertion) after Cl2 in-situ defects decoration, using inlens detector and reprocessed for automatic pits detection. (Right) pits count displayed as statistic mosaic chart on 1x1 μm² pixel.

Figure S2: Stack to evaluate influence of SiNx masking layers, ①-③ indicate position of SiNx masking layer.

Figure S3 Comparison of wafer FWHM data among four of the experiments showing the significant potential of the method on vertical device stacks.