#### Towards simulation of an unified address space for 128-bit massively parallel computers

Eduardo Tomasi, César Fuguet, Christian Fabre, Frédéric Pétrot

#### ▶ To cite this version:

Eduardo Tomasi, César Fuguet, Christian Fabre, Frédéric Pétrot. Towards simulation of an unified address space for 128-bit massively parallel computers. RISC-V Summit Europe 2023, Jun 2023, Barcelone, Spain. . hal-04392810

#### HAL Id: hal-04392810 https://hal.science/hal-04392810

Submitted on 14 Jan 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Towards Simulation of an Unified Address Space for 128-bit Massively Parallel Computers

Eduardo Tomasi<sup>1, 2</sup>, César Fuguet<sup>1</sup>, Christian Fabre<sup>1</sup>, Frédéric Pétrot<sup>2</sup>

<sup>1</sup> Univ. Grenoble Alpes, CEA, List, F-38000 Grenoble, France <sup>2</sup> Univ. Grenoble Alpes, CNRS, Grenoble INP, TIMA, F-38000 Grenoble, France

This work was funded by the French National Research Agency (ANR) under grant agreement ANR-21-CE25-0016 (MAPLURINUM)

## CONTEXT

### **Distributed Architectures**

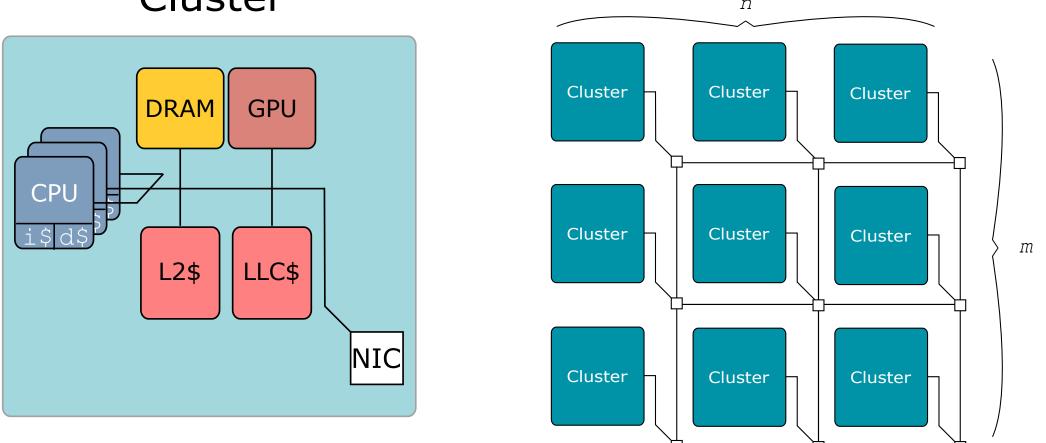

A cluster is a multicore computer that has its own memory hierarchy (multi-level caches and DRAM) and accelerators (such as GPUs). They are connected to each other through a high-performance communication network.

Cluster

C22 list

### Programming Models

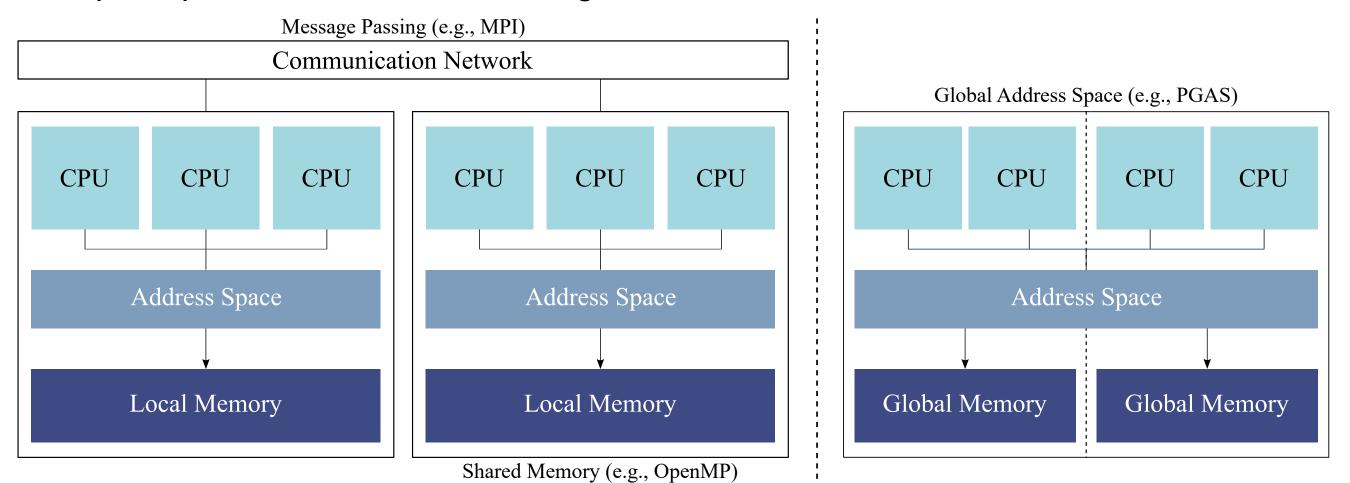

Within a cluster, memory coherence is ensured by hardware protocols, such that CPUs and accelerators communicate through a **shared memory.**

Beyond a cluster, coherence cannot be efficiently guaranteed. Processes in

Fig 1. An example of a typical clustered architecture, as can be found in high performance computing (HPC).

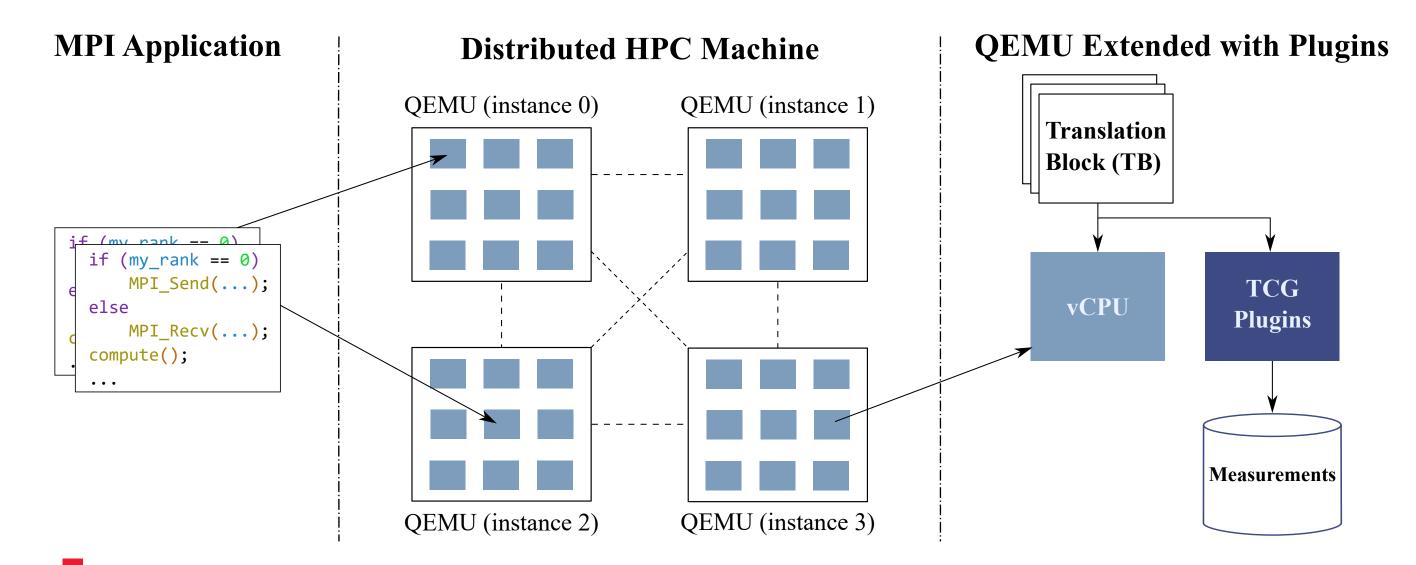

# SIMULATION OF A DISTRIBUTED SYSTEM

### QEMU

QEMU is an open-source machine emulator. Multiple architectures can be executed in a single host. It provides a virtual model of an entire machine (CPU, memory and devices). We chose it for three main reasons:

different clusters do not have access to each other's address space. Data can only be shared by **message passing** through the communication network.

A **global address space** offers a simplified programming model for distributed systems. It provides a high-level abstraction of the memory, hiding the complexity associated to its management.

## Fig 2. Shared Memory is used for parallelism inside a cluster, and Message Passing for parallelism between clusters.

MPI requires developers to expllicitly define the communication and synchronization points. Also, pointers cannot be shared, which complexifies the transfer of structured data from one process to another. PGAS, on the other hand, eliminates the need for explicit communication, but introduces challenges related to data consistency and synchronization.

## NON-INTRUSIVE WORKLOAD ANALYSIS

translation (DBT) to i reach very high s simulation speed. Also, i QEMU's scalability on SMP machines is good s [1].

interfaces to extend the simulator and add proper in HPC might, in the next decade, exceed 2<sup>64</sup> bytes. It allows us to rethink the subscribe to events during translation and execution of instructions [2].

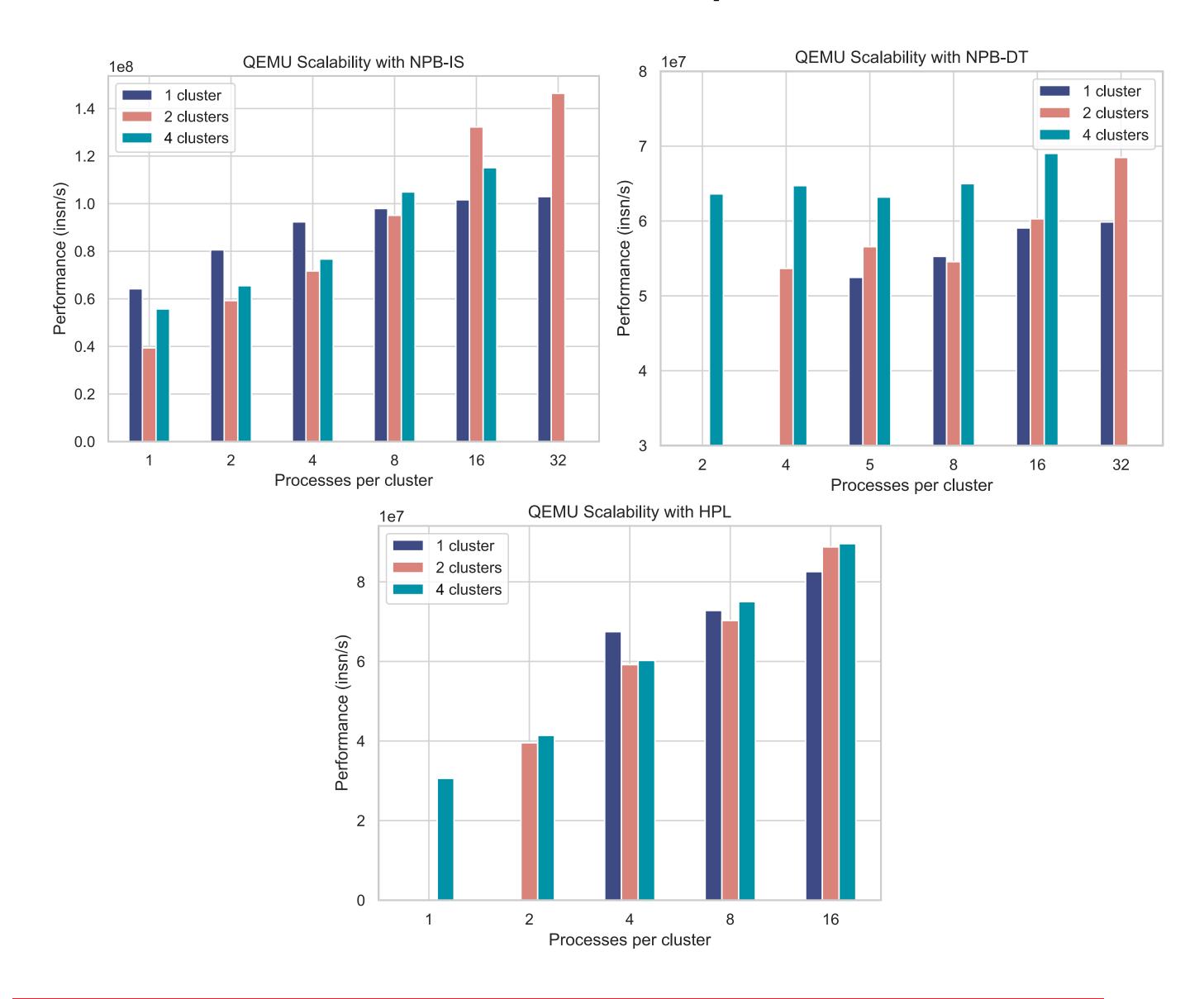

### Scalability

#### Fig 3. How to use QEMU to profile MPI calls.

To retrieve the metrics of interest, we need to monitor the code during execution. We need to know beforehand the virtual addresses of the MPI functions in the binary code. Through a QEMU plugin, we can monitor the translation blocks executed and profile the calls.

### Results

We can gather metrics such as: number of instructions during a MPI call, number of system calls and number of memory accesses.

|          |                |           | Syscalls   |            |  |   |          |  |

|----------|----------------|-----------|------------|------------|--|---|----------|--|

| Function | n <sub>p</sub> | 1 cluster | 2 clusters | 4 clusters |  |   | Syscalls |  |

|          | 1              | 0         | 1          | 624        |  | 1 |          |  |

#### References

[1] M. Badaroux, S. Miroddi, and F. Petrot, "To Pin or Not to Pin: Asserting the Scalability of QEMU Parallel Implementation," in 2021 24th Euromicro Conference on Digital System Design (DSD), Palermo, Italy: IEEE, Sep. 2021, pp. 238–245. doi: 10.1109/DSD53832.2021.00045.

[2] E. G. Cota and L. P. Carloni, "Cross-ISA machine instrumentation using fast and scalable dynamic binary translation," in Proceedings of the 15th ACM SIGPLAN/SIGOPS International Conference on Virtual Execution Environments, Providence RI USA: ACM, Apr. 2019, pp. 74–87. doi: 10.1145/3313808.3313811.

[3]F. Portas and F. Petrot, "Fast simulation of future 128-bit architectures," in 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE), Antwerp, Belgium: IEEE, Mar. 2022, pp. 1131–1134. doi: 10.23919/DATE54114.2022.9774706.

[4] A. Waterman and K. Asanović, "Chapter 6, RV128I Base Integer Instruction Set, Version 1.7," in The RISC-V Instruction Set Manual - Volume I: Unpriviliged ISA, 20191213th ed.The RISC-V Foundation, 2019. [Online]. Available: https://riscv.org/technical/specifications/

|               | 1                            |                                   | 4                                             | 000                                  | FUNCTION | Пр                 | I Cluster           | z ciuslers          | 4 Clusters          |

|---------------|------------------------------|-----------------------------------|-----------------------------------------------|--------------------------------------|----------|--------------------|---------------------|---------------------|---------------------|

| MPI_Allreduce | 2<br>4<br>8<br>16<br>32      | 93<br>78<br>80<br>85<br>144       | 41<br>3656<br>5056<br>4203<br>294             | 888<br>2379<br>2178<br>126<br>-      | MPI_Send | 5<br>8<br>16<br>32 | 9<br>10<br>11<br>19 | 9<br>10<br>12<br>22 | 10<br>10<br>15<br>- |

| MPI_Alltoall∨ | 1<br>2<br>4<br>8<br>16<br>32 | 37<br>59<br>51<br>55<br>65<br>109 | 4763<br>7627<br>8529<br>8762<br>9756<br>10666 | 5488<br>5809<br>6792<br>7242<br>4361 | MPI_Recv | 5<br>8<br>16<br>32 | 4<br>5<br>11<br>9   | 4<br>5<br>7<br>9    | 4<br>5<br>8<br>-    |

Table I. Number of syscalls during MPI calls of NPB-IS. Table II. Number of syscalls during MPI calls of NPB-DT.

|                | No plugin | insr  | n plugin | MPI plugin |          |  |

|----------------|-----------|-------|----------|------------|----------|--|

| n <sub>p</sub> | MIPS      | MIPS  | Slowdown | MIPS       | Slowdown |  |

| 1              | 74.3      | 64.2  | 13.6%    | 40.0       | 46.1%    |  |

| 2              | 101.6     | 80.6  | 20.7%    | 48.7       | 52.0%    |  |

| 4              | 126.2     | 92.3  | 26.9%    | 53.7       | 57.4%    |  |

| 8              | 155.3     | 97.9  | 36.9%    | 60.0       | 61.3%    |  |

| 16             | 170.0     | 101.6 | 40.2%    | 64.5       | 62.1%    |  |

| 32             | 203.2     | 102.9 | 49.3%    | 72.3       | 64.4%    |  |

Table III. Impact of the plugins during execution of NPB-IS.