▲□▶ ▲□▶ ▲□▶ ▲□▶ □ のQで

# Acceleration of contractor algebra on RISCV in the context of mobile robotic

#### Filiol Pierre, Jaulin Luc, Le Lann Jean-Christophe, Bollengier Theotime

June 25, 2023

### Table of contents

- 1 A bit of context

- 2 The RiscV standard

- Interval representation

- Adding support for xinterval

- 5 Emulation platform

### 6 Conclusion

▲ロ ▶ ▲周 ▶ ▲ 国 ▶ ▲ 国 ▶ ● の Q @

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ のQで

### Interval arithmetic in robotic

Interval analysis is standardized in the IEEE 1788 standard .

Robotic applications using intervals rely on libraries such as :

- ibex/gaol

- 2 libieee1788

- Impfi

#### Such libraries have flaws

- Oprimi Portability issues.

- Out designed with robotic in mind

- Lack of documentation

#### Conclusion

### Interval arithmetic in robotic

#### Interesting features for a robotic-oriented implementation

Precision is often not the biggest concern in mobile robotic. However, some other criteria are worth to be optimized :

- Overall execution speed

- Portability

- Guaranteed results (even if pessimistic)

- Inergy efficiency (embedded context).

#### Hardware implementation can be a solution

This allows to

- Reach a more accurate bitwise and timing mastery

- Portable by essence (you provide the coprocessor)

- Be power efficient

### Interval arithmetic in robotic

#### Scope of the study

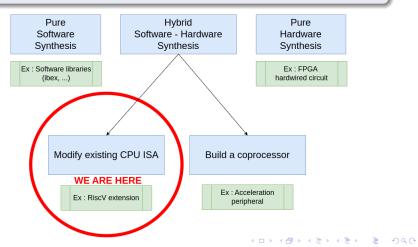

There are several ways to produce hardware accelerators :

Adding support for xinterval

Emulation platform

Conclusion 0

### The RiscV standard

#### Some key strengths

- Open specification and standard

- 2 Modular

- Section 2 Extensible

- Simple (compared to x86/arm/...)

- Omplete software stack (gcc, ...)

#### Extensibility is very interesting for us

We can insert our interval operations and modify riscv-gcc to use them.

A bit of context

The RiscV standard ○●○○○

Interval representation

Adding support for xinterva

mulation platform Co

Reserved

▲ロト ▲周ト ▲ヨト ▲ヨト ヨー のくで

### Riscv modular architecture

#### Integer multiplication М Compressed С and division Dynamically Atomic operations A translated J. User ISA languages Specification Floating point - single (F), Transactional т F D Q double (D), guad (Q) precision memory Base integer Ρ Packed SIMD V Vector operations User-level Ν interrupts L Decimal floating point В Bit manipulation Machine level Frozen Privileged ISA Specification Draft Supervisor level Hypervisor

**RISC-V Instruction Set Architecture**

Conclusion

### Extending the RiscV standard

#### RiscV has several advantages in term of extensibility

- It offers standard extensions to start building your solution

- By design, a lot of space is available for additional instructions and extension

- RiscV gcc compiler can be modified to support new instructions (strong compiler basis).

#### The goal is to build a RiscV extension called xinterval

- It is based on standard extensions I,M,A,F,D

- It provides instructions for computing with intervals

- The new instructions can be used in C language

Adding support for xinterva

Emulation platform

Conclusion O

### Why I,M,A,F,D ?

#### RV32I brings basic integer instructions + integer registers

|                           |   |        |                | s: RV321 and RV641 |                |  |

|---------------------------|---|--------|----------------|--------------------|----------------|--|

| Category Name             |   | F      | RV32I Base     |                    | +RV64I         |  |

| Shifts Shift Left Logical |   | SLL    | rd,rs1,rs2     | SLLW               | rd,rs1,rs2     |  |

| Shift Left Log. Imm.      | Ι | SLLI   | rd, rs1, shamt | SLLIW              | rd, rsl, shamt |  |

| Shift Right Logical       | R | SRL    | rd,rs1,rs2     | SRLW               | rd,rs1,rs2     |  |

| Shift Right Log. Imm.     | Ι | SRLI   | rd, rs1, shamt | SRLIW              | rd, rsl, shamt |  |

| Shift Right Arithmetic    | R | SRA    | rd,rs1,rs2     | SRAW               | rd,rs1,rs2     |  |

| Shift Right Arith. Imm.   | I | SRAI   | rd, rs1, shamt | SRAIW              | rd, rsl, shamt |  |

| Arithmetic ADD            | R | ADD    | rd,rs1,rs2     | ADDW               | rd,rs1,rs2     |  |

| ADD Immediate             | I | ADDI   | rd, rs1, imm   | ADDIW              | rd,rsl,imm     |  |

| SUBtract                  | R | SUB    | rd,rs1,rs2     | SUBW               | rd,rs1,rs2     |  |

| Load Upper Imm            | U | LUI    | rd,imm         |                    |                |  |

| Add Upper Imm to PC       | Ū | AUIPC  | rd, imm        |                    |                |  |

| Logical XOR               | R | XOR    | rd,rs1,rs2     |                    |                |  |

| XOR Immediate             | Ι | XORI   | rd, rsl, imm   |                    |                |  |

| OR                        | R | OR     | rd,rs1,rs2     |                    |                |  |

| OR Immediate              | Ι | ORI    | rd, rsl, imm   |                    |                |  |

| AND                       | R | AND    | rd,rs1,rs2     |                    |                |  |

| AND Immediate             | Ι | ANDI   | rd,rsl,imm     |                    |                |  |

| Compare Set <             | R | SLT    | rd,rs1,rs2     |                    |                |  |

| Set < Immediate           | Ι | SLTI   | rd,rsl,imm     |                    |                |  |

| Set < Unsigned            | R | SLTU   | rd,rs1,rs2     |                    |                |  |

| Set < Imm Unsigned        | I | SLTIU  | rd,rsl,imm     |                    |                |  |

| Branches Branch =         | В | BEQ    | rs1,rs2,imm    |                    |                |  |

| Branch +                  | В | BNE    | rs1,rs2,imm    |                    |                |  |

| Branch <                  | В | BLT    | rs1,rs2,imm    |                    |                |  |

| Branch ≥                  | В | BGE    | rs1,rs2,imm    |                    |                |  |

| Branch < Unsigned         | В | BLTU   | rsl,rs2,imm    |                    |                |  |

| Branch ≥ Unsigned         | В | BGEU   | rs1,rs2,imm    |                    |                |  |

| Jump & Link J&L           | J | JAL    | rd,imm         |                    |                |  |

| Jump & Link Register      | Ι | JALR   | rd,rsl,imm     |                    |                |  |

| Synch Synch thread        | Ι | FENCE  |                |                    |                |  |

| Synch Instr & Data        | Ι | FENCE  | .1             |                    |                |  |

| Environment CALL          | Ι | ECALL  |                |                    |                |  |

| BREAK                     | I | EBREAD | к              |                    |                |  |

200

Emulation platform Co

Conclusion O

## Why I,M,A,F,D ?

#### RV32F and RV32D brings basic floating point instructions

- arithmetic instructions for float and double

- Special math instructions for float and double

- Onversion instructions

- memory related instructions

#### Register configurations

Using I,M,A,F,D provides the following registers :

- **0** 32 registers of size 32 bits for unsigned instructions

- **2** 32 registers of size 64 bits for floating-point instructions

- 32 bits RiscV allows to have 64 bits long registers.

Emulation platform Co

Conclusion 0

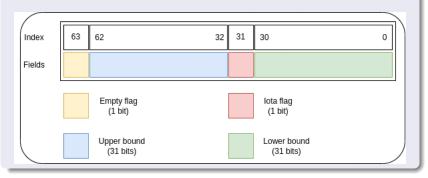

### How to represent an interval in hardware ?

#### Intervals are represented using a 64 bits word

They fit inside the 64 bits double registers brought by D extension.

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ 三三 - のへぐ

Conclusion

About bounds encoding and flags

Upper and lower bounds are encoded on 31 bits

This differs from the IEEE-754 standard which uses 32 bits.

- 1 sign bit (same as IEEE-754)

- 2 7 bits exponent (against 8 in IEEE-754)

- 3 23 bits mantissa (same as IEEE-754)

Overall precision remain the same but the range of number we can represent is smaller. This difference is often pointless in robotic.

#### This allows to define two flags

- an empty flag (to represent the empty set)

- 2 a iota flag

Conclusion

### About the iota flag

In one of our previous work, we highlighted a phenomenon which happens in most interval solvers.

Let us consider the following set  $\mathbb{X}$

$$\mathbb{X} = \{ (x_1, x_2) \, | \, x_2 + \sqrt{x_1 + x_2} \in [1, 2] \}. \tag{1}$$

Let us try to compute an inner and outer approximations of Xusing an existing solver (CODAC) :

```

1 from codac import *

2 from vibes import *

3 X0=IntervalVector([[-10,10],[-10,10]])

f = Function(x1, x2, x2+sqrt(x1+x2))

4

S=SepFwdBwd(f,Interval(1,2))

6 vibes.beginDrawing()

SIVIA(X0,S,0.01)

```

Interval representation  $000 \bullet 00$

Adding support for xinterva

mulation platform Co 000000 0

### About the iota flag

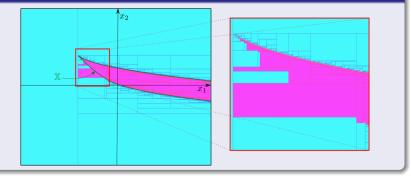

#### We obtain the following paving (which is wrong)

▲□ > ▲圖 > ▲目 > ▲目 > ▲目 > ● ④ < ⊙

mulation platform Con 0000000 0

### About the iota flag

#### Some box are wrongly classified

This happens because contractor-based methods obtain an inner approximation by considering a contractor for the complentary of  $\mathbb X$  as

$$\mathbb{X} = \{ (x_1, x_2) \, | \, x_2 + \sqrt{x_1 + x_2} \notin [1, 2] \}.$$

(2)

whereas it should be

$$\overline{\mathbb{X}} = \{ (x_1, x_2) \, | \, x_2 + \sqrt{x_1 + x_2} \notin [1, 2] \text{ or } x_1 + x_2 < 0 \}.$$

(3)

#### This what iota flag is meant for

It is used to mark intervals that are victims of this phenomenon after a chain of forward contractions. Those intervals are then trapped and handled accordingly during backward contraction.

Emulation platform Cor 0000000 0

### About the iota flag

#### Some box are wrongly classified

This happens because contractor-based methods obtain an inner approximation by considering a contractor for the complentary of  $\mathbb X$  as

$$\mathbb{X} = \{ (x_1, x_2) \, | \, x_2 + \sqrt{x_1 + x_2} \notin [1, 2] \}.$$

(4)

whereas it should be

$$\overline{\mathbb{X}} = \{ (x_1, x_2) \, | \, x_2 + \sqrt{x_1 + x_2} \notin [1, 2] \text{ or } x_1 + x_2 < 0 \}.$$

(5)

#### This what iota flag is meant for

It is used to mark intervals that are victims of this phenomenon after a chain of forward contractions. Those intervals are then trapped and handled accordingly during backward contraction. rd Interval represent

Adding support for xinterval

Emulation platform Co

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ ▲ 三 ● ● ●

Conclusion 0

### The xinterval custom extension

#### Overview

- It requires I,M,A,F,D standard extensions.

- 2 It implements the interval model detailed previously.

- It consists of a set of assembly instructions which extend RiscV standard.

The RiscV standard Interval representation

Adding support for xinterval 000000

mulation platform Co

Conclusion 0

### Main instructions of xinterval

#### Conversion functions

| Name          | Туре  | Effect                                  |

|---------------|-------|-----------------------------------------|

| itvlcvt.x.inf | D.S   | Set the lower bound of the interval     |

|               | 0,5   | stored in rd to be the fp value in rs1. |

| itulout y cup | DC    | Set the upper bound of the interval     |

| itvlcvt.x.sup | D,S   | stored in rd to be the fp value in rs1. |

| itulout y cup | D,S,T | Use the fp values in rs1 and rs2 to     |

| itvlcvt.x.sup | D,3,1 | build a new interval in rd.             |

Emulation platform Co

### Main instructions of xinterval

### Check functions

| Name        | Туре | Effect                          |

|-------------|------|---------------------------------|

| itvlisempty | d,S  | Tells if the interval stored in |

| itvisempty  | u,5  | rs1 is empty                    |

| itvlhasiota | d.S  | Tells if the interval stored    |

| itvinasiota | u,3  | in rs1 is iota-flagged          |

#### Set functions

| Name      | Туре  | Effect                          |

|-----------|-------|---------------------------------|

| itvlinter | D.S.T | Store in rd the intersection of |

| luniter   | D,3,1 | the intervals in rs1 and rs2    |

| itvlunion | D.S.T | Store in rd the union of        |

| Itviumon  | D,3,1 | the intervals in rs1 and rs2    |

Adding support for xinterval

Emulation platform C

Conclusion 0

### Main instructions of xinterval

#### Forward and backward contractors

| Addition    | Subtraction | Multiplication | Division  |

|-------------|-------------|----------------|-----------|

| Square root | Square      | Exponential    | Logarithm |

| Cosinus     | Sinus       |                |           |

#### Using addition forward contractor in assembly

addFwCtc fs2, fs3, fs4

#### Using addition backward contractor in assembly

addBwCtc1 fs3 fs2, fs3, fs4 addBwCtc2 fs4 fs2, fs3, fs4

Emulation platform Conclusion

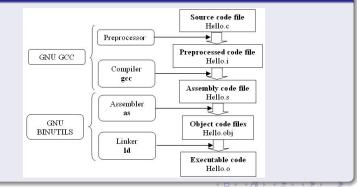

### How to make our new instructions valid in C ?

By default, gcc is totaly ignorant about xinterval

We need to instruct him how to use them. Luckily, this is handled by the riscv-toolchain.

#### Solution : Modify the assembler and binutils

Adding support for xinterval

nulation platform Cor

Modifying binutils

#### Telling the assembler how to handle forward contractors

|  |                       | "D,S,T", MATCH_ITVLADD,   | MASK_ITVLADD,   | <pre>match_opcode, 0},</pre> |

|--|-----------------------|---------------------------|-----------------|------------------------------|

|  | INSN CLASS XINTERVAL, | "D,S,T", MATCH ITVLSUB,   | MASK ITVLSUB,   | <pre>match opcode, 0},</pre> |

|  | INSN_CLASS_XINTERVAL, | "D,S,T", MATCH_ITVLMUL,   | MASK_ITVLMUL,   | <pre>match_opcode, 0},</pre> |

|  | INSN_CLASS_XINTERVAL, | "D,S,T", MATCH_ITVLDIV,   | MASK_ITVLDIV,   | <pre>match_opcode, 0},</pre> |

|  | INSN_CLASS_XINTERVAL, | "D,S,T", MATCH_ITVLINTER, | MASK_ITVLINTER, | <pre>match_opcode, 0},</pre> |

|  | INSN_CLASS_XINTERVAL, | "D,S,T", MATCH_ITVLUNION, | MASK_ITVLUNION, | <pre>match_opcode, 0},</pre> |

|  | INSN_CLASS_XINTERVAL, | "D,S,T", MATCH_ITVLSQRT,  | MASK_ITVLSQRT,  | <pre>match_opcode, 0},</pre> |

|  | INSN CLASS XINTERVAL, | "D,S,T", MATCH_ITVLSQR,   | MASK ITVLSQR,   | <pre>match opcode, 0},</pre> |

|  | INSN CLASS XINTERVAL, | "D,S,T", MATCH_ITVLEXP,   | MASK ITVLEXP,   | <pre>match opcode, 0},</pre> |

|  | INSN CLASS XINTERVAL, | "D,S,T", MATCH ITVLLOG,   | MASK ITVLLOG,   | <pre>match opcode, 0},</pre> |

|  | INSN CLASS XINTERVAL, | "D,S,T", MATCH ITVLCOS,   | MASK ITVLCOS,   | <pre>match opcode, 0},</pre> |

|  | INSN CLASS XINTERVAL, | "D,S,T", MATCH ITVLSIN,   | MASK ITVLSIN,   | match opcode, 0},            |

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ 三 のへぐ

Adding support for xinterval Emulation platform Conclusion 000000

### Modifying binutils

#### Now this code is valid in C

```

1 // inline function to allow the use of xinterval

instruction addfwctc

2 // This instruction add 2 intervals stored in double

registers and stores the result in a double

register

```

```

3 inline interval __attribute__((always_inline))

_addFwCtc(interval itv1, interval itv2) {

```

```

interval result:

4

```

```

asm("addfwctc %0,%1,%2" : "=f"(result) : "f"(itv1),

5

"f"(itv2)):

```

```

return result;

6

```

7 }

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ のQで

Adding support for xinterval

Emulation platform •000000

Conclusion

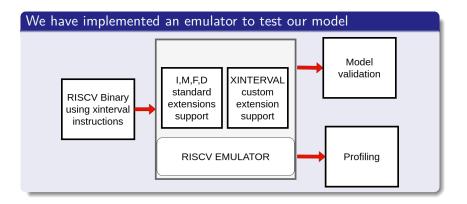

### Building an emulator to test everything

◆□ ▶ ◆□ ▶ ◆ □ ▶ ◆ □ ▶ ◆ □ ◆ ○ へ ⊙

Adding support for xinterval

Emulation platform ○●○○○○○

Conclusion

### A classic localization problem

#### Localisation problem using landmarks with known positions

- We want to estimate the position (x,y) of a robot which navigates around 3 landmarks with known positions.

- **②** It periodically receives his distance relative to each landmark with a given accuracy  $\epsilon$ .

rd Interval represer

Adding support for xinterval

Emulation platform

Conclusion 0

### A classic localization problem

#### Localisation problem using landmarks with known positions

- At each step (x,y) must obey the following constraints :  $\begin{array}{l} (x - a_{1x})^2 + (y - a_{1y})^2 \in [(d_1 - \epsilon)^2, (d_1 + \epsilon)^2] \\

(x - a_{2x})^2 + (y - a_{2y})^2 \in [(d_2 - \epsilon)^2, (d_2 + \epsilon)^2] \\

(x - a_{3x})^2 + (y - a_{3y})^2 \in [(d_3 - \epsilon)^2, (d_3 + \epsilon)^2] \end{array}$

- Using properties of forward-backward propagation, we can find a contractor which computes the set of x and y which meet those requirements.

Adding support for xinterva

Emulation platform

Conclusion

### Building the application

#### The compiled code

The code below corresponds to the contractor to one landmark :

| <pre>box2d CinRing(box2d input, interval cx, interval cy, interval r) {</pre>             |

|-------------------------------------------------------------------------------------------|

| <pre>interval x = input.x;<br/>interval y = input.y;</pre>                                |

| <pre>interval a = _subFwCtc(x, cx);<br/>interval b = _subFwCtc(y, cy);</pre>              |

| interval a2 = _sqrFwCtc(a);<br>interval b2 = _sqrFwCtc(b);<br>interval r2 = _sqrFwCtc(r); |

| a2 = _addBwCtc1(r2, a2, b2);<br>b2 = _addBwCtc2(r2, a2, b2);                              |

| a = _sqrBwCtc(a2, a);<br>b = _sqrBwCtc(b2, b);                                            |

| <pre>x = _subBwCtcl(a, x, cx);<br/>y = _subBwCtcl(b, y, cy);</pre>                        |

| <pre>box2d output = {x, y};<br/>return output;<br/>}</pre>                                |

Adding support for xinterva

Emulation platform

Conclusion 0

### Building the application

#### Binary dump of the compiled code

| - |           |                      |                      |

|---|-----------|----------------------|----------------------|

|   | 80802e24  | <cinring>:</cinring> |                      |

|   |           | e4010113             | addi sp,sp,-448      |

|   |           | 1a812e23             | sw s0.444(sp)        |

|   |           | 1c010413             | addi s0,sp,448       |

|   | 80002e30: | 22b587d3             | fmv.d fa5,fa1        |

|   | 80002e34: | e6c43427             | fsd fa2408(s0)       |

|   |           | e6d43027             | fsd fa3,-416(s0)     |

|   | 80802e3c: | e4e43c27             | fsd fa4,-424(s0)     |

|   | 80002e40: | e6a43827             | fsd fa0,-400(s0)     |

|   | 80002e44: | e6f43c27             | fsd fa5,-392(s0)     |

|   | 80002e48: | e7043787             | fld fa5,-400(s0)     |

|   | 80002e4c: | fef43427             | fsd fa5,-24(s0)      |

|   | 80002e50: | e7843787             | fld fa5,-392(s0)     |

|   | 80002e54: | fef43027             | fsd fa5,-32(s0)      |

|   | 80002e58: | fe843787             | fld fa5,-24(s0)      |

|   | 80002e5c: | eaf43c27             | fsd fa5,-328(s0)     |

|   | 80002e60: | e6843787             | fld fa5,-408(s0)     |

|   | 80002e64: | eaf43827             | fsd fa5,-336(s0)     |

|   | 80002e68: | eb843787             | fld fa5,-328(s0)     |

|   | 80002e6c: | eb043707             | fld fa4,-336(s0)     |

|   | 80002e70: | 02e7c78b             | subfwctc fa5,fa5,fa4 |

|   | 80002e74: | eaf43427             | fsd fa5,-344(s0)     |

|   | 80002e78: | ea843787             | fld fa5,-344(s0)     |

|   | 80002e7c: | fcf43c27             | fsd fa5,-40(s0)      |

|   | 80002e80: | fe043787             | fld fa5,-32(s0)      |

|   | 80002e84: | ecf43827             | fsd fa5,-304(s0)     |

|   | 80002e88: | e6043787             | fld fa5,-416(s0)     |

|   | 80002e8c: | ecf43427             | fsd fa5,-312(s0)     |

|   | 80002e90: | ed043787             | fld fa5,-304(s0)     |

|   | 80002e94: | ec843707             | fld fa4,-312(s0)     |

|   | 80802e98: | 02e7c78b             | subfwctc fa5,fa5,fa4 |

|   |           |                      |                      |

Adding support for xinterva

Emulation platform

Building the application

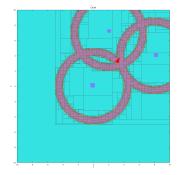

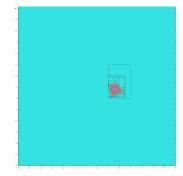

The paving obtained from inside the emulator :

(a) Union of contractors

(b) Intersection of contractors

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ のQで

Figure: Using contractors to solve a localisation problem

A bit of conte

The RiscV standard

Interval representation 000000 Adding support for xinterval

Emulation platform 000000●

▲□▶ ▲□▶ ▲□▶ ▲□▶ ■ ●の00

Conclusion 0

### Building the application

#### Our emulator allows us to monitor the execution

We can for example :

- Obtain various metrics (nb of instructions, frequency, ...).

- Estimate timing and clock cycles.

▲ロ ▶ ▲周 ▶ ▲ 国 ▶ ▲ 国 ▶ ● の Q @

### Conclusion

#### During this presentation we have shown how to :

- Build a RiscV extension to compute with intervals.

- Ø Modify the gcc compiler to use it in C.

- **③** Build an emulator to test and profile our model.

- Build an run a small robotic application.