# Demonstration of avalanche capability in 800 V vertical GaN-on-Silicon diodes

Youssef Hamdaoui, Idriss Abid, Sondre Michler, Katir Ziouche, F Medjdoub

## ▶ To cite this version:

Youssef Hamdaoui, Idriss Abid, Sondre Michler, Katir Ziouche, F Medjdoub. Demonstration of avalanche capability in 800 V vertical GaN-on-Silicon diodes. Applied Physics Express, 2023, 17 (1), pp.016503. 10.35848/1882-0786/ad106c . hal-04313786

## HAL Id: hal-04313786 https://hal.science/hal-04313786v1

Submitted on 29 Nov 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### ACCEPTED MANUSCRIPT • OPEN ACCESS

# Demonstration of avalanche capability in 800 V vertical GaN-on-Silicon diodes

To cite this article before publication: Youssef Hamdaoui et al 2023 Appl. Phys. Express in press https://doi.org/10.35848/1882-0786/ad106c

#### Manuscript version: Accepted Manuscript

Accepted Manuscript is "the version of the article accepted for publication including all changes made as a result of the peer review process, and which may also include the addition to the article by IOP Publishing of a header, an article ID, a cover sheet and/or an 'Accepted Manuscript' watermark, but excluding any other editing, typesetting or other changes made by IOP Publishing and/or its licensors"

This Accepted Manuscript is © 2023 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd.

#### $\odot$

As the Version of Record of this article is going to be / has been published on a gold open access basis under a CC BY 4.0 licence, this Accepted Manuscript is available for reuse under a CC BY 4.0 licence immediately.

Everyone is permitted to use all or part of the original content in this article, provided that they adhere to all the terms of the licence <u>https://creativecommons.org/licences/by/4.0</u>

Although reasonable endeavours have been taken to obtain all necessary permissions from third parties to include their copyrighted content within this article, their full citation and copyright line may not be present in this Accepted Manuscript version. Before using any content from this article, please refer to the Version of Record on IOPscience once published for full citation and copyright details, as permissions may be required. All third party content is fully copyright protected and is not published on a gold open access basis under a CC BY licence, unless that is specifically stated in the figure caption in the Version of Record.

View the article online for updates and enhancements.

## Demonstration of avalanche capability in 800 V vertical GaN-on-Silicon diodes

Youssef Hamdaoui<sup>1\*</sup>, Idriss Abid<sup>1</sup>, Sondre Michler<sup>2</sup>, Katir Ziouche<sup>1</sup> and Farid Medjdoub<sup>1</sup> <sup>1</sup>IEMN (Institute of Electronics, Microelectronics and Nanotechnology), CNRS-IEMN, University of Lille, France

<sup>2</sup>Department Innovation Management, Siltronic AG, München, Germany

E-mail: <u>\*youssef.hamdaoui@univ-lille.fr</u>

High-quality pseudo-vertical p-n diodes using a GaN-on-silicon heterostructure are reported. An optimized fabrication process including a beveled deep mesa as edge termination and reduced ohmic contact resistances enabled high on-state current density and low on-resistance. A uniform breakdown voltage was observed at 830 V. The positive temperature dependence of the breakdown voltage clearly indicates the avalanche capability, reflecting both the high material and processing quality of the vertical p-n diodes. The Baliga figure of merit, around 2 GW/cm<sup>2</sup>, which is favorably comparable to the state-of-the-art, combined with avalanche capability paves the way for fully vertical GaN-on-Silicon power devices.

As part of the development of next generation low-cost power devices, GaN-based high electron mobility transistors (HEMTs) stand out as an undeniable candidate due to their high electric field, high electron mobility, and large band gap  $^{1-5)}$ . In addition to its physical properties that exceed the limitations of silicon, GaN technology is cost-effective when grown on silicon (Si). While lateral GaN HEMTs have demonstrated high performances up to 900 V voltage operation, several challenges still plague the widespread use of this technology, including:

1. Electron trapping caused by complex hetero-epitaxy and surface states.

2. Destructive breakdown (in contrast to avalanche), resulting from the peak electric field at the vicinity of the gate terminal.

3. Relatively large device size due to the substantial gate-to-drain distance required to increase the breakdown voltage.

On the other hand, vertical GaN architectures offer the potential to overcome these limitations <sup>6),7)</sup>. A vertical structure takes advantage of junction-based N- and P-doped epitaxial layers, leading to a better distribution of the electrical field enabling to avoid peak electric field and charge trapping issues  $^{8)-16)}$ . The device breakdown voltage scales with the drift layer thickness, allowing small fingerprints. Furthermore, it has been demonstrated by several groups that fully vertical GaN structures grown on GaN bulk substrate or pseudovertical devices on sapphire substrate exhibit avalanche breakdown capability 17-20). Nevertheless, for widespread market adoption, a cost-effective substrate such as silicon would be preferred. Recently, pseudo-vertical GaN-on-Si p-n diodes have been demonstrated, as well as fully vertical GaN-on-Si device proof of concept <sup>21-27</sup>). However, the avalanche breakdown capability has not yet been proved, even though it is a crucial feature required for power electronic devices. Indeed, avalanche capability ensures a nondestructive behavior close to the breakdown region and thus enhances the device robustness, and reliability of the overall system. Sidewall parasitic leakage current through the mesa, high dislocation density within the GaN drift layer, and point defects are some of the issues that lead to destructive and non-uniform breakdown, which is a significant barrier to achieving avalanche capability in GaN-on-Silicon based power devices <sup>7</sup>).

In this letter, pseudo-vertical GaN-on Si p-n diodes with a drift layer thickness of 4.5  $\mu$ m, are discussed. Uniform breakdown with avalanche capability around 800V, and low on-resistance (Ron) is achieved, reflecting the high material quality.

The heterostructure was grown by metalorganic chemical vapor deposition (MOCVD)

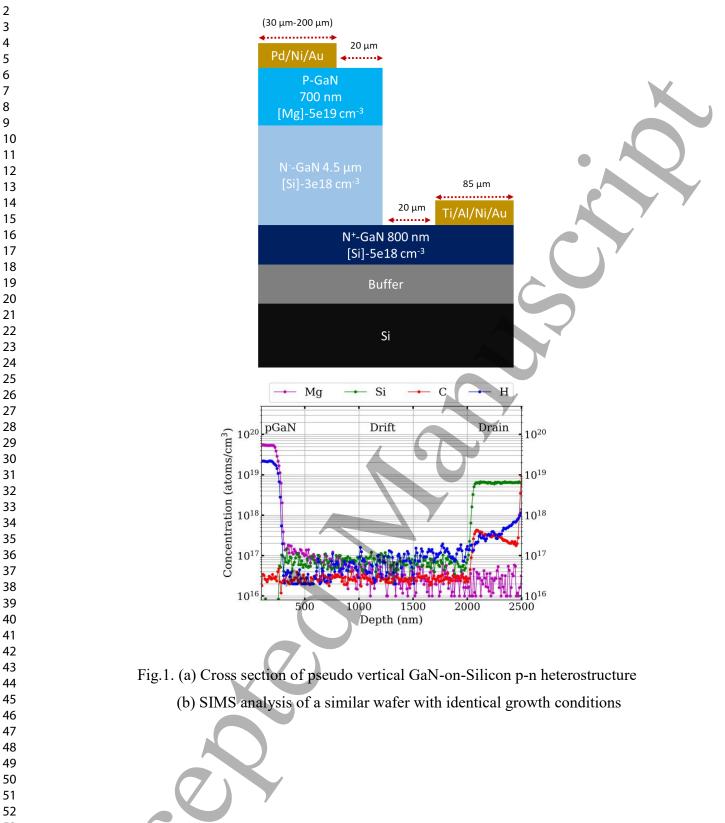

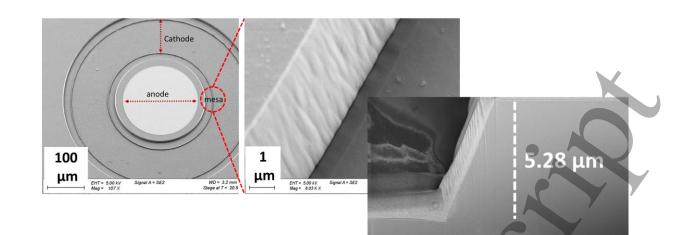

on 6-inch silicon substrate. A schematic cross-sectional diagram of a vertical GaN-on-Si pn diode is shown in Fig. 1(a). The growth process began with a proprietary buffer layer stack, followed by a 800-nm thick n+ GaN Si-doped layer ( $5 \times 10^{18}$  cm<sup>-3</sup>), a 4.5-µm thick n-type (Sidoped) drift layer ( $3 \times 10^{16}$  cm<sup>-3</sup>) and a 700-nm thick p-type GaN Mg-doped layer ( $5 \times 10^{19}$  $cm^{-3}$  with  $3 \times 10^{17}$  cm<sup>-3</sup> hole concentration). Capacitance-voltage (C-V) measurements were performed on the diodes in order to confirm the net ionized doping concentration in the drift region, which was found to be  $\sim 9 \times 10^{15}$  cm<sup>-3</sup>. Additionally, SIMS analysis was carried out with identical growth conditions to verify the epitaxial doping of the various species (Fig. 1(b)). The fabrication process started with the deposition of thick SiO<sub>2</sub> layer by plasmaenhanced chemical vapor deposition (PECVD), which is patterned by Reactive-ion etching (RIE) plasma. This layer serves as a hard mask for the mesa etching. To reach the n+ layer, deep mesa etching were performed (about 5.2 µm) using an optimized Cl<sub>2</sub>/Ar based inductively coupled plasma (ICP) recipe. The developed recipe reduced the sidewall leakage current and produced a beveled etching for edge termination<sup>28</sup>). The angle appears in Fig. 2, which was obtained with a focused ion beam by etching a vertical cross section using platinum metal as etching mask (white region in Fig. 2). The angle of the sidewalls was estimated to be around 75°. The resulting angle is used to spread the electric field at the edge of the device over a distance that is larger than the drift region thickness. This technique results in a gradient of the electrostatic potential and thus helps to manage the electric field around the anode electrode. The n+ layer was then contacted with the deposition and patterning of Ti/Al/Ni/Au metal stack by evaporation using a standard lift-off process. Subsequently, a Pd/Ni/Au stack was deposited using evaporation on top of the p-GaN layer. Both n-type and p-type contacts were optimized to achieve low ohmic contact resistances using 500°C annealing for 10 min. The corresponding contact resistances are around 5×10<sup>-6</sup>  $\Omega$ .cm<sup>2</sup> and 10<sup>-4</sup>  $\Omega$ .cm<sup>2</sup> for n-type and p-type contacts, respectively.

Template for APEX (Mar. 2022)

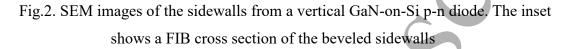

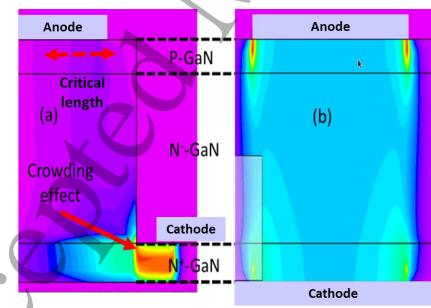

Forward characteristics of 30 µm anode diameter vertical diodes, with 70 µm as top mesa diameter, were evaluated using DC measurements from 0 to 20 V as a function of temperature. The device delivered a high current density (J) with low differential on-stateresistance (Ron  $< 0.35 \text{ m}\Omega.\text{cm}^2$ ) and a threshold voltage (Vth) of 4.5 V (Fig. 3.a and b). The Vth value can be reduced by further optimizing the p-type ohmic contacts. The on-state resistance value was extracted  $\left(\frac{\Delta V}{\Delta J}(V)\right)$  in the linear region at 12 V, where the slope is constant and normalized according to the anode area. Two distinct regimes can be observed: 1) between Vth and 12 V, the current spreads towards the epitaxial layers and the slope of Ron decreases before stabilizing. When reaching 12 V, a saturation of the forward current and a degradation of Ron are observed. This is attributed to the pseudo-vertical architecture, where the current crowds at the edge of the n+ layer, limiting the current spreading under high bias due to thermal dissipation issues. From TCAD simulations (see Fig. 4.a) using Silvaco Atlas software, the current crowding contribution can be estimated to be about 40 % of Ron value. Indeed, the current of the pseudo vertical structure flows vertically from the edge of the anode area towards the N+ layer where the charge transport change direction, generating a crowding effect that degrades the specific on-resistance. This results also in a critical length of the current spreading (Fig. 4.a) above which the Ron becomes dependent on the anode diameter. In turn, the size of the contact should be smaller than the critical length. This issue is specific to the pseudo-vertical architecture and does not occur in a fully vertical structure (Fig. 4.b) <sup>07),23)</sup>. Therefore, this explains the choice in this work of a small anode diameter (30 µm), which is near the critical length of current spreading and in line with the literature <sup>24–27)</sup>. For a more in-depth analysis of the on-state behavior of the diodes,

I(V) measurements were conducted at various temperatures (Fig. 3.a). Elevated temperatures slightly decrease Vth and enhance the current spreading due to increased thermal diffusion of carriers and narrowing of the bandgap. However, in the second regime (beyond 12 V), the degradation of Ron is more pronounced at high temperature (Fig. 3.b), confirming the thermal dissipation challenges associated to the pseudo-vertical design. Increasing the thickness of the n+ layer can reduce the thermal dissipation issue, but the additional resistance corresponding to the crowding effect will persist.

Fig.3. (a) Forward current measurements and (b) Differential on-state resistance measurements at various temperatures.

Fig. 4. Distribution of the current density extracted from Silvaco TCAD in on-state conditions for a pseudo-vertical diode (a) and a fully-vertical diode (b).

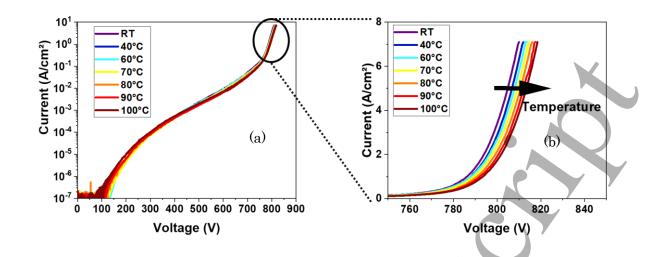

Typical reverse characteristics of the vertical GaN-on-Si p-n diodes are shown in Fig. 5. The

diodes exhibit a high blocking capability (BV) above 800 V, resulting in a high electric field

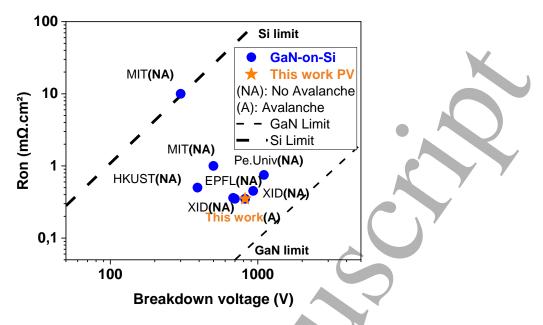

at the p-n junction of 2.3 MV/cm. This translates to an average electric field across the drift layer close to 2 MV/cm. Moreover, a uniform breakdown voltage across the sample was observed with similar values as a function of the anode sizes (up to 200 µm as diameter). Further improvement of the edge termination process should allow withstanding even higher critical field. Low leakage current density is observed to be below  $10^{-1}$  A/cm<sup>2</sup> all the way to the device breakdown. This is a strong indicator of the good material quality as well as the reduction of sidewall parasitic leakage current achieved through the optimized mesa etching step. Additionally, it provides solid evidence of low electrically active dislocations within the structure (although this has not yet been assessed). Fig. 5 shows the temperature dependence from room temperature up to 100°C of leakage current for reverse biased p-n diodes. It can be pointed out that the diode survived many voltage sweeps up to 800 V suggesting avalanche capability. This assumption is confirmed with the temperature dependence of the reverse J-V characteristics. Under high reverse bias, charge carriers flow through a specific path with high energy, enabling the accumulation of additional charge carriers. This corresponds to the so-called impact ionization, which enables for the avalanche capability<sup>29),30)</sup>. As the temperature increases, phonon scattering delay the onset of impact ionization. To achieve the same kinetic energy level at higher temperature, a higher voltage is thus required. Therefore, the increased breakdown voltage with increasing temperature is a strong indication of the avalanche capability in the devices. A clear avalanche breakdown signature is observed (Fig. 5.b), as the blocking voltage increases with temperature due to higher phonon scattering, which delays the onset of impact ionization. The demonstration of avalanche capability in 800 V-class pn diodes represents a key feature that highlights the potential vertical GaN-on-silicon heterostructures for power electronics. Fig. 6 illustrates the benchmark of R<sub>ON</sub>, sp versus BV for vertical GaN-on-Si diodes. The corresponding Baliga FOM  $(BV^2/R_{ON})$  around 2 GW/cm<sup>2</sup> is therefore favorably comparable to the state-of-the art.

Template for APEX (Mar. 2022)

Fig. 5. (a) Temperature dependence of pseudo vertical GaN-on-silicon p-n diode reverse characteristics (b) Zoom of the breakdown region

To conclude, we investigated the potential of vertical GaN-on-Si p-n diodes. With a drift thickness of 4.5  $\mu$ m, the pseudo-vertical GaN-on-Si diodes exhibited high current spreading with low on-state resistance. Furthermore, we demonstrated a high blocking voltage at 800 V with avalanche capability, resulting in a state-of-the-art BFOM of approximately 2 GW/cm<sup>2</sup>. The demonstrated avalanche breakdown capability through temperature measurements is a strong indicator of the material and processing quality. This is attributed to an optimized deep mesa etching yielding low leakage current through the sidewalls, and low electrically active dislocations. These results pave the way for medium voltage vertical GaN-on-Si based power devices. It can be pointed out that the limitations related to the pseudo-vertical architecture in terms of current crowding effect can be overcome with the use of a fully vertical structure that can be realized by means of local substrate removal <sup>5</sup>.

Fig.6. Baliga benchmark of GaN-on-Si silicon p-n diodes indicating avalanche

capability<sup>21-27)</sup>.

#### Acknowledgments

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 101007229. The JU receives support from the European Union's Horizon 2020 research & innovation programme and Germany, France, Belgium, Austria, Sweden, Spain, Italy. This work was also supported by the French RENATECH Network.

### References

1) B. J. Baliga, Semicond Sci Technol 28, 074011 (2013).

2) I. Abid, Y. Hamdaoui, J. Mehta, J. Derluyn and F. Medjdoub, Micromachines 13, 1519 (2022).

3) U. K. Mishra, P. Parikh and Y.-F. Wu proceedings of the IEEE 6, 90 (2002).

4) F. Medjdoub, M. Zegaoui, B. Grimbert, N. Rolland and P. A. Rolland, Appl. Phys. Express 4, 124101 (2011)

5) I. Abid, E. Canato, M. Meneghini, G. Meneghesso, K. Cheng and F. Medjdoub, Appl. Phys. Express 14, 036501 (2021).

Template for APEX (Mar. 2022)

- 7) Y. Zhang, A. Dadgar and T. Palacios, J. Phys. D Appl. Phys 51, 273001 (2018).

- 8) Y. Zhang, M. Sun, H. Y. Wong, Y. Lin, P. Srivastava, C. Hatem, M. Azize, D. Piedra, L.

- Yu, T. Sumitomo, N. De Almeida Braga, R. V. Mickevicius and T. Palacios, IEEE Trans Electron Devices 62, p.2155-2161 (2015).

- 9) H. Fu, K. Fu, S. Chowdhury, T. Palacios and Y. Zhao, IEEE Trans Electron Devices 68, p.3200-3211 (2021).

- 10) Z. Bian, T. Zhang, J. Zhang, S. Zhao, H. Zhou, J. Xue, X. Duan, Y. Zhang, J. Chen, K. Dang, J. Ning and Y. Hao, Appl. Phys. Express 12, 084004 (2019).

- 11) Z. Bian, J. Zhang, S. Zhao, Y. Zhang, X. Duan, J. Chen, J. Ning and Y. Hao, IEEE Electron Device Letters 41, 1476 (2020).

- 12) J. Chen, Z. Bian, Z. Liu, J. Ning, X. Duan, S. Zhao, H. Wang, Q. Tang, Y. Wu, Y. Song,J. Zhang and Y. Hao, Semicond. Sci. Technol. 34, 115019 (2019).

- 13) T. Hayashida, T. Nanjo, A. Furukawa and M. Yamamuka, Appl. Phys. Express 10, 061003 (2017)

- 14) C. Gupta, Y. Enatsu, G. Gupta, S. Keller and U. K. Mishra, Phys. Status Solidi A 213, 878–882 (2016).

- 15) G. T. Dang, A. P. Zhang, F. Ren, S. Member, X. A. Cao, S. J. Pearton, H. Cho, J. Han, J.-I. Chyi, C. Lee, C. Chuo, S. N. George Chu and R. G. Wilson, IEEE transactions on electron devices 4, 47 (2000).

- 16) Y. Hatakeyama, K. Nomoto, A. Terano, N. Kaneda, T. Tsuchiya, T. Mishima and T. Nakamura, Japanese Journal of Applied Physics 52, 028007 (2013).

- 17) O. Aktas and I. C. Kizilyalli, IEEE Electron Device Letters 36, p.890-892 (2015).

- 18) W. Liu, W. Xu, D. Zhou, F. Ren, D. Chen, P. Yu, R. Zhang, Y. Zheng and H. Lu, Phys. Status Solidi A 215, 1800069 (2018).

- 19) E. Brusaterra, E. Bahat Treidel, F. Brunner, M. Wolf, A. Thies, J. Wurfl and O. Hilt, IEEE Electron Device Letters 44, p. 388-391 (2023).

- 20) K. Nomoto, B. Song, Z. Hu, M. Zhu, M. Qi, N. Kaneda, T. Mishima, T. Nakamura, D. Jena and H. G. Xing, IEEE Electron Device Letters 37, p.161-164 (2016).

- 21) X. Zou, X. Zhang, X. Lu, C. W. Tang and K. M. Lau, in IEEE Electron Device Letters

|        | Template for APEX (Mar. 2022)                                                           |

|--------|-----------------------------------------------------------------------------------------|

| 37, p  | .636-639 (2016).                                                                        |

| 22) Y  | Z. Zhang, M. Yuan, N. Chowdhury, K. Cheng and T. Palacios, IEEE Electron Devic          |

| Lette  | rs 39, p. 715-718 (2018).                                                               |

| 23) Y  | Z Zhang, D. Piedra, M. Sun, J. Hennig, A. Dadgar, L. Yu and T. Palacios, IEEE Electro   |

| Devi   | ce Letters 38, p.248-251 (2017).                                                        |

| 24) F  | . Jia, X. Ma, L. Yang, X. Zhang, B. Hou, M. Zhang, M. Wu, X. Niu, J. Du, S. Liu an      |

| Y. Ha  | ao, IEEE Electron Device Letters 43, p.1400-1403 (2022).                                |

| 25) X  | K. Liu, M. Wang, J. Wei, C. P. Wen, B. Xie, Y. Hao, X. Yang and B. Shen, IEEE Tran      |

| Elect  | ron Devices 70, p.1636-1640 (2023).                                                     |

| 26) Y  | Z. Zhang, M. Sun, D. Piedra, M. Azize, X. Zhang, T. Fujishima and T. Palacios, IEE      |

| Elect  | ron Device Letters 35, p.618-620 (2014).                                                |

| 27) R  | . A. Khadar, C. Liu, L. Zhang, P. Xiang, K. Cheng and E. Matioli, IEEE Electron Devic   |

| Lette  | rs 39, p.401-404 (2018).                                                                |

| 28) T  | . Pu, U. Younis, H. C. Chiu, K. Xu, H. C. Kuo and X. Liu, Nanoscale Res Lett 16, 10     |

| (202)  | 1).                                                                                     |

| 29) K  | L. Fu, Z. He, C. Yang, J. Zhou, H. Fu and Y. Zhao, Appl. Phys. Lett. 121, 092103 (2022) |

| 30) H  | I. Fukushima, S. Usami, M. Ogura, Y. Ando, A. Tanaka, M. Deki, M. Kushimoto,            |

| Nitta  | , Y. Honda and H. Amano, Appl. Phys. Express 12, 26502 (2019).                          |

| Figu   | ure Captions                                                                            |

| Fig. 1 | 1. (a) Cross section of pseudo vertical GaN-on-Silicon p-n heterostructure (b)          |

| SIMS   | S analysis of a similar wafer with identical growth conditions                          |

| Fig. 2 | 2. SEM images of the sidewalls from a vertical GaN-on-Si p-n diode. The inset show      |

a FIB cross section of the beveled sidewalls

Fig. 3. (a) Forward current measurements and (b) Differential on-state resistance measurements at various temperatures.

**Fig. 4.** Distribution of the current density extracted from Silvaco TCAD in on-state conditions for a pseudo-vertical diode (a) and a fully-vertical diode (b).

**Fig. 5.** a) Temperature dependence of pseudo vertical GaN-on-silicon p-n diode reverse characteristics (b) Zoom of the breakdown region

Fig. 6. Baliga benchmark of GaN-on-Si silicon p-n diodes indicating avalanche capability.