## 455/610-GHz fT/fMAX InP DHBT technology with demonstration of a beyond-110-GHz-bandwidth large-swing PAM-4 2:1 AMUX-driver

Nil Davy, Romain Hersent, Virginie Nodjiadjim, Marina Deng, Mukherjee Chhandak, Muriel Riet, Colin Mismer, Filipe Jorge, Bertrand Ardouin,

Cristell Maneux

### ▶ To cite this version:

Nil Davy, Romain Hersent, Virginie Nodjiadjim, Marina Deng, Mukherjee Chhandak, et al.: 455/610-GHz fT/fMAX InP DHBT technology with demonstration of a beyond-110-GHz-bandwidth large-swing PAM-4 2:1 AMUX-driver. Compound Semiconductor Week (CSW), May 2023, Jeju Island (South Korea), South Korea. hal-04296467

## HAL Id: hal-04296467 https://hal.science/hal-04296467v1

Submitted on 20 Nov 2023  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# 455/610-GHz $f_T/f_{MAX}$ InP DHBT technology with demonstration of a beyond-110-GHz-bandwidth large-swing PAM-4 2:1 AMUX-driver

N. Davy<sup>1, 2</sup>, R. Hersent<sup>1</sup>, V. Nodjiadjim<sup>1</sup>, M. Deng<sup>2</sup>, C. Mukherjee<sup>2</sup>, M. Riet<sup>1</sup>, C. Mismer<sup>1</sup>, F. Jorge<sup>1</sup>, B. Ardouin<sup>1</sup>, C. Maneux<sup>2</sup>

<sup>1</sup>III-V Lab, joint lab between Nokia Bell Labs, Thales and CEA LETI, Palaiseau, France <sup>2</sup>IMS Laboratory, University of Bordeaux, CNRS UMR5218, Bordeaux INP, Talence, France nil.davy@3-5lab.fr

*Abstract*—We report on an Indium Phosphide (InP) double heterojunction bipolar transistor (DHBT) technology for integrated circuit design and fabrication. The  $0.4 \times 5 \ \mu m^2$  DHBT devices exhibit a 455-GHz  $f_T$  and a 610-GHz  $f_{MAX}$ , with a 4 V common-emitter breakdown voltage, the BV<sub>CE0</sub>, and a peak current gain  $\beta$  of 25. This enabled state-of-the-art 2:1 Analog multiplexer (AMUX)-driver results with beyond-110-GHz bandwidth and 2-Vppd PAM-4 swing at 100 GBd.

Keywords—Double heterojunction bipolar transistor; Indium Phosphide; Analog multiplexer (AMUX); large-swing linear electro-optical modulator driver; 4-level pulse amplitude modulation (PAM-4), high-speed integrated circuit (IC)

### I. INTRODUCTION

InP DHBTs have shown cut-off frequencies exceeding 1 THz with > 4 V breakdown voltages [1-2]. These devices can enhance the link capacity of high-frequency and large output-power front ends for 6G communications. However, optical communication front-end integrated circuits require several tens to thousands of transistors to be monolithically integrated, imposing very-high reproducibility and yield requirements along with the high-performance criteria. To this end, III-V Lab has developed a circuit-oriented InP-DHBT technology enabling state-of-the-art high-speed integrated circuits (IC) [3-4]. In this paper, we report on a 455-/610-GHz  $f_T/f_{MAX}$  4 V BV<sub>CE0</sub> InP-DHBT process, with up to several hundreds of DHBTs integrated per IC. Using this technology, we fabricated an AMUX-driver IC with record >2.1-THz gain-bandwidth product and 2-Vppd PAM-4 output-swing at 100 GBd.

#### II. TRANSISTOR TECHNOLOGY

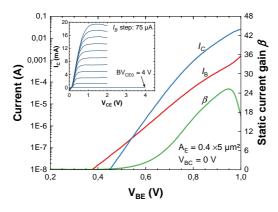

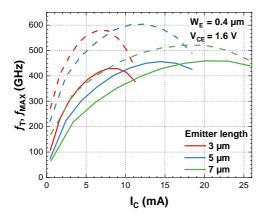

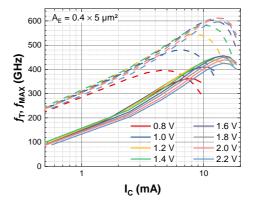

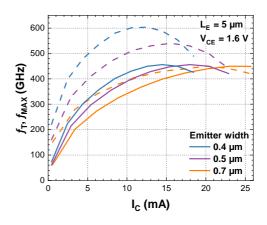

The DHBT structure is grown using solid source molecular beam epitaxy (SSMBE). The compositionally graded InGaAs base is 22-nm thick and highly C-doped (>  $8 \times 10^{19}$  cm<sup>-3</sup>). The 110-nm thick composite collector includes InGaAs spacer, a thin InGaAsP layer, a highly doped InP doping plane, and a lightly doped InP layer. Transistors, as shown in Fig. 5, are fabricated using a wet-etched self-aligned triple mesa technology [5]. Various emitter lengths (from 3 to 10 µm) and widths (from 0.4 to 0.7 µm) are available; the overall fabrication yield on the 3-inch wafer is >99%. The DC characteristics of a  $0.4 \times 5 \,\mu\text{m}^2$  DHBT are shown in Fig. 1. The peak current gain is 25, the base and collector ideality factors are  $\eta_B=1.83$  and  $\eta_C=1.12$ , respectively. This device exhibits a 4 V BV<sub>CE0</sub> at a collector current density J<sub>C</sub>=0.01 mA/µm<sup>2</sup>. Cut-off frequencies are extracted from on-wafer S-parameter measurements up to 110 GHz. Fig. 2 shows extracted  $f_T$  and  $f_{MAX}$  of a  $0.4 \times 5 \,\mu\text{m}^2$  DHBT at various V<sub>CE</sub>. The device exhibits peak  $f_T$  and  $f_{MAX}$  of 455 GHz and 610 GHz, respectively. In comparison, frequency performances of shorter devices are degraded by emitter resistance, while longer ones are affected by the base-collector capacitance, as illustrated in Fig. 3. Similarly, wider transistors feature lower performances as depicted on Fig. 4.

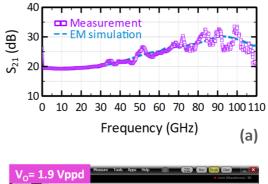

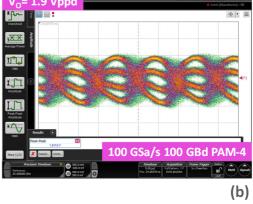

III. ULTRA-LARGE BANDWIDTH INP-DHBT ANALOG MULTIPLEXER-DRIVER INTEGRATED CIRCUIT

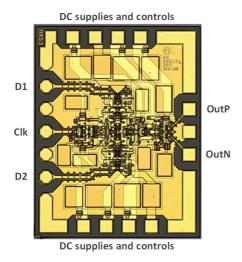

The 0.5  $\mu$ m DHBTs were leveraged for the design and fabrication of a lumped AMUX-driver IC with state-ofthe-art performances, as shown in Fig. 6. The circuit process features three Au-based metallization levels, SiN MIM capacitors and NiCr thin-film resistors. The AMUX-driver contains 76 DHBTs (5 and 7  $\mu$ m emitter lengths). The 2:1 AMUX-driver operation, electro-magnetic (EM)-simulation and design details are described in [3-4]. As depicted on Fig. 7(a) the AMUX-driver shows a record >2.1-THz gain-bandwidth product with a 19.6-dB (25.6dB differential) |S<sub>21</sub>| at 0.1-GHz and >110-GHz bandwidth. It also features ~11-dB peaking gain around 100 GHz. A good agreement between measurement and simulation is also obtained. Besides, Fig. 7(b) depicts the AMUXdriver 2-Vppd output-swing 100-GSa/s 100-GBd PAM-4 differential output eye diagram with clear eye-opening.

<u>Acknowledgement:</u> This work was supported by the European Commission through the Photonics Public Private Partnership Initiatives under Grant H2020-ICT-2019-2 (Twilight Project).

[1] A.M. Arabhavi, et al., IEEE International Electron Devices Meeting, 11.4.1–11.4.4, doi: 10.1109/IEDM19574.2021.9720644 (2021)

- [4] R. Hersent et al., IEEE Microw. and Wireless Comp. Lett., vol. 32, no. 6, pp. 752-755, doi: 10.1109/LMWC.2022.3161706 (2022)

- [5] N. Davy et al., IEEE BCICT Symposium, pp. 1-4, doi: 10.1109/BCICTS50416.2021.9682209 (2021)

<sup>[2]</sup> J. C. Rode, et al., IEEE Transactions on Electron Devices, 62, 9, 2779-2785, doi: 10.1109/TED.2015.2455231 (2015)

<sup>[3]</sup> R. Hersent et al., IEEE BCICT Symposium, pp. 1-4, doi: 10.1109/BCICTS50416.2021.9682463 (2021)

Fig. 1: Gummel plot of a  $0.4\times5~\mu m^2$  InP DHBT at  $V_{CB}=0~V$  and (inset) corresponding  $I_C\text{-}V_{CE}$  curves.

Fig. 3:  $f_T$  (solid lines) and  $f_{MAX}$  (dashed lines) as function of  $I_C$  for various emitter lengths

Fig. 5:  $0.4 \times 5 \,\mu$ m<sup>2</sup> InP DHBT microphotograph.

Fig. 2:  $\mathit{f}_{T}$  (solid lines) and  $\mathit{f}_{MAX}$  (dashed lines) as function of  $I_{C}$  for different  $V_{CE}$

Fig. 4:  $f_T$  (solid lines) and  $f_{MAX}$  (dashed lines) as function of  $I_C$  for various emitter widths at  $V_{CE}$  = 1.6 V

Fig. 6: InP-DHBT AMUX-driver die microphotograph. The chip sizes 1.2x1.5 mm<sup>2</sup>. Data/Clock input and output ports are respectively located on the west and east sides of the die. DC supplies and controls are located on the north and south sides.

Fig. 7: InP-DHBT AMUX-driver (a) measured versus simulated path-through-mode single-ended S-parameter gain,  $S_{21}$  (b) 100-GSa/s 100-GBd (200-Gb/s) PAM-4 differential output eye diagram. Horizontal and vertical scales are 5 ps/div and 600 mV/div, respectively.