# Design, Fabrication and Characterization of 10 kV 4H-SiC BJT for the Phototransistor Target

Ali Ammar, Mihai Lazar, Bertrand Vergne, Sigo Scharnholz, Luong Viêt Phung, Pierre Brosselard, D. Tournier, Camille Sonneville, Christophe Raynaud, Marcin Zielinski, et al.

### ▶ To cite this version:

Ali Ammar, Mihai Lazar, Bertrand Vergne, Sigo Scharnholz, Luong Viêt Phung, et al.. Design, Fabrication and Characterization of 10 kV 4H-SiC BJT for the Phototransistor Target. Romanian Journal of Information Science and Technology, 2023, 26 (2), pp.193-204. 10.59277/ROMJIST.2023.2.06. hal-04276812

## HAL Id: hal-04276812 https://hal.science/hal-04276812

Submitted on 9 Nov 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Design, Fabrication and Characterization of 10 kV 4H-SiC BJT for the Phototransistor Target

Ali AMMAR<sup>1</sup>, Mihai LAZAR<sup>2</sup>, Bertrand VERGNE<sup>3</sup>, Sigo SCHARNHOLZ<sup>3</sup>, Luong Viet PHUNG<sup>1</sup>, Pierre BROSSELARD<sup>1</sup>, Dominique TOURNIER<sup>1</sup>, Camille SONNEVILLE<sup>1</sup>, Christophe RAYNAUD<sup>1</sup>, Marcin ZIELINSKI<sup>4</sup>, Hervé MOREL<sup>1</sup>, Dominique PLANSON<sup>1, \*</sup>

<sup>1</sup>Univ Lyon, INSA Lyon, Université Claude Bernard Lyon 1, Ecole Centrale de Lyon, CNRS, AMPERE, 69621, Lyon, France

<sup>2</sup>Light, nanomaterials, nanotechnologies, EMR CNRS 7004, University of Technology of Troyes, 10004 Troyes, France

<sup>3</sup>ISL, French-German Research Institute of Saint Louis, 68301 Saint Louis, France

<sup>4</sup>NOVASIC, 73375 Le Bourget du Lac CEDEX, France

Email: ali.ammar@insa-lyon.fr, mihai.lazar@utt.fr, bertrand.vergne@isl.eu, sigo.scharnholz@isl.eu, luong-viet.phung@insa-lyon.fr, pierre.brosselard@insa-lyon.fr, dominique.tournier@insa-lyon.fr, camille.sonneville@insa-lyon.fr, christophe.raynaud@insa-lyon.fr, mzielinski@novasic.com, herve.morel@insa-lyon.fr, dominique.planson@insa-lyon.fr\*

\* Corresponding author

**Abstract.** For medium voltage, the SiC BJT is a convenient solution to reduce the on-losses and it could have the advantage to be optical controlled, to ease the serial connection of BJT. The design of a 10 kV, 10 A SiC BJT is described. The different fabrication steps are described. The analysis and optimization of the peripheral protection are described in detail. The fabricated wafers consist in several types of electrical BJT and diodes. Moreover some phototransistors have been fabricated. The selected solution is a combination of a JTE (Junction Termination Extension) and guard rings. The first measurement results are present. Some vacuum chamber probe level measurements have shown breakdown voltage up to 11 kV. Probe measurements of the forward characteristic have shown a good operation of the electrical BJT, with a current gain up to 20. Some dies have been packaged to achieve high-current measurement. The on-state characterizations show on current up to 15 A with a current gain that reach 15. First optical control tests have shown encouraging results.

**Keywords:** bipolar junction transistor; high-voltage power semiconductor device; peripheral protection; power electronics; silicon carbide.

#### 1. Introduction

Ecological transition [1] is a public policy applied explicitly or implicitly in most of the world countries. It implies the sustainable development and the target to reduce the greenhouse emissions with a clear target to increase electrification to reach such an objective. Silicon Carbide (SiC) is one of the new semiconductor materials that benefits of such a target for instance for the electric vehicle technologies. In 2022, the SiC power semiconductor market reaches USD 1 billion and is supposed to attain USD 15 billion by 2032 [2]. However, the availability of such

new power semiconductor devices with very good properties, enable to develop numerous other studies for new applications of such devices. For instance, one can already considered photovoltaic (PV) inverters, electric traction as railway applications and even other stationary applications (wind power, data centers, industry...) [3].

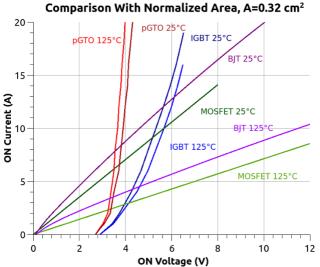

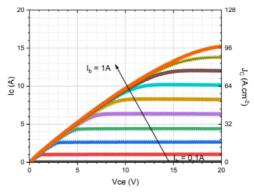

**Fig. 1.** I–V curve comparison of 15 kV SiC P-GTO, IGBT, and MOSFET at 25 °C and 125 °C [3] and our fabricated device 10 kV BJT (for  $I_B=1$  A).

In comparison to Si-based component, for the same level of conduction losses, SiC power components, enables a clear reduction of the switching losses [4]. That enables a possible reduction of total losses or for embedded applications a clear reduction of the size and mass of the converters.

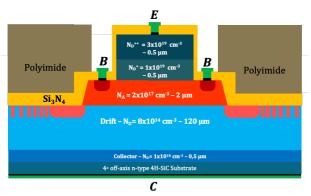

**Fig. 2**. Schematic cross-sectional view of 4H-SiC NPN BJT, with detailed epitaxial layers (thickness and doping level).

Concerning high-voltage devices, bipolar devices such as thyristors, GTOs, BJTs and IGBTs potentially enable a reduced drop voltage with respect to unipolar devices as shown in the cross-sectional view of the Bipolar Junction Transistor in Fig. 2 [4].

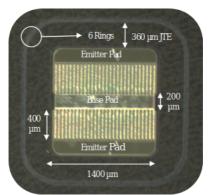

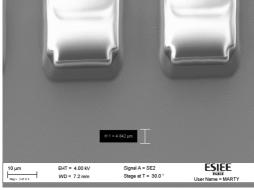

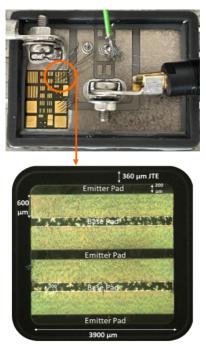

Fig. 3. Top microscopic view of 0.053 cm<sup>2</sup> fabricated BJT device with 2 emitter pads

The blocking voltage could be very high as 27 kV for a SiC IGBT [5] but the cost of fabrication of such a device is too high for commercialization. However, power SiC modules 3.3 kV, 750 A are available [6] with the target of railway applications [7].

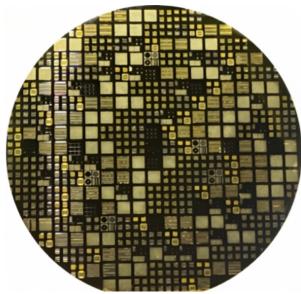

Fig. 4. Picture of the top view of a fabricated wafer.

Another advantage of bipolar power devices is the capability to be optically driven [8] which could simplify the serial association for high-voltage applications. This was the main motivation for the project that supports this paper.

High-voltage bipolar devices such as BJTs based on 4H-SiC are considered very attractive candidates for high-voltage applications. In particular, when compared to silicon thanks to a high breakdown electric field resulting in decreasing the on-resistance and probably avoiding a second breakdown avalanche effect [9]. In addition, a high saturation velocity and reduced device areas enable fast switching and its wide-band gap that allows it to operate over high temperatures [10].

Finally, a good thermal conductivity gives it the ability to easily transfer the heat generated by Joule's effect to a heat sink [11]. The recent literature reported high voltage 4H-SiC BJTs include a 10 kV open-base breakdown voltage (BV<sub>CEO</sub>) and a specific on-resistance of 130 mΩ.cm<sup>2</sup> at (RT) with a 120 µm drift layer doped to  $6 \times 10^{14}$  cm<sup>-3</sup> [12]. A 15 kV (BV<sub>CEO</sub>) at a leakage current of 0.1 mA/cm<sup>2</sup> with 125 µm drift layer doped to  $1.1 \times 10^{14}$  cm<sup>-3</sup> [13]. And a 9.2 kV (BV<sub>CEO</sub>) with a 50 µm, a  $7 \times 10^{14}$  cm<sup>-3</sup> doped drift layer and R<sub>SP\_ON</sub> = 78 mΩ.cm<sup>2</sup> [14].

For high-voltage applications, it is mandatory to implant a highly sophisticated base-drift junction termination extension (JTE), which serves in minimizing the electric field plate crowd generated at the MESA edge of the power device. Several approaches were applied to optimize the extension performance such that applying variations over the length and etching depth of the JTE [13], or by implanting different doses over the total length of the JTE [15], and by the addition of extra implanted rings [16]. In this paper a more than 10 kV NPN BJT based on 4H-SiC is reported when the theoretical value determined by its drift layer thickness and doping concentration is almost 13 kV.

Both the device design using TCAD (Sentaurus Synopsys) [20] for the peripheral protection and fabrication process are more detailed in Section 2. The electrical characterization of the fabricated device is shown in Section 3. The extended current capability is evidenced.

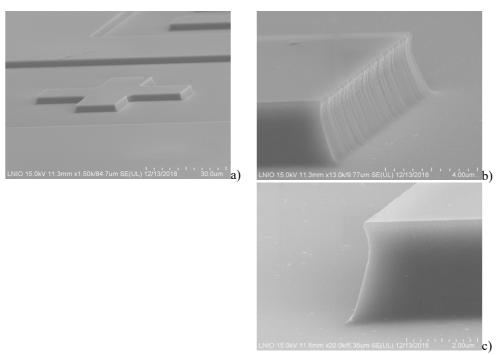

Fig. 5. Test motif for etching(a), quasi-vertical trenches (b), corner trench (c).

#### 2. Device Design and Fabrication

Fig. 2 represents a typical cross-sectional view of our fabricated BJT with five epitaxial layers grown on a ~300 µm 4° off-axis 4H-SiC substrate. Fig. 3 shows a top view of a fabricated BJT device with 2 emitter pads and Fig. 4 an image of 100 mm processed 4H-SiC wafer. To avoid equipotential line tightening and high electric field peaks in this area under reverse bias at highvoltage, rounded corners with radius of 120 µm and 250 µm have been chosen at the periphery.

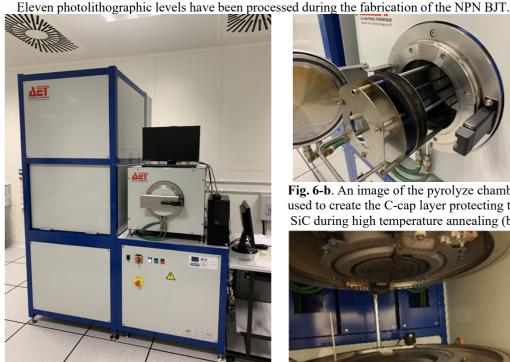

Fig. 6-a. AET furnace, utilized to activate the Al p-type doping created by ion implantation in the base and periphery (a).

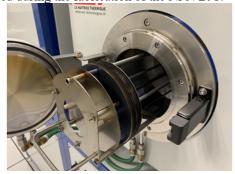

Fig. 6-b. An image of the pyrolyze chamber used to create the C-cap layer protecting the SiC during high temperature annealing (b).

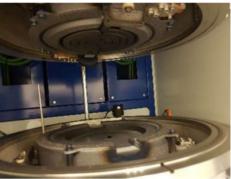

Fig. 6-c. The RTP chamber with double graphite resistors utilized to perform the doping activation annealing at 1700°C (c).

The first two levels concern a 1.2 µm and respectively 2.2 µm deep plasma etching of the 0.5  $\mu$ m n-type emitter doped to 10<sup>19</sup> cm<sup>-3</sup> meeting another 0.5  $\mu$ m emitter highly doped to 3×10<sup>19</sup> cm<sup>-3</sup> 3 and a 2 µm p-type base doped to in SF<sub>6</sub> chemistry with an ICP/RIE (Inductively Coupled Plasma Reactive Ion Etching) Plassys MU400 reactor.

The process has been optimized with high ICP density plasma (1000 W) and high RIE bias (~350 V) to obtain quasi-vertical trenches (Fig. 5(a) and Fig. 5 (b) with rounded sides walls at the bottom part, to avoid trenching phenomenon [16], as shown in Fig. 5 (c).

To avoid equipotential line tightening and high electric field peaks in this area, under reverse bias at high-voltage, the round angle of the peripheral has been select among two different values: 120 µm and 250 µm (Fig. 12).

After plasma etching two doping steps with Al ion implantation steps have been performed, in the p-type base to ensure a low resistive ohmic contact and to implant the peripheral protection. To avoid SiC amorphization the high-doped base wells have been implanted at 300°C.

Fig. 7. An image during the technological process with the BJT defined fingers.

To activate dopants, post-implantation annealing has been performed with a 1700°C/30 min plateau in an AET 6" RTP furnace with graphite resistors, specially designed for this process (Fig. 6 (a), (Fig. 6 (b) and (Fig. 6 (c)). Previously the samples have been encapsulated on both sides with a C-cap obtained by pyrolyzing AZ photoresist. The C-cap has been after being removed by O<sub>2</sub> plasma. The lowly n-doped drift layer has a thickness of 120  $\mu$ m and a doping concentration 8×10<sup>14</sup> cm<sup>-3</sup>.

Fig. 8. TCAD simulation of the variation of Blocking Voltage (kV) as a function of JTE implanted Dose and JTE Length

The next technological steps concerned the materialization with ohmic contacts formed on the high p-doped and n-doped (on both sides) layers. For the n-type emitter and collector, sputtered Ni layers were patterned, and RTA annealed at 900°C, and an alloy of Ni/Ti/Al 800°C RTA annealed [17] for the p-type base contacts.

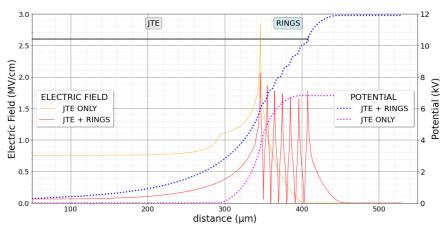

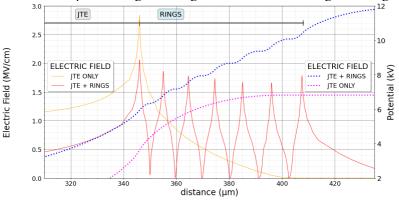

**Fig. 9.** Electric field and potential distribution over the horizontal axis through the peripheral protection as shown in Fig. 14.

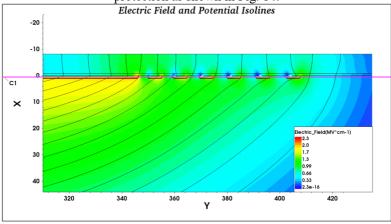

Fig. 10. TCAD simulated Electric Field and Isopotential Lines (600V steps) around the 6 rings for JTE+RING optimal design and magenta cross section for Fig. 9 and Fig. 11.

**Fig. 11.** Electric field and potential distribution over the horizontal axis cross section showing the uniform potential smoothing and optimal termination (Electric Field: red, Potential: blue) design and benefits against JTE only (Electric Field: orange, Potential: magenta).

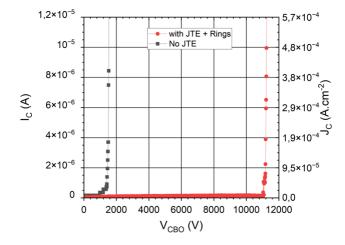

**Fig. 12.** Reverse IV characteristics recording an open emitter blocking voltage of 11 kV at room temperature w and w/o JTE. The recorded results belong to the device shown in Fig. 14.

Before the metallization steps SiC wafers have been thermally oxidized with a combined wet/dry process and the different metallic layers were isolated with LPCVD and PECVD  $Si_3N_4$  layers locally opened by  $SF_6$  plasma RIE. At the end, a last passivation layer has been patterned on the surface with a thick polyimide of 12  $\mu$ m.

Fig. 13. Forward I-V characteristics of the fabricated BJT with an active area of 2.06 mm<sup>2</sup> measured on a probe station.

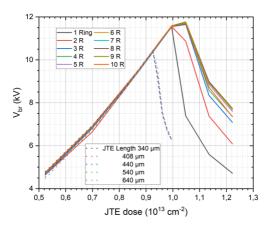

The peripheral protection is made of a 360  $\mu$ m long JTE (Junction Termination Extension), done by Al implantation with an optimum dose of  $1.1 \times 10^{13}$  cm<sup>-2</sup> determined by TCAD simulations [19] (Fig. 8). Lengthier JTE won't provide any benefits. The peripheral protection is then completed by a set of several rings, each 5  $\mu$ m long, with a 4  $\mu$ m spacing between the JTE and the first ring. After that, a space increase of 0.5  $\mu$ m is given between each ring, each time a ring is added (i.e. the space between 1<sup>st</sup> and 2<sup>nd</sup> ring is 4.5  $\mu$ m, between 2<sup>nd</sup> and 3<sup>rd</sup> is 5  $\mu$ m). The TCAD simulations show that the addition of one supplementary ring will push further the maximum expected breakdown voltage while shifting the optimum dose to higher values. Therefore, by keeping the JTE dose at  $1.1 \times 10^{13}$  cm<sup>-2</sup>, the breakdown voltage is becoming less sensitive to process variation as it will less likely be located on the right-hand side of the sharply decreasing curve.

Fig. 9 and Fig. 10 shows the simulated electric field profile of the fabricated device whose the ring number is set at 6. This value was chosen as the gain in holding voltage capability becomes less pronounced for higher ring numbers. The peripheral protection design and parameters such as JTE length, ring number, and implanted dose were extracted from [18] upon a study done on a simulation model using TCAD from Synopsys Sentaurus [20] by performing various breakdown simulations to detect optimum technological parameters. The electric field distribution shown in (Fig. 11) shows the impact of having such an optimized system to ensure a smooth flow of the high electric field that accumulates at the junction termination, increasing by this phenomenon the blocking voltage.

#### 3. Results

Electrical characterizations were performed on the fabricated devices. Reverse IV characteristics as shown in Fig. 12 were performed using a high vacuum probe station at ISL [21]. A high-blocking voltage of 11 kV with a leakage current density of 0.1 mA/cm<sup>2</sup> was recorded, validating our model and simulation results.

**Fig. 14.** Top: picture of a package with several dies to achieve high-current measurements. Bottom: picture of the bounded BJT die.

The efficiency of our peripheral protection can be clearly visualized when comparing both graphs in Fig. 9 and Fig. 11 the distribution of the electric field all over the device due to the junction termination extension (red curve in Fig. 9) when compared to the electric field in the absence of a rings (orange curve) lead to a great increase in blocking the voltage from 7 kV without rings to 11.8 kV with a well-parameterized JTE + RINGS. Fig. 10 shows a uniform potential distribution in both SiC material and passivation layers on top of the semiconductor. The TCAD simulations results have been confirmed with breakdown voltage measurements. The blocking voltage increases from 1.3 kV when the JTE is absent (Fig. 12) to 11 kV with a well-parameterized structure.

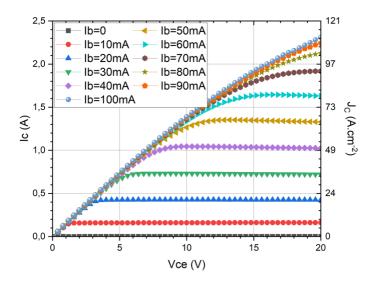

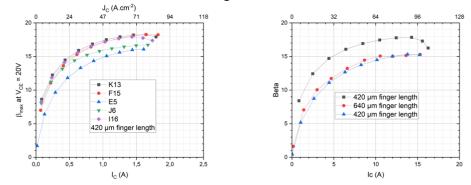

Fig. 13 shows forward common-emitter current-voltage I-V characteristics at room temperature, of the fabricated BJT (Fig. 14) with an active area of 2.06 mm<sup>2</sup> and an emitter finger width of 25  $\mu$ m long. The maximum current gain achieved is  $\beta = 27$  at a base current I<sub>B</sub> = 70 mA and V<sub>CE</sub> = 20 V for a collector current of I<sub>C</sub> = 1.9A (Hexagonal Symbol), corresponding to a current density of 92 A/cm<sup>2</sup>.

To achieve high current measurements, some dies were packaged as shown in (Fig. 14. This new packaging has been improved since our previous paper on this topic [19] presented in CAS conference. If the current gain is a little reduced with respect to probe measurements shown in Fig. 16, the current gain reduction from 20 to 15 seems due to the change of emitter fingers, as shown just below.

Fig. 15. On-state characteristic of the 5 mm  $\times$  5 mm electrical BJT shown in Fig. 12. The current gain reach 15.

Fig. 16. Analysis of the current gain for various finger length of large electrical BJTs (5 mm × 5 mm) (a), analysis of the current gain for various small electrical BJT designs (1.4 mm × 1.4 mm) (b).

#### 4. Conclusion

In this article, a more than 10 kV class BJT based on 4H-SiC is reported with an optimized junction termination extension and an isolation ring system. The fabricated device attained 11 kV as open base breakdown voltage, which corresponds to almost 90% of its theoretical value, at a leakage current of 10  $\mu$ A. The raw dies also show at room temperature a maximum current gain  $\beta = 27$  at a base current of 70 mA, current density of 92 A/cm<sup>2</sup> and a total collector current of 1.9 A. The packaged dies show higher current level 15 A with a little reduce current gain, about 15. A second lot of fabrication is under progress and a higher number of dies with a breakdown voltage greater than 10 kV is expected. Hard switching measurements are also planned up to 7 kV applied voltage and 20 A switched current. The next target will be to characterize optical controlled BJTs, which have been designed in the same project.

Acknowledgement. This study was supported by a grant overseen by the French National Research Agency (ANR), the project HV-PhotoSwitch, ANR-18-CE05-0020-01. The technological fabrication was carried out within the ESIEE (www.esiee.fr/en/about-esiee/cleanrooms) and Nanomat platforms (www.nanomat.eu).

#### References

- F. ROTONDO, P. PERCHINUNNO, S. L'ABBATE and L. MONGELLI, Ecological transition and sustainable development: integrated statistical indicators to support public policies, Scientific Reports 12(18513), 2022.

- [2] Global Market Insights, GaN & SiC Power Semiconductor Market, Oct 2022, Accessed: Mar. 23, 2023.

[Online]. Available: <u>https://www.gminsights.com/industry-analysis</u>.

- [3] X. SHE, A. Q. HUANG, O. LUCIA and B. OZPINECI, *Review of silicon carbide power devices and their applications*, IEEE Transactions on Industrial Electronics **64**(10), pp. 8193-8205, 2017.

- [4] S. TIWARI, O.-M. MIDTGÅRD and T. M. UNDELAND, SiC MOSFETs for future motor drive applications, Proceedings of the 18<sup>th</sup> European Conference on Power Electronics and Applications, Karlsruhe, Germany, pp 1-10, 2016.

- [5] E. VAN BRUNT, L. CHENG, M. O'LOUGHLIN, J. RICHMOND, V. PALA, J. PALMOUR, C. TIPTON AND C. SCOZZIE, 27 kV, 20 A 4H-SiC n-IGBTs, Materials Science Forum 821-823, pp. 847-850, 2015.

- [6] N. SOLTAU, E. WIESNER, K. ATORI and H. UEMURA, 3.3 kV full SiC MOSFETs-towards highperformance traction inverters, Bodo's Power Systems 1, pp. 22-24, 2018.

- [7] K. SATO, H. KATO, T. FUKUSHIMA. Development of SiC applied traction system for nextgeneration Shinkansen high-speed trains, IEEJ Journal of Industry Applications 9(4), pp. 453-459, 2020.

- [8] S.B. HOU, P.E. HELLSTRÖM, C.-M. ZETTERLING and M. ÖSTLING, High temperature high current gain IC compatible 4H-SiC phototransistor, Materials Science Forum 963, pp. 832-836, 2019.

- [9] J.A. COOPER and A. AGARWAL, SiC power-switching devices-the second electronics revolution?, Proceedings of the IEEE, 90(6), pp. 956-968, 2002.

- [10] M.-L. LOCATELLI and S. GAMAL, Silicon carbide against silicon: a comparison in terms of physical properties, technology and electrical performance of power devices, Journal de Physique III, 3(6), pp. 1101-1110, 1993.

- [11] S. KRISHNASWAMI, A. AGARWAL, SEI-HYUNG RYU, C. CAPELL, J. RICHMOND, J. PALMOUR, S. BALACHANDRAN, T.P. CHOW, S. BAYNE, B. GEIL, K. JONES and C. SCOZZIE, 1000-V, 30-A 4H-SiC BJTs with high current gain, IEEE Electron Device Lett., 26(3), pp. 175–177, 2005.

- [12]Q. ZHANG, R. CALLANAN, A. AGARWAL, A. BURK, M. O'LOUGHLIN, J. PALMOUR and C. SCOZZIE, 10 kV, 10 A bipolar junction transistors and darlington transistors on 4H-SiC, Materials Science Forum, 645–648, pp. 1025–1028, 2010.

- [13]A. SALEMI, H. ELAHIPANAH, K. JACOBS, C. M. ZETTERLING and M. ÖSTLING, 15 kV-Class Implantation-Free 4H-SiC BJTs with Record High Current Gain, IEEE Electron Device Lett., 39(1), pp. 63–66, 2018.

- [14]E. G. TURITSYNA and S. WEBB, Simple design of FBG-based VSB filters for ultra-dense WDM transmission, Electron. Lett., 41(2), pp. 40–41, 2005.

- [15]A. SALEMI, H. ELAHIPANAH, G. MALM, C. M. ZETTERLING and M. OSTLING, Area- and efficiency-optimized junction termination for a 5.6 kV SiC BJT process with low ON-resistance, Proceedings of the 27<sup>th</sup> International Symposium on Power Semiconductor Devices & ICs, Hong-Kong, China, pp. 249–252, 2015.

- [16] D.M. NGUYEN, R. HUANG, L.V. PHUNG, D. PLANSON, M. BERTHOU, P. GODIGNON, B. VERGNE and P. BROSSELARD, *Edge termination design improvements for 10 kV 4H-SiC bipolar*

diodes, Materials Science Forum, 740-742, pp. 609-612, 2013.

- [17]F. LAARIEDH, M. LAZAR, P. CREMILLIEU, J. PENUELAS, J. L. LECLERCQ and D. PLANSON, The role of nickel and titanium in the formation of ohmic contacts on p-type 4H-SiC, Semicond. Sci. Technol., 28(4), 2013.

- [18]A. AMMAR, L.V. PHUNG, D. PLANSON, H. MOREL and C. SONNEVILLE, Design and Methodology of Silicon Carbide High Voltage Termination Extension for Small Area BJTs, Materials Science Forum, 1062, pp. 613–618, 2022.

- [19]A. AMMAR, M. LAZAR, B. VERGNE, S. SCHARNHOLZ, L.V. PHUNG, C. SONNEVILLE, C. RAYNAUD, H. MOREL, D. PLANSON and M. ZIELINSKI, *Optimized Junction Termination Extension and Ring System for 11 kV 4H-SiC BJT*, Proceedings of the 45<sup>th</sup> International Semiconductor Conference (CAS), Poiana Brasov, Romania, pp. 191-194, 2022.

- [20]Sentaurus TCAD Simulation Tool by Synopsys Inc. Version U 2022.12-SP1.

- [21]B. VERGNE, S. SCHARNHOLZ, D. PLANSON, D. TOURNIER and P. BROSSELARD, Precise Automated Semiconductor Characterization Under Ambient Control for testing wide bang gap semiconductors, Proceedings of the 19<sup>th</sup> International Symposium on High Voltage Engineering, Pilsen, Czech Republic, pp. 23–28, 2015.