## 3D Logic circuit design oriented electrothermal modeling of vertical junctionless nanowire FETs

Sara Mannaa, Arnaud Poittevin, Cédric Marchand, Damien Deleruyelle, Bastien Deveautour, Alberto Bosio, Ian O'connor, Chhandak Mukherjee, Yifan Wang, Houssem Rezgui, et al.

### ▶ To cite this version:

Sara Mannaa, Arnaud Poittevin, Cédric Marchand, Damien Deleruyelle, Bastien Deveautour, et al.. 3D Logic circuit design oriented electrothermal modeling of vertical junctionless nanowire FETs. IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, 2023, 9 (2), pp.116 - 123. 10.1109/JXCDC.2023.3309502 . hal-04230911

## HAL Id: hal-04230911 https://hal.science/hal-04230911

Submitted on 6 Oct 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# 3D Logic circuit design oriented electrothermal modeling of vertical junctionless nanowire FETs

Sara Mannaa, Arnaud Poittevin, Cédric Marchand, Damien Deleruyelle, Bastien Deveautour, Alberto Bosio, Ian O'Connor Univ. Lyon, ECL, INSA Lyon, CNRS, UCBL, CPE Lyon INL, UMR CNRS 5270 Ecully, France {firstname.lastname}@ec-lyon.fr, bastien.deveautour@cpe.fr, damien.deleruyelle@insa-lyon.fr

Chhandak Mukherjee, Yifan Wang, Houssem Rezgui, Marina Deng, Cristell Maneux University of Bordeaux, Bordeaux INP IMS Laboratory, UMR CNRS 5218 Talence, France {firstname.lastname}@u-bordeaux.fr Jonas Müller, Sylvain Pelloquin, Konstantinos Moustakas, Guilhem Larrieu LAAS CNRS, UPR 8001, CNRS, Université of Toulouse, France {firstname.lastname}@laas.fr

*Abstract*— This work presents new insights into 3D logic circuit design with vertical junctionless nanowire FETs (VNWFET) accounting for underlying electrothermal phenomena. Aided by the understanding of the nanoscale heattransport in VNWFETs through multiphysics simulations, the SPICE-compatible compact model captures temperature and trapping effects principally through a shift of the device threshold voltage. Circuit level simulations indicate a strong impact of temperature variation on functionality and figures of merits such as energy-delay products. Subsequent guidelines for design considerations are discussed that are intended to provide feedback for technology improvements.

## Keywords—3D electronics, vertical nanowire transistor, compact model, logic circuit design, electrothermal modeling

#### I. INTRODUCTION

In the era of emerging computing paradigms and artificial neural networks, hardware and functionality requirements are in the surge. With the deployment of large numbers of sensors and smart devices to form the edge of the Internet of Things to the scale of 50 billion and rising, data is now being generated at the edge rather than in the large-scale data centers that form the cloud. Current estimates put the ratio of data generation at the edge at over 40x that of global data center traffic, today around some 20ZB. The pure cloud computing model cannot handle this massively distributed, YB-scale quantity of data - the network infrastructure resources simply do not have the capacity to move the data from the edge to the cloud, the data is vulnerable to attacks and the transmission delay is prohibitively high. In advanced applications where delay requirements are particularly stringent (e.g. 1 ms in cooperative autonomous driving), the cloud computing model cannot consistently meet the deadlines.

The limits of the cloud computing model have given rise to the emergence of edge computing, where computing tasks are performed as close as possible to data sources to meet the low power and latency criteria [1]. However, resources are constrained at the edge, in terms of available computational power, memory capacity and most importantly energy. Hardware is critical at this level and there is a clear need to explore the suitability of breakthrough emerging technologies to meet the energy-efficiency, performance and compactness requirements of edge computing hardware as alternatives to traditional von Neumann machines. IRDS identifies Gate-All-Around (GAA) nanowire field effect transistors (NWFETs) as a future mainstream solution [1], both in lateral and vertical configurations – however, the challenge is to extrapolate analyses beyond the device level to quantify relevant performance metrics [2-3].

In particular, junctionless Vertical NWFETs (VNWFET), capable of addressing existing process challenges such as downscaling, short-channel effects, compactness and electrostatic control, are difficult to meaningfully compare to existing mainstream technologies due to the additional vertical dimension and opportunities for innovative 3D logic design [4]. A critical specific issue in this evaluation lies in the correct evaluation of the electrothermal behavior of the device [5]. Indeed, the electrical performances of aggressively scaled transistors are strongly impacted by selfheating, ultrafast thermal transport and thermal conductivity degradation, all of which link to electron-phonon coupling which is not well understood at the nanoscale. The integration of this technology in the mainstream design flow is thus not straightforward and requires design technology cooptimization (DTCO) at an early stage [6-7]. This paper is an important step to achieve this goal.

In this paper, we propose a compact model to enable multiphysics evaluation of intrinsic transistors, considering electro-thermal and trapping effects investigated through multiphysics simulations based on non-Fourier heat-flow [8]. From the theoretical understanding of these effects in junctionless devices, the proposed compact model [9] captures temperature-induced increase in drain current through temperature dependence of model parameters including threshold voltage, drain/source Schottky barrier height and series access resistances. The proposed model also incorporates two additional sub-circuits for dynamic selfheating and trapping phenomena for evaluation of these effects at circuit level. We then project device performance to circuit level by using this compact model to characterize four basic 3D logic cells (INV, NAND, NOR and XOR) based on vertical nanowire transistors in terms of delay and energy consumption, thus proving that this emerging technology can be used as the basic building block for logic gates.

The paper is organized as follows: section II first describes the physical basis and implementation of the compact model (based on experimental measurements of the devices under test). Section III subsequently describes the logic cells and our characterization methodology in terms of delay and energy consumption, and with varying temperature. Section IV discusses results and perspectives, and summarizes possible future work.

#### II. TRANSISTOR: COMPACT AND NUMERICAL MODELING

#### A. Multiphysics modeling of intrinsic transistors

To accurately capture the underlying physics of junctionless FETs, the compact model presented in this work has been specifically developed based on the understanding of carrier transport studied using numerical multiphysics and TCAD simulations. Junctionless FETs offer a much and simpler fabrication process in comparison with classical MOSFETs [10], making them compatible for pursuing scaling beyond the sub 20-nm nodes. Most importantly, along with the absence of metallurgical junctions in these devices, they are heavily doped and the nanowire diameters are tailored to be quite thin in order to maintain gate electrostatic control over the channel. In order to ensure design compatibility between the junctionless VNWFET technology [10] and associated circuit simulations, the transistor compact model developed based on charge transport in gate-all-around junctionless transistors [9] is used first to calibrate the model parameters against experimental data of a wide range of transistor geometries (22 and 34 nm NW diameter with 16 to 81 nanowires in parallel) at room temperature.

Key physical parameters include doping, gate work function, mobility, drain/source Schottky barrier and threshold voltage. Once a good accordance between the model and the data is obtained, the compact model is then modified to take into account electrothermal and trapping effects, two critical issues in nano-scale junctionless transistors that can potentially impact dynamic circuit performance. To do so, we leveraged on-wafer DC measurements over a wide temperature range (15-100 °C) and pulsed-conditions with varying pulse widths (1 µs - 10 ms) to dissociate temperature and trap-induced effects. From the experimental observations, it could be understood that increasing the temperature leads to a monotonically increasing drain current conforming to prior observations in junctionless transistors [11]. This is explained by the strong temperature dependence of the threshold voltage in junctionless devices that leads to an increase in drain current along with a degradation of the on-off current ratio. This effect is further pronounced by the weak temperature dependence of the mobility due to competing lattice and impurity scattering mechanisms [11]. From the pulsed I-V measurements, it could similarly be observed that the drain current showed a continuous increase with increasing gate pulse-width, allowing for an increasing number of traps to activate while the device temperature increases simultaneously. For very large pulses, the transistor current saturated to the measured DC current. This phenomenon can also be considered to impact the threshold voltage as confirmed by the  $V_{TH}$ -shift with pulse width. This further affirmed that the threshold voltage in junctionless transistors is an important parameter to model both electrothermal and trapping effects. In the following sections, in-depth physical understanding of these effects, obtained through multiphysics simulations and compact modeling, are presented.

#### 1) Electro-thermal and Trapping effects

Thermal management is one of the most challenging design criteria in nanoscale transistors owing to a lack of understanding of the heat conduction governed by phonon transport in sub-10 nm devices that include (1) ballistic, (2) boundary scattering and (3) confinement regimes [12]. Junctionless transistors are fabricated with a very thin channel along with a chosen gate work-function to ensure that the transistors switch to off state at zero gate bias, switching to full depletion mode. In addition, the nanowires are required to be strongly doped to ensure a higher drive current in order to compensate for the Schottky barriers at the source and drain sides. Phonons can be considered as a quasiparticle originating due to lattice vibration and can be confined in the Si/SiO<sub>2</sub> interface similar to trapping, leading to a reduction of the thermal conductivity. In addition, due to electron-phonon coupling and phonon confinement, carriers (electron or hole) can also be trapped in the lattice distortion leading to the wellknown self-trapped electron phenomena [13]. Moreover, in the nanoscale regime, explaining ultrafast heat flow using the classical hydrodynamic formalism based on Fourier's law no longer remains valid. The Guyer and Krumhansl equation (GKE) has recently been demonstrated to capture nondiffusive heat transport in the nanoscale regime beyond classical Fourier's law, offering understanding of non-local thermal effects [14].

To understand the electron-phonon coupling behind the electrothermal behavior and trapping effects for nonequilibrium states in both steady and transient conditions in junctionless transistors, we leveraged finite element method (FEM) based COMSOL multiphysics simulations [15] based on the GKE formulation by solving the non-Fourier heat equation coupled with the drift-diffusion model and interface trapping effects. The material parameters are included in the simulator physics library whereas the operating conditions and device geometries are defined according to our experimental setups. The governing equation of the GKE for non-Fourier heat dissipation is written as [16],

$$q_x(r) = -\kappa \frac{dT}{dx} + l^2 \frac{d^2 q_x(r)}{dr^2} + l^2 \frac{1}{r} \frac{dq_x(r)}{dr}$$

(1)

where *q* is the heat flux,  $\tau_R$  is the phonon relaxation time,  $\kappa$  is the thermal conductivity,  $\ell$  is the phonon MFP, *c* is the heat capacity, *T* is the temperature. To consider the electrothermal effect we use the energy-conservation equation:

$$c\frac{dT}{dt} + \nabla . q_x(r) = P$$

(2)

where *P* is the dissipated power defined as  $P = V_{DS} I_D$ .

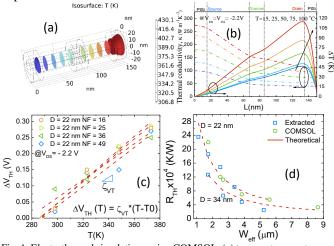

The multiphysics simulations reveal that the temperature distribution inside the nanowire exhibits a steady increase of internal device temperature along the channel (Fig. 1(a)), reaching the peak near the drain (Fig. 1(b)), implying thermal confinement and self-heating at elevated temperatures and bias conditions. This is reflected by an equivalent degradation in thermal conductivity within the channel (Fig. 1(b)). As highlighted in the previous section, the temperature variation induces a linear threshold voltage shift which can be extracted from experimental results (Fig. 1(c)). In addition, the thermal resistances ( $R_{TH}$ ) of the VNWFETs have been extracted from both measurements and Multiphysics simulations [17] which exhibit an inverse geometry–dependence (Fig. 1(d)).

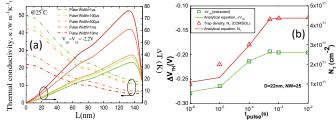

Similarly, under pulse conditions, we studied the thermal conductivity and temperature rise using COMSOL for various pulse widths that also indicated an increase of the device temperature (along with an equivalent reduction of thermal conductivity) due to phonon accumulation near the drain region at high bias conditions and larger pulse widths (Fig. 2(a)). The numerical model was then used to extract the

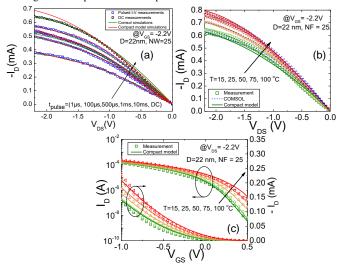

trap densities (Fig. 2(b)) that were compared with the V<sub>TH</sub> variation for different pulse widths, which revealed a clear trend in both cases: the V<sub>TH</sub> drift observed from the measurements could be described by a similar relation that also governs trap density,  $N_T = N_{SS}(1 - \exp(-t_{pulse}/\tau))$ . This led us to define the following physical relation for trapinduced V<sub>TH</sub>-shift in our model:  $\Delta V_{TH} = \alpha q N_T / C_{ox}$ , where  $\alpha$  is a constant, q is the electronic charge and C<sub>OX</sub> is the gate oxide capacitance. Figs. 3(a) and (b) show the multiphysics simulation results depicting good agreement with experimental I-V characteristics.

Fig. 1: Electrothermal simulations using COMSOL: (a) temperature contours along the nanowire, (b) Temperature and thermal conductivity at different measurement temperatures; Extracted (c) temperature dependence of the threshold voltage, (d) thermal resistance of the VNWFETs.

Fig. 2: Electrothermal simulations using COMSOL: (a) temperature and thermal conductivity distribution inside the nanowire obtained at room temperature under different pulse conditions along the nanowire, (b) Extracted threshold voltage (measurement) and trap density (COMSOL) showing similar dependence on the pulse width.

Fig. 3: Evolution of drain current with (a) different pulse widths and (b), (c) measurement temperatures comparing experimental results, multiphysics and compact model simulations for a p-VNWFET with 25 parallel nanowires of 22 nm diameter.

#### 2) Compact model implementation

Following the multiphysics simulations, it could be confirmed that in the junctionless nanowires, thermal conductivity reduces significantly with temperature, thus creating temperature hot-spots and leading to possible device Moreover, the trap self-heating. density evolves exponentially with applied gate pulse width saturating to the DC value where internal device temperature rises significantly coupled with the presence of traps. To translate these effects for compact modeling, we modify the expression of the threshold voltage to capture the effect of internal device temperature increase and trap density fluctuation. To do so, we leverage the equation  $\Delta V_{TH} =$  $\Delta V_{TH}(T) + \Delta V_{TH}(N_T)$ , where the first term captures a linear temperature dependence through a temperature coefficient whereas the second term incorporates a trap density-like dynamic exponential formulation activated through a FLAG parameter, with both parameters extracted from experimental results. In addition, an equivalent electrical subcircuit consisting of the thermal resistance and capacitance (extracted from low-frequency S-parameter measurements) has also been added to the compact model formulation in order to capture the dynamic variation of internal device temperature due to self-heating which can also be activated through a FLAG parameter. Lastly, temperature coefficients of additional model parameters such as the Schottky barrier height. series access resistances, intrinsic carrier concentration and drain induced barrier lowering are also implemented in the model equations. Compact model simulation results are validated against experimental data for both pulsed (Fig. 3(a)) and temperature (Figs. 3(b) and (c)) measurements.

## B. Enhanced devices through the integration of materials or architectures

While junctionless VNWFETs already bring significant benefits to transistor performance, additional features can be naturally achieved. This subsection covers emerging characteristics of such functional enhancements from a prospective viewpoint.

#### 1) Ferro gate

Adding ferroelectric material to the VNWFET gate stack [18] enables non-volatile logic as well as non-volatile reconfigurability. For example, a non-volatile full adder [19] is able to store one of the summands in a non-volatile manner, which is of particular interest in multiplication operations used in digital filters or convolutional neural networks, and where one summand varies constantly (data), while the other one varies rarely (coefficients). Reconfigurable in-memory computing is enabled by the conjunction of ferroelectric VNWFETs with classical LookUp Table (LUT) circuit structures such as a LUT2 [20] and where the output depends both on the select inputs (S<sub>0</sub> and S<sub>1</sub>) as well as on the stored states (here 4 states stored in a non-volatile manner to reflect a 2-input truth table), i.e.  $Y = A. \overline{S_1}. \overline{S_0} + B. \overline{S_1}. S_0 + C.S_1. \overline{S_0} + D.S_1. S_0.$

#### 2) Reconfigurable FETs

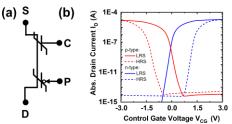

Polarity-controllable transistors (PC-FETs) leverage a multitude of input gates on a single ambipolar channel, to dynamically select both conduction state, as well as carrier type (Fig. 4) [21]. PC-FETs connected to a common body enable inherent X-to-1 multiplexing in a single transistor with

X independent drain-contacts. Non-volatile PC-FETs in a 3D tile also intimately incorporate multi-bit memory capability within computing elements, thus opening the way for a new concept for computing-in-memory.

Fig. 4. Polarity-controllable transistor with Fe-Gate. While PC-FETs require a constant input to program gates, Fe-gate oxides are programmed by a pulse, reducing the dynamic power consumption.

#### C. Toward Dynamic Modeling

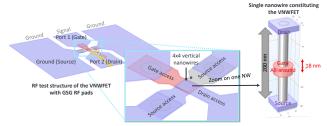

Another design perspective for improved dynamic performance of the logic cells includes optimized test structures. To ensure circuit design involving a 3D emerging technology, accurate compact models capturing the static and dynamic device behavior are mandatory [7], but on-wafer test structures of such devices also include parasitic elements induced by pads and interconnects that are necessary to probe the devices under test (DUT). Due to the 3D nature of interconnects, standard methods to remove these parasitic contributions (de-embedding) become inaccurate owing to the fact that classical design of passive test-structures (Open and Short) no longer remain sufficient to completely model the extrinsic 3D parasitic network. Figure 5 shows the respective sizes of the DUT and its associated test structure illustrating the requirement to reinvent dedicated deembedding methods for the 3D VNWFET technology. In [22] a new de-embedding method for this technology was introduced that makes use of electromagnetic (EM) simulations to virtually reconstruct the entire parasitic network including coupling capacitive, inductive and resistive parasitic elements.

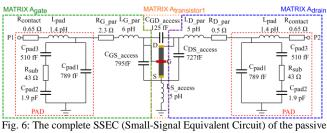

The values of all these parasitic elements constituting the small-signal equivalent circuit (SSEC) were calculated through (i) analytical equations from the physical dimensions, (ii) the material properties of the device, (iii) the standard calibration techniques such as SOLT (Short-Open-Load-Thru) as well as (iv) from EM simulations. The overall SSEC is shown in Fig. 6 along with the values of the parasitic elements. At this stage, this SSEC can be used to generate the ABCD matrices of the gate and drain parasitic access contributions for successful de-embedding of the intrinsic S-parameter measurements [17, 22]. This allows us to extract the intrinsic transistor S-parameters for device modeling and subsequently continue towards 3D logic cell design.

Fig. 5: Schematic depicting the size of the test structure featuring GSG (Ground-Signal-Ground) pads allowing the use of the RF probe with regards to the size of one single nanowire featuring the channel of the VNWFET.

Fig. 6: The complete SSEC (Small-Signal Equivalent Circuit) of the passive elements associated with the VNWFET test structure.

#### III. STANDARD LOGIC CELL MODELING

In this section, we leverage the developed compact model to assess the performance metrics of various 3D logic cell circuit topologies in the VNWFET technology. The ultimate goal of this study is to enable logic synthesis, which needs a library of characterized basic logic cells as a prerequisite.

#### A. Energy-delay characterization of standard logic cells

The goal of the following simulation-based exploration is to study the impact of using a large range of nanowires per transistor on typical static and dynamic logic performance metrics, for several standard logic cell topologies. In the simulation protocol, we assume that the gate capacitance behaves in the same way for both p- and n-type VNWFETs, and that the capacitive load on the output of each structure is equivalent to that of a single inverter of drive strength 1. Since the VNWFET gate capacitance is experimentally determined to be 20aF per NW, and assuming that its evolution with NW number is linear, we deduce a capacitance contribution for INV1X1 as 160aF.

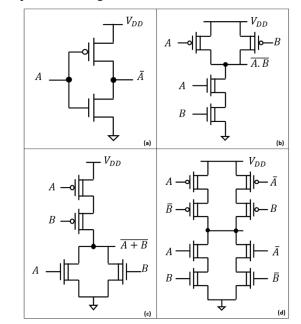

In this context we aimed to study the behavior of four main logic cells: INVX1, NAND2X1, NOR2X1, and XOR2X1. Figure 7 depicts the transistor-level schematics of these Boolean gates, where the formalism OPnXk indicates the boolean operation OP, the number of inputs *n* and the number of outputs *k* of each gate.

Fig. 7. Schematics of logic cells studied: (a) INV1X1, (b) NAND2X1, (c) NOR2X1, (d) XOR2X1.

The first step was to prove the ability of implementing such cells based on the VNWFET technology. In this context, we

carried out simulations using the HSpice<sup>TM</sup> commercial simulator, where we used the compact model described in section II implemented as an executable Verilog-A model for the VNWFET.

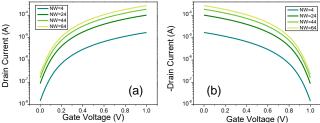

The gate physical length  $L_g$  and the nanowire (NW) diameter  $d_{nw}$  are both parameters which are determined by the fabrication process. Throughout this work, and based on experimental devices, the values of these parameters are set to  $L_g = 18$  nm and  $d_{nw} = 22$  nm respectively. Based on this, as well as the definition of other fixed model parameters, we investigated the number of nanowires for p-type and n-type transistors to be used, as the only design parameter remaining to enable the optimization of device and circuit performance. The first essential step in this work is to verify the functionality of the n-type and p-type VNWFET devices themselves through DC-sweep simulation in order to ensure that they have the expected  $I_{DS}/V_{GS}$  characteristic behavior, as illustrated in Figure 8.

Fig. 8. Variation of drain-source current  $I_{\rm DS}$  with gate-source voltage  $V_{\rm GS}$  and number of nanowires per VNWFET NW of (a) n-type VNWFET and (b) p-type VNWFET.

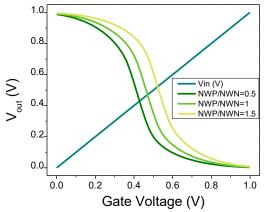

Subsequent to this verification, we simulate an elementary inverter gate shown in Figure 7(a) in order to determine the correct ratio between n-type and p-type NW (number of nanowires per VNWFET) values to obtain an optimal midpoint voltage. In this work, we also chose a range of values of NW for n-type transistors that allows us to study the behavior of the device under different drive strengths. For each value, we run DC-sweep simulations while varying the gate voltage from 0 to  $V_{DD}$  and assessing the output behavior for varying numbers of nanowires for the p-type device. We find that for all the defined NW values, a ratio of 1 between the number of NWs of p-type and n-type will give us an optimal midpoint voltage at half  $V_{DD}$  as shown in Figure 9, which leads to balanced noise margins and well-matched rise and fall times of the cell.

Fig. 9: Variation of inverter output voltage as function of the input voltage variation between 0 and  $V_{\rm DD}$  (1V) for different ratios between the number of nanowires (NW) used for p-type and n-type transistors. It can be clearly seen that a ratio of 1 between NW of p-type and n-type devices achieves optimal midpoint voltage at half  $V_{\rm DD}$ .

It is important of course to note that this ratio depends on the set of parameters used in the simulation. For this study, the chosen values for the number of NWs of the n-type device of the inverter were 4, 24, 44 and 64. The corresponding number of NWs for the p-type device is chosen according to the above described methodology. For the other cells, and in order to achieve drive strengths equivalent to that of the inverter, we redefine the number of nanowires by doubling the number of NWs in case of two series transistors.

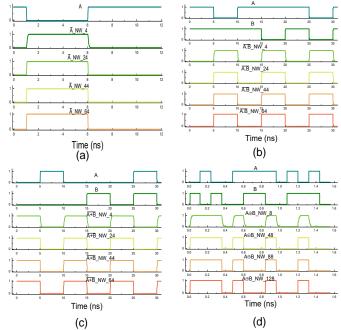

Fig. 10: All possible output transitions in: (a) Inverter, (b) NAND, (c) NOR, and (d) XOR affected by input transitions.

After defining the sets of NW parameters, we identify the simulation limitations of the executable model and adjust our simulations accordingly. Then a detailed study of the static and dynamic behavior of all cells was carried out, as detailed in the following subsections.

This study was done by varying the number of nanowires used in each logic gate to study their behavior under different drive strength. The simulations showed that using this technology we can successfully implement logic NOT, NAND, NOR and XOR functionalities as shown in Fig 10.

To characterize the library of standard logic cells, it is necessary to study the main conventional performance metrics of the targeted logic cells, i.e. propagation delay, rise/fall time and dynamic power consumption where:

- The delay corresponds to the time difference between the output voltage and input voltage to reach half V<sub>DD</sub>

- Rise (resp. fall) time corresponds to the time needed by the output voltage to rise (resp. fall) from  $0.1V_{DD}$  (resp.  $0.9V_{DD}$ ) to  $0.9V_{DD}$  (resp.  $0.1V_{DD}$ )

- The dynamic power consumption for a particular transition is calculated by measuring the supply current during the output transition

- The leakage power is calculated by measuring the supply current during all static combinations of inputs

For each cell, all the possible output transitions based on input(s) transitions are defined. Then for each case, the timing and energy consumption are measured as described above.

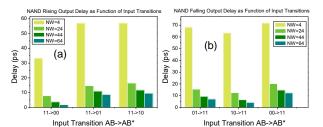

Fig. 11. Delay in output (a) rising, (b) falling transitions of a NAND gate as affected by different input transitions

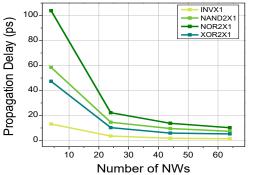

Fig. 12. Average propagation delay of logic cells under study as function of the number of nanowires used per VNWFET device.

Fig. 11 is a detailed example on how we studied the delay behavior of each logic cell. It is clear that the delay is dependent on the input(s) transitions, and that with the increases of NWs used per VNWFET the delay will decrease. For all the cells under study we found, as expected, that with the increase in the number of NWs used, a decrease in delay (Fig 12) and rise/fall times is observed as well as an increase in dynamic power consumption (Table I).

|            |              |                       | Nb of nanowires of nmos |      |      |      |  |

|------------|--------------|-----------------------|-------------------------|------|------|------|--|

| Logic Cell | Output Tran  | Input AB              | 4.0                     | 24.0 | 44.0 | 64.0 |  |

| INV        | ↑            | ¥                     | 171                     | 395  | 645  | 880  |  |

|            | $\checkmark$ | 1                     | 1.80                    | 232  | 439  | 650  |  |

| NAND       | Ŷ            | ↓1                    | 1151                    | 1374 | 1490 | 1736 |  |

|            |              | 1↓                    | 1152                    | 1288 | 1554 | 1839 |  |

|            |              | $\downarrow \uparrow$ | 1151                    | 1374 | 1490 | 1736 |  |

|            | ¥            | ↑1                    | 2.05                    | 111  | 326  | 537  |  |

|            |              | 1个                    | 2.90                    | 133  | 385  | 658  |  |

|            |              | ተተ                    | 2.05                    | 111  | 326  | 537  |  |

| NOR        | Ŷ            | 10                    | 2119                    | 2249 | 2463 | 2807 |  |

|            |              | 0↑                    | 2106                    | 2147 | 2459 | 2658 |  |

|            |              | $\uparrow \uparrow$   | 2119                    | 2249 | 2463 | 2807 |  |

|            | <b>1</b>     | ተ0                    | 2.23                    | 82   | 308  | 591  |  |

|            |              | 0ተ                    | 2.19                    | 203  | 540  | 911  |  |

|            |              | ተተ                    | 2.23                    | 82   | 308  | 591  |  |

| XOR        | ŕ            | ↓1                    | 742                     | 1289 | 1934 | 2533 |  |

|            |              | ተ0                    | 736                     | 1015 | 1241 | 1386 |  |

|            |              | 1↓                    | 761                     | 1498 | 2368 | 2485 |  |

|            |              | <u>0</u>              | 750                     | 1402 | 1235 | 1370 |  |

|            | $\checkmark$ | ↑1                    | 27.5                    | 712  | 1781 | 1801 |  |

|            |              | 10                    | 66.6                    | 271  | 495  | 667  |  |

|            |              | 1个                    | 19.5                    | 546  | 1169 | 1785 |  |

|            |              | 0↓                    | 17.7                    | 244  | 484  | 672  |  |

Table I: The dynamic energy values (aJ) for the logic cells under study, for all possible input transitions leading to output rising or falling transitions and for different number of NWs.

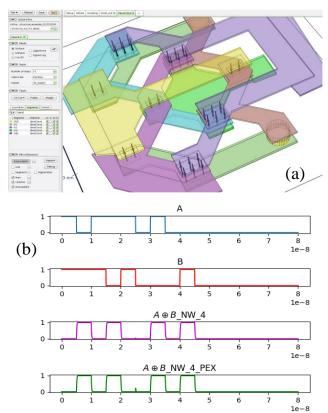

#### B. Parasitic-annotated assessment

For devices with such small dimensions and compact footprint, circuit-level parasitics (in particular from coupling capacitance, metal contact, layout-related issues) can significantly limits the benefit in design. In order to assess the impact of parasitics, we designed the layout for a 2-input XOR gate (one of the more complex logic functions, and including in-cell generation of complemented inputs) as shown in Fig. 13(a) and extracted the associated parasitic network based on the aforementioned geometrical parameters and material coefficients. Metal interconnect layers connect top and bottom nanowire contacts, as well as gate contacts surrounding the nanowires to create GAA devices. Transient simulation results for the resulting parasitic-annotated 2-NW/transistor XOR2 cell are shown in Fig. 13 (b). This enabled us to carry out a comparative study in order to quantify the impact of parasitic interconnect networks on key performance metrics. The full dataset is shown in Table II. Comparing delay and energy per transition figures, we quantify the average increase in delay as +4% and energy/transition as +19% when considering the parasitic interconnect network.

Fig. 13. 2-input XOR logic cell. (a) Layout used for parasitic extraction. (b) Transient simulation results with and without parasitic annotation.

|                      |                            | Delay (ps)     |             | Energy / transition (aJ) |             |

|----------------------|----------------------------|----------------|-------------|--------------------------|-------------|

| Output<br>transition | Input<br>transition<br>A B | Without<br>PEX | With<br>PEX | Without<br>PEX           | With<br>PEX |

| 1                    | ↓1                         | 93.74          | 83.83       | 724.81                   | 825.82      |

|                      | 个0                         | 90.93          | 111.63      | 725.42                   | 803.65      |

|                      | 1↓                         | 90.73          | 83.41       | 724.91                   | 851.42      |

|                      | 0个                         | 89.40          | 100.32      | 725.77                   | 792.08      |

| $\checkmark$         | ↑1                         | 92.12          | 85.60       | 5.09                     | 34.69       |

|                      | 10                         | 90.75          | 112.12      | 5.29                     | 58.59       |

|                      | 1个                         | 95.57          | 83.42       | 4.70                     | 45.04       |

|                      | 0↓                         | 92.73          | 102.55      | 5.00                     | 59.05       |

|                      | Average                    | 92.00          | 95.36       | 365.12                   | 433.79      |

|                      | Increase                   |                | +3.65%      |                          | +18.81%     |

Table II: Delay (ps) and energy/transition values (aJ) for a 2-NW per transistor XOR2 with and without layout-extracted parasitic annotation.

#### C. Impact of electro-thermal and trapping effects

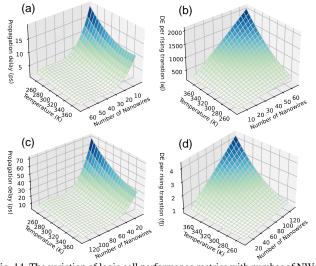

In order to study the electrothermal and trapping effects on the behavior of VNWFET based logic cells, we first set the related model FLAG parameters to 1 (described in section II-A) to activate self-heating and trapping. Next, we vary the temperature (250K-400K), within the range allowed by the technology and model specifications, and perform logic circuit simulations. For all logic cells, we observe that these variations have no effect on the functional behavior. We also observe that while the propagation delay decreases with the increase of temperature, dynamic energy consumption/transition increases. These phenomena result from a reduction of the threshold voltage with temperature, leading to a higher drive current as well as a higher leakage current. Fig. 14 shows these trends using the INV1 and XOR2 cells as examples.

Fig. 14. The variation of logic cell performance metrics with number of NWs per VNWFET and temperature while considering self-heating and trapping effects. (a) INV1 / propagation delay (ps). (b) INV1 / dynamic rising energy consumption (aJ). (c) XOR2 / propagation delay (ps). (d) XOR2 / dynamic rising energy consumption (fJ).

#### IV. DISCUSSIONS AND PERSPECTIVES

We presented comprehensive insights into 3D logic circuit design based on junctionless vertical nanowire transistors leveraging multi-physics simulations and SPICE-compatible compact models. In particular, we studied temperature effects and trap dynamics through dedicated measurements and extracted associated model parameters that couple these effects dynamically to circuit simulations. Cell-level performance of circuits such as inverter or XOR, studied based on the developed compact model, indicate a strong impact of electrothermal effects in the VNWFET technology. Threshold voltage shift due to increasing temperature leads to an increase in drive current at the detriment of a reduced on-off current ratio which in turn limits circuit functionality at elevated temperatures especially at the onset of self-heating due to confinement effects for cells with increased complexity. In addition, interface trapping has a major role in determining dynamic performance metrics such as the delay. Careful consideration is thus required for designing circuits operating under high-temperature conditions using the current state of the VNWFET technology. Work-around solutions such as gate work-function / doping engineering can be envisioned that could be useful as a feedback for process improvement. Other fabrication potential improvements include test-structure and cell-level 3D interconnect design optimization to achieve low-latency and compact 3D logic circuits.

#### ACKNOWLEDGMENT

This work was supported by the project FVLLMONTI funded by European Union's Horizon 2020 research and innovation program under grant agreement No101016776.

#### REFERENCES

- [1] The International Roadmap for Devices and Systems: 2022 Update.

- [2] J. Jeong, et al., "Performance-power management aware state-of-theart 5nm FinFET design (5LPE) with dual CPP from mobile to HPC application", IEDM, pp. 20.1.1-20.1.4, December 2020.

- [3] Y. Yasuda-Masuoka, et al., "High performance 4nm FinFET platform (4LPE) with novel advanced transistor level DTCO for dualCPP/HP-HD standard cells", IEDM, pp. 13.3.1-13.3.4, December 2021.

- [4] F.-K. Hsueh, et al., "First demonstration of ultrafast laser annealed monolithic 3D gate-all-around CMOS logic and FeFET memory with near-memory-computing macro", IEDM, pp. 40.4.1-40.4.4, 2020.

- [5] S. Venkateswarlu, O. Badami, and K. Nayak, "Electro-Thermal performance boosting in stacked Si gate-all-around nanosheet FET with engineered source/drain contacts," *IEEE Trans. Electron Device*, vol. 68, no. 9, pp. 4723–4728, Jul. 2021.

- [6] S.C. Song, et al., "System design technology co-optimization for 3D integration at <5nm nodes", IEDM, pp. 22.3.1-22.3.4, December 2021.</p>

- [7] C. Maneux et al. "Modelling of vertical and ferroelectric junctionless technology for efficient 3D neural network compute cube dedicated to embedded artificial intelligence" (Invited). 67th Annual IEEE IEDM, San Francisco, Dec. 11-15, 2021.

- [8] D.S. Tang, and B.Y. Cao, "Ballistic thermal wave propagation along nanowires modeled using phonon Monte Carlo simulations," *App. Therm. Eng.*, Vol. 117, pp. 609–616, May 2017.

- [9] C. Mukherjee, A. Poittevin, I. O'Connor, G. Larrieu and C. Maneux, "Compact modeling of 3D vertical junctionless gate-all-around silicon nanowire transistors towards 3D logic design", *Solid-State Electronics*, vol. 183, pp. 108125, Sep. 2021.

- [10] Y. Guerfi, G. Larrieu "Vertical silicon nanowire field effect transistors with nanoscale gate-all-around" Nanoscale Res Lett 11, 210 (2016).

- [11] C.-W. Lee, A. Borne, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, P. Razavi, and J.-P. Colinge, "High-Temperature Performance of Silicon Junctionless MOSFETs," IEEE Transactions on Electron Devices, vol. 57, no. 3, pp. 620-625, March 2010.

- [12] S. Kwon, M. C. Wingert, J. Zheng, J. Xiang, and R. Chen, "Thermal transport in Si and Ge nanostructure in the 'confinement' regime," Nanoscale, vol. 8, no. 27, pp. 13155–13167, Jun. 2016.

- [13] J. B. Varley, A. Janotti, C. Franchini, and C. G. Van de Walle, "Role of self-trapping in luminescence and p-type conductivity of wide-bandgap oxides," *Phys. Rev. B*, vol. 85, pp. 081109–04, Nov. 2012.

- [14] Y. Guo and M. Wang, "Phonon hydrodynamics for nanoscale heat transport at ordinary temperatures," *Phys. Rev. B*, vol. 97, pp. 035421– 27, Jan. 2018.

- [15] COMSOL, Inc., COMSOL Multiphysics.

- [16] Y. Wang, H. Rezgui, C. Mukherjee, M. Deng, A. Kumar, J. Muller, G. Larrieu and C. Maneux, "Evidence of Trapping and Electrothermal Effects in Vertical Junctionless Nanowire Transistors", EUROSOI-ULIS, Tarragona, Spain, May 2023

- [17] C. Maneux, C. Mukherjee, M. Deng, G. Larrieu, Y. Wang, Houssem Rezgui and B. Neckel Wesling, "Strategies for Characterization and Parameter Extraction of Vertical Junction-less Nanowire FETs dedicated to Design Technology Co-Optimization", 243<sup>rd</sup> ECS Meeting, Boston, US, May 28<sup>th</sup> -June 2<sup>nd</sup>, 2023.

- [18] H. Fujisawa, K. Ikeda, S. Nakashima, "Nonvolatile operation of vertical ferroelectric gate-all-around nanowire transistors," Jpn. J. Appl. Phys., 60 SFFB10, August 2021.

- [19] X. Yin et al., "Exploiting ferroelectric FETs for low-power non-volatile logic-in-memory circuits", Proc. of International Conference on Computer-Aided Design, 2016, pp. 121:1 – 121:8.

- [20] E.T. Breyer et al., "Ultra-dense co-integration of FeFETs and CMOS logic enabling very-fine grained Logic-in-Memory", Proc. of European Solid-State Device Research Conference, 2019, pp. 118-121.

- [21] T. Mikolajick, G. Galderisi, S. Rai, M. Simon, R. Böckle, M. Sistani, J. Trommer, "Reconfigurable field effect transistors: a technology enablers perspective", Solid-State Electron. 2022, pp. 108381.

- [22] B. Neckel Wesling et al., "Extraction of small-signal equivalent circuit for de-embedding of 3D vertical nanowire transistor", Solid-State Electronics, vol. 194, p. 108359, Aug. 2022.