## Improving off-state capacitance of SOI-CMOS RF switches: how good are air microcavities?

Daniel Gheysens, Alain Fleury, Stéphane Monfray, Frédéric Gianesello, Philippe Cathelin, Jean-François Robillard, David Troadec, Emmanuel Dubois

### ► To cite this version:

Daniel Gheysens, Alain Fleury, Stéphane Monfray, Frédéric Gianesello, Philippe Cathelin, et al.. Improving off-state capacitance of SOI-CMOS RF switches: how good are air microcavities?. IEEE 53rd European Solid-State Device Research Conference, ESSDERC, Sep 2023, Lisbon, Portugal. pp.109-112, 10.1109/ESSDERC59256.2023.10268524. hal-04226645

## HAL Id: hal-04226645 https://hal.science/hal-04226645

Submitted on 3 Oct 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Improving off-state capacitance of SOI-CMOS RF switches: how good are air microcavities?

Daniel Gheysens<sup>1,2</sup>, Alain Fleury<sup>2</sup>, Stéphane Monfray<sup>2</sup>, Frédéric Gianesello<sup>2</sup>, Philippe Cathelin<sup>2</sup>, Jean-François Robillard<sup>1</sup>, David Troadec<sup>1</sup> and Emmanuel Dubois<sup>1</sup>

1) Univ. Lille, CNRS, Centrale Lille, Univ. Polytechnique Hauts de France, JUNIA, UMR 8520 -IEMN, F-59000 Lille, France 2) STMicroelectronics, 850 rue Jean Monnet 38920 Crolles France

Abstract— This paper investigates the reduction of the off-state capacitance (COFF) of SOI-CMOS RF switches induced by the introduction of air microcavity in the back-end interconnection network. A detailed methodology combining electromagnetic and semiconductor transport simulations is used to separately evaluate the respective contributions of the interconnects and junction capacitances. A baseline switch and an optimized version of the same are studied to evaluate their ability to take advantage of air microcavities. Simulations show a reduction of 73 fF/mm regardless of the switch structure considered, resulting in a 24.6% and 30.6% improvement in COFF for baseline and optimized switches, respectively, bringing the optimized version to a 60fs record Ron × Coff. This concept was experimentally implemented using a partial etch process that resulted in a reduction of 21.7 fF/mm, i.e., 7.2%. Finally, the implementation of a more isotropic and selective etching process using HF in vapor phase is shown to approach the optimal configuration of air microcavities.

*Keywords*— RF switch, Air microcavities, CMOS, SOI, Off-state capacitance, Vapor phase selective etching

#### I. INTRODUCTION

THE constant demand for evolution in communications forces standards to push their limits in terms of data rate, latency or security. As such, the latest 5G standard is based on key technologies such as spectrum sharing, massive MIMO or carrier aggregation for optimized usage of available bandwidth. We also note the deployment of a millimeter wave frequency bands (mmW) referred to as FR2 band covering the 24.25-52.6 GHz range to expand into high data rate marked at fixed locations [1][2]. As a consequence of the growing complexity of communication systems, an increase of switches becomes necessary to selectively propagate high frequency signals through the transmit/receive pathways. This constraint of complexity must of course be handled without impacting the systems in terms of insertion loss, linearity, power handling and isolation [3]. In order to limit the accumulation of losses along the propagation path, RF switches must offer low insertion losses reflected by a small on-state resistance with a sufficient isolation in the off-state. The two important parameters, R<sub>ON</sub> and C<sub>OFF</sub>, precisely reflect the performance of a switch in terms of insertion loss and isolation, respectively. Minimizing them also means reducing their product ( $R_{ON} \times C_{OFF}$ ), the main figure of merit (FoM) used to compare switches with various layouts implemented in different semiconductor technologies. Strategies for optimizing switch performance are manyfold, such as reducing the SOI film thickness to reduce COFF and

downscaling the gate length to lower R<sub>ON</sub>. Several reports have shown that these optimization levers can be implemented without compromising linearity and power handling [4][5][6] [7]. Nevertheless, these papers do not sidestep the point that the optimization of both insertion losses and isolation is a matter of compromise since any path leading to the reduction of RON inevitably degrades C<sub>OFF</sub> and the RF breakdown voltage as well. Improving these two parameters together is all the more difficult given the level of optimization already achieved to date, e.g., by simultaneously reconsidering the junction design, introducing offset spacers, boosting the stress level in the Contact-Etch-Stop-Layer (CESL), reducing the gate length and thickness as well as optimizing the circuit layout and the routing strategy of metal interconnect tracks [8]. In that context, the use of air microcavities within the metal interconnect network, also known as back-end-of-the-line (BEOL), appears as a legitimate option to investigate in an attempt to lower COFF independently of RON. The contribution of BEOL to the overall COFF is significant and typically ranges from 30 to 40%. [4][9]. The replacement of the intermetal dielectric with air theoretically enables the reduction of the material permittivity from  $\varepsilon_r \sim 4$  to  $\varepsilon_r=1$ , thus holding the promise of a substantial reduction of C<sub>OFF</sub>. In the present study, the impact of air microcavities in the BEOL is analyzed on two generations of switches, the first one serving as a baseline [4] and the second one being a significant evolution integrating many optimization factors [8]. Through this comparison, the specific question that is addressed here is whether the same COFF reduction margin can be achieved on a baseline structure and on an optimized structure. In this perspective, this paper first presents a simulation strategy to finely evaluate the impact of air microcavities in BEOL of RF switches. It follows by detailing a selective etching method to create microcavities in a post-process sequence. Subsequently, the efficiency of the proposed approach is experimentally validated by extracting COFF from S-parameter measurements on switches incorporating microcavities. Finally, perspectives for improvement of the etching process using a selective vapor phase are discussed in order to perfect the etching of the intermetallic dielectric down to the CESL, i.e., at the bottom of the metal 1 (M1) interconnect layer.

#### II. RF SWITCH LAYOUT AND BEOL ROUTING

As outlined previously, the baseline switch, referred to as [A] is based on a previous 130nm technology [4]. The improved switch structure, referred to as [B], is an upgrade of structure [A] in many points [8]. Here we focus on one of the

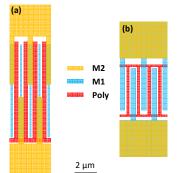

fundamental differences between structures [A] and [B], namely the organization of its layout and routing strategy of source/drain terminals and body contact. The respective layouts are available in Fig.1. The structure [A] is composed of 25 MOS transistors in parallel, each with a gate width of 10 µm, i.e., a cumulative width of 250 µm. Several variations of this structure exist in terms of polysilicon gate pitch (0.86 µm 0.92µm) and gate length (0.14, 0.16, 0.18 and 0.22  $\mu$ m). In the following of the study, we will restrict considerations on structure [A] with a grid length of 0.14 µm and a poly pitch of 0.92µm. The structure [B] is different in its layout and routing of the M1 layer. First, it consists of 50 transistors in parallel with a gate width of 5µm giving a cumulative width identical to structure [A]. The structure [B] also features variations on the polysilicon gate pitch and length. To obtain comparable and consistent results, a geometrical configuration similar to structure [A] is selected. Another main difference between the structures is the access to the active zone. On the one hand, structure [A], which has 4 metal layers, uses M1 and M2 levels to contact the source/drain terminals and for the body bias, resulting in a rather congested central region. Structure [B] has only 3 metal levels and uses only M1 over the active zone to reduce as much as possible parasitic capacitive coupling. This layout and routing simplification is achieved by using the active silicon layer to distribute the body bias along the chain of 50 transistors in parallel.

Fig. 1. (a) Partial layout of the RF switch test structure [A] (b) Partial layout of the RF switch test structure [B]

#### III. SIMULATION STRATEGY AND RESULTS

Since the efficiency of air microcavities is very strongly related to the BEOL density of metal tracks in the central zone of the switch, structure [B] is expected to limit the potential C<sub>OFF</sub> reduction as we start from an already optimized structure. To verify this assertion, a comprehensive simulation strategy was set up to appreciate with accuracy the impact of air microcavities. RF modeling is partitioned into two parts. The first consists in a 2D simulation of the transistors at the FEOL level using the IMPACT software to solve the small-signal transport equations based on the drift-diffusion (DD) approach. The second simulation task manages the complex interconnects in three dimensions (3D) due to the complexity of BEOL geometry. This is realized by solving Maxwell's equations with the Momentum module of the ADS software. In both simulation methods, COFF is extracted from the identification of the calculated Y-parameters to a lumped equivalent circuit [10]. The effect of air microcavities is essentially captured by simulations of the BEOL part of the switch. The DD simulation of the transistor is therefore used to calibrate results against measurements as the overall COFF derives from the sum of the BEOL and FEOL contributions. Under these conditions, the

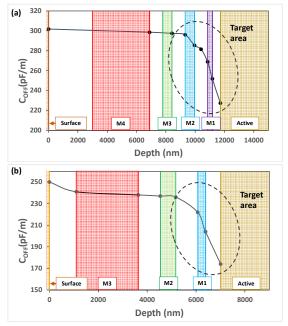

modelling approach is therefore able to determine the relative contributions of FEOL and BEOL to COFF before the introduction of air microcavities. For structure [A], we obtain C<sub>OFF-FEOL</sub>= 190.1 fF/mm (63%) and C<sub>OFF-BEOL</sub>= 111.7 fF/mm (37%) for a total figure of 301.8 fF/mm. On the other hand, structure [B] features C<sub>OFF-FEOL</sub>= 134.2 fF/mm (53%) and a  $C_{OFF-BEOL}$  = 116.5 fF/mm (47%) which yields a total  $C_{OFF}$  of 250.7 fF/mm. It is worth noting that the relative weight of the BEOL in the total capacitance is more important in structure [B] given the optimizations made to the intrinsic transistor. The relative contribution of air microcavities is therefore expected to be more consequent when compared to structure [A]. The electromagnetic simulation of the interconnect network (BEOL) is built from the circuit layout and the description of the metal/dielectric multilayer stack, each layer being described by its material and the relevant electrical parameters. The simulation methodology consists in replacing the inter-metal dielectric by air above a uniform etching front penetrating the interconnection network stack. The attenuation of the parasitic capacitive coupling induced by the BEOL can thus be appreciated as a function of the etching depth. The results of this simulation study are available in Fig. 2, from which two main conclusions can be drawn. First, it is clearly established that the attenuation of C<sub>OFF</sub> is extremely sensitive as the etching front falls below the M2 level and reaches its maximum when the dielectric removal is complete down to the bottom of M1. This defines the optimum target area to reach by etching. The second point relates to the C<sub>OFF</sub> reduction margin obtained for each structure. COFF of structure [A] is reduced from 301.8 fF/mm to 227.4 fF/mm representing a reduction of 24.6%. For the structure [B], a reduction of 30.5% is obtained from 250.7 fF/mm to 174.1fF/mm.

Fig. 2. (a) Simulated  $C_{OFF}$  as a function of the air microcavity etching depth for (a) structure [A] and for (b) structure [B]

These results show that air microcavities lead to a larger relative reduction of  $C_{OFF}$  on structure [B] despite an absolute improvement of about 73 fF/mm for the two styles of switch structures. In both cases, the simulations confirm the interest and efficiency of air microcavities for  $C_{OFF}$  reduction, even in the case of structure [B] whose layout had been optimized in

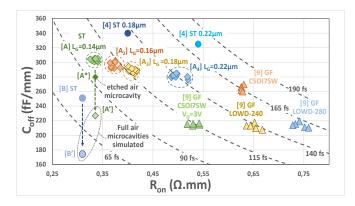

order to lighten the M2 metal density. Fig. 3 represents the classical  $R_{ON} \times C_{OFF}$  figure of merit of the simulated structures [A] and [B] along with some other measured results taken from the literature. The 4 clouds of points with labels [A], [A<sub>2</sub>], [A<sub>3</sub>], and [A<sub>4</sub>] correspond to measurements performed on the baseline switch structure. The measured performance achieved by structure [B] is also highlighted [8]. Data points labelled [A'] and [B'] correspond to the simulated ultimate case where the intermetal dielectric is totally removed down to the CESL layer, i.e., 227.4 fF/mm and 174.1 fF/mm for structures [A] and [B], respectively. The interest of air microcavities in the BEOL is well emphasized as structure [B'] establish a new state-of-the-art.

Fig. 3. R<sub>ON</sub> x C<sub>OFF</sub> figure of merit with the simulated impact of the cavities

#### IV. AIR MICROCAVITY PROCESS

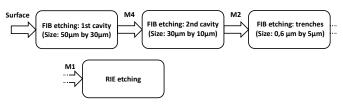

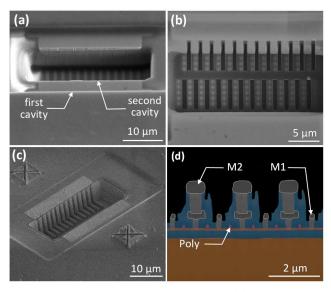

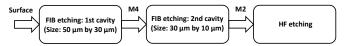

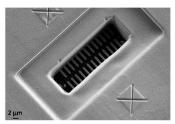

A post-process etching sequence has been set up for implementing the concept of air microcavities theoretically studied so far. The process flow is schematically illustrated in Fig.4 and comprises 3 localized etching steps using a focused ion beam (FIB) and a final finishing step based on reactive ion etching (RIE). Among the FIB steps, the first two create rectangular cavities,  $50 \times 30 \,\mu\text{m}^2$  and  $30 \times 10 \,\mu\text{m}^2$ , respectively, as shown in Fig. 5(a). These two cavities enable to go down 9 µm and reach the top of the M2 metal level. The separation in two distinct steps is used to recalibrate the etching depth at each transition between two metal levels, here M4 and M3, successively. The third FIB step creates narrow trenches of 0.6  $\times$  5 µm<sup>2</sup> between the fingers of the M2 level as shown in Fig. 5(b) and penetrate to a depth of 1.5  $\mu$ m down the top of M1 level. This step is the most critical in the process as any misalignment of the trenches can lead to a degradation of the metal interconnections. Finally, the last step, carried out by RIE etching, removes as much oxide as possible from the bottom of the trenches. The RIE chemistry used is composed of CF4 and Ar in order to achieve etch selectivity with respect to the aluminum layers, the nitride CESL layer and the polysilicon gate fingers in case of CESL over etching. The result after RIE etching is given in Fig. 5 (c) and (d). It is worth noting that the obtained result is still imperfect but is sufficient to evaluate the impact of air microcavities.

Fig. 4. Air microcavity etching process flow focused on RIE etching

Fig. 5. SEM pictures taken during successive steps of the process: (a) Top view of the first two cavities. (b) Tilted view of the trenches. (c) Tilted view of the final structure. (d) Cut view of the structure after RIE etching

The C<sub>OFF</sub> small signal characterization of the etched structure gives 279 fF/mm, i.e., an improvement of 22 fF/mm (7.3%) as shown by marker [A\*] in Fig.3. This figure does not match the simulated best result that reaches 227.4 fF/mm. To explain this discrepancy, the remaining volume of oxide due to incomplete etching at the M1 level must be carefully taken into account. It is possible to calculate an equivalent permittivity for each dielectric layer constituting the BEOL stack by considering the volume of oxide removed during the etching. The calculation is governed by the following formula:

$$\varepsilon_{eq} = \left(\frac{V_{etched}}{V_{layer}}\right) \cdot \varepsilon_{air} + \left(1 - \frac{V_{etched}}{V_{layer}}\right) \cdot \varepsilon_{oxide}$$

After applying these modifications in the BEOL stack description, Momentum simulation gives a revised  $C_{OFF}$  of 274 fF/mm, in excellent agreement with the experimental result. This model can be used regardless of the shape of remaining oxide obtained during the process by introducing effective permittivities.

#### V. PROCESS OUTLOOK AND CONCLUSION

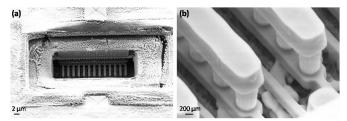

In order to completely remove the intermetallic oxide from the BEOL, a final vapor phase etching step is desirable to promote the isotropic penetration of the etchant. A second prerequisite is to ensure etch selectivity with respect to the metal interconnects. Hydrofluoric acid (HF) in vapor phase fulfills both of these requirements and has therefore been implemented in a simplified etching scheme given in Fig. 6 [11][12].

Fig. 6. Air microcavity etching process flow focused on HF etching

Fig.7 proposes pictures taken after vapor phase HF etching oxide into the cavity for 9 min. The implementation of this process highlights the efficiency deep into the cavity and the aggressiveness on top surface of the chip. This process matches expectations by reaching the polysilicon gates and by etching the oxide between the vias and contacts. Compared to the process using RIE etching, the efficiency of this process is closer to the complete oxide removal scenario on which simulations are based.

Fig. 7. SEM picture taken after vapor phase HF etching:

(a) Tilted view of the complete structure. (b) Tilted view focused at the bottom of the structure

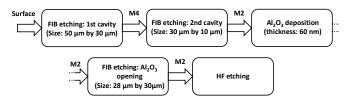

No characterization could be performed on these chips due to the damage of vapor HF on the contact probing pads located at the top surface of the chip. To cope with this problem, the process has been revisited by adding a protective layer so that the surface of the chip is not exposed to vapor HF. A 60 nm thick Al<sub>2</sub>O<sub>3</sub> layer meets all requirements and was implemented using atomic layer deposition (ALD) after the second FIB etching step. This additional protective layer requires a new FIB etching step to expose the cavity bottom to vapor HF. The final process given in Fig. 8 has been implemented as illustrated in Fig.9 showing that the Al<sub>2</sub>O<sub>3</sub> protective coating preserves the chip integrity.

Fig. 8. Air microcavity etching process flow focused on HF etching with  $\rm Al_2O_3$  protection layer

Fig. 9. SEM picture taken after vapor phase HF etching (with Al<sub>2</sub>O<sub>3</sub>)

The degree of completion of the latest process scheme opens the way to a complete demonstration of the concept of air microcavities in the BEOL. The results obtained have allowed to appreciate how much the efficiency of this concept depends on a total elimination of the dielectric down to the base of the first metal level. Future work will focus on confirming the principle of air microcavities through a series of characterization on  $C_{OFF}$ ,  $R_{ON}$  and the RF breakdown voltage. Particular attention will also be given to the impact of microcavities on thermal dissipation. Beyond its implementation in a post-process approach, this proof of concept must also be extended for an industrial deployment, which requires replacing the FIB steps, which is achievable through a modification of the BEOL process.

#### ACKNOWLEDGEMENT

This work was supported by: i) the STMicroelectronics-IEMN joint laboratory ii) the French government through the National Research Agency (ANR) under program PIA EQUIPEX LEAF ANR-11-EQPX-0025 and iii) the French RENATECH network on micro and nanotechnologies.

#### REFERENCES

- W. Chen, J. Montojo, J. Lee, M. Shafi and Y. Kim, "The Standardization of 5G-Advanced in 3GPP," in *IEEE Communications Magazine*, vol. 60, no. 11, pp. 98-104, November 2022, doi: 10.1109/MCOM.005.2200074.

- [2] M. -D. Tsai et al., "10.3 A 12nm CMOS RF Transceiver Supporting 4G/5G UL MIMO," 2020 IEEE International Solid- State Circuits Conference -(ISSCC), San Francisco, CA, USA, 2020, pp. 176-178, doi: 10.1109/ISSCC19947.2020.9063012.F.

- [3] Balteanu, "RF Front End Module Architectures for 5G," 2019 IEEE BiCMOS and Compound semiconductor Integrated Circuits and Technology Symposium (BCICTS), Nashville, TN, USA, 2019, pp. 1-8, doi: 10.1109/BCICTS45179.2019.8972735.

- [4] F. Gianesello, A. Monroy, V. Vialla, E. Canderle, G. Bertrand, M. Buczko, M. Coly, J. Nowakowski, N. Revil, L. Rolland, D. Gloria, A. Juge, S. Gachon, J.P. Aubert, E. Granger, "Highly linear and sub 120 fs Ron × Coff 130 nm RF SOI technology targeting 5G carrier aggregation RF switches and FEM SOC," 2016 IEEE 16th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Austin, TX, USA, 2016, pp. 9-12, doi: 10.1109/SIRF.2016.7445454.

- [5] C. Tinella, J. M. Fournier, D. Belot and V. Knopik, "A 0.7dB insertion loss CMOS-SOI antenna switch with more than 50dB isolation over the 2.5 to 5GHz band," *Proceedings of the 28th European Solid-State Circuits Conference*, Florence, Italy, 2002, pp. 483-486.

- [6] D. Im and K. Lee, "Characterization and optimization of partially depleted SOI MOSFETs for high power RF switch applications," *J. Solid-State Electronics*, vol. 90, pp. 94–98, Dec. 2013. Available: https://doi.org/10.1016/j.sse.2013.02.046

- [7] D. Kim and B.-W. Min, "High Power Ku-Band T/R and SP4T Switches in SOI CMOS, " *J. Electromagn. Waves and Appl.*, vol. 30, no. 6, pp. 728– 739, Mar. 2016. doi : 10.1080/09205071.2016.1145077

- [8] F. Gianesello et al., "Advanced 200-mm RF SOI Technology exhibiting 78 fs R<sub>ON</sub>×C<sub>OFF</sub> and 3.7 V breakdown voltage targeting sub 6 GHz 5G FEM, " in 2022 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Denver, CO, USA, 2022, pp. 191-194, doi: 10.1109/RFIC54546.2022.9863082.

- [9] M. Jaffe, M. Abou-Khalil, A. Botula, J. Ellis-Monaghan, J. Gambino, J. Gross, Z.X. He, A. Joseph, R. Phelps, S. Shank, J. Slinkman, R. Wolf, "Improvements in SOI technology for RF switches," 2015 IEEE 15th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, San Diego, CA, USA, 2015, pp. 30-32, doi: 10.1109/SIRF.2015.7119865.

- [10] A. Bhaskar *et al.*, "Substrate-Induced Dissipative and Non-Linear Effects in RF Switches: Probing Ultimate Performance Based on Laser-Machined Membrane Suspension," *Electronics*, vol. 11, no. 15, p. 2333, Jul. 2022, doi: 10.3390/electronics11152333.

- [11]A. Witvrouw et al., "Comparison between wet HF etching and vapor HF etching for sacrificial oxide removal," Proc. SPIE, vol. 4174, pp. 130–141, Aug. 2000.

- [12] J. Valle, D. Fernández and J. Madrenas, "Experimental Analysis of Vapor HF Etch Rate and Its Wafer Level Uniformity on a CMOS-MEMS Process," in Journal of Microelectromechanical Systems, vol. 25, no. 2, pp. 401-412, April 2016, doi: 10.1109/JMEMS.2016.2533267