## Concept and technology for full monolithic MOSFET and JBS vertical integration in multi-terminal 4H-SiC power converters

Ralph Makhoul, Nour Beydoun, Abdelhakim Bourennane, Luong Viêt Phung, Frédéric Richardeau, Mihai Lazar, Philippe Godignon, Dominique Planson, Hervé Morel, David Bourrier

## ▶ To cite this version:

Ralph Makhoul, Nour Beydoun, Abdelhakim Bourennane, Luong Viêt Phung, Frédéric Richardeau, et al.. Concept and technology for full monolithic MOSFET and JBS vertical integration in multi-terminal 4H-SiC power converters. 20th International Conference on Silicon Carbide and Related Materials (ICSCRM) - ICSCRM 2023, Naples University - Federico II, Sep 2023, Sorrento, Italy. hal-04221605

HAL Id: hal-04221605

https://hal.science/hal-04221605

Submitted on 28 Sep 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Concept and technology for full monolithic MOSFET and JBS vertical integration in multi-terminal 4H-SiC power converters

R. Makhoul<sup>1,2)</sup>, N. Beydoun<sup>3)</sup>, A. Bourennane<sup>1)</sup>, L. V. Phung<sup>2)</sup>, F. Richardeau<sup>4)</sup>, M. Lazar<sup>3)</sup>, P. Godignon<sup>5)</sup>, D. Planson<sup>2)</sup>, H. Morel<sup>2)</sup>, D. Bourrier<sup>1)</sup>

<sup>1)</sup> LAAS-CNRS, University of Toulouse, CNRS, UPS, Toulouse, France

<sup>2)</sup> Univ Lyon, INSA Lyon, Université Claude Bernard Lyon 1, Ecole Centrale de Lyon, CNRS, AMPERE, UMR5005, 69621 Villeurbanne, France

<sup>3)</sup> L2n - CNRS EMR 7004, UTT, 12 rue Marie Curie, 10004 Troyes, France

<sup>4)</sup> LAPLACE, University of Toulouse, CNRS, INPT, UPS, Toulouse, France

<sup>5)</sup> IMB-CNM, Campus UAB (08193) Bellatera, Spain E-mail: mihai.lazar@utt.fr (corresponding author)

For electric vehicles, there is a growing interest for the monolithic integration of dedicated power conversion functions in SiC dies [1]. Power converters are today realized using single VDMOS bonded on a power substrate using multiple bond wire interconnections [2], these last requiring an expensive operation time-consuming and source of aging problems [3]. In silicon carbide, few works are reported on the monolithic integration of power functions built with vertical VDMOS, most of them focused on the integration of auxiliary low-voltage functions [4].

The present paper explores the monolithic integration in SiC, within a single chip, of vertical switching cells based on JBS diodes and VDMOS. It proposes new and original medium power multi-terminal SiC converter architectures: Buck, Boost, H-bridge high-side row chip common drain-type and low-side row chip common source-type. This ultimate efficient power vertical integration proposed, using a minimum number of chips, will improve further the performance, reliability and cost reduction of the currently used discrete-dies-based switching cells.

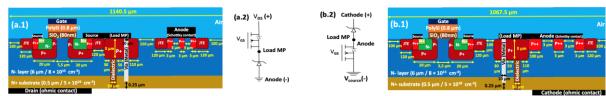

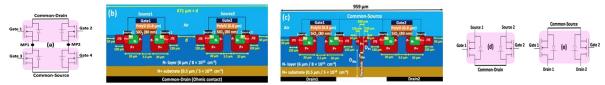

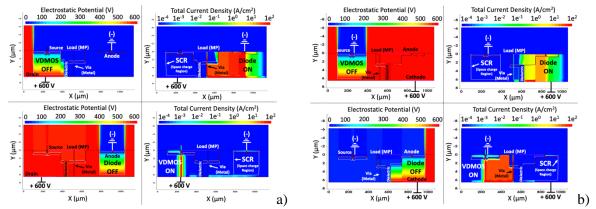

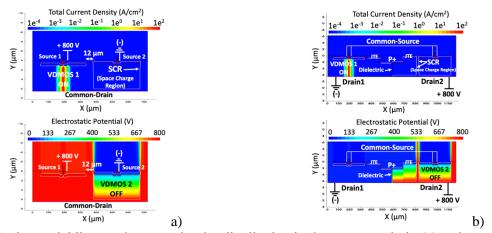

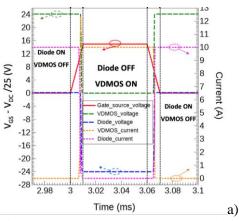

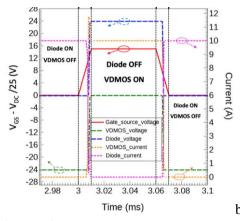

These vertical multi-terminal integrated architectures, presented in Fig. 1 (Buck and Boost) and Fig. 2 (H-bridge high-side and low-side dual-MOSFET) have been designed in order to support an applied voltage, up to 800 V, both vertically and laterally at the upper-side of the chip, and to carry a nominal current of 10 A. The operating modes, off-state, on-state and switching, were validated through 2D TCAD Sentaurus<sup>TM</sup>. Mixed-Mode simulations [5]. Particular attention was paid to the distribution of equipotential lines and current density within the elementary chip (Fig. 3 and Fig. 4) in order to limit the electric field peaks to 2.1 MV/cm, lower than the critical electrical field in SiC. Technological parameters have been determined as thickness and doping layers, junction termination extension (JTE) length, or minimal lateral distances to withstand the high voltage between the different integrated vertical MOSFET and JBS diodes (Fig. 5). The switching on/off waveforms of the individual part of the multi-terminal structures are presented in Fig. 6.

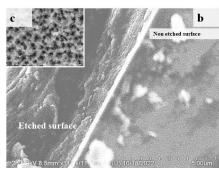

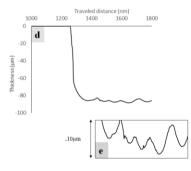

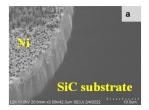

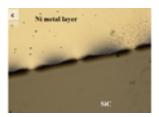

A first key technological step has been developed to insulate vertically the individual integrated transistors and diodes. Electrical insulation using a deep trench in the back-side and a p-type highly doped, deep well, above this trench is introduced. P<sup>+</sup>-layers are created by aluminum ion implantation and high temperature activation annealing [6]. The trench in the back-side SiC wafers is created by mask patterning, fluorinated plasma etching and electrochemical etching utilizing p-type created wells as stopping layers to selectively etch the N<sup>+</sup>-substrate (Fig. 7). A second key technological step has been developed for the Buck and Boost structures. A via in trench is created in the front-side by fluorinated plasma etching, filled with Ni metal by electroplating (Fig. 8) to connect the VDMOS and the JBS from one side to the other of the SiC wafer. Ni is preferred to Cu due to the MOSFET process compatibility.

At the conference and in the final paper, results from the first fabricated run will be presented.

- [1] Z. J. Shen, IEEE Power Electron. Mag. vol. 8, no. 2, pp. 14-23 (2021).

- [2] H. Yamaguchi et al., 3D-PEIM International Symposium Osaka, Japan, 2021, pp. 1-5.

- [3] S. Tanimoto et al., IEEE Transactions on Electron Devices, vol. 62, no.2, pp.258-269 (2015).

- [4] M. Okamoto et al., ISPSD International Symposium, Nagoya, Japan, 2021, pp. 71-74.

- [5] Sentaurus TCAD Simulation Tool by Synopsys Inc. Version U 2022.12-SP1.

- [6] M. Lazar et al., Nucl.Instrum.Method Phys.Res.B 365 pp. 256–259 (2015).

Fig. 1. (a) SiC VDMOS-JBS Buck-type switching cell principle: (a.1) Cross sectional view of the proposed 3-terminal chip with the different technological and geometrical parameters, (a.2) Simplified equivalent electrical circuit. (b) SiC VDMOS-JBS Boost-type switching cell principle: (b.1) Cross sectional view of the proposed elementary 3-terminal chip with the different technological and geometrical parameters, (b.2) Simplified equivalent electrical circuit.

Fig. 2. (a) Half-bridge using N-type VDMOS devices, (b) Cross-sectional principle of the Common-Drain type structure (high-side row), (c) Cross-sectional principle of the Common-Source type structure (low-side row), (d) Common-Drain simplified equivalent electrical circuit, (e) Common-Source simplified equivalent electrical circuit.

Fig. 3. Equipotential lines and current density distribution in the Buck (a) and Boost-type (b) switching cell

Fig. 4. Equipotential lines and current density distribution in the common-drain (a) and common-source (b) type three-terminal H-bridge SiC MOSFET power chip (X to Y ratio: 30)

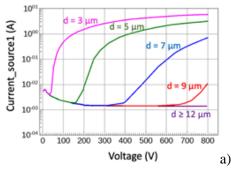

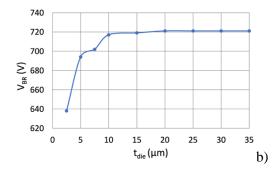

Fig. 5. Variation of the breakdown voltage of the common-drain H-bridge structure as a function of the distance "d" between the two MOSFET (a) and as a function of the dielectric thickness "t<sub>die</sub>".

Fig.6. MOSFET-part and JBS-part switching waveforms of the proposed 3-pole Buck (a) and Boost-type (b) switching cell at  $V_{DC} = 600V$ ,  $I_{LOAD} = 10A$ ,  $V_{GSmax} = 15V$ ,  $T_{CASE} = 300K$ .

Fig. 7. Surface patterning with p-type layers (a), SEM image of electrochemical etched surface (b). Inset showed the obtained porous surface (c),  $\alpha$ -step thickness (d) and roughness (e) measurements.

Fig. 8. SEM images of a 10 $\mu$ m thickness SiC substrate etched with Ni mask to perform the metallic via between the back-side cathode JBS-part and the front-side VDMOS-part (a), electroplating process to fill the via with Ni (b), optical image of the Ni electroplated layer on the SiC (c) and  $\alpha$ -step measurement of the Ni metal layer performed (d).

Acknowledgment: This national inter-lab research work received financial support from the French National Research Agency (ANR). The project name is "MUS²-IC" for Monolithic Ultimate power Switching cell in Silicon Carbide (n° ANR-21-CE05-0005), over the period 2022 – 2025. This work was supported by LAAS-CNRS and L2n-NanoMat micro and nanotechnologies platforms, members of the Renatech French national network.