# Full-SiC Single-Chip High-Side and Low-Side Dual-MOSFET for Ultimate Power Vertical Integration -Basic Concept and Technology

Ralph Makhoul, Nour Beydoun, Abdelhakim Bourennane, Luong Viet Phung, M. Lazar, Frédéric Richardeau, Philippe Godignon, Dominique Planson, Hervé Morel, David Bourrier

#### ▶ To cite this version:

Ralph Makhoul, Nour Beydoun, Abdelhakim Bourennane, Luong Viet Phung, M. Lazar, et al.. Full-SiC Single-Chip High-Side and Low-Side Dual-MOSFET for Ultimate Power Vertical Integration - Basic Concept and Technology. 25th Conference on Power Electronics and Applications (and Exhibition), EPE '23 (IEEE) ECCE Europe (Energy Conversion Congress and Expo Europe), Sep 2023, Aalborg, Denmark. 10.23919/EPE23ECCEEurope58414.2023.10264325 . hal-04203163

HAL Id: hal-04203163

https://hal.science/hal-04203163

Submitted on 11 Sep 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Full-SiC Single-Chip High-Side and Low-Side Dual-MOSFET for Ultimate Power Vertical Integration – Basic Concept and Technology

Ralph Makhoul<sup>(1,2)</sup>, Nour Beydoun<sup>(3)</sup>, Abdelhakim Bourennane<sup>(1)</sup>, Luong Viêt Phung<sup>(2)</sup>, Mihai Lazar<sup>(3)</sup>, Frédéric Richardeau<sup>(4)</sup>, Philippe Godignon<sup>(5)</sup>, Dominique Planson<sup>(2)</sup>, Hervé Morel<sup>(2)</sup>, David Bourrier<sup>(1)</sup>

(1)LAAS-CNRS, Université de Toulouse, CNRS, UPS, Toulouse, France

(2)Ampère, Univ Lyon, INSA Lyon, Université Claude Bernard Lyon 1, Ecole Centrale de Lyon, CNRS, Ampère, UMR5005, 69621 Villeurbanne, France

(3)Light, nanomaterials, nanotechnologies, Université technologique de Troyes & CNRS EMR 7004, 12 rue Marie Curie, 10004 Troyes, France

(4)LAPLACE, Université de Toulouse, CNRS, INPT, UPS, Toulouse, France (5)IMB-CNM, Campus UAB (08193) Bellatera, Spain

#### Acknowledgements

This national inter-lab research work received financial support from the French National Research Agency (ANR). The project name is "MUS²-IC" for Monolithic Ultimate power Switching cell in Silicon Carbide (n° ANR-21-CE05-0005), over the period 2022 – 2025. This work was supported by LAAS-CNRS and NanoMat micro and nanotechnologies platforms, members of the Renatech french national network.

#### **Keywords**

« Switching cell », « SiC MOSFET », « Device integration », « Device modelling », « Device simulation ».

#### Abstract

A full monolithic integration in multi-terminal SiC dies of a generic H-bridge power converter (800V/10A) consisting of dual N-type vertical MOSFET switches within only two multiterminal chips is proposed. Innovative two multiterminal monolithic power SiC-chips introduced and studied by 2D Sentaurus™ simulations. The first one integrates the high-side row switches of the bridge and the second one integrates the low-side row switches. Static and dynamic operating modes were validated through 2D-Mixed-Mode simulations. Main new process bricks allowing back-side insulating trenches based on plasma combined with photoelectrochemical etching are experimentally evaluated for the first time on power device SiC wafer.

#### Introduction

With the significant improvement in performance of SiC power VDMOS and their widespread adoption in the field of critical applications such as electric vehicles and railway, there is today a growing interest for the monolithic integration of dedicated power conversion functions in SiC dies [1]. Power converters are generally realized using Vertical Double diffused MOSFET (VDMOS) bare chips that are bonded on a power substrate and interconnected to each other using multiple bond wires. These latter require an expensive and time-consuming wiring operation and are source of aging problems. Moreover, the stray inductance of wire bonds limits the turn-off switching speed and increases losses of the converter using wide-bandgap devices. To overcome these drawbacks, the power converter can be realized using a minimum number of multi-terminal chips, that integrate monolithically the VDMOS switches, and a dedicated packaging 2D partial flip-chip on DBC/IMS substrate process. However, due to the chip size limitations, monolithic integration in multi-terminal dies is nowadays limited to low current ratings.

In previous works, the monolithic integration of power converters for medium power converters was applied to the case of converters consisting of silicon RC-IGBT switches [2] and permitted the proposition of new and original concepts of multi-terminal chips that involve the two-chip [3], three-chip [4] and finally the ultimate full monolithic single chip-converter [3].

In silicon carbide, few works were however reported on the monolithic integration of power functions built around the VDMOS. Furthermore, most of them mainly focused on the monolithic integration of auxiliary low voltage functions within a single high voltage VDMOS. Indeed, one can find the P-Well monolithic functionalization of a series normally-on cascode JFET current limiter [5], integration of auto-adjust JFET with VDMOS [6], integration of VDMOS with a CMOS gate buffer [7]. In the category of monolithic bidirectional switches, on SiC material, two vertical common drain-type VDMOS switches was recently reported in literature [8-10].

This article focuses on the innovative full monolithic integration of H-bridge high-side row chip common drain-type and low-side row chip common source-type, consisting of SiC VDMOS switches. The article is organized as follows: first of all, the basic concept of the monolithic integration in two multi-terminal chips is presented; then, the operating modes, off-state, on-state and switching, were validated through 2D TCAD Sentaurus™ Mixed-Mode simulations; after that, in order to provide the vertical insulation of the source-type chip a mandatory specific technological process brick was set-up for etching of back-side thick SiC wafer. It combines Inductively Coupled Plasma - Reactive Ion Etching (ICP-RIE) process and UV laser Photo-electrochemical (PEC) process; finally, a conclusion is suggested covering the conceptual and technological sections proposed in this article.

#### Principle of the single-chip high-side row and low-side row monolithic dual VDMOSFET

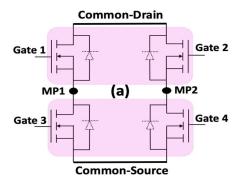

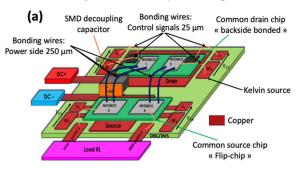

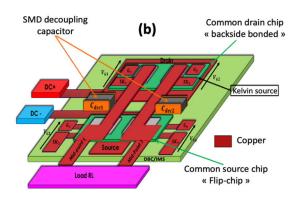

The power converter circuit is divided into two distinct and separate blocks as shown in Fig. 1 (a). The high-side row is composed of quasi-parallel connected VDMOS devices that share the same drain-side electrode. These VDMOS devices can be integrated quasi directly in a "common-drain" multi-terminal SiC power chip sharing their SiC bulk and epi-layer parts. The low-side is also composed of quasi-parallel connected VDMOS devices that share the same source-side electrode. This second chip is much more complex to develop as it requires a deep vertical insulating region that must be realized by etching a thick in back-side SiC substrate. A judicious packaging on DBC/IMS substrate of these two multiterminal power chips using partial flip-chip

connection make possible the realization of low stray inductance multi-phase power converter.

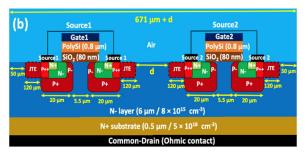

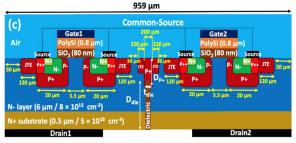

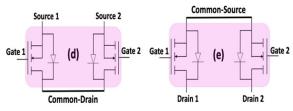

Fig. 1: (a) Half-bridge using N-type VDMOS devices, (b) Cross-sectional principle of the Common-Drain type structure (high-side row), (c) Cross-sectional principle of the Common-Source type structure (low-side row), (d) Common-Drain simplified equivalent electrical circuit, (e) Common-Source simplified equivalent electrical circuit.

Each of the two three-terminal proposed design are sketched in Fig. 1 (b) and (c) which are composed of two VDMOS sections. The common drain chip as well as the common source chip taken separately constitute half of a switching cell. The two VDMOS sections, in each power chip, can be in on-state or off-state. In off-state, the VDMOS within the multi-terminal chip must support the applied voltage. The design of these

chips has also to minimize the electrical interactions between the two VDMOS sections due to the extension of the lateral Space Charge Region (SCR).

The front-side of each three-terminal device is composed of MOS sections and lightly doped Pdiffusions (JTE termination). The back-side of the two three-terminal power chips are composed of thick N<sup>+</sup> substrate. In the common-drain type three-terminal structure, the VDMOS sections share an N<sup>-</sup> drift region which is sufficiently thick to support the applied 800 V. The optimization of the separation distance is carried-out using 2D simulations under Sentaurus  $^{\text{TM}}.$  The common source-type structure requires a mandatory insulation region between the two NVDMOS sections. This is achieved by a combination of a frontside P<sup>+</sup> well and a backside deep trench filled by a dielectric. Experimental results on the technological realization of this trench is provided by L2n (Light, nanomaterials, nanotechnologies) laboratory and its platform.

Fig. 2: Top view of the H-bridge on the SMI/DBC substrate using partial flip-chip technique: (a) with SiC chips backside bonded on the FR4 substrate, (b) wire bonds are replaced by copper tracks.

A judicious packaging on DBC/IMS substrate of these two multi-terminal power chips using partial flip-chip connection make possible the

realization of low stray inductance multi-phase power converter. Fig. 2 illustrates the two possible packaging of the two proposed multiterminal chips. In Fig. 2 (a), the high-side row multi-terminal chip is directly bonded by its backside on a DBC/IMS substrate [3]. However, the low-side row multi-terminal chip is advantageously flipped and is bonded by its source side as previously proposed [11-12]. In this configuration the switching loop is not planar-type as in a standard drain-side soldering packaging but orthogonal-type with a lowering loop area. A windowed insulating Kapton layer is placed between the flipped SiC chip and the DBC/IMS substrate. For the sake of illustration, the assembly of Fig. 2 (a) makes use of bonding wires while the assembly of Fig. 2 (b) makes use of direct copper-bars bonded on the power electrodes [19]. In Fig. 2 (b) using wider and thinner copper tracks plated close to the substrate. This latter permit reducing the loop area and the stray inductance. Moreover, in this latter, the midpoint voltage variations, dv/dt during switching, does not occur on the surface of the IMS/DBC substrate that radically reduces the commonmode current leakage at the turn-on dv/dt.

# 2D Sentaurus $^{TM}$ simulations of the single-chip high-side row and low-side row monolithic dual VDMOSFET

The proposed three-terminal chips were studied using 2D TCAD Sentaurus<sup>TM</sup> simulations [13]. The active area of each VDMOS section in Fig. 1 is 5 mm<sup>2</sup>. The monolithic three-terminal chips have to support the applied voltage both vertically and laterally at the upper-side of the chip, and to carry a nominal current of 10 A. The proposed vertical monolithic integrated devices should support between 600 and 800 V voltage and carry a nominal current of 10 A at 300 K.

The physical and geometrical parameters of the VDMOS illustrated in Fig. 1 were imposed by the CNM laboratory (Centro Nacional de Microelectrónica) process flow, an experienced and recognized technology center in Europe for SiC technology for more than twenty years and in particular in SiC MOSFETs [14].

### A. Common-Drain three-terminal power chip

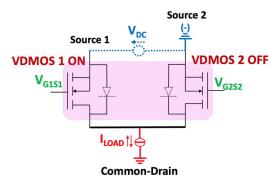

Fig. 1 (b) represents the 2D cross-sectional view of the elementary common-drain type three-terminal power chip. Fig. 3 shows the equivalent

electrical schematic of the common-drain type three-terminal power chip where the VDMOS 2 ( $V_{G2S2}$  OFF) is in the OFF-state and the VDMOS 1 in the ON-state ( $V_{G1S1}$  ON).

Fig. 3: Equivalent electrical schematic of the common-drain type three-terminal power chip at  $V_{DC} = 800 \text{ V}$ ,  $I_{LOAD} = 10 \text{ A}$ ,  $V_{G1S1} = 15 \text{ V}$ ,  $V_{G2S2} = 0 \text{ V}$ ,  $T_{CASE} = 300 \text{ K}$ .

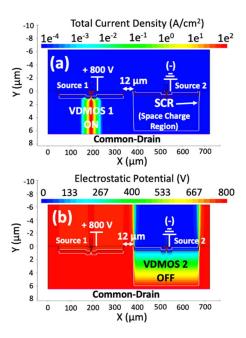

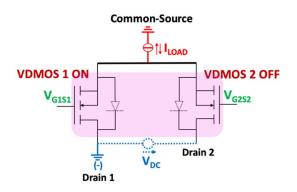

The first validation study on the common-drain type three-terminal power chip requires to determine the minimum lateral distance "d" to withstand the voltage of 800 V and avoid electrical interaction between the 2 sections of the VDMOS. Fig. 4 represents the variation of the breakdown voltage of the VDMOS 2 which is in the off-state as a function of the distance "d". One can notice that for a distance greater than or equal to 12 um the three terminal chip is able to withstand the voltage of 800V. Once the VDMOS 2 is in the OFF-state, two space charge regions (SCR) spread out: the first one spreads vertically in the N- layer while the second one spreads out laterally. For the lateral SCR, a distance "d" equal to 12 µm is sufficient to support the applied voltage.

Fig. 4: Variation of the breakdown voltage of the VDMOS 2 as a function of the distance "d".

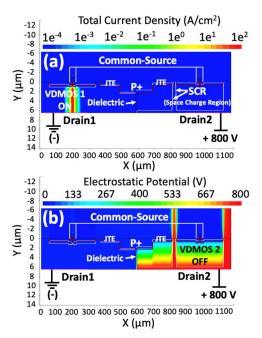

Fig. 5: Equipotential lines and current density distribution in the common-drain type three-terminal power chip (X to Y ratio: 30): (a) VDMOS 1 is in the ON-state, (b) VDMOS 2 in the OFF-state. (d = 12  $\mu$ m) (Leakage current = 6  $\mu$ A) (E<sub>max SiC</sub> = 2.1 MV/cm).

Fig. 5 gives the corresponding distribution of equipotential lines and current density within the elementary common-drain type chip. In the case a) we can notice that the VDMOS 1 is in ON-state and carries a current density of 100 A/cm<sup>2</sup>. In the case b) the VDMOS 2 is in OFF-state and withstands 800 V.

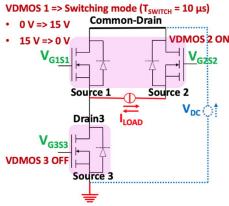

Fig. 6: Equivalent electrical schematic of the common-drain type three-terminal power chip using an additional discrete freewheeling body diode's MOSFET in low-side connection. Such a basic schematic is mandatory to easily put forward switching operation of the proposed common-drain type chip at  $V_{DC} = 400 \text{ V}$ ,  $I_{LOAD} = 10 \text{ A}$ ,  $V_{GISI}$  in switching mode ( $T_{SWITCH} = 10 \text{ }\mu\text{s}$ ),  $V_{G2S2} = 15 \text{ V}$ ,  $V_{G3S3} = 0 \text{ V}$ ,  $T_{CASE} = 300 \text{ K}$ .

Fig. 6 represents the equivalent electrical schematic of the common-drain type three-terminal power chip.

Fig. 7: VDMOS-part switching waveforms of the proposed common-drain type three-terminal power chip ( $V_{G2S2} = 15 \text{ V}$ ,  $V_{G3S3} = 0 \text{ V}$ ): (a)  $V_{G1S1}$  in switching mode ( $T_{SWITCH} = 10 \mu s$ ), (b)  $V_{DC} = 400 \text{ V}$ ,  $I_{LOAD} = 10 \text{ A}$ ,  $T_{CASE} = 300 \text{ K}$ .

Fig. 7 shows the VDMOS drain-source and gatesource voltage/current waveforms of the of the electrical schematic at turn-off illustrated in Fig. 6. A voltage of 400 V is applied between the Common-Drain and the VDMOS 3. A load current of 10 A is applied between the Source 1 and Source 2. An equivalent trapezoidal shaped waveform is applied to the gate with respect to the source voltage. The voltage value was imposed from 0 to 15 V with a switching time (T<sub>SWITCH</sub>) of 10us. This switching time was used because we have noticed that it improves the simulations convergence and reduces the simulation time as compared to the case of simulations that use usual switching times that are of the order of a nanosecond. From Fig. 7 (a) that shows the VDMOS 1 turn-off, and the drain-source voltage/current waveforms presented in Fig. 7 (b), we have found that the equivalent threshold voltage "Vth" is about 5.5 V

### **B.** Common-Source three-terminal power chip

Fig. 1 (c) represents the 2D cross-sectional view of the elementary common-source type three-

terminal power chip. Fig. 6 shows the equivalent electrical schematic of the common-source type three-terminal power chip where the VDMOS 2 ( $V_{G2S2}$  OFF) is in the OFF-state and the VDMOS 1 in the ON-state ( $V_{G1S1}$  ON).

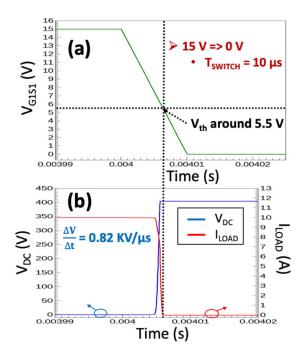

Fig. 8: Equivalent electrical schematic of the common-source type three-terminal power chip at  $V_{DC} = 800 \text{ V}$ ,  $I_{LOAD} = 10 \text{ A}$ ,  $V_{G1S1} = 15 \text{ V}$ ,  $V_{G2S2} = 0 \text{ V}$ ,  $T_{CASE} = 300 \text{ K}$ .

The technological challenge for the realization of the common-source type three-terminal power chip is related to the realization of the full vertical insulation, which combines a deep trench in the backside filled with a dielectric, and a deep P<sup>+</sup> implementation on the top side above this trench (Fig. 1.c). This insulation is essential to prevent any lateral current flow in both the N<sup>-</sup> drift layer and the N<sup>+</sup> substrate between the two VDMOS sections.

The first validation study on the common-source type three-terminal power chip requires to optimize the 3 technological parameters  $D_{P^+}$ ,  $D_{\rm die}$  and  $t_{\rm die}$  (Fig. 1.c) in order to withstand up to 800 V and prevent any lateral current flow between the two VDMOS sections.

Table I: Influence of " $D_{P+}$ " and " $D_{die}$ " on the breakdown voltage " $V_{BR}$ " of the VDMOS 2. (Leakage current = 6  $\mu A$ )

| $D_{P^{+}}(\mu m)$ | D <sub>die</sub> (µm) | $V_{BR}(V)$ |

|--------------------|-----------------------|-------------|

| 1.5                | 5.5                   | 800         |

| 2.5                | 4.5                   | 721         |

| 3.5                | 3.5                   | 610         |

| 4                  | 3                     | 547         |

| 4.5                | 2.5                   | 486         |

Table I shows the variation of the breakdown voltage of the VDMOS 2 as a function of the depth of the P+ layer " $D_{P+}$ " and the depth of the dielectric trench " $D_{die}$ " in the N- layer ( $D_{Die} = N$ -layer -  $D_{P+}$ ). Considering the technological realization of the P+ implantation zone, the minimum depth of this zone is 2.5  $\mu$ m. According to table I and for  $D_{P+}$  equal to 2.5  $\mu$ m the VDMOS 2 withstands a voltage of 721 V. Beyond this depth, the breakdown voltage decreases drastically thanks to a significant increase of the leakage current which provokes the premature breakdown.

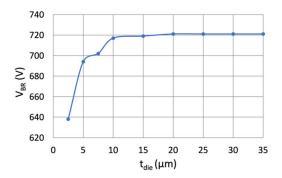

Fig. 9: Variation of the breakdown voltage " $V_{BR}$ " of the VDMOS 2 as a function of the dielectric thickness " $t_{die}$ ". ( $D_{P^+}$ = 2.5 µm) (Leakage current = 6 µA)

Fig. 10: Equipotential lines and current density distribution in the common-source type three-terminal power chip (X to Y ratio: 30): (a) VDMOS 1 is in the ON-state, (b) VDMOS 2 in the OFF-state. ( $D_{P+}=2.5~\mu m$  and  $t_{die}=20~\mu m$ ) (Leakage current = 6  $\mu A$ ) ( $E_{max~SiC}=2.1~MV/cm$ )

Fig. 9 shows the variation of the breakdown voltage of the VDMOS 2 as a function of the thickness of the dielectric " $t_{die}$ " and for  $D_{P^+} = 2.5$  µm. We can see that for a thickness greater than or equal to 20 µm the VDMOS 2 can withstand the optimal voltage of 721 V. Also, this thickness seems sufficient to prevent any lateral current flow between the two VDMOS sections.

Fig. 10 gives the corresponding distribution of equipotential lines and current density within the elementary common-source type chip. In case a) we can notice that the VDMOS 1 is in ON-state and carries a current density of 100 A/cm<sup>2</sup>. In case b) the VDMOS 2 is in OFF-state and withstands 800 V.

## Technological realization of the deep vertical insulating SiC etched-trench region

In our experimental work, we are reporting the SiC etching using two techniques: fluorinated plasma etching and electrochemical etching to perform the trenches needed in our devices.

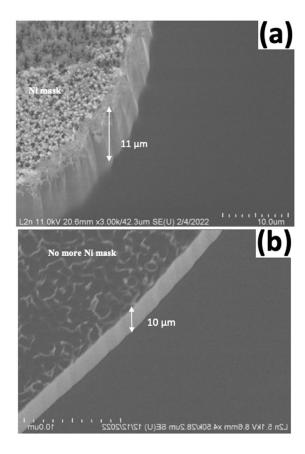

Compared to our previous studies reported [15-17], in our Plassys MU400 fluorinated plasma ICP/RIE equipment we could reach a maximum etching rate for SiC up to  $0.6~\mu m/min$ . We tried to increase the time of etching in order to increase the obtained etching thickness but the Ni mask could completely be consumed as shown in Fig. 11 (b) if the thickness of the Ni layer is not increased.

The ability to increase the Ni-deposited metal layer is limited in our cleanroom facilities, since our e-beam evaporators allow to deposit of a maximum thickness of metal layer about 250 nm.

We performed electrolysis as reported in our previous study to have a thicker metal layer [18]. We could have a metal layer equal to around 4  $\mu$ m that allows us to perform deeper SiC plasma etching. The parameters we used in our performed plasma etching are based on studies done before where the optimum parameters to obtain deep etching and smooth etched surface have been investigated [15-17].

Firstly, we performed plasma etching for 30 min and we got 15  $\mu$ m etching thickness then we could have performed twice the plasma etching with a 30 min duration for the etching time and the etching thickness doubled up to around 30  $\mu$ m.

Fig. 11: (a) SEM images of etched SiC masked with Ni Mask, (b) SEM image of etched SiC and the Ni mask consumed totally.

This is today the limit of our plasma etching system, with a reasonable etching time and preserving the initial SiC state obtaining vertical and smooth trenches.

To perform the vertical insulation through the entire SiC N<sup>+</sup>-substrate, we need an etching thickness corresponding to the thickness of the entire N<sup>+</sup> substrate (100 to 350 um) which is above the maximum etching thickness that we could obtain by plasma etching. Therefore, we go to electrochemical etching using KOH potassium hydroxide) wet solution. In our studies, we tried different metal layers such as nickel, chrome, copper, gold, titania, silver, and silicon to pattern SiC but these metals started to release before the release of SiC. Due to the high strength of SiC, which supports and necessities high applied voltage, it is not possible to pattern it by electrochemical etching with a common metal and dielectric hard mask layers.

P-type SiC needs higher voltage than n-type SiC to release. Therefore, in our work, we used p-type SiC to pattern n-type SiC by KOH

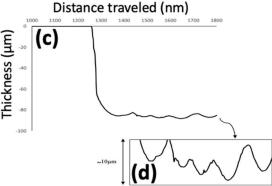

electrochemical etching. To perform this patterning, first, we deposited Ni mask on p-type SiC and pattern it using photoresist and lithography then we perform plasma etching on the SiC p-type layer up to the N<sup>+</sup> substrate. Then electrochemical etching as shown in Fig. 12 was performed. Using electrochemical etching we could obtain at least 80 µm etching thickness.

Fig. 12: Schematized image showing: (a) n-type SiC covered by p-type SiC and AZ9260 photoresist, (b) after patterning the photoresist using lithography UV irradiation, (c) after deposition of 200 nm Ni metal layer, (d) after performing lift-off using acetone and alcohol, (e) after performing plasma etching, (f) after performing electrochemical etching and the p-type SiC act as a stoping layer

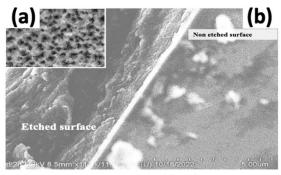

Despite the deep etching thickness that we obtained using electrochemical etching, the electrochemical etched surface has more roughness compared to the plasma etched surface. This different surface-state is due to the porous surface formed on the SiC electrochemical etching process as shown in Fig. 13.

Fig. 13: (a) SEM image of SiC electrochemical etched surface: to the right we have the non-etched surface and to the left we have the etched surface. (b) Inset showed the porous surface of the electrochemical etched part of SiC. (c) Dektak stylus profilometer measurements showing the thickness of the SiC electrochemical etched surface. (d) Inset with the roughness of the electrochemical etched surface.

#### Conclusion

In this paper, a design perimeter for a full-SiC single-chip high-side and low-side dual-MOSFET for ultimate power vertical integration is proposed. The operating modes of the commondrain and common-source three-terminal power chip were validated using 2D Sentaurus<sup>TM</sup> mixedmode simulations. A minimum distance of 12 um is required to minimize the electrical interaction between the two VDMOS sections of the common-drain three-terminal power chip. A 2.5 µm depth for the P+ layer and a 20 µm dielectric thickness is required to prevent any lateral current flow between the two VDMOS sections of the common-source three-terminal power chip. Electrical insulation using a deep trench in the back side and a deep P+ implementation above this trench is introduced. This technological step requires deep etching through the N<sup>+</sup> substrate up to the P<sup>+</sup> layer created in surface. We propose to combine fluorinated ICP/RIE dry plasma and

electrochemical etching to obtain the deep trenches. Higher etching thicknesses can be obtained by electrochemical process but in this case rough etched surfaces are obtained and compatible masks are difficult to found to pattern, excepting using SiC sacrificial p-type layers. The impact of the rough surface should be considered on the electrical insulating and electric field crowding in the MOSFET active area. For this, plasma etching should be also utilized at the process end in order to smooth the rough trenches and the bottom surface.

#### References

- [1]. Z. John Shen, SiC Research Beyond Power MOSFET: What's Next?, IEEE POWER ELECTRONICS MAGAZINE, June 2021

- [2]. P. Diaz Reigosa et al., "Switching Stability Analysis of Paralleled RC-IGBTs With Snapback Effect," in IEEE Transactions on Electron Devices, vol. 68, no. 7, pp. 3429-3434, July 2021, doi: 10.1109/TED.2021.3081614.

- [3]. Converter Integration in Si: Dual-Chip and Ultimate Monolithic Integrations", in IEEE TED, vol. 63, no. 5, pp. 1977-1983, May 2016. doi:10.1109/TED.2016.2537212.

- [4]. A. Lale, et al., "Mixed monolithic-hybrid integration of multiphase power converter: Preliminary evaluation of the 3-chip integration concept", IEEE ESARS-ITEC), Toulouse, 2016, pp. 1-7.

- [5]. X.Li et al., "Series-connection of SiC normally-on JFETs", IEEE ISPSD, 2015. 10.1109/ISPSD.2015.7123429.

- [6]. X. Li et al., "A Novel SiC MOSFET With Embedded Auto-Adjust JFET With Improved Short Circuit Performance", in IEEE Electron Devices Letters, vol. 42, no. 12, pp. 1751-1754, November 2021. 10.1109/LED.2021.3124526.

- [7]. Monolithic SiC Power IC Integrating a Vertical MOSFET with a CMOS Gate Buffer", IEEE ISPSD Conf., 2021. 10.23919/ISPSD50666.2021.9452262.

- [8]. K. Han et al., "Monolithic 4-Terminal 1.2 kV/20 A 4H-SiC Bi-Directional Field Effect Transistor (BiDFET) with Integrated JBS Diodes," IEEE ISPSD conf., Vienna, Austria, 2020, pp. 242-245, doi: 10.1109/ISPSD46842.2020.9170064.

- [9]. J. Huber et al., "Monolithic Bidirectional Power Transistors", IEEE Power Electronics Magazine, vol. 10, no. 1, pp. 28-38, March 2023. 10.1109/MPEL.2023.3234747.

- [10]. B. Baliga et al., "The BiDFET Device and Its Impact on Converters", IEEE Power Electronics Magazine, vol. 10, no. 1, pp. 20-27, March 2023. 10.1109/MPEL.2023.3237059.

- [11]. A. Lale, et al., "Three Multiterminal Silicon Power Chips for an Optimized Monolithic Integration of Switching Cells: Validation on an H-Bridge Inverter," in IEEE Transactions on Electron Devices, vol. 66, no. 12, pp. 5238-5245, Dec. 2019, doi: 10.1109/TED.2019.2946749.

- [12]. A. Lale et al., "Analysis of the three-chip switching cells approach for integrated multiphase power converter combining monolithic and hybrid techniques: Experimental validation on SiC and Si power assembly prototypes," EPE'15 ECCE-Europe, Geneva, Switzerland, 2015, pp. 1-12, doi: 10.1109/EPE.2015.7311711.

- [13]. J. Hasegawa et al., "Simulation-Based Study About the Lifetime and Incident Light Properties Dependence of the Optically Triggered 4H-SiC Thyristors Operation", IEEE Transactions on Electron Devices, 2017, 64 (3), pp.1203-1208. (10.1109/TED.2017.2657223). (hal-01636430)

- [14]. V. Soler, "Design and Process Development towards an Optimal 6.5 kV SiC Power MOSFET", Phd Thesis, Universitat Politècnica De Catalunya Barcelonatech, 2019.

- [15]. M. Lazar et al., "Deep SiC etching with RIE," Superlattices Microstruct., vol. 40, no. 4-6 SPEC. ISS., pp. 388–392, 2006, doi: 10.1016/j.spmi.2006.06.015.

- [16]. M. Lazar et al., "Influence of the masking material and geometry on the 4H-SiC RIE etched surface state," Mater. Sci. Forum, vol. 679–680, pp. 477–480, 2011, doi: 10.4028/www.scientific.net/MSF.679-680.477.

- [17]. T. T. H. Nguyen et al., "Vertical Termination Filled with Adequate Dielectric for SiC Devices in HVDC Applications," Mater. Sci. Forum, vol. 858, pp. 982–985, May 2016, doi: 10.4028/www.scientific.net/MSF.858.982.

[18]. N. Beydoun et al., "Surface engineering for SiC etching with Ni electroplating masks," 2022 International Semiconductor Conference (CAS), Poiana Brasov, Romania, 2022, pp. 119-122, doi: 10.1109/CAS56377.2022.993470.