# Technology Dependence of Stuck Bits and Single-Event Upsets in 110-, 72-, and 63-nm SDRAMs

Daniel Söderström, Lucas Matana Luza, André Martins Pio de Mattos, Thierry Gil, Heikki Kettunen, Kimmo Niskanen, Arto Javanainen, Luigi Dilillo

# ▶ To cite this version:

Daniel Söderström, Lucas Matana Luza, André Martins Pio de Mattos, Thierry Gil, Heikki Kettunen, et al.. Technology Dependence of Stuck Bits and Single-Event Upsets in 110-, 72-, and 63-nm SDRAMs. IEEE Transactions on Nuclear Science, 2023, 70 (8), pp.1861-1869. 10.1109/TNS.2023.3295435 . hal-04192915

HAL Id: hal-04192915

https://hal.science/hal-04192915

Submitted on 31 Aug 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Technology Dependence of Stuck Bits and Single Event Upsets in 110, 72, and 63-nm SDRAMs

Daniel Söderström, *Student Member, IEEE*, Lucas Matana Luza,

André Martins Pio de Mattos, *Student Member, IEEE*, Thierry Gil, *Member, IEEE*,

Heikki Kettunen, *Member, IEEE*, Kimmo Niskanen, *Member, IEEE*,

Arto Javanainen, *Member, IEEE*, and Luigi Dilillo, *Member, IEEE*

#### **Abstract**

Three SDRAMs from the same manufacturer with technology node sizes 110, 72, and 63 nm, were investigated under proton irradiation and using scanning electron microscopy (SEM). The radiation-induced faults were characterized and compared between the different part types. The devices under test (DUT) were irradiated with protons and experienced single event effects (SEE) in the form of stuck bits and single bit upsets (SBU). Analysis of the data retention times of bits which had SBU and were stuck during irradiation, showed similar patterns of retention time degradation, suggesting that the SBUs and stuck bits in all three part types could be induced by the same mechanism. Detailed data retention time analyses were also performed before and after irradiation to investigate the evolution of data retention times after irradiation, and after periods of annealing. The largest radiation-induced retention time losses were found to anneal, but the bits least affected directly after irradiation experienced decreasing data retention time as a function of annealing time. SEM imaging showed differences in the memory cell structure between the tested part types. The largest node size device was the most sensitive to the radiation, both for SEE and cumulative radiation effects.

#### **Index Terms**

Proton Irradiation, Radiation Effects, Retention Time, SDRAM, Single Event Effects, Stuck Bits, Technology Nodes

#### I. INTRODUCTION

SINGLE energetic particles can cause different types of faults in electronic components. In synchronous dynamic random access memories (SDRAM), these radiation-induced single event effects (SEEs) can be, among others, single bit upsets (SBU), single event functional interrupts (SEFI) and stuck bits. Different particles have been shown to cause SEEs in SDRAMs. Neutrons [1, 2], protons [3, 4], electrons [5], and heavy ions [2, 6] can all induce SEE in such memories.

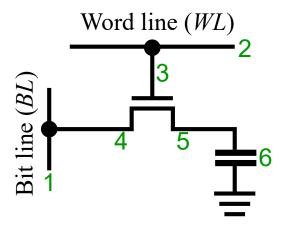

The basic DRAM cell structure is shown in the schematic drawing in Fig. 1. The individual cells are accessed by a word line (WL) and a bit line (BL), where the WL is used to activate an access transistor, which enables the sensing of the charge stored in the cell capacitor through the BL. The cell has two possible states: either have stored charge over a certain threshold limit, or under the limit (i.e. no stored charge). These two states can correspond to either '0' or '1' when written, depending on the programming of the device by the manufacturer.

The way the DRAM cell is constructed, the cell capacitor will discharge over time because of leakage currents in the access transistor, or other leakage paths from for instance material defects. To retain the bit information, the memory needs to be periodically refreshed by rewriting the bit values, so the cells with charge stored in the capacitor will not lose their data between write and read operations of the memory. The amount of time a cell can retain its charge so that it returns the charged state value after being written is known as the data retention time.

Stuck bits are bits that have recurring errors in such a way that the memory cell returns the same data when it is read (corresponding to the discharged cell state), independently of the value which was written to it. The stuck bits are often intermittently stuck [3,5], when the cells are able to operate normally most of the time and fail just sometime. In this case, either the retention time of the cells is very close to the refresh time interval, or the cells show variable retention time [7]. In this work, stuck bits are defined as bits with multiple (more than one) error occurrences,

This study has been supported by the European Union's Horizon 2020 research and innovation program through the Marie Sklodowska-Curie RADSAGA and RADNEXT projects under grant agreements No 721624 and No 10100812. It has also been supported by the European Space Agency through contract 4000124504/18/NL/KML/zk.

D. Söderström, H. Kettunen, K. Niskanen and A. Javanainen are with the University of Jyvaskyla, Department of Physics, Accelerator laboratory, FI-40014 Jyvaskyla, Finland. Contact: daniel.p.soderstrom@jyu.fi.

L. Matana Luza, A. Martins Pio de Mattos, T. Gil, and L. Dilillo are with LIRMM, University of Montpellier, CNRS, Montpellier, France.

A. Javanainen is also with the Department of Electrical and Computer Engineering, Vanderbilt University, Nashville, TN 37235, USA.

The beam time at PSI was provided through the Transnational Access program within the European Union's Horizon 2020 RADNEXT project.

Fig. 1. Schematic view of a DRAM cell, with numbers (green) that will be used for referencing functions of the memory cell later in the paper.

where the bit value has been re-written in between the reads of the bit using the bit refresh rate specified for the test. The SDRAM cells that get stuck after irradiation, have been affected by the radiation so that the data retention capability is reduced, thus the stored charge leaks out between two refresh operations of the memory array. Changes in data retention time of the cells are a useful way to probe the cell damage that has been induced during irradiation [8].

In early studies of stuck bits induced in DRAM and SDRAM, the main discussion of the cause of the faults were towards micro-dose effects [6, 8, 9]. Later studies, and studies on newer devices, have favored a discussion around displacement damage effects from single-particles as the cause of the stuck bits [2, 3, 10, 11]. The generation of defects in the depletion region between the access transistor and the storage capacitor have been identified as particularly important for the creation of stuck bits [10, 11]. Stuck bits can also be induced by cumulative radiation effects, by the accumulation of displacement damage clusters or by the accumulation of TID, until the data retention capabilities are degraded enough to cause the bits to become stuck [3, 5, 12, 13].

New generations of electronic components present different design features compared with their previous generations, along with a steady decrease of topological sizes. In this study, three generations of an SDRAM device from the same manufacturer were studied, with technology node sizes of 110 nm, 72 nm, and 63 nm. These SDRAM parts are described in Section II-A and Table I. The three part types under study were subjected to high-energy proton irradiation to compare each device response to this particle species, complementing the previously conducted studies, where they were tested under atmospheric neutron irradiation as described in [1], and with high-energy electrons, as described in [5]. SBUs and stuck bits were observed and described in both experiments, and in [5] the two fault types were suggested to originate by the same mechanism, due to the similarity in the memory cell retention time degradation for cells that had suffered SBU and those which had been stuck. The same observation was made for different DRAMs studied under neutron irradiation in [14].

This paper goes into greater detail of radiation-induced data retention time changes, and the distributions of data retention time of irradiated memory cells. Specimen of the memories were also opened and studied under a scanning electron microscope (SEM) to determine variations in the cell structure of the different part types, and to relate the memory behavior under irradiation as well as the observed radiation-induced retention-time degradation to varying features between the tested SDRAMs. All the tested memories share the basic features depicted in Fig. 1, but with variations in the implementation.

In the following parts of the paper, DUTs and experimental procedures are introduced in Section II, facilities where the irradiation experiments were conducted are presented in Section III. The test results is presented and discussed in Section IV, where Section IV-A presents memory cell structures of the DUTs, in Section IV-B error cross sections at various energies are shown along with the effects of SEEs on the data retention time of the affected bits, and Section IV-C presents radiation-induced retention-time changes of different bit populations in the DUTs before and after irradiation, as well as after periods of annealing.

TABLE I Samples used in the experiments.

| Part type           | Technology | Node<br>size (nm) | DUT IDs<br>PSI | DUT IDs<br>RADEF |

|---------------------|------------|-------------------|----------------|------------------|

| IS42S16320 <b>B</b> | Planar     | 110               | B1, B2         | -                |

| IS42S86400 <b>B</b> | Planar     | 110               | -              | B3               |

| IS42S16320 <b>D</b> | RCAT       | 72                | D1, D2         | D3               |

| IS42S16320 <b>F</b> | RCAT       | 63                | F1, F2         | F3               |

#### II. TESTED DEVICES AND EXPERIMENTAL PROCEDURE

#### A. Devices under test

The tested components were ISSI 512 Mib SDRAMs of three different generations. They were parts IS42S86320B / IS42S86400B [15] with node size 110 nm, the 72 nm IS42S86320D [16], and the 63 nm IS42S86320F [17]. The 110 nm memory cells were constructed using planar technology, while the 72 nm and 63 nm parts utilize a recessed channel array transistor (RCAT) technology [18] for the access transistors to the cell storage capacitors. Three samples of each part type were tested: two at PSI and one at RADEF, as listed in Table I. The small number of tested DUTs could mask part-to-part variations within the tested part types when comparing them to each other. However, the results and behaviors are consistent to previous tests and experiences (e.g. in [1,5]) and within the tested DUT populations of Table I.

The memory arrays are composed of 512 Mib divided into four banks, and each bank has 8192 rows and 1024 columns of 16 bits for the -320**X** devices, while the -400**B** part has 8192 rows and 2048 columns of 8 bits. Their operating frequency is up to 143 MHz and they use a 3.3 V supply voltage. The memories were packaged in 54-pin TSOP-II plastic packages, which were not opened for the irradiation tests.

The components that were tested at PSI, were mounted on dedicated test boards, each board housing three devices: one sample of each part type. Apart from the devices under test (DUT), the test boards included a System-on-Chip FPGA from Microchip, a SmartFusion2 M2S025, as the main controller unit. These test boards were designed to be used for radiation test evaluation of these components on the ground in accelerator-based testing, as well as in space, where the test board is envisioned to fly in the cubesat mission FloripaSat-2 [19], as the *Harsh Environment CubeSat Payload*.

The components tested at RADEF were controlled by Terasic DE0-CV FPGA development boards, utilizing a different test setup and test methodology than what was used in PSI. At RADEF, one DUT were connected to one controller board at a time.

#### B. Test procedure

1) Tests at PSI: During irradiation, static and dynamic test procedures were utilized. At PSI, a rotating schedule among the three samples (one of each part type) on each test board was used, so that a dynamic test was running on one of the samples at all times, while the other two samples were performing static tests. The term static test is used here, referring to that the DUT under static testing was not actively written and read. The data on the memory was still periodically refreshed during the static mode testing, as was the case for the dynamic mode testing. The dynamically tested memory was in addition constantly read and re-written. The procedure was such that the same pattern (either all '0' or all '1') was first written to the two memories under static test, then a dynamic test was started on the third memory, which consisted of one loop of a March C- test [20], after which the two static test patterns were read back. The procedure is seen in (1). After completion, the test was restarted, but with a different DUT under dynamic testing.

$$S1 \uparrow (w0) \text{ or } \uparrow (w1)$$

$$S2 \uparrow (w0) \text{ or } \uparrow (w1)$$

$$D \uparrow (w0); \uparrow (r0, w1); \uparrow (r1, w0);$$

$$\downarrow (r0, w1); \downarrow (r1, w0); \uparrow (r0);$$

$$S1 \uparrow (r0) \text{ or } \uparrow (r1)$$

$$S2 \uparrow (r0) \text{ or } \uparrow (r1)$$

$$(1)$$

In (1), w signifies a write operation and r a read operation, while '0' and '1' specifies the data patterns all '0' and all '1'. The symbols  $\uparrow$  and  $\downarrow$  indicate the accessing order of the memory addresses, from the lowest address to the

highest, or from the highest address to the lowest, respectively. S1 and S2 marks the two memories used for static testing in the current loop, using patterns alternating between all '0' and all '1', and D represents the memory that was tested dynamically. The full procedure in (1), including the S1 and S2 write and read operations were performed under irradiation. After each completed test loop, the DUTs on the test board operating as S1, S2 and D in (1) was rotated.

All operations in (1) were following each other. To limit the time for one test loop, only the first quarter of the memories bits were used (128 Mib), which resulted in a total time for one test loop as detailed in (1) of about 3 min 30 s.

The operational frequency that was used for the test in PSI was 50 MHz in order to have a stable and controlled communication with the three memories on the board, instead of the maximum frequency of the SDRAMs of 143 MHz. Also the refresh rate of the memory bits was reduced compared to the nominal one. The nominal value is 8192 refresh operations (one per row in the memory) every 64 ms, which corresponds to sending an auto-refresh command at a frequency of 128 kHz. Instead of this value, the auto-refresh command frequency was set to 32 kHz, with a resulting refresh operation at each bit every 256 ms. This was done to increase the radiation sensitivity of the memories to be able to collect a larger number of errors than at the normal refresh rate. At longer times between refresh events, smaller increases in cell leakage currents can cause stuck bits and smaller disturbances on the cell can cause upsets. The number of errors and estimated cross sections are thus not representative for what can be expected in these part types during normal operation, but serves as comparative values between them.

2) Tests at RADEF: The tests at the different irradiation facilities were not done for the results to be directly compared with each other, but rather to elucidate different types of behaviors, where results from the separate tests can reveal differences between the part types.

The goals of the tests at RADEF were to investigate the effects of radiation on the SDRAMs, by monitoring the data retention time of the individual bits of the memories. For this purpose, detailed retention time characterizations were made on a portion of the memories. These characterizations were done by writing a data pattern to the memory, then disabling the automatic data refresh for a time period, after which the data refresh was enabled while the memory was read back to avoid bits losing their charge during the time spent reading the memory portion. A logical checkerboard pattern,  $AA_h$ , was used in this case, and the physical locations of the cells on the dies were unknown. This procedure was then repeated with a different time period with the refresh disabled. Time periods between the nominal refresh time 64 ms and around  $4.3 \cdot 10^3$  s with the memory refresh disabled was used in the characterizations of the devices tested at RADEF.

In the irradiation tests at RADEF, 128 kib of the memories capacity was utilized. With a checkerboard pattern, this corresponds to half of the bits (64 kib) being in their charged state and half in their discharged state. This was verified by observing the bleed-down pattern, i.e. the read data pattern as all bits approaches their discharged state. To be able to still collect error events during irradiation with this small memory size, an auto-refresh command frequency of 1024 Hz was used, corresponding to a time of 8 s in between data refresh events in each bit. No errors were present in the tested 128 kib memory of the pristine DUTs at this refresh frequency.

During irradiation, the DUTs were written with a checkerboard pattern,  $AA_h$ , then a read operation was performed and followed by a new write operation, every minute during the full irradiation period. This procedure is described in (2), with the same nomenclature as in (1), with  $t_{wait} = 60$  s, and the operations within brackets repeated.

$$\uparrow (wAA); \{ \text{wait } t_{wait}; \uparrow (rAA, wAA) \}$$

(2)

The wait time of one minute between the read/write operations of the memory was chosen to have multiple periods of normal data refresh operations (at every 8 s in each bit) in between rewriting the data in the DUTs.

#### III. IRRADIATION TEST FACILITIES

# A. PIF

The irradiation tests performed at the Proton Irradiation Facility (PIF) at the Paul Scherrer Institute (PSI) in Switzerland used proton energies of 70, 151, and 230 MeV. The primary proton energy from the PROSCAN cyclotron at PSI was 230 MeV for all three cases, and to reach the lower energies, copper plates were introduced in the beam path to reduce the energy of the protons. Proton fluxes of about  $3\cdot10^7$  to  $8\cdot10^7$  p/cm²/s were used, and all tests were performed in ambient room temperature and air pressure.

The beam homogeneity was checked for each energy setting by moving a small scintillator within the beam area, which was also used to calibrate in-beam ionization chambers used for flux monitoring during the irradiation runs. The reported proton fluence on the DUTs is estimated to have an uncertainty of less than 10 %.

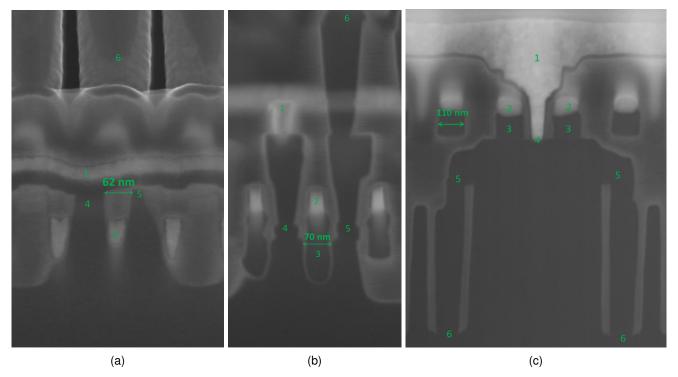

Fig. 2. Cross-sectional microscopic images of the memory cells of SDRAM type F (a), type D (b), and type B (c). The numbers in the images refers to the different parts of the cell as shown in Fig. 1.

#### B. RADEF

The Radiation Effects Facility (RADEF) at the University of Jyväskylä in Finland was used for irradiation with 52 MeV protons, which was the energy of the primary proton beam at the target station in air. A proton flux of about 1·10<sup>8</sup> p/cm<sup>2</sup>/s was used for the tests at RADEF.

An in-beam ionization chamber calibrated against a Si detector at the DUT position was used to monitor the proton flux during the irradiation tests, and a fluence uncertainty of less than 10 % is assumed.

#### IV. RESULTS AND DISCUSSION

## A. Cell imaging study

Samples of the three part types were opened, and imaged with SEM. Cross-sectional views of the memory cells are shown in Fig. 2, with the scale of the image marked in one of the visible structures in each image. In the images, the numbers 1 to 6 marks structures corresponding to the same numbers in the schematic view seen in Fig. 1.

The devices with the smallest feature sizes are shown in Fig. 2a and Fig. 2b, depicting the memory cells of part types F and D, respectively. These memories utilize the RCAT technology for the access transistor, where the gate of the access transistor is marked with number 3 in the images. Due to the RCAT structure of the access transistor, the channel forming under the gate is curved, and the effective channel length of the transistor is longer than the horizontal dimension of the gate.

Part type B has a cell structure as shown in Fig. 2c, built on planar technology. The access transistor gate (3), controlled with a bias level on the word line (2), opens a straight channel connecting the stored charge in the cell (5-6) to the bit line contact (4-1). The storage capacitors for part type B are buried in the bulk of the device, below the access transistors and the word and bit lines, while for part types D and F, the capacitors are tubes that instead are located above.

#### B. Fault modes and cross sections, PSI

During proton irradiation, SBUs and stuck bits were observed, where the stuck bits are bits with more than one detected error where the DUT has been rewritten in between, and the SBUs are bits with one occurrence of a faulty reading of the data in it. Errors coming from block errors or SEFIs were not included here and not part of this study. An example of how the number of bits with detected errors evolve during irradiation as a function of proton fluence

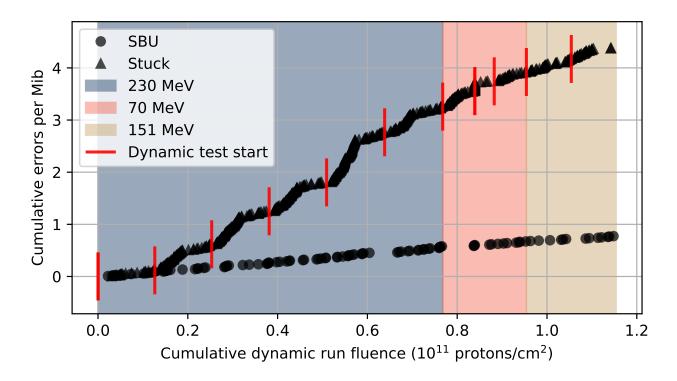

Fig. 3. Example of the error trends found in one DUT during dynamic testing. The figure shows the cumulative number of stuck bits and SBUs in DUT B2 over the fluence of protons with energies 230, 70, and 151 MeV during dynamic testing.

during tests with dynamic mode is shown in Fig. 3, where the results for one tested part type B device (DUT B2 using the IDs from Table I) are shown. In the figure, only the proton fluence and errors during dynamic mode is considered, and as discussed in Section II-B1, static tests were performed interleaved with the dynamic tests. This results in an increase of stuck bits in the beginning of the dynamic cycle marked with red vertical lines, since the stuck bits induced during the static runs were observed in the first reads of the DUT in the dynamic test cycle.

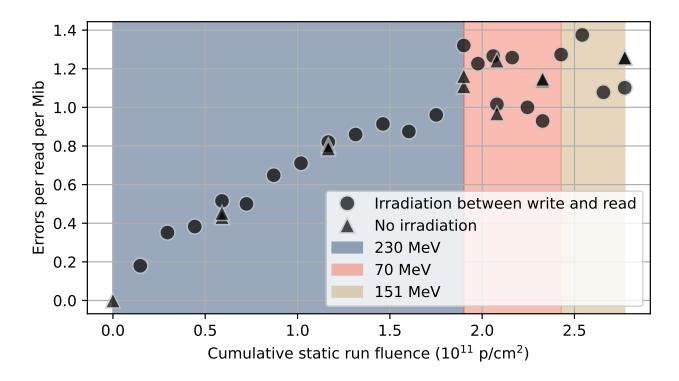

The errors found during static mode tests for the same DUT (B2) are presented in Fig. 4. Here the total amount of errors per read of the memory is presented as a function of the accumulated fluence during the static mode tests. The number of errors is thus the sum of stuck bits and SBUs, and the increasing trend of errors in this figure is due to accumulating stuck bits in the memory over the test duration. Write and read operations were performed also between irradiation runs in the DUTs, with the beam off, by writing and reading back patterns of all '0' and all '1' in the DUTs. The returned errors during these operations are presented with a different symbol in Fig. 4. Since there was no beam on the DUT in these cases, the recorded errors are only caused by stuck bits.

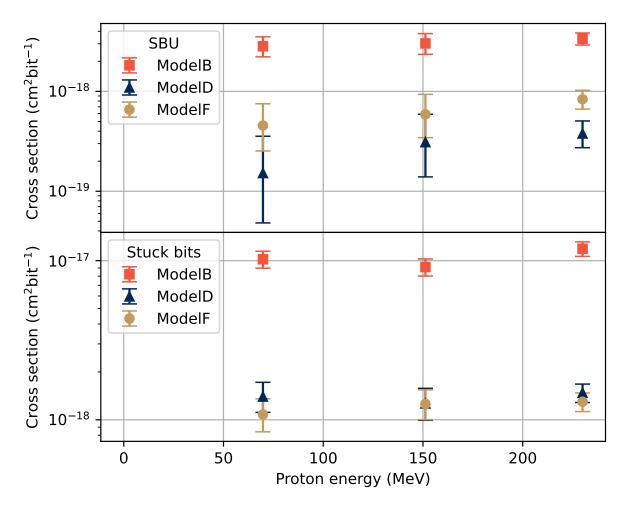

In Figs. 3 and 4, regions of fluence with protons of energies 230 MeV, 70 MeV, and 151 MeV are marked. The spread of number of errors increases in Fig. 4 much due to annealing of radiation damage, ISBs being in stuck and non-stuck states, and varying run fluence resulting in a varying number of SBUs. Cross sections separated in stuck bits and SBUs for the tested energies are presented in Fig. 5. Part types D and F have similar cross sections to each other, while type B has a larger error cross section than the other part types. The stuck bit cross sections are larger than the SBU cross sections for all memories. Fig. 3 shows this trend for DUT B2. Part B is the oldest device with the largest technology node size, and a larger cell area might translate to a larger sensitive area where a proton strike is able to generate an SEE in the memory cell [21].

As depicted in Fig. 2, a design change of the memory cells took place comparing part type B with D and F, going from a planar cell architecture to an RCAT structure of the access transistor. This resulted in a drop of SEE bit cross section of close to 10 times for stuck bits, and 5-10 times for SBUs. The vertical structures of the cells are also very different between part types B and D, so the generated secondaries by the proton radiation traversing the region of the access transistor and the storage capacitor (area 5 in Fig. 2) might differ considerably. This will affect the likelihood of creating defects and damage clusters in the area, and thus leakage paths for the stored charge of the

Fig. 4. Errors in a DUT during static testing. The figure shows the number of errors in DUT B2 during each static read, as a function of the acquired fluence of protons with energies 230, 70, and 151 MeV during the static tests of the DUT.

cells to dissipate through.

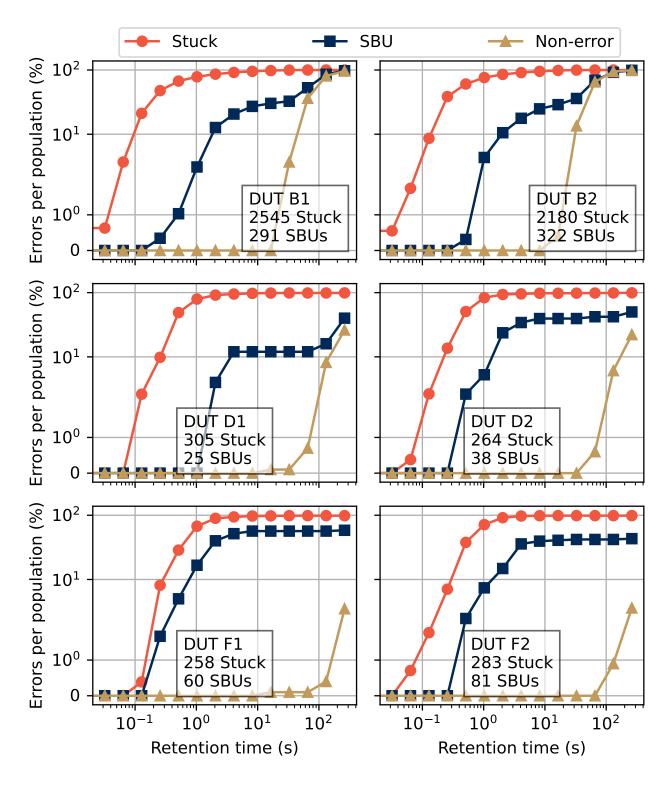

The bits in the memories which exhibited errors during the irradiation (stuck bits and bits with SBU), were investigated in terms of their retention time and compared with populations of bits with no observed errors. The portion of each tested bit population failing at varying wait times between write and read operations with data refresh disabled is shown in Figure 6 for the DUTs irradiated at PSI. The shown characterization was performed nine months after the irradiation, with the non-error population size fixed to 1000 bits chosen at random in the full memory space of the DUTs. The sizes of the other populations are specified in the inset boxes of the figure frames.

The characterization was conducted by writing the targeted memory bits with a pattern of all '0', then waiting a period of time before reading the memory portion back. This was then repeated with a pattern of all '1'. The waiting time is marked as the retention time in Fig. 6.

The figure shows that the populations of stuck bits have the worst retention time capability and fail considerably faster than the bits which had not experienced any error during irradiation. The populations of bits with SBUs also have retention time distributions shifted to lower times, but not as far as the stuck bit populations.

The most noticeable difference between the three tested part types, is the larger part of the non-error populations failing for part type B, compared with D and F. This is further shown and discussed in the following Section IV-C.

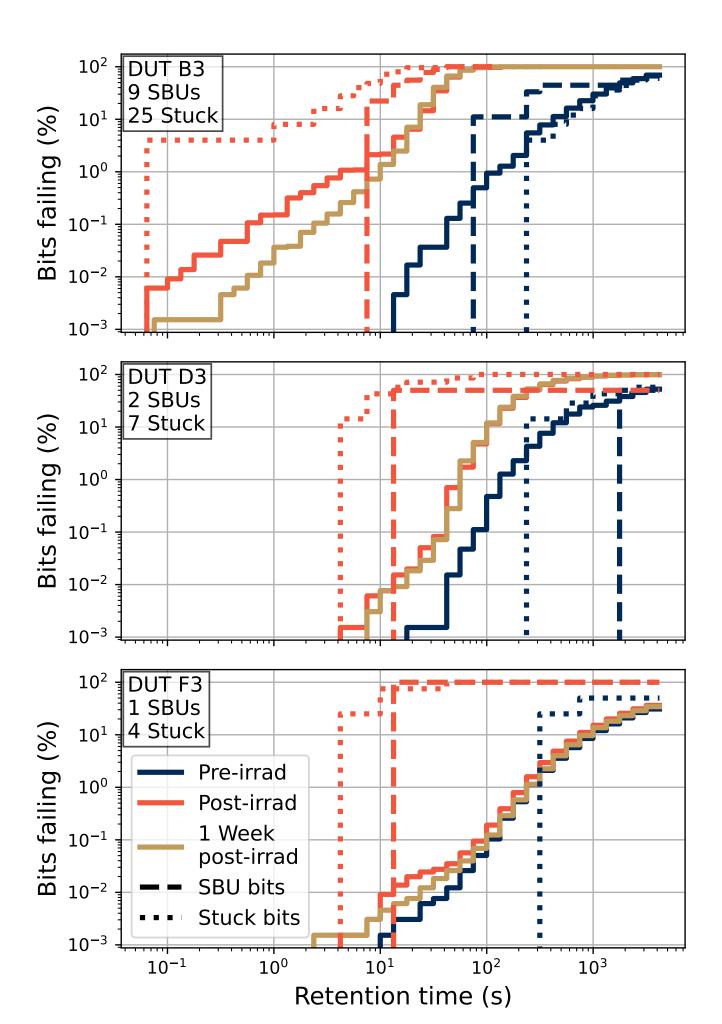

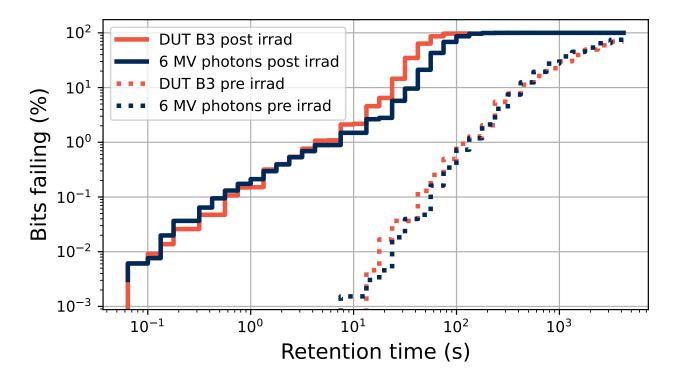

#### C. Retention time distributions, RADEF

A detailed characterization of the memory bits retention times was performed in a small portion of one sample of each part type. This was done before and after the irradiation tests, as described in Section II-B2. A memory portion corresponding to 64 kib of the memory capacity in the charged state was utilized. For the purpose of investigating the data retention time, only the charged state is of interest since bits written to the discharged state will always return the discharged value (without outside stimuli). Data retention times ranging from the nominal refresh frequency at 64 ms up to around  $4.3 \times 10^3$  s were investigated.

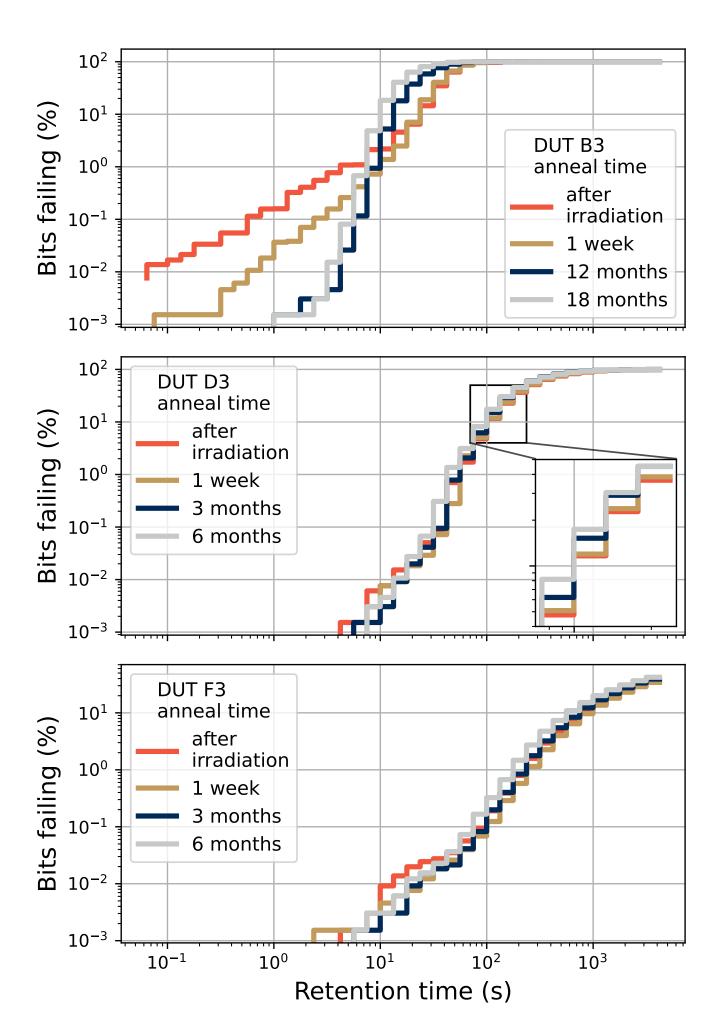

The degradation of the data retention capability of the memories due to radiation is shown in Fig. 7. In the figure, also the annealing of the radiation damage one week after irradiation is shown. The annealing was done in room temperature without any electrical connections attached to the memories apart from when it was actively

Fig. 5. Error cross sections for SBUs (top) and stuck bits (bottom) for the different memory parts, for the tested 128 Mib using a data refresh interval of 256 ms, thus larger cross sections than what can be expected for nominal operation using a 64 ms refresh interval. The events observed during static and dynamic tests have been combined in the figures, as well as the results from DUTs B1 and B2, D1 and D2, and F1 and F2.

characterized. The retention time distribution of the bits one week after irradiation is shown in Fig. 7 with golden colored lines. After one week of annealing, DUTs D3 and F3 do not show much difference compared to immediately after irradiation, while DUT B3 which suffered larger radiation-induced retention time losses show a larger degree of recovery.

Further annealing steps are displayed in Figure 8. The type B SDRAM which showed the largest degree of radiation damage also shows a larger degree of retention time change after irradiation of the tested bit population. As the time of annealing increases, the most damaged cells with the shortest data retention time after irradiation gets longer retention times with several orders of magnitude. In the figure is also seen that the distribution shifts to a more vertical orientation, as the bits with longer retention times gets decreased data retention capabilities as the annealing time increases. A similar behavior was seen for the same part type in [5] and for different parts in [2]. This behavior could be caused by the slow migration of trapped charges within the insulating oxides over time, eventually reaching interface states where they negatively effect the cell performances. Another possibility is interface states and defects evolving to configurations associated with larger cell leakage currents. Theseannealing characteristics, and the global shift of the full population of bits to shorter retention times in Fig. 7 suggest a strong effect of total ionizing dose (TID) on the observed retention times for the bits is DUTs B3 and D3 after irradiation.

Fig. 6. Retention time distributions of three populations in the DUTs tested at PSI. The populations are: bits that were stuck during irradiation, bits with SBU, and a population of 1000 random bits without observed errors (Non-error distribution).

The annealing effects of part types D and F DUTs were not as large as was seen for DUT B3. The same trends can however not be excluded, with the slight decrease of data retention time magnified in the inset of Fig. 8 for DUT D3 at longer annealing times, and small retention time increases of the bits with the shortest retention times after irradiation.

The retention time distribution curves reveal a larger collective loss of data retention capability after irradiation for DUT B3 than D3, and for D3 than F3. Looking at Fig. 2c, there is a large insulation structure present from the access transistor (3), down to the storage capacitor (5-6), isolating adjacent cells from each other. Charged particles passing through this structure can induce electron-hole pairs which might not recombine in the presence of electromagnetic fields generated from biases on close WLs or BLs resulting in charges trapped in the oxide and in interface states, as well as cause higher densities of defects and interface states by the Si-oxide interfaces.

The layout of SDRAM part types D and F differ from B, as seen in Fig. 2. Around the WL contacts and on the path around the access transistor, there is a thicker insulator layer present in part type D than in F, as well as by the access transistor gate. Accumulation of charges in and on the surface of insulators like these could be the cause for the larger collective loss of retention time seen for DUT D3 than F3 in Fig. 7. There the whole population of bits have shifted noticeably to lower retention times after irradiation for DUT D3, but the retention times of F3 are fairly similar for times over 10<sup>2</sup> s before and after irradiation.

The dashed and dotted lines in Fig. 7 represent the cumulative distributions of retention times of the population of bits that had SBUs, and bits that became stuck from SEE during irradiation. The distributions are shown for these bits before and after irradiation in blue and orange respectively, and the number of SBUs and stuck bits observed as SEE during irradiation is shown in the figure insets for each DUT. Only few SEEs were observed due to the small portion of the memory that was considered, so each failing bit in the SBU and stuck bit populations cause a large jump of the dashed lines in Fig. 7.

A time of 8 s between refresh events of each bit was used in the DUTs under irradiation. In Fig. 7 it is seen that the bits which suffered SBUs (one single non-recurring error in the bit) have retention times after the irradiation only slightly larger than the time interval between refresh events during the irradiation test, while the stuck bits have data retention times reaching shorter times than the refresh time interval.

From the nature of the error modes, the expected behavior of the stuck bits would be exactly this, that they have shorter data retention times than the time between the data is refreshed, and the stored charges on the cell capacitor leak out between refresh events. The stuck bits can however anneal over time, and are often intermittently stuck with potential retention-time variations [4, 5, 7], thus the full population of observed stuck bits would not be expected to necessarily have retention times shorter than the refresh time interval.

Regarding the SBU bit populations, there is also here a shift towards shorter retention times after irradiation compared with before. This is most notably present for samples D3 and F3, where in e.g. F3 the only bit which had an SBU was not failing during the tested wait times of up to 4.3·10³ s before irradiation. The large decreases of retention time for SBU bits observed here as well as in Fig. 6 point towards that stuck bits and SBUs in these types of memories are likely affected by the same radiation interaction mechanisms, causing a similar type of long-term retention-time degradation.

An exception is found for the case of DUT B3, where only one of the two observed SBUs is failing in the retention time characterizations made for Fig. 7. This is due to that the SBU bit not showing up is an error where the bit was written to the discharged state, and the read returned the state corresponding to a charge stored in the cell capacitor. All other observed SBUs have been from cells written to the charged state and returning a value corresponding to a discharged state, which is the case also for all observed stuck bits, as would be expected. The SEE mechanism causing the cell to return a value corresponding to a charged state is different from the opposite case. An example of what could cause this type of upset would be for instance a particle strike in the region of the BL or the memory cell in question, occurring at the time of reading the bit value. This could induce a charge pulse on the BL so it would be interpreted as the bit being in the charged state by the sensing node [22].

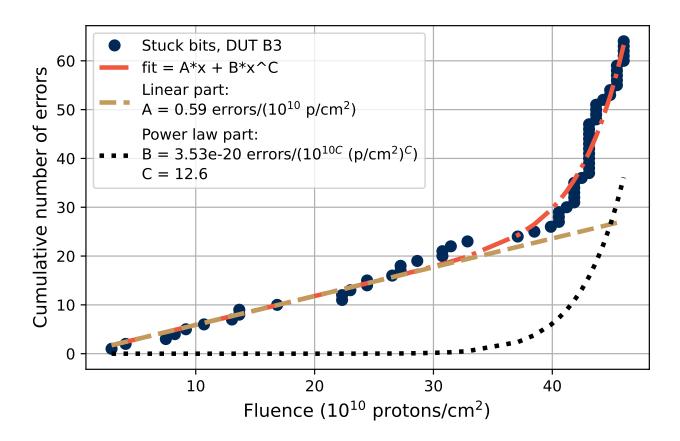

During the tests at PSI, the observed events were originating from SEE with linear error trends as a function of fluence, as was the observed errors during irradiation at RADEF for DUTs D3 and F3. In the case of DUT B3, many bits were becoming stuck due to cumulative radiation effects towards the end of the irradiation, due to the long refresh time interval used during the tests. The accumulation of stuck bits in B3 follows a power law as a function of proton fluence at large deposited doses to account for the multiple particle interactions which caused these bits to be stuck [3, 5]. This is shown in Fig. 9, where the linear part of the figure represent the stuck bits induced by single protons, and which are used for creating the retention time distributions of SBU bits and stuck bits in Fig. 7 for DUT B3. The stuck bits induced by cumulative radiation effects follow the power-law part of the fit. The large amount of total stuck bits at the end of irradiation can also be seen from Fig. 7, where around 1% of the bit population have

Fig. 9. Cumulative number of stuck bits as a function of proton fluence observed in DUT B3 during irradiation at RADEF. The number of accumulated stuck bits was fitted to a function  $A \cdot fluence[10^{10} \text{p/cm}^2] + B \cdot fluence[10^{10} \text{p/cm}^2]^C$ , where A, B and C are fitted constants.

shorter retention times than the used refresh time interval of 8 s. The limit between the SEE and cumulative parts was set as 3.9·10<sup>11</sup> protons/cm<sup>2</sup>.

The fitted power in Fig. 9 for the generation of stuck bits denoted by *C* is 12.6. According to Poisson statistics, this is the number of protons on a bit required for it to get stuck (with a note that this parameter is sensitive to the fitting procedure and can there vary a few numbers up or down). The cumulative radiation damage is attributed to mainly originate from the accumulation of TID, thus the dose deposition events of on average around 13 protons in a bit in this DUT causes the bit to become stuck. These events can be ranging from the deposition of dose based on the stopping power of the primary protons, to larger dose depositions from heavier recoil particles. A power-law trend of stuck bit generation was observed also under photon irradiation in [5], where very little displacement damage occurs compared to under the proton beam. The same shape of radiation-induced retention-time degradation as shown in Fig. 7 for DUT B3 was also observed for another DUT of part type B after a similar level of TID under a 6 MV photon beam, further confirming the origin of the observed cumulative radiation effects to be caused by TID. The comparison of the retention time distributions of DUTs of part type B irradiated by photons and protons is shown in Fig. 10, with further descriptions of the 6 MV photon beam found in [5]. The power-law increase of errors was in [5] attributed to the accumulation of smaller damage clusters potentially induced by displacement damage effects, but the similar retention-time degradation between photon and proton irradiated DUTs suggest that the retention-time shift and power-law increase of errors are caused instead by TID accumulation.

Connecting to previous studies on the subject of stuck bits and radiation-induced retention-time changes, two separate mechanisms for the observed SEE and cumulative effects are suitable to explain the observed effects in this study. The cumulative radiation effects primarily by TID deposition causing retention-time degradation and eventually stuck bits, are likely due to the generation of charges in the insulators, and of interface states and defects as discussed in e.g. [7]. The single event effects on the other hand are likely induced by single particle displacement

Fig. 10. Retention-time distributions before and after irradiation of DUT B3 by 52 MeV protons and of a different DUT of part type B by a 6 MV photon beam.

damage clusters in the depletion region by the access transistor contact to the storage capacitor as have been discussed in e.g. [3, 4, 7, 11]. The observed SBUs caused as well large retention-time decreases in the affected bits, suggesting that they have been affected by particle impacts similar to those causing the observed stuck bits. The same type of particle interactions and mechanism might thus be the cause of the SBUs as of the stuck bits as also discussed in [5, 14].

## V. CONCLUSION

Three generations of SDRAMs from one manufacturer were studied under high-energy proton beams, where SEUs and stuck bits were observed, and the error cross sections were compared between the different part types. The different memories were opened and imaged using SEM to study the memory cell structures. It was found that the memory cells with the planar structure and largest node size were more sensitive to SEE than the ones with smaller node sizes and RCAT structure in the study.

The SEEs observed in the tested memories did not occur in bits which were the weakest in terms of the measured data retention time before irradiation. However, there is a shift of data retention capability towards shorter retention times for bits which experienced either SBU or were stuck.

Both observed SEE failure modes, SBU and stuck bits, could be caused by the same mechanism induced by single high-energy protons. This was found due to the similar loss of data retention time observed in bits which experienced SBU and that were stuck. The bits which were stuck were found to have a larger loss of retention time than the SBU bits, pointing towards that the SBU in these SDRAMs are less severe versions of stuck bits. An exception of this is the case was an SBU observed in DUT D3, where the returned value from the bit corresponded to a charged state, even though it was written to the discharged state. All other observed errors corresponded to bits returning values corresponding to the discharged state after being written to their charged states.

The cumulative radiation effects causing retention time losses in the tested SDRAMs were found to be originating from the deposition of TID, and seem to be closely related to the oxide present around the access transistor and stored charge in the memory cells. The three tested part types showed a different response in the amount of retention time lost for the whole tested bit population, where the part type with the least oxide present close to the access transistor was the least affected.

#### REFERENCES

- [1] L. Matana Luza et al., "Technology impact on neutron-induced effects in SDRAMs: A comparative study," in DTIS 2021: Proceedings of the 16th IEEE International Conference on Design and Technology of Integrated Systems in Nanoscale Era, Montpellier, France, Jun. 2021, pp. 1–6, doi: 10.1109/DTIS53253.2021.9505143.

- [2] J. P. David et al., "Light particle-induced single event degradation in SDRAMs," IEEE Trans. Nucl. Sci., vol. 53, no. 6, pp. 3544–3549, Dec. 2006, doi: 10.1109/TNS.2006.886210.

- [3] A. M. Chugg *et al.*, "The random telegraph signal behavior of intermittently stuck bits in SDRAMs," *IEEE Trans. Nucl. Sci.*, vol. 56, no. 6, pp. 3057–3064, Dec. 2009, doi: 10.1109/TNS.2009.2032184.

- [4] ——, "Probing the nature of intermittently stuck bits in dynamic RAM cells," IEEE Trans. Nucl. Sci., vol. 57, no. 6, pp. 3190–3198, Dec. 2010, doi: 10.1109/TNS.2010.2084103.

- [5] D. Söderström et al., "Electron-induced upsets and stuck bits in SDRAMs in the Jovian environment," IEEE Trans. Nucl. Sci., vol. 68, no. 5, pp. 716–723, May 2021, doi: 10.1109/TNS.2021.3068186.

- [6] L. D. Edmonds et al., "Ion-induced stuck bits in 1T/1C SDRAM cells," IEEE Trans. Nucl. Sci., vol. 48, no. 6, pp. 1925–1930, Dec. 2001, doi: 10.1109/23.983152.

- [7] V. Goiffon et al., "Radiation induced variable retention time in dynamic random access memories," *IEEE Trans. Nucl. Sci.*, vol. 67, no. 1, pp. 234–244, Jan. 2020, doi: 10.1109/TNS.2019.2956293.

- [8] L. Scheick et al., "Analysis of radiation effects on individual DRAM cells," IEEE Trans. Nucl. Sci., vol. 47, no. 6, pp. 2534–2538, Dec. 2000, doi: 10.1109/23.903804.

- [9] G. M. Swift et al., "A new class of single event hard errors," IEEE Trans. Nucl. Sci., vol. 41, no. 6, pp. 2043–2048, Dec. 1994, doi: 10.1109/23.340540.

- [10] H. Shindou et al., "Bulk damage caused by single protons in SDRAMs," IEEE Trans. Nucl. Sci., vol. 50, no. 6, pp. 1839–1845, Dec. 2003, doi: 10.1109/TNS.2003.820727.

- [11] L. D. Edmonds and L. Z. Scheick, "Physical mechanisms of ion-induced stuck bits in the hyundai 16M x 4 SDRAM," IEEE Trans. Nucl. Sci., vol. 55, no. 6, pp. 3265–3271, Dec. 2008, doi: 10.1109/TNS.2008.2006902.

- [12] M. Herrmann, K. Grürmann, F. Gliem, H. Schmidt, and V. Ferlet-Cavrois, "In-situ TID test of 4-Gbit DDR3 SDRAM devices," in 2013 IEEE Radiation Effects Data Workshop REDW, San Francisco, CA, USA, Jul. 2013, pp. 1–7, doi: 10.1109/REDW.2013.6658199.

- [13] M. Hamrbar and S. M. Guertin, "In-situ TID test of 4-Gbit DDR3 SDRAM devices," in 2016 IEEE Radiation Effects Data Workshop (REDW), Portland, OR, USA, Jul. 2016, pp. 199–204, doi: 10.1109/NSREC.2016.7891750.

- [14] L. Matana Luza et al., "Neutron-induced effects on a self-refresh DRAM," Microelectronics Reliability, vol. 128, p. 114406, 2022, doi: 10. 1016/j.microrel.2021.114406.

- [15] ISSI, IS42S86400B, IS42S16320B, IS45S16320B 64M x 8, 32M x 16, 512Mb SYNCHRONOUS DRAM, Rev. H, Integrated Silicon Solution, Inc., Dec. 2011, accessed on: March 2, 2023. [Online]. Available: http://www.issi.com/WW/pdf/42S16320B-86400B.pdf

- [16] —, IS42/45R86400D/16320D/32160D IS42/45S86400D/16320D/32160D 16Mx32, 32Mx16, 64Mx8 512Mb SDRAM, Rev. B, Integrated Silicon Solution, Inc., May 2015, accessed on: March 2, 2023. [Online]. Available: http://www.issi.com/WW/pdf/42-45R-S\_86400D-16320D-32160D.pdf

- [17] ——, IS42R86400F/16320F, IS45R86400F/16320F, IS42S86400F/16320F, IS45S86400F/16320F 32Mx16, 64Mx8 512Mb SDRAM, Rev. B1, Integrated Silicon Solution, Inc., Jul. 2017, accessed on: March 2, 2023. [Online]. Available: http://www.issi.com/WW/pdf/42-45R-S\_86400F-16320F.pdf

- [18] J. Y. Kim et al., "The breakthrough in data retention time of DRAM using Recess-Channel-Array Transistor (RCAT) for 88nm feature size and beyond," in 2003 Symposium on VLSI Technology, Kyoto, Japan, Jun. 2003, pp. 11–12, doi: 10.1109/VLSIT.2003.1221061.

- [19] SpaceLab, FloripaSat-2 Documentation, Space Technology Research Laboratory, march 2021, accessed on: January 19, 2022. [Online]. Available: https://github.com/spacelab-ufsc/floripasat2-doc

- [20] L. Dilillo et al., "Soft errors in commercial off-the-shelf static random access memories," Semiconductor Science and Technology, vol. 32, no. 1, p. 013006, dec 2016, doi: 10.1088/1361-6641/32/1/013006.

- [21] C. Slayman, "Soft error trends and mitigation techniques in memory devices," in 2011 Proceedings Annual Reliability and Maintainability Symposium, no. 2011RM0248, 2011, doi: 10.1109/RAMS.2011.5754515.

- [22] P. E. Dodd and L. W. Massengill, "Basic mechanisms and modeling of single-event upset in digital microelectronics," IEEE Trans. Nucl. Sci., vol. 50, no. 3, pp. 583–602, Jun. 2003, doi: 10.1109/TNS.2003.813129.