# A G-band Packaged Amplified Noise Source using SiGe BiCMOS 55 nm Technology

Victor Fiorese, Joao Carlos Azevedo Goncalves, Simon Bouvot, Sylvie Lepilliet, Daniel Gloria, Guillaume Ducournau, Christophe Gaquière, Emmanuel Dubois

# ▶ To cite this version:

Victor Fiorese, Joao Carlos Azevedo Goncalves, Simon Bouvot, Sylvie Lepilliet, Daniel Gloria, et al.. A G-band Packaged Amplified Noise Source using SiGe BiCMOS 55 nm Technology. IEEE Transactions on Microwave Theory and Techniques, 2024, 72 (3), pp.1775 - 1789. 10.1109/TMTT.2023.3311476. hal-04192337v2

# HAL Id: hal-04192337 https://hal.science/hal-04192337v2

Submitted on 28 Aug 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A G-Band Packaged Amplified Noise Source Using SiGe BiCMOS 55-nm Technology

Victor Fiorese<sup>®</sup>, João Carlos Azevedo Gonçalves<sup>®</sup>, Simon Bouvot<sup>®</sup>, Sylvie Lépilliet, Daniel Gloria<sup>®</sup>, Guillaume Ducournau<sup>®</sup>, Christophe Gaquière<sup>®</sup>, and Emmanuel Dubois<sup>®</sup>, *Member, IEEE*

Abstract—This article introduces the first B iCMOS SiGe technology-based packaged noise source (NS) operating in the G-band (140-220 GHz). An amplified p -n j unction d iode has been packaged and biased in avalanche mode to generate excess noise ratios (ENRs<sub>av</sub>) of approximately 25 dB between 140 and 170 GHz at package output for an unbiased low state and a high state corresponding to a 20-mA cathode current. The two-stage amplifier is a cascode cell composed of two BiCMOS 55-nm NPN very high speed (NPNVHS) transistors with an emitter length and a width of 5.56 and 0.2  $\mu$ m, respectively. An optimal biasing results in a 8.2-mA current consumption for one cascode stage and an overall available power gain  $(G_{av})$  better than 12 dB between 140 and 180 GHz. This supports operation in a low state, where the diode is unbiased and the amplifier is biased, which constitutes a scheme that easily validates the minimum detectable signal (MDS) condition while exhibiting a 14-dB ENR<sub>av</sub> level in the beginning of G-band compared to this polarized low state. This NS shows a monitorable  $P_{\text{COLD}}$  and is adaptable to several noise receivers. In addition, the ENR<sub>av</sub> level flatness is better than 3 dB over the entire frequency range, and the impedance matching, better than -7.5 dB at package output, is not dependent on the NS bias condition. Noise figure (NF) extraction of a WR05-connectorized III-V amplifier [MPA04-1 from Virginia Diodes, Inc. (VDI)] was performed and compared to the ELVA ISSN-05 commercial NS measurement, showing low discrepancy. The same study was performed on-wafer for an NPNVHS transistor on BiCMOS 55-nm technology, showing a maximum discrepancy of 0.8 dB between the two measured NFs. The NF measurement accuracy of the MPA04-1 amplifier was

This work was supported in part by the STMicroelectronics-Institute of Electronics, Microelectronics, and Nanotechnologies (IEMN) Joint Laboratory; in part by the French Government through the National Research Agency (ANR) under Program PIA EQUIPEX LEAF ANR-11-EQPX-0025; and in part by the French RENATECH Network on Micro and Nanotechnologies. (Corresponding author: Victor Fiorese.)

Victor Fiorese is with STMicroelectronics, 38019 Grenoble, France (e-mail: victor.fiorese1@st.com).

João Carlos Azevedo Gonçalves, Simon Bouvot, and Daniel Gloria are with STMicroelectronics, 38920 Crolles, France (e-mail: joao.azevedogoncalves1@st.com; simon.bouvot@st.com; daniel.gloria@st.com).

Sylvie Lépilliet, Guillaume Ducournau, and Christophe Gaquière are with the CNRS, Centrale Lille, Université Polytechnique Hauts de France, UMR 8520—Institut d'Electronique de Microélectronique et de Nanotechnologie (IEMN), Université de Lille, 59000 Lille, France (e-mail: sylvie.lepilliet@univ-lille.fr; guillaume.ducournau@univ-lille.fr; christophe.gaquiere@univ-lille.fr).

Emmanuel Dubois is with the CNRS, Centrale Lille, Université Polytechnique Hauts de France, JUNIA, UMR 8520—Institut d'Electronique de Microélectronique et de Nanotechnologie (IEMN), Université de Lille, 59000 Lille, France (e-mail: emmanuel.dubois@univ-lille.fr).

Article are available at https://doi.org/10.1109/TMTT.2023.3311476.

assessed up to 220 GHz, by varying the chosen high state while keeping the low state completely unbiased. A maximum 0.5-dB variation over 12 obtained NF values is observed up to 200 GHz.

*Index Terms*—ENR<sub>av</sub>, *G*-band, NF50, organic substrate, SiGe BiCMOS 55 nm, split block, tunable low state.

#### I. INTRODUCTION

RECENT years show great interest in the *D*- and *G*-band noise sources (NSs) development to address applications, such as remote sensing instruments based on millimeter-wave (mmW) radiometers used for meteorological forecasting [1], [2], [3], [4], [5] and 6G perspectives. Remote sensors including low-Earth orbit (LEO) remote imagers and sounders and geostationary (GEO) atmospheric sounders need high degree of sensitivity. These systems rely on fundamental building blocks, such as frequency mixers [6], [7], power detectors, low noise amplifier (LNA), switch [8], coupler [9], and NSs [10]. From another use case perspective, upcoming mobile communication networks will have to support applications ranging from immersive reality to haptic sensing and actuation without neglecting the real-time, ultralow latency and reliability requirements for mission critical communications involving, e.g., vehicle traffic control, automated critical process management, assisted, and remote surgery [11]. Beyond the current commercial deployment of 5G, this implies that 6G is bound to continue its relentless expansion into the 100-300-GHz bands, where the aforementioned satellite exploration and radio astronomy applications have already spread at specific frequencies. Obviously, the success of 6G is intimately tied to the performance of transistors and circuits to meet the requirements in terms of frequency rise, available gain, output power, and noise figure (NF) needed to compensate for higher path losses in the millimeter wavebands [12]. From that perspective, recently developed heterojunction bipolar transistors (HBTs) have already demonstrated operating frequencies of 505/720 GHz for  $f_T/f_{\rm max}$  [13], and current developments at STMicroelectronics are targeting 400/600 GHz leveraging a SiGe BiCMOS 55-nm technology [14], compatible with industrial 300-mm fabrication lines. To lay the groundwork for 6G development, constant, monitorable, and compact NSs in the frequency bands covering the 100-300-GHz interval are therefore essential to enable silicon devices and circuits noise characterization and modeling in that frequency range. Several published contributions demonstrated noise generation with solid-state NS using diodes biased in avalanche

regime [15], [16], [17], [18], [19], while others show promising performance when using BiCMOS amplifiers [20]. An accurate and comprehensive state-of-the art of mmW, submmW, and THz NS is proposed in [2]. Commercially available NSs are mainly based on IMPATT diodes biased under 28 V exhibiting an impressive excess noise ratio (ENR) of 50 dB [21]. However, ENR flatness is worse than 20 dB of variation within a 25-GHz frequency range [21]. This may lead to noise receiver saturation or to insufficient noise power injection to validate the minimum detectable signal (MDS) condition [16] in some parts of the targeted frequency spectrum. In this work, SiGe BiCMOS 55-nm packaged NSs are described. While having the advantage of sufficient ENRav of up to 25 dB in the 140-170-GHz frequency range, the developed packaged NS is monitorable and shows a constant output matching, regardless of the biasing condition, which is a key feature for noise measurement accuracy [22]. Moreover, the presence of an amplifier at p-n diode output enables a low-state biased operating mode, facilitating the MDS condition validation by choosing a biased low state, where the NS itself is unbiased and the amplifier is biased. The result is a lowered ENR<sub>av</sub>, due to a decrease in the difference in generated noise powers between low state and high states, but this technique allows to adapt the noise power injected at the noise receiver input, depending on the device under test (DUT) available power gain  $G_{av,DUT}$ , DUT NF NF<sub>DUT</sub>, and receiver NF NF<sub>RCV</sub>. To the best of our knowledge, this is the first packaged NS based on SiGe technology with such performance in the G-band (140–220 GHz). To place this development beyond the simple feasibility standpoint, repeatability and robustness studies have been conducted on several packaged NS specimens, through multiple assemblies/disassemblies. In detail, this article is organized as follows. Section II is the description of the SiGe BiCMOS circuits used as an NS. Section III covers the packaging technique and the electromechanical structures of the assembled NS. Section IV shows the main characterization results obtained in G-band in terms of S-parameters and ENR<sub>av</sub>, including the detailed description of the methodology for its extraction. In order to validate the NS hardware and the associated methodological approach, the NF50 extraction of a III–V amplifier (WR4.3AMP, denoted MPA04-1 in this article) from Virginia Diodes, Inc. (VDI) [23] and an on-wafer NPN very high speed (NPNVHS) B55 bipolar transistor in the Gband is detailed. The NF extraction method is described, and the obtained results are compared with those from measured noise powers generated by a commercially available NS. Section V gives measurements repeatability assessment for S-parameters and ENR<sub>av</sub> of such packaged NS. Over ten NS packages were assembled and measured to assess S-parameters and noise performance reproducibility. An innovative packaging technique, allowing multiple assembly and disassembly based on graphene paper and low-cost organic substrates, is proposed. Finally, Section VI provides a synthesis of the main results and gives an overview of the available solutions and perspectives of this work.

# II. SIGE BICMOS 55-NM NS DESCRIPTION

The used NS active component is a SiGe BiCMOS 55-nm p-n diode, whose ENR level is monitorable up to 17 dB at

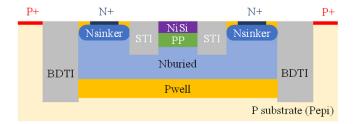

Fig. 1. Cross-sectional schematic view of a SiGe BiCMOS 55-nm p-n diode used as an NS. The p-doped region under anode is created with the PP implant, while the n-doped region is provided by the Nburied region [17].

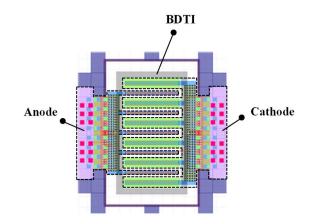

Fig. 2. Top layout view of SiGe BiCMOS 55-nm p-n diode (front-end view with back-end interconnections). Anode surface is 6.25  $\mu$ m<sup>2</sup>.

260 GHz depending on the reverse bias current level in the avalanche regime [17]. Cross-sectional and top views of this diode are shown in Figs. 1 and 2, respectively.

The p-n junction is present between the PP (p-doped silicon) and N-buried ion implantations below the anode access. Shallow trench isolation (STI) provides electrical isolation between the anode and the cathode. The NS has been designed to achieve the correct tradeoff between cutoff frequency, frontend footprint, and noise generation. Therefore, the adopted geometry is a five-fingers anode, each finger being 5  $\mu$ m long. The resulting anode surface is 6.25  $\mu$ m<sup>2</sup>, allowing a maximum cathode current of approximately 25 mA before p-n junction breakdown. In this study, the maximum applied biasing current is limited to 20 mA to preserve samples.

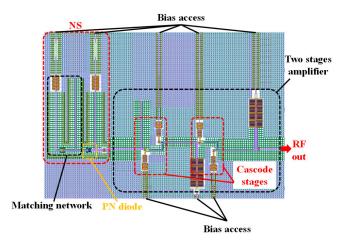

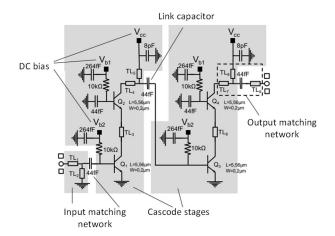

To comply with package insertion losses (ILs) described in Section III, a LNA is used as a buffer stage, enhancing the generated noise power of the p-n diode. A layout view of the amplified NS is given in Fig. 3. It consists of a conventional two-stage cascode structure, each of which is composed of two NPN HBTs with an emitter width and a length of 0.2 and  $5.56~\mu m$ , respectively.

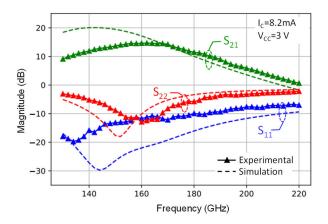

Fig. 4 shows a 15-dB gain between 130 and 160 GHz, relatively flat on this frequency band. LNA design and characterization are more detailed in [24]. Fig. 5 gives the schematic of this LNA. This gain is obtained for a bias of 1 and 2.2 V applied on the transistors base of each cascode stage and a 3-V collector supply voltage. The resulting current consumption of each cascode stage is 8.2 mA. The NS itself is the p-n junction diode previously shown in Figs. 1 and 2, with a matching network stage composed of an nMOS transistor in

Fig. 3. Layout view of the on-wafer amplified NS. The p-n diode is in series with the two-stage LNA used as a buffer stage. A matching network is present both at p-n diode anode and at the two-stage amplifier input [24].

Fig. 4. Measured and simulated S parameters of the two-stage amplifier under a 3-V collector supply voltage and 1- and 2.2-V base voltages bias. The corresponding current consumption of one cascode stage is 8.2 mA [24].

linear regime and a stub. The nMOS transistor gate voltage can be tuned to control the matching impedance.

# III. PACKAGING TECHNIQUE AND MECHANICAL STRUCTURE DESCRIPTION

#### A. Organic Substrate Design and Die Reporting

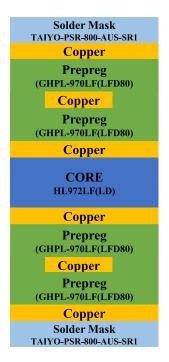

With regard to the substrate hosting the semiconductor chip, the literature contains many reports, where, for the frequency range under consideration, a quartz substrate is used for its very low-loss properties [25], [26]. Although quartz is an excellent material choice from the standpoint of dielectric properties, it is traditionally used as a thin substrate, around 50  $\mu$ m, for die housing. This makes it very fragile and costly, as well as not compatible with industrial assembly line tools. This study aims not only to develop the packaging of a tunable active NS but also to demonstrate the invariance and robustness of performance following multiple assemblies. To minimize the substrate cost and to be able to perform flipchip (FC) assemblies of several dies, the chosen platform is a multilayer organic substrate, leveraging usual processcontrolled materials. The six metallic layers organic substrate stack is described in Table I with a total thickness of 318  $\mu$ m

Fig. 5. LNA electrical schematic [24].

Fig. 6. Schematic cross section of the six metallic layers organic substrate designed and manufactured for flip-chipping the BiCMOS 55-nm die.

and a cumulative thickness tolerance of 30  $\mu$ m. A schematic cross section of this organic substrate is shown in Fig. 6. The substrate core is made of HL972LF(LD) [27], a low transmission loss nonhalogenated laminate material showing 3.4/0.004 for Dk/Df constants at 10 GHz. The chosen prepreg material associated with this core is GHPL-970LF(LFD80) for manufacturing reasons. The values for Dk/Df were extrapolated from those measured up to 110 GHz and used for HFSS simulations.

Organic substrates are singulated by femtosecond laser cutting. This technique holds the distinctive advantage of excellent alignment accuracy and precise control of the kerf line by controlling several process parameters, such as average laser source power, pulse frequency and width, scan speed, and beam tilt angle. Following this process, an accuracy of  $\pm 3~\mu m$  is obtained on the position and width of the

TABLE I

MATERIAL STACK-UP OF ORGANIC SUBSTRATE USED FOR

BICMOS 55-NM FC ASSEMBLIES

| Organic substrate stack |            |                   |                                  |  |  |  |  |

|-------------------------|------------|-------------------|----------------------------------|--|--|--|--|

|                         | Layer      | Thickness (mm)    | Material                         |  |  |  |  |

| Тор                     | Soldermask | $0.015 \pm 0.005$ | TAIYO-PSR-800-AUS-<br>SR1        |  |  |  |  |

| M1                      | Cu plating | $0.018 \pm 0.008$ | Copper                           |  |  |  |  |

|                         | Cu foil    | 0.018 ± 0.008     |                                  |  |  |  |  |

| ABI                     | or Prepreg | $0.03 \pm 0.006$  | MITSUBISHI-GHPL-<br>970LF(LFD80) |  |  |  |  |

| D1                      | Cu plating | $0.008 \pm 0.003$ | Common                           |  |  |  |  |

| P1                      | Cu foil    | 0.008 ± 0.003     | Copper                           |  |  |  |  |

| ABI                     | or Prepreg | $0.03 \pm 0.006$  | MITSUBISHI-GHPL-<br>970LF(LFD80) |  |  |  |  |

| P2                      | Cu plating | $0.018 \pm 0.008$ | Common                           |  |  |  |  |

| P2                      | Cu foil    | $0.018 \pm 0.008$ | Copper                           |  |  |  |  |

|                         | Core       | $0.08 \pm 0.008$  | MITSUBISHI-<br>HL972LF(LD)       |  |  |  |  |

| Р3                      | Cu plating | $0.008 \pm 0.003$ | Common                           |  |  |  |  |

| rs                      | Cu foil    | 0.008 ± 0.003     | Copper                           |  |  |  |  |

| ABF or Prepreg          |            | $0.03 \pm 0.006$  | MITSUBISHI-GHPL-<br>970LF(LFD80) |  |  |  |  |

| D4                      | Cu plating | $0.008 \pm 0.003$ | Campan                           |  |  |  |  |

| P4                      | Cu foil    | 0.008 ± 0.003     | Copper                           |  |  |  |  |

| ABI                     | or Prepreg | $0.03 \pm 0.006$  | MITSUBISHI-GHPL-<br>970LF(LFD80) |  |  |  |  |

| M2                      | Cu plating | $0.018 \pm 0.008$ | Copper                           |  |  |  |  |

| IVIZ                    | Cu foil    | 0.016 ± 0.008     |                                  |  |  |  |  |

| Bottom Soldermask       |            | $0.015 \pm 0.005$ | TAIYO-PSR-800-AUS-<br>SR1        |  |  |  |  |

| Total thickness         |            | $0.318 \pm 0.03$  |                                  |  |  |  |  |

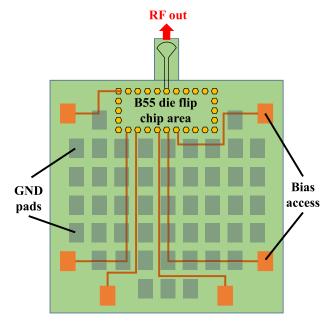

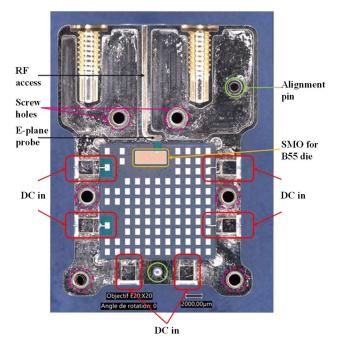

kerf line. The substrate surface finish is full organic solder preservative (OSP) with the addition of 15- $\mu$ m-thick solder mask (SM). Some SM openings (SMOs) are performed on substrate top and bottom surfaces, where the chip is attached and for taking ground contacts. These SMOs have a dimension of 650  $\times$  850  $\mu$ m<sup>2</sup> with horizontal and vertical pitches of 650 and 450  $\mu$ m, respectively. A substrate layout view is given in Fig. 7.

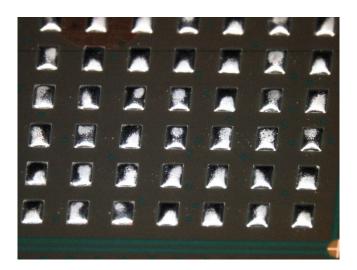

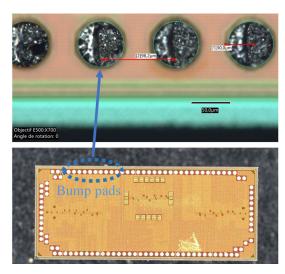

SMOs are filled with solder balls with a height of 30  $\mu$ m extending beyond the SM outer face. The process sequence applied for solder application and FC die assembly on organic substrate is as follows: 1) solder dispensing on the substrate top surface, followed by chip attachment and reflow, and 2) solder dispensing on the substrate bottom surface followed by a second low-temperature reflow step. These reflow steps have been devised to prevent any degradation of the OSP FC pads. Fig. 8 is a view of solder pads dispensed after completion of the process. Several consecutive low-temperature reflow can be performed to monitor the solder height in excess of SM by changing its surface spreading on SMO.

On the semiconductor die side, the FC pad surface is a 30- $\mu$ m-radius disk and consists of a 20- $\mu$ m high copper pillar (CuPi). The under bump metallization (UBM) is circular

Fig. 7. Organic substrate layout detailing main features for B55 die packaging: dc signal routing, RF access, and SMO for GND reporting [28].

Fig. 8. Dispensed matrix of solder pads on bottom organic substrate surface after low-temperature reflow [28].

in shape with a 60  $\mu$ m diameter and the FC pads pitch is 99  $\mu$ m. This UBM is composed of a 0.15- $\mu$ m-thick Ti/Cu alloy layer. The technique used to manufacture such bump is called "bump on pad." This process consists in seven main steps. UBM sputtering is performed to improve conductivity at pad surface.

Then, UBM plating is done selectively due to a resist patterning before the bump plating step, where the SnAg alloy is deposited on the UBM plated zone. Some resist and UBM removals are performed afterward, combined with a thermal bump shaping step. The bump material is a Cu/SnAg alloy. A polyimide passivation step is required to protect bumps against the potential impact of moisture over the long term.

A complete BiCMOS B55 wafer was processed according to the specifications of this bumping process and cut to singulate 64 chips, on which the NSs comprising a single diode and its

Fig. 9. Singulated SiGe BiCMOS 55-nm chip with CuP is grown on bump pads for FC assembly. CuPis have a 30  $\mu$ m radius and 99  $\mu$ m pitch [28].

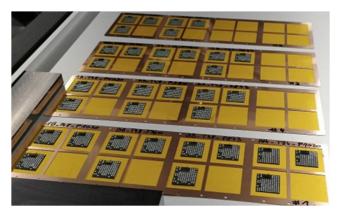

Fig. 10. Samples of substrates with reported B55 dies [28].

amplified version were embedded. A view of such a singulated die with CuPi grown on bump pads is shown in Fig. 9.

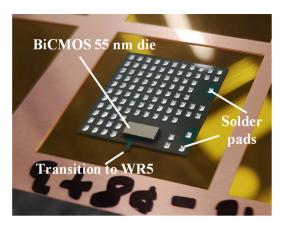

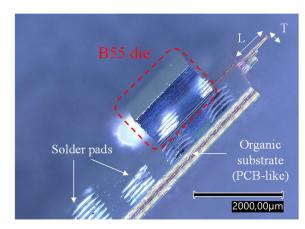

Finally, diced dies were flip-chipped onto the precut organic substrates following the process sequence described above. Fig. 10 is a view of the final 36 pieces of B55 dies assembled on organic substrates. At this stage, an X-ray check was performed to verify the quality of the internal dc routing tracks and the FC transfer-bonding step, without showing any defectivity. Fig. 11 is a zoom on one of the singulated and flip-chipped BiCMOS 55-nm die on a cut organic substrate.

## B. Split-Block Package Design

The NS substrates have been packaged into a two-parts mechanical split-block fabricated using a classical computer numerical control (CNC) machining process in a brass alloy with gold plating on surfaces to enhance the guiding of the mmW signal. At such frequencies, surface roughness may have a significant impact on ILs. A 7-μm-thick Ni/Au surface finishing has therefore been applied to minimize surface roughness and improve surface conductivity along the walls of the WR5 rectangular waveguide. Two split-block packages have been manufactured to assess the reproducibility of the

Fig. 11. BiCMOS 55-nm SiGe die containing the NS and amplified NS, flip-chipped on a singulated six metallic layers organic substrate. Solder pads have been deposited on substrate for homogeneous ground contact [28].

Fig. 12. CNC manufactured brass split-block after NiAu surface finishing [28].

package and its mechanical integrity. An open view of one of the two split-block packages is shown in Fig. 12.

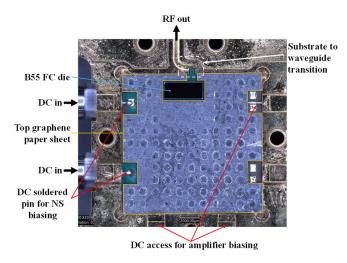

To place this study in an industrial development context, the ease of use and variation of performance in relation to substrate assembly and disassembly have been investigated. To bring dc bias to NS dies, optimized routing metal tracks have been designed within the organic substrate. Specific solder pads have been placed on the top surface of the substrate. For ground contact, the idea is to reduce the parasitic resistance of ground feedback currents by applying as homogeneous as possible a substrate ground to all surfaces of the substrate. The mechanical split-block itself is used as a ground as well. The aim is to avoid additional soldering or wire-bonding during assembly for reasons of time saving and mechanical robustness. The conductive glue option was rejected due to the difficulty in controlling its thickness and the need to clean the surfaces on which it was dispensed afterward. For packaging, sheets of 120-\mu m-thick graphene paper were placed in split-block cavities below and above the substrate. When the split-block is closed and the mechanical assembly is tightened, solder pads arranged on the substrate surfaces induce a partial deformation of graphene paper. This layer is then in contact between the substrate ground signal and the split-block parts, which guarantees a homogenous ground contact between the substrate and the split-block. The depth of each split-block cavity was adjusted to ensure a partial deformation of the

Fig. 13. Opened split-block package after assembly and tightening of an organic substrate with graphene sheets. In this case, the standalone NS is packaged. Three additional dc bias voltages are needed for the amplified version [28].

Fig. 14. Open brass split-block package with an organic substrate inserted into the cavity also showing the positioning of the *E*-plane transition in the rectangular hollow half waveguide [28].

top and bottom graphene sheets when tightening the package, thereby improving self-placement and locking of the substrate position.

Fig. 13 gives a view of the opened split-block after assembly and tightening of an organic substrate. The top graphene sheet is visible and partial deformation at solder pads positions is noticeable.

An additional view of the opened split-block is proposed in Fig. 14. In this case, neither the chip has yet been assembled nor solder pads distributed. Six screws are used for tightening and two alignment pins ensure that the split-blocks are correctly positioned with respect to each other. Once assembled, the split-block package features a WR5 mmW flange

termination, allowing interconnection with an external mmW probe or DUT. The overall split-block size is approximately  $40 \times 27 \text{ mm}^2$  and is 30 mm thick.

The rectangular SMOs for ground contact and dc biasing are clearly visible in Fig. 14. Ground contacts have been arranged as evenly as possible on the substrate surface to ensure a consistent ground contact quality. With this splitblock housing, up to six dc bias signals can be fed to the NS die independently. dc male connectors are fixed by screws to external faces of the split-block. The central pin of the connector penetrates the metal body of the split-block through a cylindrical hole. The hole is filled with a hollow cylindrical Teflon tube to provide electrical insulation. The central metal pin can then slide, so that its end lands on a pad where it can be soldered with the addition of an alloy ball. Room for dc decoupling capacitance has been reserved in the split-block, but measurements showed that this provision was not necessary. In this study, the same silicon chip integrates both the simple NS based on an avalanche diode and its amplifier-augmented version. By imposing the constraint that the split-block can accommodate both types of NS, two types of substrates were designed with different routings of the interconnect traces. The NS circuit needs a cathode bias current to control the avalanche effect and a bias voltage for an impedance matching stage on the anode side. Fig. 14 corresponds to this nonamplified NS configuration showing the die assembled with two dedicated dc bias terminals. The other NS configuration is the same p-n diode with the addition of the two-stage amplifier shown in Fig. 3, which requires three additional dc bias voltages for NPN transistors base biasing and supplying the collector of the cascode stages.

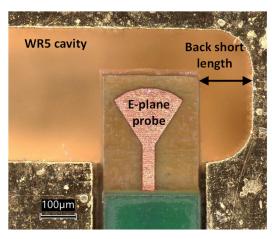

The key transition for RF performance is the one between the organic substrate and the WR5 waveguide. This transition relies on an *E*-plane probe transforming a stripline propagation mode toward the TE10 one of the rectangular waveguide cavities. The key parameters of such transition that determine the ILs and phase shift are the amount of dielectric material in waveguide cavity, the probe position, and back-short length. Fig. 15 shows the precise positioning of the *E*-plane transition resulting from the insertion of the organic substrate into the split-block cavity.

To place this study in a context of a potential industrial scale-up, a design of experiment (DOE) was carried out on the cutting and thinning of the organic substrate to assess the impact of the assembly tolerances on the dispersion of mmW performance.

The thickness and length of the dielectric beam under the *E*-plane bow tie were modified using several cutting and surface machining variants using a femtosecond laser. Two dielectric thicknesses and three different lengths of the dielectric beam have been selected as summarized in Table II. The DOE parameters are identified in Fig. 16 on the microscopy image showing the substrate in profile view with the dielectric beam supporting the *E*-plane transition and the flip-chipped silicon die. Each option corresponding to a given variant of laser cutting and thinning was produced in triplicate for the purpose of evaluating the repeatability of measurements.

Fig. 15. *E*-plane probe transition between organic substrate and WR5 waveguide. Back short length is the distance between substrate edge and waveguide cavity edge [28].

| TABLE II                       |           |

|--------------------------------|-----------|

| FEMTOSECOND LASER DOE PARAMETE | RS VALUES |

| Thickness of dielectric<br>below E plane probe T (μm) | Length of E-plane probe in<br>WR5 cavity L (µm) |

|-------------------------------------------------------|-------------------------------------------------|

|                                                       | 873                                             |

| 24                                                    | 960                                             |

|                                                       | 1020                                            |

|                                                       | 873                                             |

| 48                                                    | 960                                             |

|                                                       | 1020                                            |

#### IV. MEASUREMENT RESULTS IN G-BAND

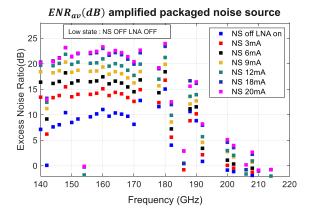

To confirm the functionality of the chips integrated into the packaged NS prior to making RF measurements, the bias current levels were systematically checked for an applied dc voltage bias, and additionally, the consistency of the avalanche diode voltage was checked for an applied dc current bias level. All the chips assembled on substrates were found to be functional, making the S-parameters and noise measurements in G-band possible. Results shown in this section mainly focus on the amplified packaged NS since it presents the most remarkable performance in terms of S-parameters, ENR levels, and MDS condition validation.

#### A. S-Parameters Measurements

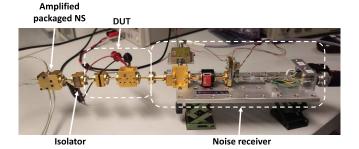

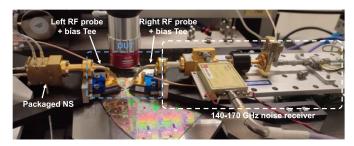

One-port S-parameters measurements have been performed with a vector network analyzer (VNA) and Rohde & Schwarz mmW frequency extension heads in the G-band (ZC220 type). A setup view is proposed in Fig. 17. First, measurements were performed on packaged standalone NS to validate the packaging process on the simplest configuration. Then, the amplified NS version was characterized.

This setup allows to characterize the output matching of the amplified packaged NS for several bias conditions. A key aspect regarding the accuracy of noise measurement using the *Y*-factor method (see Section IV-B for more information) is to guarantee a constant NS output matching regardless of bias in order to avoid indistinguishable losses due to standing waves between the NS and the DUT. More specifically, when

Fig. 16. Side view of a B55 die assembled on organic substrate showing DOE laser cutting parameters L and T [28].

Fig. 17. One-port *G*-band *S*-parameters test setup of standalone packaged NS. The same setup was employed for the amplified packaged NS, with more dc cables to bias the buffer stage.

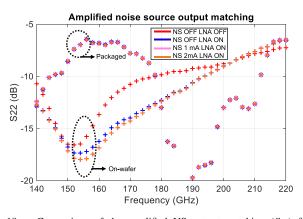

Fig. 18. Comparison of the amplified NS output matching  $(S_{22})$  from measurements on-wafer and in packaged form output over the G-band for several bias conditions. Packaged configuration shows superimposed curves for various NS and LNA biasing.

measuring the Y-factor, the amplified NS is used in the OFF and ONstates, OFF corresponding to an unbiased NS and ON corresponding to a biased NS. Fig. 18 shows the matching at the package output and provides a comparison with  $S_{22}$  of the NS measured on-wafer, i.e., without package. On-wafer impedance matching extraction plane is at FC pad input. Regarding the packaged configuration, impedance matching extraction plane is at package output.

The change in NS biasing has very little influence on the output matching due to the package losses. Superimposed curves at various NS and LNA biases and states are observed in Fig. 18 for the packaged version of amplified NS. The package losses have been extracted using short structures at several

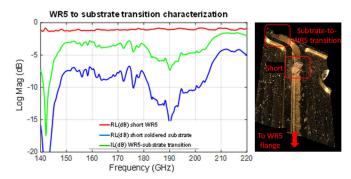

Fig. 19. Organic substrate to WR5 waveguide transition characterization. Measurement results of short structures and transition IL calculus [28].

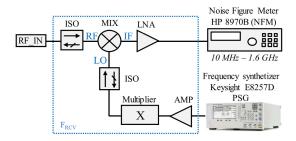

Fig. 20. Noise receiver architecture. This architecture is common to the two receivers used in the study, covering, respectively, 130–170- and 170–220-GHz frequency ranges [17].

reference planes to infer the IL of the substrate to waveguide transition, as shown in Fig. 19. A first short structure was made with an iron sheet placed in waveguide cavity. A second short structure was emulated on a substrate without die by soldering RF line to adjacent ground. With these two structures, it was possible to extract substrate to waveguide transition IL. Fig. 19 displays the characterization results of the shorts. Transition IL [IL $_{transition}(dB)$ ] was calculated from measured return loss of short structures [RL $_{shortWR5}(dB)$ , RL $_{shortsolder}(dB)$ ] as explained in the following:

$$IL_{transition}(dB) = \left| \frac{RL_{shortWR5}(dB) - RL_{shortsolder}(dB)}{2} \right|. \quad (1)$$

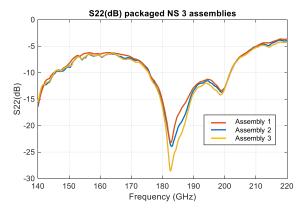

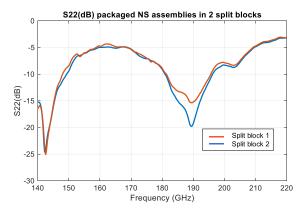

One can infer from Fig. 19 that substrate to waveguide transition dictates the IL (dB) observed in Fig. 18 for the packaged NS configuration. These losses have been estimated to be 4 dB in average in the 140–220-GHz frequency range. One key feature is the constant output matching observed regardless of amplified NS biasing. This aspect is particularly important when operating in the two temperatures method for noise measurement accuracy concerns. The observed shape in  $S_{22}$  is due to transition IL, showing a notch at 190 GHz and approximately -7 dB around 160 GHz. This behavior is also depicted in Fig. 31, where  $S_{22}$ (dB)has been measured over three consecutive assemblies of an NS.

# B. Available ENR (ENR<sub>av</sub>) Extractions

Considering the mismatch between the packaged NS and the DUT, the ENR level (dB) has been extracted with the knowledge of packaged NS output matching in the *G*-band. The effective uncalibrated noise power was measured for

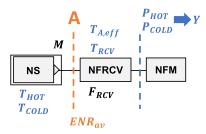

Fig. 21. Block diagram of the setup used for ENRav (dB) extraction of amplified packaged NS.

several NS bias states and transposed to available noise power in the input plane of the noise receiver with the knowledge of its noise factor ( $F_{\rm RCV}$ ), characterized in previous works with the Y-factor method. Reference planes are shown in Fig. 21. Plane A corresponds to the noise receiver input plane.  $P_{\rm HOT}$  and  $P_{\rm COLD}$  are measured at NF meter (NFM) input plane, since NFRCV down converts and amplifies measured RF signal to NFM frequency range. Fig. 20 gives more details regarding NFRCV architecture.

Using (2), one can deduce  $T_{RCV}$  from  $F_{RCV}$  and  $T_0$ . It is the first step leading to  $ENR_{av}(dB)$  extraction

$$T_{\text{RCV}} = T_0(F_{\text{RCV}} - 1) \tag{2}$$

with  $T_{\rm RCV}$  the equivalent noise temperature of the noise receiver and  $T_0 = 290$  K. Using the NS in low and high states, the Y-factor is defined as in the following:

$$Y = \frac{P_{\text{HOT}}}{P_{\text{COLD}}} \tag{3}$$

with  $P_{\text{HOT}}$  and  $P_{\text{COLD}}$  being the measured noise powers at the input of the NFM for a high state and low state of the amplified NS, respectively. As a result, the effective hot noise temperature in the input plane of the noise receiver is given by the following:

$$T_{A,\text{eff}} = T_{RCV}(Y - 1) + Y \frac{T_{\text{cold}}}{M}$$

(4)

with M being the impedance mismatch coefficient between the packaged NS and the noise receiver, and  $T_{\rm cold}$  the NS equivalent noise temperature when the NS and the amplifier are unbiased and supposed known close to 290 K.  $T_{\rm RCV}$  is deduced from the measured value of  $F_{\rm RCV}$  and provides calculation of  $T_{\rm A,eff}$ . In our case, the noise receiver features an isolator at its input and is therefore considered as a 50- $\Omega$  load. With this knowledge, M can be expressed as shown in (5). Due to amplifier isolation and package losses, the resulting mismatch coefficient is close to 1 in the entire frequency range

$$M = \frac{1}{\left(1 - \left|\Gamma_{\text{OUT,PackagedNS}}\right|^2\right)}.$$

(5)

The available hot noise temperature in the input plane of the noise receiver can be subsequently deduced from  $T_{A,\text{eff}}^{\text{HOT}}$  and M by the following:

$$T_{\text{An,av}}^{\text{HOT}} = \text{M.T}_{A,\text{eff}}^{\text{HOT}}.$$

(6)

Fig. 22. Extracted ENR<sub>av</sub>(dB) in *G*-band from the developed amplified packaged NS under several bias conditions [28].

While ENR<sub>av</sub>(dB) can be deduced by the following:

$$ENR_{av}(dB) = 10log\left(\frac{T_{HOT}^{A,av} - T_{COLD}^{A,av}}{T_0}\right)$$

(7)

where  $T_{\text{HOT}}^{A,\text{av}}$  and  $T_{\text{COLD}}^{A,\text{av}}$  correspond to  $T_{A,\text{av}}$  when the amplified NS is biased and unbiased, respectively.  $T_A$  describes the noise equivalent temperature at A plane shown in Fig. 21. Note that one key feature of the present packaged NS is that it can be monitored. Thus, multiple ENRav values can be generated, making this NS adaptable to a wide selection of noise receivers and DUTs. The extracted ENRav values are represented in Fig. 22, for a low state of the NS for which both the avalanche diode and the amplifier are not biased, i.e., NS OFF and LNA OFF. Some ENR values are missing or showing divergences regarding other ENR values measured at adjacent frequency points due to noise receiver frequency response. More specifically, the noise receiver mixer shows some limitation in gain conversion at specific frequency points. This results in a reduced noise receiver sensitivity and can be observed on the extracted ENR<sub>av</sub> levels at 154 and 178 GHz, as shown in Fig. 22.

These results demonstrate a distinctive feature of the greatest interest of this NS in that ENR<sub>av</sub> is monitorable to levels up to 24 dB with a 2-dB flatness between 140 and 170 GHz. Table III gives an overview of the mmW NSs state of the art. The proposed solution shows available ENR levels in line with the existing commercial solutions, while leveraging SiGe technology, compatible with high volume packaging. The key feature is the ability to monitor these ENR levels by adjusting the NS biasing to the noise receiver sensitivity. Moreover, ENR flatness is among one of the best reported in literature. This is an important aspect since high ENR-level frequency variations can induce either noise receiver saturation of insufficient injected noise powers with regard to the MDS condition.

#### C. Noise Figure Measurement in G-Band

The developed packaged NS has been used to extract the NF of several DUTs, using a set of two noise receivers [140–170 GHz (Rx1) and 170–260 GHz (Rx2)]. The first

Fig. 23. Setup for NF measurements of MPA04-1 MPA amplifier with the developed SiGe packaged NS between 140 and 170 GHz.

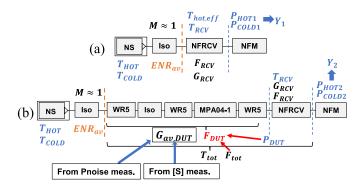

Fig. 24. Schematic setups for  $F_{\rm DUT}$  extraction methodology. (a) Noise receiver calibration step with the amplified packaged NS, using the Y-factor method. An isolator ensures a constant 50  $\Omega$  match for high and low bias states of NS. (b) NF measurement with the DUT in place between packaged NS and noise receiver.

DUT tested is a WR5 connectorized medium-power amplifier (MPA) MPA04-1 from VDI. This PA, initially designed for operation in 170–260 GHz, has an average  $G_{\rm av}$  of 17 dB between 140 and 170 GHz. We want to stress that this band was chosen according to the availability of the noise receiver and solid-state NS, thus enabling the comparisons of NF extraction using different NSs and the same DUT. In this frequency range, the packaged NS has approximately 23 dB of ENR<sub>av</sub> and the associated noise receiver has a 10-dB NF, making this setup relevant for NF extraction. Measurements were also performed with a commercially available NS solution to serve as a base reference. A setup view is shown in Fig. 23.

Fig. 24 illustrates the methodology employed to extract the NF of the MPA04-1 MPA. The NS is either the ELVA commercial solution or the developed packaged NS described in this article. The considered DUT is a group of elements consisting of a WR5 access flange, an isolator, another WR5 access flange, the MPA04-1 amplifier, and a third WR5 access line. The Y-factor method is employed by using the NS in several bias states. The first step consists in connecting the NS directly to the noise receiver and measuring two noise powers corresponding to OFF and ON states, hereafter referred to as  $P_{\rm COLD1}$  and  $P_{\rm HOT1}$ , respectively. This enables the calculation of a first Y-factor called  $Y_1$  and the equivalent noise temperature at the receiver input  $T_{\rm RCV}$  as described in the following:

$$T_{\text{RCV}} = \frac{T_{\text{HOT}} - Y_1 T_{\text{COLD}}}{Y_1 - 1} \tag{8}$$

$\begin{tabular}{ll} TABLE III \\ MMW NSS STATE OF THE ART \\ \end{tabular}$

| Monitorable low state $(P_{COLD})$ | $ENR_{av}(dB)$ | Packaged | Technology              | Monitorable | ENR <sub>av</sub> (dB)<br>flatness | Frequency<br>(GHz) | Constant<br>output<br>matching | Reference                |

|------------------------------------|----------------|----------|-------------------------|-------------|------------------------------------|--------------------|--------------------------------|--------------------------|

| No                                 | 45             | Yes      | IMPATT Diode            | No          | ±15                                | 140-220            | NA                             | ELVA ISSN-05<br>[21]     |

| No                                 | 50             | Yes      | IMPATT Diode            | No          | ±20                                | 220-330            | NA                             | ELVA ISSN-03<br>[21]     |

| No                                 | 10             | Yes      | NA                      | No          | ±2                                 | 110-170            | NA                             | VDI WR6.5NS<br>[29]      |

| No                                 | 8,5            | Yes      | NA                      | No          | ±2                                 | 140-220            | NA                             | VDI WR5.1NS<br>[29]      |

| No                                 | 25             | Yes      | NR Noisecom<br>Process  | No          | ±2                                 | 18                 | No                             | NC346D<br>Precision [30] |

| Yes                                | 9              | Yes      | GaAs                    | Yes         | ±2                                 | 170-200            | NA                             | [19]                     |

| Yes                                | 15-27          | No       | SiGe BiCMOS<br>130nm    | Yes         | ±5                                 | 90-270             | Yes                            | [20]                     |

| Yes                                | <20 & 28       | No       | SiGe BiCMOS<br>& UTC-PD | Yes         | ±7                                 | 120-325            | Yes<br><-10                    | [18]                     |

| Yes                                | 37             | No       | SiGe BiCMOS<br>55nm     | Yes         | ±2                                 | 140-170            | Yes < -7,5                     | [16]                     |

| Yes                                | 24             | Yes      | SiGe BiCMOS<br>55nm     | Yes         | ±2                                 | 140-170            | Yes < -7,5                     | This work                |

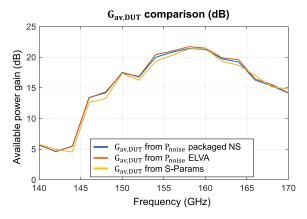

Fig. 25. DUT available power gain extractions based on S-parameters and measured noise powers from the present amplified packaged NS and the commercial ELVA NS [28].

where  $T_{\rm HOT}$  and  $T_{\rm COLD}$  are the noise equivalent temperatures associated with NS ON and OFF states, respectively.

The second step consists in measuring the noise powers in the same NS OFF and ON states in order to calculate a second Y-factor noted  $Y_2$  with the DUT inserted in the measurement chain. The available power gain of the DUT  $G_{\rm av,DUT}$  can be calculated from these noise powers with the following:

$$G_{\text{av,DUT}} = \frac{P_{\text{HOT2}} - P_{\text{COLD2}}}{P_{\text{HOT1}} - P_{\text{COLD1}}}.$$

(9)

A comparison of  $G_{\text{av,DUT}}$  extracted from S-parameters and noise powers is given in Fig. 25, where it can be observed that the maximum discrepancy is lower than 0.4 dB between 140 and 170 GHz.

These two steps allow the calculation of the noise receiver gain  $G_{RCV}$ , which is necessary for the calculation of the

NF at the input plane of the noise receiver, as detailed in the following:

$$G_{\text{RCV}} = \frac{P_{\text{HOT1}} - P_{\text{COLD1}}}{(T_{\text{HOT}} - T_{\text{COLD}})k\Delta_f} \tag{10}$$

where k is the Boltzmann constant,  $T_{\rm HOT}$  and  $T_{\rm COLD}$  are the equivalent noise temperatures of the NS in high and low states, respectively, and  $\Delta_f$  is the noise receiver bandwidth. The knowledge of these parameters gives the expression of the available noise power  $P_{\rm DUT}$  at the DUT output expressed by the following:

$$P_{\text{DUT}} = \frac{P_{\text{COLD2}}}{G_{\text{RCV}}} - kT_{\text{RCV}}\Delta_f.$$

(11)

Finally, the DUT linear noise factor  $(F_{\rm DUT})$  is given by the following:

$$F_{\text{DUT}} = \frac{P_{\text{DUT}}}{G_{\text{av,DUT}} k T_{\text{COLD}} \Delta_f}.$$

(12)

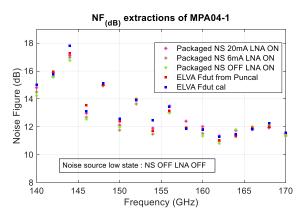

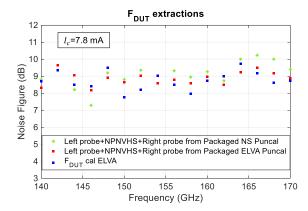

The extraction results are shown in Fig. 26. The packaged NS has the advantage to be controllable in terms of bias and was therefore used in three different ON states in order to assess the variability of measurements. The ELVA NS can be used to measure either calibrated or uncalibrated noise powers using a calibration algorithm corresponding to the associated 140-170-GHz noise receiver. For a fair and relevant comparison, one should consider in priority extractions made from uncalibrated noise powers with both NS. In this context, measurements show a maximum discrepancy between the packaged NS and ELVA NS of 0.3 dB at 146 GHz. Puncal refers to NF extracted from uncalibrated noise powers. This is the only available technique with the proposed packaged NS since the calibration algorithm is only compatible with the ELVA commercial NS. One development axis could be to develop such algorithm associated with the introduced

Fig. 26. Extracted NF of MPA04-1 using commercial ELVA NS and package NS with different bias conditions between 140 and 170 GHz [28].

Fig. 27. On-wafer NPNVHS NF test setup with packaged NS between 140 and 170 GHz [28].

NS based on its available ENR levels. The three distinct NF measurements performed with the packaged NS under three bias conditions give a maximum dispersion of 0.4 dB at 140 GHz. These results prove the relevance of using the developed packaged NS compared with commercial NS solutions. In this variable bias measurement scenario, it is important to note that the waveguide flange assembly induces a typical variability of  $\pm 0.2$  dB at such frequencies, which contributes to the measurement dispersion mentioned above.

To further consolidate previous results, a bipolar transistor NPNVHS HBT in SiGe B55 technology has also been characterized on wafer with the packaged NS and commercial ELVA NS between 140 and 170 GHz. A picture of the setup is given in Fig. 27. The considered DUT is the group of elements consisting in the left RF probe, the B55 NPNVHS bipolar transistor, and the right RF probe. The NPNVHS bipolar transistor has  $5.56 \times 0.2 \ \mu \text{m}^2$  emitter length and width, respectively. It is biased under a collector current of 7.8 mA. A similar NF extraction methodology to that used previously was employed, using two measurement steps, with and without the DUT. Extraction results are represented in Fig. 28. A comparison is also made between the ELVA calibrated and uncalibrated noise powers and packaged NS noise powers. The discrepancy between the packaged amplified NS and the ELVA extractions is less than 0.8 dB in the 140-170 GHz range. This gap tends to be larger as the available power gain of the DUT decreases.

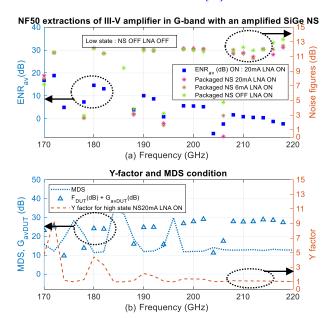

Finally, an assessment of the accuracy of NF extraction has been performed between 170 and 220 GHz based on the measurements of the MPA04-1 MPA. By using the packaged NS under several bias conditions, it is possible to monitor its

Fig. 28. On-wafer NPNVHS NF extraction results with packaged amplified NS and ELVA NS between 140 and 170 GHz [28].

Fig. 29. NF extraction accuracy assessment of MPA04-1 between 170 and 220 GHz. (a) Available ENR and NF values obtained for several biasing conditions. (b) Associated noise measurement validity indicators (MDS condition, *Y*-factor) [28].

ENR<sub>av</sub> levels and place the setup at the limit of validation of the MDS condition. The resulting ENR<sub>av</sub> values are all referred to an unbiased low state and three biased high states. To evaluate the tradeoff between a sufficient ENR<sub>av</sub> value and the MDS condition with regard to the NF extraction accuracy, MDS condition and ENR<sub>av</sub> are shown in Fig. 29(a) and (b). As a reminder, the MDS condition can be expressed as in the following, depending on DUT available power gain ( $G_{av,DUT}$ ) and NF (NF<sub>DUT</sub>) and noise receiver NF (NF<sub>RCV</sub>):

$$NF_{DUT} + G_{av,DUT} \ge NF_{RCV} + 3 \text{ dB}.$$

(13)

The MDS condition validation limit is naturally reached since the ENR<sub>av</sub> level of the packaged NS decreases beyond 180 GHz due to the two-stages LNA bandwidth, as shown in Fig. 4. The maximum ENR<sub>av</sub> level is reached in the configuration, where the high state corresponds to a 20-mA biased NS and LNA turned ON. The *Y*-factor has been plotted in the 170–220-GHz frequency range for this operating mode in Fig. 26(b). It shows decreasing values down to 1, which

Fig. 30. Statistical representation of MPA04-1 NF extracted values between 170 and 220 GHz for 12 bias states of the packaged amplified NS [28].

means that the difference between noise powers in high and low states of the amplified NS tends to 0. In such condition, the NF extraction accuracy is decreasing, showing discrepancies of more than 2 dB above 200 GHz between the different high states amplified NS biasing. However, the MDS condition is validated in the entire frequency range: the MDS curve refers to the NF<sub>RCV</sub> increased by a 3-dB margin. Some frequency points show discontinuities in the MDS condition. This is due to the noise receiver input mixer having a gain conversion dropping at specific frequency points. One can infer from Fig. 29(b) that the MDS condition is validated with more than 10-dB margin. It is important to note that at such frequencies, a commercial NS for the purpose of comparison was not available within our measurement platform. Moreover, the DUT considered here is quite favorable to perform an NF extraction since its available power gain is wideband. To the best of our knowledge, it is the first time a III-V amplifier has been characterized with a SiGe packaged NS at these frequencies.

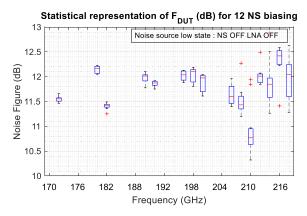

To further investigate the accuracy of NF extraction with the setup comprising the MPA04-1 MPA amplifier, the packaged NS, and the 170–220 GHz noise receiver, a statistical approach to measure NF as a function of the choice of amplified NS high-state biasing was conducted. Since the MDS condition is easily validated even when operating in the low-state operating mode (NS OFF and LNA OFF), this biasing has been chosen as a lower reference for ENR values. Fig. 27 provides the illustration of the impact that the bias state of the NS can have on the dispersion of the NF. Twelve different high states biases were considered, between 0.5 and 20 mA for the p-n diode cathode current and the LNA turned on. The extraction results reveal an NF dispersion better than 0.5 dB at frequencies up to 200 GHz over these various bias conditions. Above this frequency, significant dispersion can be observed, marked by the red crosses in Fig. 30. To the best of our knowledge, it is the first time a statistical approach regarding NF extraction has been conducted in this frequency range.

# V. Measurements Repeatability Assessment in G-Band

This part aims to illustrate the reproducibility work carried out on S-parameters and ENR<sub>av</sub> extractions on several

Fig. 31. S-parameters repeatability measurements in G-band of one sample assembled three consecutive times in the same split-block package [28].

Fig. 32. S-parameters repeatability measurements in G-band of one sample assembled in two available split-block packages [28].

amplified NS as a function of sensitivity to the package assembly/disassembly steps and for two different split-block units.

#### A. S-Parameters Measurement Repeatability

To place this study beyond the proof-of-concept stage, several repeatability measurements have been performed over multiple assemblies. More specifically, one-port *S*-parameters measurements have been performed on a sample mounted and dismounted three consecutive times in the same split-block package. The results given in Fig. 31 exhibit an excellent reproducibility between several assemblies, which consolidates the packaging approach implemented.

Moreover, the same substrate has been packaged in the two available split-block units to assess the overall manufacturing quality. Results are given in Fig. 32 and show a high degree of repeatability, validating the assembly strategy as well as the robustness of the split-block and organic substrates fabrication scheme.

#### B. ENR<sub>av</sub> Measurement Repeatability

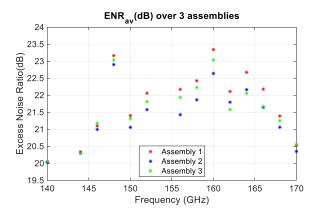

An assessment of generated  $ENR_{av}$  variability over several assemblies has also been conducted between 140 and 170 GHz. In order to study the impact of multiple packaging steps on  $ENR_{av}$  variability, one sample has been mounted and dismounted three times and measured at

Fig. 33. ENR<sub>av</sub> repeatability measurements of one sample over three consecutive assemblies in the same package [28].

Fig. 34. ENR<sub>av</sub> repeatability measurements of a packaged NS over 20 consecutives extractions by switching from low (NS OFF/LNA OFF) to high (NS 20 mA/LNA ON) states [28].

each assembly/disassembly stage. Results given in Fig. 33 show a maximum  $\rm ENR_{av}$  variability between two assemblies of 0.7 dB.

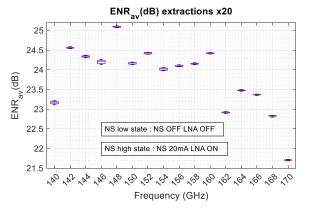

Moreover, the packaged NS has been used in the low state and high state to extract consecutively 20 ENR<sub>av</sub> values by directly switching the bias from NS OFF/LNA OFF to NS 20 mA/LNA ONin order to check the robustness of the packaged circuit with respect to bias switchovers and to evaluate the variations of generated noise powers. As shown in Fig. 34, this experiment revealed a maximum change in ENR<sub>av</sub> of 0.13 dB at a given frequency, confirming the robustness of the packaged NS.

## VI. CONCLUSION AND PROSPECTS

For the first time, a packaged NS based on a SiGe BiCMOS 55-nm technology operating between 140 and 220 GHz has been fabricated, packaged, and measured. The chip packaging strategy based on low-cost organic substrates and compatible with multiple assemblies has been detailed. S-parameters and ENR<sub>av</sub> have been measured in G-band, showing unprecedented levels for a packaged SiGe NS at such frequencies. ENR<sub>av</sub> up to 24 dB, with the capability of ENR<sub>av</sub> level monitoring between 140 and 170 GHz, has been demonstrated. One can consider a 14 dB range of ENR<sub>av</sub> levels at a given frequency between low state (NS OFF LNA ON) and high state (NS 20-mA LNA ON). This NS can generate up to 5 dB of

ENR<sub>av</sub> at 200 GHz. One of the key aspects of NF extraction accuracy using the *Y*-factor method is to guarantee a constant NS output matching. This is the case with the developed packaged NS owing to the amplifier stage isolation. This amplification stage brings the distinctive asset of being able to work with a biased low state, ensuring sufficient noise power generation to comply with the MDS condition validation.

This is a differentiating advantage compared to existing commercial NS solutions at these frequencies. To assess NS validity, it has been used for NF measurements of two DUTs. The first one is a WR5-connectorized III-V MPA amplifier from VDI (MPA04-1). NF extractions have been performed concurrently with a commercial ELVA NS to compare and validate extraction with a reference standard. The maximum NF discrepancy observed between the two NSs is 0.3 dB, which proves the quality of the developed packaged NS. In addition, the NF extraction of an on-wafer SiGe BiC-MOS 55-nm NPNVHS bipolar transistor has been performed, showing a maximum discrepancy of 0.8 dB between the packaged NS and ELVA NS in the 140-170-GHz frequency range. In another respect, many measurements repeatability regarding S-parameters and ENR<sub>av</sub> results have been discussed and demonstrate the robustness and quality of the developed packaged NS. The developed package can be kept for a future upgrade that could embed a multi-impedance tuner, offering the possibility of four noise parameters measurements up to 220 GHz for multiple wafer technologies.

#### ACKNOWLEDGMENT

The authors are grateful to Amkor Technology for their support with wafer bumping and the BEM&T Team from STMicroelectronics Grenoble for their highly valuable assistance related in the design, fabrication, and assembly of the organic substrates. They also acknowledge MC2 Technologies for their collaboration in the design and fabrication of split-blocks. The assistance of the Pôle Caractérisation Hyperfrêquence, Optique et Photonique (CHOP) high-frequency characterization platform at the Institute of Electronics, Microelectronics, and Nanotechnology (IEMN) is acknowledged for the extensive test campaigns in *G*-band related to this work.

# REFERENCES

- [1] D. Cuadrado-Calle, D. George, B. Ellison, G. A. Fuller, and K. Cleary, "Celestial signals: Are low-noise amplifiers the future for millimeterwave radio astronomy receivers?" *IEEE Microw. Mag.*, vol. 18, no. 6, pp. 90–99, Sep. 2017, doi: 10.1109/MMM.2017.2712038.

- [2] D. Cuadrado-Calle, P. Piironen, and N. Ayllon, "Solid-state diode technology for millimeter and submillimeter-wave remote sensing applications: Current status and future trends," *IEEE Microw. Mag.*, vol. 23, no. 6, pp. 44–56, Jun. 2022, doi: 10.1109/MMM.2022.3155031.

- [3] B. Thomas et al., "Millimeter & sub-millimeter wave radiometer instruments for the next generation of polar orbiting meteorological satellites—MetOp-SG," in *Proc. 39th Int. Conf. Infr., Millim., THz* waves (IRMMW-THz), Sep. 2014, pp. 1–3, doi: 10.1109/IRMMW-THz2014.6956005.

- [4] D. Cuadrado-Calle et al., "EQM front-end receivers at 183 and 229 GHz for the microwave sounder on MetOp-SG," in *Proc. 33rd Gen. Assem. Sci. Symp. Int. Union Radio Sci.*, Aug. 2020, pp. 1–4, doi: 10.23919/URSIGASS49373.2020.9232214.

- [5] M. Hoefle et al., "Low noise 89 GHz detector module for MetOp-SG," in *Proc. Eur. Microw. Conf. (EuMC)*, Sep. 2015, pp. 395–398, doi: 10.1109/EuMC.2015.7345783.

- [6] Y. Sun and C. J. Scheytt, "A 122 GHz sub-harmonic mixer with a modified APDP topology for IC integration," *IEEE Microw. Wire-less Compon. Lett.*, vol. 21, no. 12, pp. 679–681, Dec. 2011, doi: 10.1109/LMWC.2011.2170830.

- [7] Y. Mao, K. Schmalz, J. Borngräber, and J. C. Scheytt, "A 245 GHz CB LNA and SHM mixer in SiGe technology," in *Proc. IEEE 12th Topical Meeting Silicon Monolithic Integr. Circuits RF Syst.*, Jan. 2012, pp. 5–8, doi: 10.1109/SiRF.2012.6160120.

- [8] P. Song, R. L. Schmid, A. Ç. Ulusoy, and J. D. Cressler, "A high-power, low-loss W-band SPDT switch using SiGe PIN diodes," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2014, pp. 195–198, doi: 10.1109/RFIC.2014.6851695.

- [9] S. R. Zahran, L. Boccia, F. Podevin, and P. Ferrari, "BiCMOS ratrace coupler based on slow-wave CPS transmission lines for 120 GHz applications," in *Proc. Microw. Medit. Symp. (MMS)*, May 2022, pp. 1–5, doi: 10.1109/MMS55062.2022.9825575.

- [10] H. Ghanem, S. Lépilliet, D. Gloria, F. Danneville, and G. Ducournau, "SiGe based LNA for data communication applications at 211 GHz," in *Proc. 46th Int. Conf. Infr., Millim. THz Waves (IRMMW-THz)*, Aug. 2021, pp. 1–2, doi: 10.1109/IRMMW-THz50926.2021.9567152.

- [11] H. Tataria, M. Shafi, A. F. Molisch, M. Dohler, H. Sjöland, and F. Tufvesson, "6G wireless systems: Vision, requirements, challenges, insights, and opportunities," *Proc. IEEE*, vol. 109, no. 7, pp. 1166–1199, Jul. 2021, doi: 10.1109/JPROC.2021.3061701.

- [12] T. Waliwander. THz-to Be or Not to Be in 6G. Farran.com. Accessed: Jul. 4, 2020. [Online]. Available: https://www.farran.com/wp-content/uploads/2022/02/THz-To-be-or-not-to-be-in-6G.pdf

- [13] B. Heinemann et al., "SiGe HBT with fx/fmax of 505 GHz/720 GHz," in *IEDM Tech. Dig.*, Dec. 2016, pp. 3.1.1–3.1.4, doi: 10.1109/IEDM.2016.7838335.

- [14] A. Gauthier, "Etude et développement d'une nouvelle architecture de transistor bipolaire à hétérojonction Si/SiGe compatible avec la technologie CMOS FD-SOI," Ph.D. dissertation, Dept. Elect. Eng., Univ. Lille, Lille, France, 2017.

- [15] M. Gilden and M. E. Hines, "Electronic tuning effects in the read microwave avalanche diode," *IEEE Trans. Electron Devices*, vol. ED-13, no. 1, pp. 169–175, Jan. 1966, doi: 10.1109/T-ED.1966.15652.

- [16] V. Fiorese et al., "A 140 GHz to 170 GHz active tunable noise source development in SiGe BiCMOS 55 nm technology," in *Proc. 16th Eur. Microw. Integr. Circuits Conf. (EuMIC)*, Apr. 2022, pp. 125–128, doi: 10.23919/EuMIC50153.2022.9783645.

- [17] J. C. A. Gonçalves et al., "Millimeter-wave noise source development on SiGe BiCMOS 55-nm technology for applications up to 260 GHz," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 9, pp. 3732–3742, Sep. 2019, doi: 10.1109/TMTT.2019.2926289.

- [18] H. Ghanem et al., "Silicon based diode noise source scaling for noise measurement up to 325 GHz," in *Proc. 44th Int. Conf. Infr., Millim.*, THz Waves (IRMMW-THz), Sep. 2019, pp. 1–2.

- [19] N. Ehsan, J. Piepmeier, M. Solly, S. Macmurphy, J. Lucey, and E. Wollack, "A robust waveguide millimeter-wave noise source," in *Proc. Eur. Microw. Conf. (EuMC)*, Sep. 2015, pp. 853–856, doi: 10.1109/EuMC.2015.7345898.

- [20] H. Forstén, J. H. Saijets, M. Kantanen, M. Varonen, M. Kaynak, and P. Piironen, "Millimeter-wave amplifier-based noise sources in SiGe BiCMOS technology," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 11, pp. 4689–4696, Nov. 2021, doi: 10.1109/TMTT.2021.3104028.

- [21] ISSN-03/ISSN-05 mm-Wave High ENR CW Noise Sources. elva-1.com. Accessed: Aug. 5, 2022. [Online]. Available: https://elva-1.com/products/sub-terahertz-noise-sources-140-to-330-ghz

- [22] (2014). Noise Figure Measurement Accuracy—The Y-Factor Method. Accessed: May, 11 2020. [Online]. Available: https://www.keysight.com/us/en/assets/7018-06829/application-notes/5952-3706.pdf

- [23] (2022). Waveguide Amplifiers Operational Manual. Accessed: Aug. 2, 2022. [Online]. Available: https://www.vadiodes.com/images/Products/AmpsandFilters/VDI-792.34\_VDI\_Waveguide\_ Amplifier\_Product\_Manual.pdf

- [24] S. Bouvot, "Contribution au BIST in-situ: Intégration sur silicium d'un banc de caractérisation en bruit en bande D," Ph.D. dissertation, Dept. Elect. Eng., Univ. Lille, Lille, France, 2018.

- [25] A. Maestrini et al., "A 1.7–1.9 THz local oscillator source," *IEEE Microw. Wireless Compon. Lett.*, vol. 14, no. 6, pp. 253–255, Jun. 2004, doi: 10.1109/LMWC.2004.828027.

- [26] A. R. Kerr, S. Pan, S. Whiteley, M. Radparvar, and S. Faris, "A fully integrated SIS mixer for 75–110 GHz," in *Proc. IEEE Int. Dig. Microw.* Symp., May 1990, pp. 851–854, doi: 10.1109/MWSYM.1990.99712.

- [27] Nypcb/English/Product/PCBIntroduction. nanyapcb.com. Accessed: Feb. 14, 2023. [Online]. Available: https://www.nanyapcb.com.tw/nypcb/english/Technology/PPSRoadmap.aspx

- [28] V. Fiorese, "Nano sonde active intelligente pour mesures de bruit et de puissance dans la bande de fréquence 130–260 GHz," Ph.D. dissertation, Dept. Elect. Eng., Univ. Lille, Lille, France, 2022.

- [29] Virginia Diodes, Inc Your Source for Terahertz and mm-Wave Products. vadiodes.com. Accessed: May, 15 2022. [Online]. Available: https://vadiodes.com/en/

- [30] Products. noisecom.com. Accessed: Jul. 4, 2022. [Online]. Available: https://noisecom.com/products/calibrated-sources/nc346-broadband-awgn-up-to-67-ghz

Victor Fiorese received the M.S. degree in RF electronics from the École Nationale Supérieure de l'Électronique et de ses Applications (ENSEA), Cergy, France, in 2018, and the Ph.D. degree in electronics from the University of Lille, Lille, France, in 2022.

He is currently involved with the RF and millimeter-wave (mmW) Validation Laboratory, STMicroelectronics, Grenoble, France, to develop on-wafer RF measurement activity. His main interests are RF test automation, noise, and small- and

large-signal measurements of transceivers up to 67 GHz.

João Carlos Azevedo Gonçalves received the M.S. degree in microélectronique nanotechnologie et telecom from the University of Lille, Lille, France, in 2015, and the Ph.D. degree in electrical engineering from the Institute of Electronics, Microelectronics, and Nanotechnology (IEMN), University of Lille, in 2019.

He is currently with the Technology Design Platform Department, STMicroelectronics, Crolles, France, where he focuses on RF and millimeter-wave (mmW) characterization for BiCMOS and CMOS

advanced technologies. His current research interests include advanced silicon device small signal, high frequency (HF) noise, and large-signal characterization up to 320 GHz.

**Simon Bouvot** received the M.S. degree in automatic control and electronics from the INSA Toulouse, Toulouse, France, in 2014, and the Ph.D. degree in electrical engineering from the Institute of Electronics, Microelectronics, and Nanotechnologies (IEMN), University of Lille, Lille, France, in 2018.

He is currently employed with STMicroelectronics, Crolles, France, where he is involved in research and development on RF and millimeterwave BiCMOS and CMOS circuit characterization. His research interests are focused on built-in self-test

for silicon noise characterization above 110 GHz.

**Sylvie Lépilliet** was born in Béthune, France, in 1964. She received the B.E. degree in electronics from the Centre National des Arts et Métiers (CNAM), Lille, France, in 1991.

In 1986, she joined the Centre Hyperfréquences et Semiconducteurs, University of Lille, Lille. She is currently in charge of the high-frequency measurement facilities with the Institute of Electronics, Microelectronics, and Nanotechnology, University Lille I, Villeneuve d'Ascq, France, particularly of the noise test set.

Daniel Gloria received the Engineering degree in electronics from the École Nationale Supérieure d'Électronique et de Radioélectricité de Grenoble, Grenoble, France, in 1995, and the M.S.E.E. degree in optics, optoelectronics, and microwaves design systems from the Institut National Polytechnique de Grenoble (INPG), Grenoble, in 1995.

He spent two years as an RF Designer Engineer, from 1995 to 1997, with the ALCATEL Bell Network System Labs, Charleroi, Belgium, and was involved in the development of the Cablephone RF

front end and its integration in hybrid-fiber-coax telecommunication networks. Since 1997, he is working with the Technology Design Platform Department, STMicroelectronics, Crolles, France. His interests are in the development and optimization of RF and photonics platforms for applications in BiCMOS and CMOS advanced technologies.

Guillaume Ducournau has been with the Institute of Electronics, Microelectronics and Nanotechnology (IEMN), UMR-CNRS 8520, University of Lille, Villeneuve d'Ascq, France, since 2007. He is the Leader of the THz wireless communications activity with IEMN using optoelectronic THz photomixers, electronic receivers, THz instrumentation, and millimeter-wave (mm-wave) characterization. He worked on several European projects: STREP ROOTHz 2010–2013, THOR H2020, and now on GRAPH-X as well as in TIMES (6G SNS) as well

as the Marie-Curie TERAOPTICS network. At national level, he was the Coordinator of the COM'TONIQ Project, from 2014 to 2017, funded by the Agence Nationale de la Recherche (ANR) (INFRA 2013) dedicated to THz communications in the 300-GHz band, the ANR/DFG TERASONIC Project for the use of THz photonics technologies and electrical solid-state technologies for THz communications, and SPATIOTERA for spatially distributed photomixers. He is involved in national France 2030 programs gathering several French laboratories under the "PEPR" programs supported by the ANR. In this framework, the FUNTERA Project (six partners) is investigating THz converters, while the SYSTERA Project (12 partners) is dedicated to beyond 90-GHz systems for future networks. He also participates to the ST-IEMN common laboratory, and more specifically involved in the mm-wave technologies characterization part. He has authored or coauthored more than 180 publications in peer-reviewed international journals or peer-reviewed conferences proceedings and holds one patent.

Dr. Ducournau received the 2020 International Symposium on Antennas and Propagation (ISAP) Best Paper Award.

**Christophe Gaquière** received the Ph.D. degree in electronic from the University of Lille, Lille, France, in 1995.

He was responsible for the microwave characterization part of the common laboratory between Thales TRT and Institut d'Electronique de Microélectronique et de Nanotechnology (IEMN), University Lille I, Villeneuve d'Ascq, France, focused on wide bandgap semiconductors (GaN, SiC, and diamond), from 2003 to 2007. He is in charge of the silicon millimeter-wave advanced

technologies part of the common laboratory between STMicroelectronics, Crolles, France, and IEMN. He created the company MC2-Technologies, Villeneuve d'Ascq. He is currently a Full Professor with the Polytech'Lille, University of Lille, and carries out his research activity at IEMN. His research topics concern design, fabrication, characterization, and modeling of HEMTs and heterojunction bipolar transistor (HBT) devices. He works on GaAs, InP, and metamorphic HEMTs, and he is involved in GaN activities. He has authored or coauthored over 150 publications and 300 communications. His current research interests include microwave characterizations (small and large signal between 1 and 500 GHz) in order to correlate the microwave performances with the technological and topology parameters. His current activities mainly concern the investigation of 2-D electronic plasmons and Gunn-like effects for terahertz solid-state GaN-based detectors and emitters [High Electron Mobility Transistor (HEMT) and Self-Switching Diode (SSD)], AlGaN/GaN nanowires for microwave applications, and Microelectromechanical Systems (MEMS) activities based also on GaN.

Dr. Gaquière served on the Technical Program Committee (TPC) of several European conferences.

Emmanuel Dubois (Member, IEEE) received the M.S. degree in engineering from the Institut Supérieur d'Electronique et du Numérique (ISEN), Lille, France, in 1985, and the Ph.D. degree from the University of Lille, Lille, in 1990.

In 1992, he was a Visiting Scientist with the International Business Machines Corporation (IBM) T.J. Watson Research Centre, Yorktown Heights, NY, USA, working on characterization and simulation of submicrometer SOI-MOSFETs. In 1993, he joined the Institut d'Electronique de Microélectronique et

de Nanotechnologie (IEMN UMR 8520), Lille, where he is currently the Director of the Research at the Centre National de la Recherche Scientifique, CNRS. He was a Coordinator of three European Projects focused on Schottky source—drain MOS technologies (FP4-IST-QUEST, FP5-IST-SODAMOS, and FP6-IST-METAMOS) and was involved as the Workpackage/Task Leader in a series of European projects devoted to ultimate MOS architectures (FP5 SASEM, FP6 SiNANO NOE, FP7 NANOSIL NOE, FP6 NANOCMOS IP, and FP6 PULLNANO IP). He is currently the Head of the STMicroelectronics-IEMN Joint Laboratory and coordinates the PIA-EQUIPEX project LEAF on advanced laser-based microfabrication for System Moore integration. His research interests cover advanced source/drain CMOS technology, RF and millimeter-wave (mmW) CMOS/BiCMOS, nonconventional thermal energy harvesting, laser micromachining, and functional packaging of compact RF/mmW/photonics subsystems.

Dr. Dubois was a recipient of the IBM Award for high-performance computing in 1990. From 2005 to 2016, he was on the Technical Program Committee of European Solid-State Device Research Conference (ESSDERC) and was the Technical Program Committee (TPC) Member of the VSLI Symposium on Technology (2018–2020). Until 2017, he participated to the nanoelectronics committee of the French Observatory on Micro and Nano Technologies (OMNT).