## Analysis of Airgaps for Off State Capacitance Reduction in SOI CMOS RF Switches

Daniel Gheysens, Alain Fleury, Stephane Monfray, Frederic Gianesello, Philippe Cathelin, David Troadec, Jean-François Robillard, Emmanuel Dubois

### ▶ To cite this version:

Daniel Gheysens, Alain Fleury, Stephane Monfray, Frederic Gianesello, Philippe Cathelin, et al.. Analysis of Airgaps for Off State Capacitance Reduction in SOI CMOS RF Switches. IEEE Transactions on Electron Devices, 2023, 70 (11), pp.5814 - 5817. 10.1109/TED.2023.3311415 . hal-04192324

## HAL Id: hal-04192324 https://hal.science/hal-04192324

Submitted on 31 Aug 2023  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Analysis of Airgaps for Off-State Capacitance Reduction in SOI-CMOS RF Switches

#### Daniel Gheysens, Alain Fleury, Stéphane Monfray, Frédéric Gianesello, Philippe Cathelin, David Troadec, Jean François Robillard, and Emmanuel Dubois

Abstract—This article analyses the introduction of airgaps in the interconnect network of SOI-CMOS based RF switches to significantly reduce the off-state capacitance COFF without degrading the on-state resistance RON. Based on the 130 nm node of an existing RF-SOI-CMOS technology, an accurate COFF evaluation is performed by calculating the respective contributions of the interconnects and the intrinsic transistor separately. The impact of the relative airgap volume is simulated and results in an ultimate COFF reduction of 24.6% when the intermetal dielectric is completely replaced by air. It is shown that most of the reduction in COFF is achieved by introducing airgap at the first metal level. The airgap approach is verified experimentally by partially eliminating the interconnect dielectric of RF switches in post-process etching steps. A measured COFF improvement of 21.7 fF/mm (7.2%) and 18.3 fF/mm (6.3%) is demonstrated for 0.14 and 0.16 µm gate length transistors for which the airgap volume is only partial.

#### Index Terms— RF switches, Airgap, CMOS, SOI, RF, Offstate capacitance, On-state resistance

#### I. INTRODUCTION

THE demand for secure, reliable, low-latency, high data rate and massive connectivity is driving the increasingly stringent specifications on the front-end modules of mobile communication systems [1] [2]. As more switches add to the link budget loss, it is of utmost importance that they offer the lowest possible insertion loss in the on-state while keeping the best isolation in the off-state. These two distinctive requirements are reflected in the minimisation of the RON×COFF time constant which is a well-established figure of merit (FoM) for benchmarking switch technologies. Currently, the partially depleted silicon-on-insulator (PDSOI) CMOS technology is extremely successful in the RF front-end market [3][4]. To further improve the FoM of PDSOI CMOS switches, a difficulty inevitably arises because efforts to reduce R<sub>ON</sub> by L<sub>G</sub> downscaling entails an increase of COFF by reducing the distance between source/drain terminals. The introduction of airgaps in the interconnection network, also referred to as backend-of-line (BEOL), allows to partially solve this antagonistic

relationship, thus reducing R<sub>ON</sub> without altering C<sub>OFF</sub>. Over the last two decades, the introduction of airgaps in interconnects has been widely studied as a solution to overcome the bottleneck of RC delay, power consumption and cross-talk in dense CMOS digital circuits [5]. The literature reports two main approaches for creating airgaps in the BEOL: i) the first one is based on the use of a sacrificial oxide or template of decomposable polymers to define air cavities [6][7][8][9] and ii) the second version involves a non conformal deposition of a dielectric layer over a cavity that pinches and closes at its the top, thus creating a teardrop shaped airgap [10][11][12][13] [14]. More recently, a third approach has been demonstrated using a 2D material, namely h-BN for its exceptional mechanical properties, in order to seal the airgaps which eliminates the need for a sacrificial material [15]. Although the concept of airgaps in BEOL is not new, very few papers have addressed its benefit in the context of RF applications. Following the third integration approach mentioned above, Prawoto et al. [16] demonstrated the interest of lateral airgaps embedded only in the ultra-thick topmost metal layer to mitigate the parasitic capacitance associated to integrated inductances, but without providing a significant advantage on the quality factor. Finally, two patents take advantage of airgaps in RF switches by integrating them above the gate of MOS transistors and with a vertical extension only limited to the first dielectric and metal level [17][18]. This article proposes to evaluate new aspects of air-gapped interconnects applied to RF switches that have not yet been addressed in the literature: (i) how C<sub>OFF</sub> reduction margin evolves as the airgap extends vertically across the entire BEOL stack, (ii) the feasibility of complete intermetal dielectric (IMD) removal in apertures spanning the deep submicron scale at the first contact level of the transistor to the micrometer range on the uppermost metal layers and (iii) the simulation of COFF variations with the airgap volume that captures the 3D complexity of the BEOL layout and the charge dynamics within the transistor. Depending on the RF switch circuit layout and the gate pitch, the relative contribution of the BEOL to the total C<sub>OFF</sub> can reach up to 40% [4][19]. To appreciate the potential gain margin, it is easy to understand that replacing the oxide-like ( $\varepsilon_r \sim 4$ ) IMD by air  $(\varepsilon_r \sim 1)$  means C<sub>OFF</sub> could theoretically be lowered to 70% of the

This work was supported by: i) the STMicroelectronics-IEMN joint laboratory ii) the French government through the National Research Agency (ANR) under program PIA EQUIPEX LEAF ANR-11-EQPX-0025 and iii) the French RENATECH network on micro and nanotechnologies.

D. Gheysens, A. Fleury, S. Monfray, F. Gianesello and P. Cathelin are with STMicroelectronics, 850 rue Jean Monnet 38920 Crolles France (e-mail: daniel.gheysens@externe.junia.com). D. Troadec, J.-F. Robillard and E. Dubois are with Univ. Lille, CNRS, Centrale Lille, Univ. Polytechnique Hauts de France, JUNIA, UMR 8520 -IEMN, F-59000 Lille, France (e-mail: emmanuel.dubois@iemn.fr).

original figure. To confirm the above expectation, this article first proposes a simulation-based accurate calculation of  $C_{OFF}$ . In a second part, we discuss the creation of airgaps in the BEOL of a CMOS PDSOI technology using post-process etching steps. Finally, RF measurement performed on partially hollowed-out switches confirm that  $C_{OFF}$  can be lowered at no extra penalty on  $R_{ON}$ .

#### II. TEST STRUCTURE AND SIMULATION MODEL

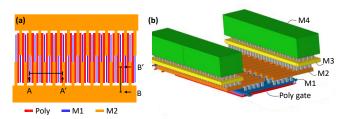

The considered 200 mm RF SOI-CMOS technology is based on a previous 130 nm technology node [4]. The test structure consists of an array of 25 MOS transistors in parallel with a unitary gate finger width of 10 µm as shown in Fig. 1(a). Several polysilicon gate lengths were considered in the experimental plan ( $L_G = 0.14, 0.16, 0.18, 0.22 \mu m$ ) with two gate pitches of 0.86 and 0.92 µm. This structure is optimized for COFF and RON extraction in the series and shunt branches of an RF switch [20]. It is worth noting that both the gate and body of the transistor are biased through a 200 k $\Omega$  resistor to accommodate high RF input power, thus mitigating the electric field that the gate dielectric and junctions must experience to prevent breakdown. The gate and body voltage are both set to 3.3 V to extract R<sub>ON</sub> in the on-state and -2.5 V to extract C<sub>OFF</sub> in the off-state. The total COFF capacitance can be partitioned into two components, the first being associated to the interconnection network (BEOL) above the silicon surface while the front-end of the line (FEOL) contribution is related to the intrinsic MOS transistor where the source/drain coupling in the off-state is essentially induced by the source/body and drain/body junctions in series. Due to the highly 3D nature of the interconnection network, the BEOL contribution to COFF is well appreciated by solving the Maxwell equations (ADS-Momentum [21]) on a 3D simulation geometry extracted from the circuit layout as illustrated in Fig. 1. Conversely, the intrinsic MOS transistor is well captured by a 2D cross-section as the geometry is invariant along the transistor width. A driftdiffusion simulation code (IMPACT [22]) is therefore used to simulate the small-signal response of the FEOL source/drain two-port system.

Fig. 1. (a) Layout of the RF switch test structure comprising 25 MOS transistors in parallel (b) 3D view of the BEOL interconnect network showing 4 metal layers M1 to M4.

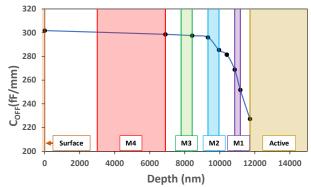

In both simulation cases,  $C_{OFF}$  is extracted from S-parameters which are converted into Y-parameters used to identify the elements of a  $\pi$ -type lumped equivalent circuit [23]. In a first step, simulations were calibrated for a gate length and pitch of 0.14 and 0.92 µm, respectively. This yields the two components of the off-state capacitance as  $C_{OFF-BEOL}$ = 111.7 fF/mm and  $C_{OFF-FEOL}$ = 190.1 fF/mm, the sum of which is 301.8 fF/mm in excellent agreement with the measurement performed on the initial switch test structure (301.6 fF/mm). In a second step, we have evaluated the impact of a selective removal of the intermetal oxide as the etching front penetrates into the BEOL stack. This front is assumed to be uniform and the dielectric volume above it is replaced by air. Fig. 2 shows the variations of C<sub>OFF</sub> as the etching front moves deeper into the BEOL and ultimately reach the contact etch-stop layer (CESL) just above the active silicon layer of the transistor. The sharpest gradient of COFF reduction is achieved when the dielectric removal front falls below the first metal level. In the fully hollowed-out configuration, the minimum simulated COFF reaches 227.4 fF/mm which represents a significant reduction of 24.6 %. This corresponds to an improvement of the RON×COFF FoM from 101 fs to 76 fs when airgaps with total IMD removal are implemented.

Fig. 2. Simulated off-state capacitance COFF as a function of the airgap etching front for gate length and pitch of 0.14 and 0.92  $\mu$ m, respectively. M1-M4 correspond to the metal interconnect layers.

#### III. POST-PROCESS AIRGAP PROCESS

For proof of concept purposes, an etching sequence was developed using 3 focused ion beam (FIB) steps and a final reactive ion etching (RIE) step.

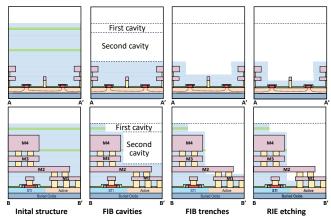

Fig. 3. Airgap etching process step illustrated by schematic crosssections along A-A' and B-B' directions as outlined in Fig. 1.

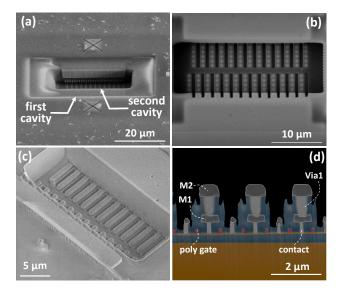

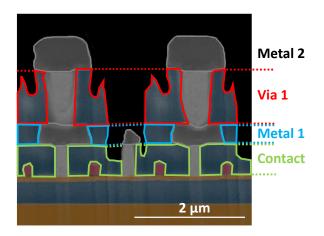

The post process steps are detailed in Fig. 3 which presents schematic cross-sections taken along the A-A' and B-B' directions shown in Fig. 1, perpendicular and parallel to the polysilicon gate fingers, respectively. The first two steps consist of FIB etching concentric cavities above the active area of the switch from which the IMD is removed over ~ 9.32  $\mu$ m down to the top level of the M2 metal layer. This 2-step procedure is used to recalibrate the alignment of the second cavity from the M4 metal layer that is uncovered after etching the first cavity. The third FIB step consists in etching rectangular narrow trenches above the gate fingers, i.e., between the M1 lines alternatively connected to the transistor source/drain extensions. The final RIE step is based on CF<sub>4</sub>/Ar chemistry to gently remove as much oxide as possible from both sides of the poly gates without altering it. Fig. 4 shows the etching results at different stages and highlights that dielectric removal is achieved imperfectly (Fig. 4(d)) due to the anisotropy of the last RIE step. It is however sufficient to demonstrate the reduction in capacitive coupling by the airgaps as detailed in next section.

Fig. 4. SEM images at various stages of the airgap etching process: (a) Tilted view of first two FIB cavities. (b) Top view of FIB trenches. (c) Tilted view final structure. (d) Cross section view showing partial dielectric etching after final RIE step.

#### IV. EXPERIMENTAL VALIDATION

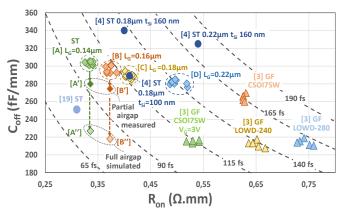

S-parameter measurements were first performed on all nonpost-processed switches of the above-mentioned experimental plan. The results are reported under markers [A] to [D] in Fig. 5, which summarizes the R<sub>ON</sub>-C<sub>OFF</sub> figure of merit in clouds of data points corresponding to measurements on 4 devices with the same gate length and pitch in order to capture the variability. This figure also includes experimental points labelled [A'] and [B'] on devices subjected to the incomplete BEOL airgap process illustrated in Fig. 4. The obtained C<sub>OFF</sub> are 279.8 and 274.3 fF/mm for  $L_G = 0.14$  and 0.16  $\mu$ m, respectively, both with a 0.92 µm polysilicon gate pitch. This corresponds to a C<sub>OFF</sub> improvement by 21.7 fF/mm (7.2%) and 18.3 fF/mm (6.3%), respectively. Finally, data points with marker [A"] and [B"] correspond to the best achievable COFF of 227 and 218 fF/mm, respectively, as obtained by simulations when the intermetal oxide is completely removed. Although the experimental COFF reduction observed in [A'] et [B'] do not reach the best achievable simulated figures given by [A"] and [B"], the mitigation of capacitive coupling is significant. Fig. 5 also

shows that airgaps with total IMD removal reduces  $R_{ON} \times C_{OFF}$  from 109 fs (marker [A], measured) to 81 fs (marker [A"], simulated) as obtained from simulations. This last figure is very close to the performance of 78 fs recently measured in [19] for a PDSOI technology that has been deeply redesigned at the intrinsic transistor level. It can be anticipated that the application of the same airgap principle on an optimized technology [19] would result in a FoM of 50-53 fs.

Fig. 5.  $C_{\text{OFF}}$  versus  $R_{\text{ON}}$  showing the impact of experimental partial and full simulated airgaps.

The reduction in capacitance associated with incomplete etching of the airgap corresponding to marker [A'] can be precisely captured by the retro-simulation of the partially etched BEOL structure. As shown in Fig. 6, an effective dielectric permittivity can be assigned to each layer as a function of the remaining oxide surface and the airgap surface introduced, according to the following weighting formula:

$$\varepsilon_{eq} = \left(\frac{S_{etched}}{S_{layer}}\right) \cdot \varepsilon_{air} + \left(1 - \frac{S_{etched}}{S_{layer}}\right) \cdot \varepsilon_{oxide} \tag{1}$$

where  $S_{etched}$  is the surface of etched dielectric while  $S_{layer}$  is the surface of the initial oxide layer before etching. Table I shows the calculated effective permittivity values associated with the partitioning shown in Fig. 6, which have been fed back into Momentum to assess the impact of partial etching.

TABLE I

EFFECTIVE DIELECTRIC PERMITTIVITY OF STACK LAYER

| Layer            | Dielectric permittivity<br>of unprocessed layer | Effective permittivity of partially etched layer |

|------------------|-------------------------------------------------|--------------------------------------------------|

| Contact          | Metal 1 4.1                                     | 3.82                                             |

| Metal I<br>Via 1 |                                                 | 3.56<br>2.89                                     |

The corrected  $C_{OFF}$  value amounts to 274 fF/mm in excellent agreement with the measurement at 279.8 fF/mm. This result demonstrates the consistency of the measurements obtained in the case of an incomplete airgap, and clearly opens up the prospect that the results represented by markers [A"] and [B"] are achievable.

Fig. 6. Cross section obtained by SEM images at the end of the airgap etching process showing partial surface of oxide and air.

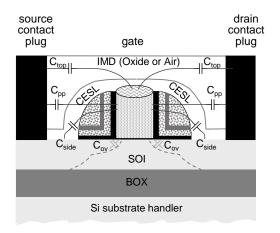

Finally, it is interesting to consider the role of fringing capacitances in the  $C_{OFF}$  reduction mechanism. Referring to Fig. 7, the components of fringing capacitances that are potentially affected by the airgaps are the parallel plate and top components,  $C_{pp}$  and  $C_{top}$ , respectively. However, most of the electric field lines starting from the gate are guided laterally into the medium with the highest dielectric constant, i.e., the multilayer spacer and the CESL nitride layer, thus contributing to the side capacitance  $C_{side}$ . The relative weight of  $C_{pp}$  and  $C_{top}$  with respect to  $C_{side}$  remains low for this reason.

Fig. 7. Schematic representation of a unitary transistor showing the various components of fringing capacitances

In summary, the substitution of the IMD oxide with air leads to a reduction of the  $C_{pp}$  and  $C_{top}$  components and, in turn, the total fringing capacitance. These slight variations of fringing capacitances are expected to have a minor impact on the reduction of  $C_{OFF}$  because the surface of gate electrode involved in the electrostatic coupling effect remains small compared to the surface of electrodes offered between the source and drain contact plugs. The reduction in dielectric permittivity resulting from the introduction of airgaps is therefore considered to be the predominant mechanism for  $C_{OFF}$  reduction. This result is further supported by the retro-simulation results presented above, based solely on the reduction in capacitive coupling through the introduction of effective dielectric permittivities.

#### V. CONCLUSION

In summary, the impact of airgaps extending over the entire interconnection stack of RF switches has been analyzed in detail. A partial validation has been proposed using post process etching steps. The obtained experimental results can be analyzed by realizing that the substantial reduction in R<sub>ON</sub> from 0.50 to 0.33  $\Omega$ .mm obtained by scaling L<sub>G</sub> from 0.22 to 0.14 µm comes at the cost of an increase in C<sub>OFF</sub> from 279.0 to 301.6 fF/mm. This penalty is here fully compensated by the airgaps that we introduced using post-process etching of the BEOL, even though complete oxide removal is not achieved. While L<sub>G</sub> downscaling from 0.22 to 0.14 µm results in a significant reduction of R<sub>ON</sub>×C<sub>OFF</sub> from 141 fs to 101 fs without airgaps, their introduction, as illustrated in Fig.4, further improve this FoM to 94 fs. To demonstrate the full potential of BEOL airgaps for RF switch applications, future work will focus on the introduction of a thin liner on the sidewalls of airgaps as a passivation layer and implementing an isotropic and selective vapor phase etching (e.g. vapor HF) strategy to hollow out the oxide at the M1 level down to the CESL.

#### REFERENCES

- W. Chen, J. Montojo, J. Lee, M. Shafi and Y. Kim, "The Standardization of 5G-Advanced in 3GPP," in *IEEE Communications Magazine*, vol. 60, no. 11, pp. 98-104, November 2022, doi: 10.1109/MCOM.005.2200074.

- [2] F. Balteanu, "RF Front End Module Architectures for 5G," 2019 IEEE BiCMOS and Compound semiconductor Integrated Circuits and Technology Symposium (BCICTS), Nashville, TN, USA, 2019, pp. 1-8, doi: 10.1109/BCICTS45179.2019.8972735.

- [3] M. Jaffe, M. Abou-Khalil, A. Botula, J. Ellis-Monaghan, J. Gambino, J. Gross, Z.X. He, A. Joseph, R. Phelps, S. Shank, J. Slinkman, and R. Wolf, "Improvements in SOI technology for RF switches," 2015 IEEE 15th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, San Diego, CA, USA, 2015, pp. 30-32, doi: 10.1109/SIRF.2015.7119865.

- [4] F. Gianesello, A. Monroy, V. Vialla, E. Canderle, G. Bertrand, M. Buczko, M. Coly, J. Nowakowski, N. Revil, L. Rolland, D. Gloria, A. Juge, S. Gachon, J.P. Aubert, E. Granger, "Highly linear and sub 120 fs Ron × Coff 130 nm RF SOI technology targeting 5G carrier aggregation RF switches and FEM SOC," 2016 IEEE 16th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Austin, TX, USA, 2016, pp. 9-12, doi: 10.1109/SIRF.2016.7445454.

- [5] Z. Tőkei, V. Vega, G. Murdoch, M. O'Toole, K. Croes, R. Baert, M. Van der Veen, C. Adelmann, J. P. Soulié, J. Boemmels, C. Wilson, S. H. Park, K. Sankaran, G. Poutois, J. Sweerts, S. Paolillo, S. Decoster, M. Mao, F. Lazzarino, J. Versluijs, V. Blanco, M. Ercken, E. Kesters, Q-T. Le, F. Holsteyns, N. Heylen, L.Teugels, K. Devriendt, H. Struyf, P. Morin, N. Jourdan, S. Van Elshocht, I. Ciofi, A. Gupta, H. Zahedmanesh, and K. Vanstreels, "Inflection points in interconnect research and trends for 2nm and beyond in order to solve the RC bottleneck," 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2020, pp. 32.2.1-32.2.4, doi: 10.1109/IEDM13553.2020.9371903.

- [6] P. A. Kohl, D. M. Bhusari, M. Wedlake, C. Case, F. P. Klemens, J. Miner, B.-C. Lee, R. J. Gutmann, and R. Shick, "Air-gaps in 0.3µmelectrical interconnections," IEEE Electron Device Lett., vol. 21, no. 12, pp. 557– 559, Dec. 2000. doi:10.1109/55.887464.

- [7] L. G. Gosset, F. Gaillard, D. Bouchu, R. Gras, J. de Pontcharra, S. Orain, O. Cueto, Ph. Lyan, O. Louveau, G. Passemard, and J. Torres, "Multi-Level Cu Interconnects Integration and Characterization with Air Gap as Ultra-Low K Material Formed using a Hybrid Sacrificial Oxide / Polymer Stack," 2007 IEEE International Interconnect Technology Conferencee, Burlingame, CA, USA, 2007, pp. 58-60, doi: 10.1109/IITC.2007.382348.

- [8] R. Gras, F. Gaillard, D. Bouchu, A. Farcy, E. Petitprez, B. Icard, J. C. Le-Denmat, L. Pain, J. Bustos, P. H. Haumesser, P. Brun, G. Imbert, L. Clément, C. Borowiak, M. Rivoire, C. Euvrard, V. Arnal, S. Olivier, S. Moreau, M. Mellier, T. Chevolleau, G. Passemard, and J. Torres, "300 mm Multi Level Air Gap Integration for Edge Interconnect Technologies and Specific High Performance Applications," 2008 International Interconnect Technology Conference, Burlingame, CA, USA, 2008, pp. 196-198, doi: 10.1109/IITC.2008.4546965.

- [9] H. Warashina, H. Kawasaki, H. Nagai, A. Yamaguchi, N. Sato, Y. Kikuchi, and X. Sun, "Advanced Air Gap Formation Scheme Using Volatile Material," 2021 IEEE International Interconnect Technology Conference (IITC), Kyoto, Japan, 2021, pp. 1-3, doi: 10.1109/IITC51362.2021.9537549.

- [10] T. Harada, A. Ueki, K. Tomita, K. Hashimoto, J. Shibata, H. Okamura, K. Yoshikawa, T. Iseki, M. Higashi, S. Maejima, K. Nomura, K. Goto, T. Shono, S. Muranaka, N. Torazawa, S. Hirao, M. Matsumoto, T. Sasaki, S. Matsumoto, S. Ogawa, M. Fujisawa, A. Ishii, M. Matsuura, and T. Ueda, "Extremely Low Keff (1.9) Cu Interconnects with Air Gap Formed Using SiOC," 2007 IEEE International Interconnect Technology Conferencee, Burlingame, CA, USA, 2007, pp. 141-143, doi: 10.1109/IITC.2007.382364.

- [11]J. Noguchi, T. Oshima, T. Matsumoto, S. Uno and K. Sato, "Multilevel Interconnect with Air-Gap Structure for Next-Generation Interconnections," in *IEEE Transactions on Electron Devices*, vol. 56, no. 11, pp. 2675-2682, Nov. 2009, doi: 10.1109/TED.2009.2030538.

- [12]S. Natarajan, M. Agostinelli, S. Akbar, M. Bost, A. Bowonder, V. Chikarmane, S. Chouksey, A. Dasgupta, K. Fischer, Q. Fu, T. Ghani, M. Giles, S. Govindaraju, R. Grover, W. Han, D. Hanken, E. Haralson, M. Haran, M. Heckscher, R. Heussner, P. Jain, R. James, R. Jhaveri, I. Jin, H. Kam, E. Karl, C. Kenyon, M. Liu, Y. Luo, R. Mehandru, S. Morarka, L. Neiberg, P. Packan, A. Paliwal, C. Parker, P. Patel, R. Patel, C. Pelto, L. Pipes, P. Plekhanov, M. Prince, S. Rajamani, J. Sandford, B. Sell, S. Sivakumar, P. Smith, B. Song, K. Tone, T. Troeger, J. Wiedemer, M. Yang, and K. Zhang, "A 14 nm logic technology featuring 2nd-generation FinFET, air-gapped inter-connects, self-aligned double patterning and a 0.0588µm2SRAMcell size," inIEDM Tech. Dig., Dec. 2014, pp.3.7.1–3.7.3. doi:10.1109/IEDM.2014.7046976.Z

- [13]C. Penny, S. Gates, B. Peethala, J. Lee, D. Priyadarshini, S. Nguyen, P. McLaughlin, E. Liniger, C. K. Hu, L. Clevenger, T. Hook, H. Shobha, P. Kerber, I. Sheshadri, J. Chen, D. Edelstein, R. Quon, G. Bonilla, V. Paruchuri, and E. Huang, "Reliable airgap BEOL technology in advanced 48 nm pitch copper/ULK interconnects for substantial power and performance benefits," 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 2017, pp. 1-4, doi: 10.1109/IITC-AMC.2017.7968970.

- [14]Z-J. Hu, X-P. Qu, H. Lin, M. Li, S-M. Chen, and Y-H. Zhao, "Development of air-gap etching process by a mask approach for characterization of intralayer and interlayer capacitances," 2018 Jpn. J. Appl. Phys. 57 07ME03, doi: 10.7567/JJAP.57.07ME03

- [15]C. Prawoto, Z. Ma, Y. Xiao, S. Raju and M. Chan, "Air-Gap Technology With a Large Void-Fraction for Global Interconnect Delay Reduction," in *IEEE Transactions on Electron Devices*, vol. 68, no. 10, pp. 5078-5084, Oct. 2021, doi: 10.1109/TED.2021.3105086.

- [16] C. Prawoto, Z. Ma, Y. Xiao, S. Raju, C. Zhou and M. Chan, "Low-Loss RF Passive Elements by Top-Metal Air-Gap Technology," 2022 6th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Oita, Japan, 2022, pp. 47-49, doi: 10.1109/EDTM53872.2022.9798013.

- [17]Z-X. He, M. D. Jaffe, R. L. Wolf, A. J. Joseph, B. T. Cucci, and A. K. Stamper, "Air Gap over transistor gate and related method," U.S. Patent 10 211 146 B2, Feb. 19, 2019. Available: https://patents.google.com/patent/US10211146B2/en.

- [18] B. Yami, N. Magi, B. Liat, A. Heiman, and Y. Roizin, "SOI devices with Air Gaps and stressing layers," U.S. Patent 10 707 120 B1, Jul. 7, 2020. Available:

https://patents.google.com/patent/US10707120B1/en.

- [19]F. Gianesello, A. Fleury, F. Julien, J. Dura, S. Monfray, S. Dhar, C. A. Legrand, J. Amouroux, B. Gros, L. Welter, C. Charbuillet, P. Cathelin, E. Canderle, N. Vulliet, E. Escolier, L. Antunes, E. Granger, P. Fornara, C. Rivero, G. Bertrand, P. Chevalier, A. Regnier, and D. Gloria, "Advanced 200-mm RF SOI Technology exhibiting 78 fs RON×COFF and 3.7 V breakdown voltage targeting sub 6 GHz 5G FEM, " in 2022 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Denver, CO, USA, 2022, pp. 191-194, doi: 10.1109/RFIC54546.2022.9863082.

- [20]Z. Shaked, P. Hurwitz, A. Heiman, K. Moen, R. Kanawati, S. Chaudhry, and M. Racanelli, "SOI technology for front end applications," 2015 IEEE

International Conference on Microwaves, Communications, Antennas and Electronic Systems (COMCAS), Tel Aviv, Israel, 2015, pp. 1-3, doi: 10.1109/COMCAS.2015.7360403.

- [21]E. Dubois, D. Collard, B. Baccus, and D. Morel,"IMPACT3 user's guide," Lille, IEMN-ISEN, Jan. 1991.

- [22] Keysight Advanced Design System ADS Available: https://edadocs.software.keysight.com/display/support/ADS+DesignGuid es

- [23] A. Bhaskar, J. Phillipe, E. Okada, F. Braud, J-F. Robillard, C. Durand, F. Gianesello, D. Gloria, C. Gaquière, and E. Dubois, "Substrate-Induced Dissipative and Non-Linear Effects in RF Switches: Probing Ultimate Performance Based on Laser-Machined Membrane Suspension," *Electronics*, vol. 11, no. 15, p. 2333, Jul. 2022, doi: 10.3390/electronics11152333.