# Impacts of low voltage distribution grid resilience constraints on AC/DC converter sizing

Frédéric Reymond-Laruina, Loïc Queval, Djamel Hadbi, Philippe Egrot, Marc Petit, Michel Cordonnier

#### ▶ To cite this version:

Frédéric Reymond-Laruina, Loïc Queval, Djamel Hadbi, Philippe Egrot, Marc Petit, et al.. Impacts of low voltage distribution grid resilience constraints on AC/DC converter sizing. 27th International Conference on Electricity Distribution (CIRED 2023), CIRED, Jun 2023, Rome, Italy. hal-04191814

### HAL Id: hal-04191814 https://hal.science/hal-04191814v1

Submitted on 31 Aug 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Copyright

## Impacts of low voltage distribution grid resilience constraints on AC/DC converter sizing

Frédéric REYMOND-LARUINA EDF R&D – France Frederic.reymond-laruina@edf.fr

> Philippe EGROT EDF R&D – France philippe.egrot@edf.fr

Loïc QUEVAL

CentraleSupélec, GeePs – France

Loic.queval@centralesupelec.fr

Marc PETIT CentraleSupélec, GeePs – France marc.petit@centralesupelec.fr Djamel HADBI EDF R&D - France djamel.hadbi@edf.fr

Michel CORDONNIER Enedis - France michel.cordonnier@enedis.fr

#### **ABSTRACT**

In a context of increasing DC applications and energy savings, LVDC technologies could be a key technology towards more efficient distribution grids. However, the specific behavior of DC short circuits and the selectivity constraints of existing installations must be taken into account when sizing the converter that interfaces the AC and DC grids. This article details these requirements, proposes a sizing method by electrothermal simulation and highlights the consequences on the converter sizing.

#### INTRODUCTION

Over the past few decades, the development of distributed electricity generation and energy storage systems, as well as the increase in the number of native direct current (DC) consumers, has led to an increasing focus on low voltage direct current (LVDC) distribution grids or at least dedicated DC feeders. Such a grid would allow better interaction between applications [1], but also, and more importantly, greater efficiency. First, because the resistance of a DC cable could be lower than that of an AC cable. Second, the current absence of standards could allow for voltages up to 1500 V, resulting in lower transmission losses [2]. Finally, a DC distribution system would centralize and standardize the AC/DC conversion step, which is currently performed by each user. Due to the large number of transformer substations, the use of an electronic transformer would not be relevant, due to its cost, size, and high losses. In this context, the preferred solution is to keep the existing LVAC transformer and to implement a centralized AC/DC converter on its secondary on a limited number of feeders [3].

Despite a large number of commercially available converters, electrical safety remains an obstacle to the deployment of these solutions. This is because the behavior of a DC short circuit is very different from that of an AC short circuit, due to the presence of capacitors on the DC link. In the event of a fault, these capacitors discharge almost instantaneously, before the grid current flows through the converter [4]. The absence of zero-crossing of the current requires the generation of an opposite voltage to force the decrease of the DC current

and interrupt the fault [5], which slows down traditional protections. Combined with the limited overcurrent capabilities of semiconductor components, these factors have encouraged manufacturers to look for fast protective devices. Many different proposals can be found in the literature, such as hybrid or electronic circuit breakers [6], which can achieve response times of 2 to 0.1 ms. Another solution is to use fuses, already used in distribution grids, which are cheaper but offer unpredictable response time [7]-[9].

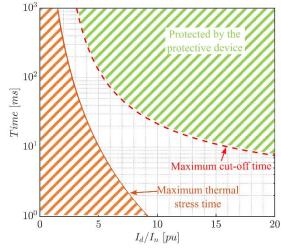

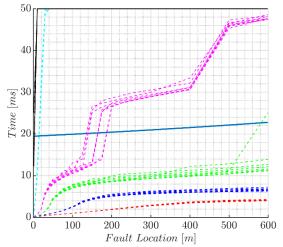

However, fast protection is not sufficient in the case of a DC distribution grid. In fact, to ensure the selectivity of the protection, the grid operator requires that the protection closest to the fault reacts first. Therefore, the further away a protection is from a consumer, the later the interruption should be. In the absence of national or international standards, this constraint is mostly omitted by manufacturers. AC/DC converters may then have a time to reach the maximal thermal stress that is lower than the maximum protection cut-off time (Figure 1). To ensure a safe operation, the maximum cut-off time must be lower than the maximum module thermal stress time for the whole fault current range.

Figure 1: Example of protection not coordinated with the admissible module thermal stress of the converter.

This paper proposes to address this issue by presenting a

CIRED 2023 1/5

method for sizing 2-level voltage source converters (VSC), taking into account the operating constraints of the distribution grid. Firstly, these constraints are detailed. Then the sizing method is presented. Finally, the results are discussed.

#### CONSTRAINTS AND ASSUMPTIONS

#### **Grid requirement**

Table 1: Harmonic current constraints in relation to the magnitude of the fundamental current at rated power

| Harmonics       | Odd   | Even    |

|-----------------|-------|---------|

| h < 11          | 4 %   | 1 %     |

| 11 ≤ h < 17     | 2 %   | 0.5 %   |

| $17 \le h < 23$ | 1.5 % | 0.375 % |

| 23 ≤ h < 35     | 0.6 % | 0.15 %  |

| 35 ≤ h          | 0.3 % | 0.075 % |

There are 3 constraints for the grid-connection of a power electronic converter: power quality, efficiency, and selectivity.

The power quality on the DC side of a converter is still debated in the literature. The only consensus parameter is the voltage ripple, but its exact value is still undefined. Similarly to the accepted voltage deviation on the LVAC grid [10], we select a ripple whose peak-to-peak value is less than 5% of the nominal DC voltage. For the AC side, an overall harmonic content  $THD_i \leq 8\%$  at rated power, with the constraints per current harmonic specified in Table 1, is recommended [11].

An efficiency  $\eta_{min}$  of at least 97 % is required [3], including semiconductors and passive components. This efficiency should be bi-directional and calculated for 100 %, 75 %, 50 % and 25 % of the rated power.

For *selectivity*, existing fuses in electrical substations have a response time of a few seconds to hundreds of milliseconds [6] which is too slow for their use with power electronics. Therefore, we assume here that a dedicated protection device is implemented, with a maximum cut-off time given by,

$$t_{trip,max} = e^{15.38 \left(\frac{l_d}{l_n} - 1\right)^{-0.5309}} \tag{1}$$

where  $I_a$  [A] is the estimated fault current in steady state and  $I_n$ [A] the nominal current. Due to the specific behavior of a VSC during a short circuit [4], [12], the steady state fault current is almost perfectly sinusoidal. Its RMS value  $I_d$  can be estimated by,

$$I_{d} = \frac{V}{\sqrt{\frac{2}{3}(2r_{DC}l_{fault} + R_{d}) + R_{L})^{2}} + (\frac{4}{3}x_{DC}l_{fault} + X)^{2}}$$

(2)

where V is the phase to neutral RMS voltage,  $r_{DC}$  is the cable resistance per unit length,  $l_{fault}$  is the fault distance from the feeder,  $R_d$  is the fault resistance,  $R_L$  is the tie reactor resistance,  $x_{DC}$  is the cable reactance per unit length, and X is the tie reactor reactance.

Table 2: LVAC and LVDC grid parameters

| Transformer                         |               |  |  |  |

|-------------------------------------|---------------|--|--|--|

| Primary voltage                     | 20 kV L-L RMS |  |  |  |

| Secondary voltage                   | 400 V L-L RMS |  |  |  |

| Short-circuit voltage               | 4 %           |  |  |  |

| DC Cable [22]                       |               |  |  |  |

| Resistance per unit length $r_{DC}$ | 0.124 Ω/km    |  |  |  |

| Reactance per unit length $x_{DC}$  | 0.071 Ω/km    |  |  |  |

| Length                              | 600 m         |  |  |  |

| Fault                               |               |  |  |  |

| Location $l_{fault}$                | 0 – 600 m     |  |  |  |

| Starting time $t_{fault}$           | 0 - 20  ms    |  |  |  |

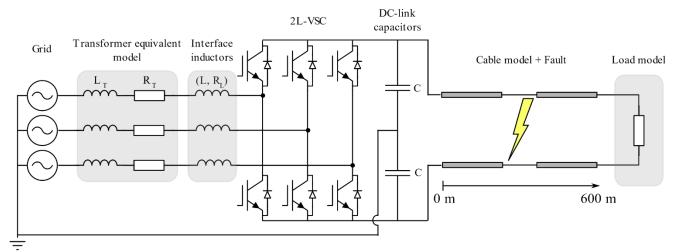

Figure 2: Circuit under study: grid, step-down transformer of the substation, 2-level voltage source converter with its tie reactor and DC-link capacitors and the DC grid.

CIRED 2023 2/5

| Impedance      | 1 mΩ  |  |  |  |

|----------------|-------|--|--|--|

| Resistive Load |       |  |  |  |

| Power          | 20 kW |  |  |  |

#### **Grid definition**

The parameters of the studied distribution grid are summarized in Table 2. It is assumed that existing LVAC cables are reused [13] with a TN-S configuration for the LVDC grid. The DC-link mid-point is grounded at the same point as the star coupled transformer, due to space limitations in a substation.

#### **Converter definition**

Because of its low number of semiconductors and simplicity, a two-level converter (2L-VSC) is considered. It is interfaced to the LVAC grid with a tie reactor, as illustrated in Figure 2. The DC-link capacitors consist of two capacitors in series.

#### SIZING METHODOLOGY

The following paragraphs detail the different steps of the converter sizing process.

#### **Module selection**

Due to the large number of available products, we focus on fully integrated 2L-VSCs, also referred to as "sixpack" which are cheaper for the same function.

For each reference, we extract the module cost and its datasheet parameters: diode and IGBT switching losses and conduction losses, junction thermal model, diode voltage threshold, diode conduction resistance, diode thermal stress  $i^2t_{max}$  and maximum steady-state junction temperature  $T_{j,max}$ . The commutation losses depend on the driver gate resistance. For modules under 150 A, there is usually no integrated driver. In that case, the gate resistance is assumed to be equal to  $10~\Omega$ . For modules over 150 A, we use the resistance value of the integrated driver. The selection of the switching frequency is left to the user's discretion but must stay within the range of the driver and module capabilities.

#### **Capacitor selection**

The pole-to-pole short circuit is the most critical fault for a LVDC grid: it results in a sharp increase in current and a drop in DC voltage. However, the voltage can become negative [4], [7] and damage electrolytic capacitors, which can only accept a voltage reversal of 1 to 1.5 V [14]. To overcome this issue, film capacitors should be used. The capacitors are chosen from the C44U 900 V series. For each reference, the capacitance and equivalent series resistance (ESR) are extracted.

#### **Inductance selection**

With large fault currents, the magnetic core of the coil could saturate, decreasing its inductance. This behavior leads to a further increase in the fault current from the grid,

as illustrated by equation (2). To avoid this, air-core coils are used.

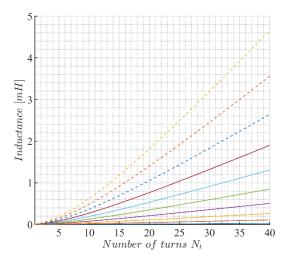

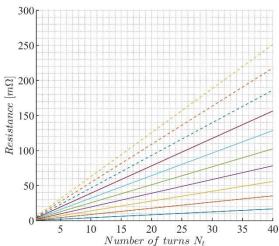

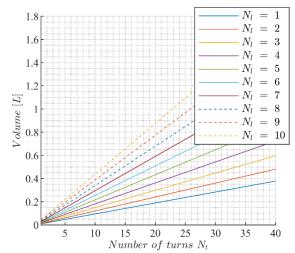

Figure 3: Evolution of inductance, resistance and volume of a circular air core coil according to the number of turns and layers, assuming the use of a AWG 7 wire and an internal diameter of 50 mm.

We consider a circular dry-type air-core copper coil. To

CIRED 2023 3/5

choose the wire diameter, a first estimation can be made based on the steady-state current. Based on the American Wire Gauge (AWG) recommendations, a wire of 3.6 mm [16], accepting 30 A RMS, should be chosen to avoid overheating at the rated current. This conductor, and in particular its insulation, must also be able to withstand transient short circuit currents. To validate the selection of the conductor, the empirical equation (3) must be validated [17].

$$I_d \le A \sqrt{\frac{0.0297}{\Delta t} log\left(\frac{T_2 + 234}{T_1 + 234}\right)}$$

(3)

where  $T_1$  [°C] is the initial temperature of the wire,  $T_2$  [°C] is the maximal temperature acceptable by the insulation,  $\Delta t$  [s] is the duration of the fault and A [ $m^2$ ] is the section of the wire. These parameters are set to 70 °C, 150 °C, 1 s and 10 mm<sup>2</sup>, respectively. The maximal temperature is due to the use of varnished conductors [17]. By defining the number of turns  $N_t$ , the number of layers  $N_l$ , the internal diameter of the coil  $D_{int}$  and the wire diameter  $d_w$ , we calculate its parameters using the equations of [15]: inductance L, resistance  $R_L$  and volume. The Figure 3 shows the result of this sizing process, considering an internal diameter of 50 mm. For a given inductance value, the duplet  $(N_t, N_l)$  that minimizes the volume is selected chosen.

Such air-core inductors are usually custom-made, so there is no cost data available. Based on our experience, we assume that the cost  $C_L$  is expressed as,  $C_L = 4.22 X_L I_n^2$

$$C_L = 4.22 \, X_L I_n^{\ 2} \tag{4}$$

where  $X_L[\Omega]$  is the inductor reactance at 50 Hz and  $I_n[A]$ is the inductor nominal current.

#### **Validation**

To validate the chosen sizing according to the above constraints, two PLECS simulation sequences are performed. The first one simulates the steady state operation of the converter. It aims to validate the power quality and efficiency criteria. Note that we consider openloop operation to speed up the computing time, while considering that closed-loop could further improve the performance. The temperature of each diode and each IGBT is monitored and must remain below  $0.8T_{j,max}$ .

The second sequence simulates the transient operation of the converter feeding a DC load, during a pole-to-pole short circuit. It aims to validate the selectivity criterion. For each diode, the thermal stress  $i_D^2 t$  is calculated for different fault locations and starting times, and compared to its datasheet value  $i_D^2 t_{max}$ . The sizing is deemed correct when,

$$\int_{0}^{t_{trip,max}} i_{D}(t, l_{fault}, t_{fault})^{2} dt \leq i_{D}^{2} t_{max}$$

(5)

#### **RESULTS & DISCUSSION**

Using the methodology described above, a first sizing of the converter is carried out. First considering only the power quality and efficiency criteria. The resulting sizing #A is summarized in the first column of Table 2. Then considering the selectivity criterion too. The resulting sizing #B is summarized in the second column of Table 2.

For the sizing #A, a module having a nominal current of  $1.7I_n$  is necessary in order to respect the efficiency criteria. Note that the tie reactor can handle large currents (Eq. (3) is satisfied) but the modules cannot (Eq. (5) is not satisfied). Therefore, the tie reactor is oversized. An ironcore tie reactor could be used instead, which could result in an even less expensive alternative [18].

For the sizing #B, in order to meet the selectivity criteria, it is necessary to select the module having the largest nominal current, corresponding to  $15I_n$ . This represents an 800% increase compared to #A, resulting in a ~700% increase in the module cost. However, this modification is not sufficient to meet the selectivity criterion. This is illustrated in Figure 4: for an inductance of 1.56 mH, even for a 450 A module, the maximum thermal stress time can be smaller than the protection cut-off time when the fault is located near the feeder. To meet the selectivity criterion, one needs to increase the inductance to 2.08 mH. This modification results in higher losses which are nevertheless compensated by a reduction of the switching frequency. At the end, the selectivity constraint results in a 66% increase in the total cost of the converter.

Table 3: Summary of the sizings of 2L-VSC for LVDC grids

|                             | # <b>A</b>      | #B       | #C        |  |

|-----------------------------|-----------------|----------|-----------|--|

| Power                       | <b>√</b>        | <b>√</b> | <b>√</b>  |  |

| quality                     |                 |          |           |  |

| Efficiency                  | ✓               | ✓        | ✓         |  |

| Selectivity                 | ×               | ✓        | ✓         |  |

| Topology                    | Sixpack         | Sixpack  | Dual      |  |

| Module                      | FS50R12K        | FS450R12 | IFF600B12 |  |

|                             | T3G             | OE4      | ME4P      |  |

| $I_n[A]$                    | 50              | 450      | 600       |  |

| $C_{module}[\in]$           | 117             | 803      | 3×388     |  |

| $f_{sw}[kHz]$               | 12              | 8        | 11        |  |

| $THD_i$ [%]                 | 7.04            | 5.16     | 7.8       |  |

| $\eta_{min}$ [%]            | 97.06           | 97.1     | 97.06     |  |

| Capacitor                   | C44UOGT7450M34K |          |           |  |

| L[mH]                       | 1.56            | 2.08     | 1.56      |  |

| $R_L[m\Omega]$              | 78              | 95       | 78        |  |

| <i>C<sub>L</sub></i> [€]    | 1861            | 2481     | 1861      |  |

| <i>C</i> <sub>tot</sub> [€] | 1978            | 3284     | 3025      |  |

In order to keep the sizing #A inductance value, while meeting the selectivity criteria, it is necessary to use "dual" modules, i.e., modules containing only one arm of the converter. In contrast to the "sixpack" topologies, these modules have a higher current rating (up to 900 A) and use newer semiconductor technologies. The resulting sizing #C is summarized in the third column of Table 2. This

**CIRED 2023** 4/5

results in an increase of 45% in the cost of the modules compared to the sizing #B. Compared to sizing #B and #A, the total cost is decreased by 8 % and augmented by 35 % respectively.

Figure 4: Simulation results for 2L-VSC with a 1.56 mH tie reactor. Maximum module thermal stress time as a function of the fault location, for different starting times. The dotted lines correspond to modules of 50 A (red), 100 A (blue), 150 A (green), 200 A (magenta), 300 A (cyan) and 450 A module (black). The continuous line represents the maximum protection cut-off time.

#### **CONCLUSION**

This paper highlights the need to take into account the grid constraints, especially selectivity, when sizing interface converters for LVDC grids. First, because of the DC short-circuit behavior, it is required to use specific passive components, such as film capacitors and air-core inductors. Then, because the thermal stresses are severe, the converter must be strongly oversized (at least 15 times the nominal current for the modules). These results may prompt converter manufacturers to increase the thermal stress of their module or to propose new resilient topologies.

#### REFERENCES

- [1] J. J. Justo, F. Mwasilu, J. Lee, and J.-W. Jung, 'AC-microgrids versus DC-microgrids with distributed energy resources: A review', *Renewable and Sustainable Energy Reviews*, vol. 24, pp. 387–405, Aug. 2013, doi: 10.101m6/j.rser.2013.03.067.

- [2] K. Smith, D. Wang, A. Emhemed, S. Galloway, and G. Burt, 'Overview paper on: low voltage direct current (LVDC) distribution system standards', p. 24.

- [3] J. E. Huber and J. W. Kolar, 'Applicability of Solid-State Transformers in Today's and Future Distribution Grids', *IEEE TRANSACTIONS ON SMART GRID*, vol. 10, no. 1, p. 10, 2019.

- [4] S.-M. Xue and C. Liu, 'Line-to-Line Fault Analysis and Location in a VSC-Based Low-Voltage DC Distribution Network', *Energies*, vol. 11, no. 3, p.

- 536, Mar. 2018, doi: 10.3390/en11030536.

- [5] Y. Pelenc, 'Interruption des circuits alimentés en courant continu', p. 18.

- [6] R. Rodrigues, Y. Du, A. Antoniazzi, and P. Cairoli, 'A Review of Solid-State Circuit Breakers', *IEEE Trans. Power Electron.*, vol. 36, no. 1, pp. 364–377, Jan. 2021, doi: 10.1109/TPEL.2020.3003358.

- [7] S. Ravyts, G. V. den Broeck, L. Hallemans, M. D. Vecchia, and J. Driesen, 'Fuse-Based Short-Circuit Protection of Converter Controlled Low-Voltage DC Grids', *IEEE Trans. Power Electron.*, vol. 35, no. 11, pp. 11694–11706, Nov. 2020, doi: 10.1109/TPEL.2020.2988087.

- [8] EATON, 'Fusible Overcurrent Protection for DC Applications'. 2020.

- [9] Bussman Series, 'Protecting semiconductors with high speed fuses'. Jun. 2016.

- [10] Direction Technique d'Enedis, 'Principes d'étude et de développement du réseau pour le raccordement des clients', Enedis, Enedis-PRO-RES\_43E, Aug. 2019.

- [11] 'IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems', IEEE. doi: 10.1109/IEEESTD.2014.6826459.

- [12] J. Yang, J. E. Fletcher, and J. O'Reilly, 'Short-Circuit and Ground Fault Analyses and Location in VSC-Based DC Network Cables', *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3827–3837, Oct. 2012, doi: 10.1109/TIE.2011.2162712.

- [13] Stephan Rupp, Sebastian Krahmer, Robert Adam, Karsten Backhaus, Christian Hildmann, and Matthias Nilges, 'Conversion of Existing AC into DC Cable Links in Distribution Grids Benefits and Challenges', presented at the ETG Kongress, 2021.

- [14] G. Mouriès, 'Condensateurs utilisés en électronique de puissance', *Conversion de l'énergie électrique*, Aug. 2015, doi: 10.51257/a-v1-d3010.

- [15] Maxwell, James Clerk, A Treatise on Electricity and Magnetism, Third., vol. 2. Dover, 1954.

- [16] Surya Santoso and H. Wayne Beaty, Standard Handbook for Electrical Engineers, 17th ed. McGraw-Hill Education, 2018.

- [17] EATON, 'Component Protection Wire & Cable'.

- [18] R. Burkart and J. W. Kolar, 'Component cost models for multi-objective optimizations of switched-mode power converters', in 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, Sep. 2013, pp. 2139–2146. doi: 10.1109/ECCE.2013.6646971.

CIRED 2023 5/5