# Full-SiC Single-Chip Buck and Boost MOSFET-JBS Converters for Ultimate Efficient Power Vertical Integration

Ralph Makhoul, Abdelhakim Bourennane, Luong Viêt Phung, Frédéric Richardeau, Mihai Lazar, Nour Beydoun, Sergueï Kostcheev, Philippe Godignon, Dominique Planson, Hervé Morel, et al.

#### ▶ To cite this version:

Ralph Makhoul, Abdelhakim Bourennane, Luong Viêt Phung, Frédéric Richardeau, Mihai Lazar, et al.. Full-SiC Single-Chip Buck and Boost MOSFET-JBS Converters for Ultimate Efficient Power Vertical Integration. IEEE 30th International Conference Mixed Design of Integrated Circuits and Systems, Institute of Computer Science of AGH University of Science and Technology, Jun 2023, Kraków, Poland. https://www.mixdes.org/Mixdes3/, 10.23919/MIXDES58562.2023.10203213. hal-04147862

### HAL Id: hal-04147862 https://hal.science/hal-04147862v1

Submitted on 1 Jul 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Full-SiC Single-Chip Buck and Boost MOSFET-JBS Converters for Ultimate Efficient Power Vertical Integration

Ralph Makhoul<sup>(1,2)</sup>, Abdelhakim Bourennane<sup>(1)</sup>, Luong Viêt Phung<sup>(2)</sup>), Frédéric Richardeau<sup>(3)</sup>, Mihai Lazar<sup>(4)</sup>, Nour Beydoun<sup>(4)</sup>, Sergueï Kostcheev<sup>(4)</sup>, Philippe Godignon<sup>(5)</sup>, Dominique Planson<sup>(2)</sup>, Hervé Morel<sup>(2)</sup>, David Bourrier<sup>(1)</sup>

(1)LAAS-CNRS, University of Toulouse, CNRS, UPS, Toulouse, France

(2) Univ Lyon, INSA Lyon, Université Claude Bernard Lyon 1, Ecole Centrale de Lyon, CNRS, Ampère, UMR5005, 69621 Villeurbanne, France

(3)University of Toulouse, CNRS, INPT, UPS, Toulouse, France (4)University of Technology of Troyes, 12 rue Marie Curie, 10004 Troyes, France (5)IMB-CNM, Campus UAB (08193) Bellatera, Spain

Abstract— This paper aims at demonstrating the relevance of a new design perimeter for power switching cells through a monolithic vertical integration approach on a multi-terminal power chip with Wide-Band Gap material such as 4H silicon carbide (SiC). Multi-terminal monolithic architectures making use quasi-only of vertical unipolar switch (VDMOS) and JBS diode architecture within the context of a 600V/10A full integration of switching cells on 4H-SiC chips are proposed and validated through Sentaurus™ 2D numerical simulations. The key method to etch and to fill the metallic via neededto connect the VDMOS and the JBS from top to back side of the SiC wafer is presented. The first optimization of the electroplating process resulted in a Ni metal layer of about 5µm thick.

*Keywords*—Power switching cells; monolithic; VDMOS; JBS diode; 2D simulations; metallic via; electroplating process

#### I. INTRODUCTION

Silicon carbide (SiC) vertical power metal-oxidesemiconductor field-effect transistors (VDMOS) are of great interest since they are unipolar gate-controlled switches with high blocking voltage capability, low specific on-resistance and high frequency operation. With the growing industrial maturity of SiC VDMOS and their multi-sectorial widespread diffusion into the field of critical embedded power systems, there is a growing interest for the monolithic integration of dedicated power conversion functions in SiC dies [1]. As compared to the hybrid multi-chip integration approach, the monolithic integration offers reduced costs and manufacturing time through optimizing the number of steps within a single technology fab-chain. However, due to the chip size capability, monolithic integration remains targeted to low current ratings. Regarding high-performance applications, integration aims at minimizing the parasitic elements, resulting from the external interconnection wiring of different chips. The impact of these circuit parasitics becomes critical at higher switching frequencies as they can lead to unwanted oscillations, which degrade system performance and can damage devices. For instance, the parasitic inductances induce high-voltage overshoot during the switch turn-off that not only

adds electrical stress to the power dies but also lead to an increase of switching losses that degrades the overall efficiency and reliability.

In medium power applications, the gradual progress that took place, during many decades, in the monolithic integration of power conversion functions in silicon wafers permitted the design and realization of a great number of monolithic power functions built around the power IGBT switch. For some of these power functions, it required the set-up of new specific technological process bricks that were integrated within the basic IGBT technological process-flow [2-3]. context, several monolithic power functions integrating auxiliary functions built around a single power IGBT switch such as protection functions [4-7] were reported. Moreover, regarding the monolithic integration of switching cells and generic power converter, within a minimum number of multiterminal Si-chips, original integration approaches that make use of RC-IGBTs were reported [8-9]. These new and original multi-terminal chips involve the two-chip [10], three-chip [11] and the ultimate monolithic single chip-converter [10].

Up to date, few works reported on the monolithic integration in silicon carbide of power functions with the VDMOS. Indeed, those works mainly focused on the monolithic integration of auxiliary low voltage functions within a single high voltage VDMOS. Among the reported works, one can find the P-Well monolithic functionalization of a series normally-on cascode JFET current limiter [12], integration of auto-adjust JFET with VDMOS [13], integration of VDMOS with a CMOS gate buffer [14-15]. However, none of these works addressed or discussed the design of a complete full-SiC basic switching cell.

The present paper explores the monolithic integration of new and original switching cells made of a JBS diode and a SiC VDMOS in series within a single chip. It proposes new multi-terminal architectures, validates their operating modes through 2D TCAD Sentaurus™ simulations and proposes technological process steps, compatible with a standard SiC VDMOS process, in order to consider their future practical

integration on SiC wafers. This monolithic integration is interesting in order to improve further the performance, reliability and cost reduction of the currently used discretedies-based switching cells. In addition, the design of medium power H-bridge converters will consequently require a minimum number of chips that will contribute to the improvement of the large-scale productivity of power converters and also to the reduction of their fabrication cost. Within this category, the monolithic integration on SiC material for the first time of two vertical VDMOS switches was reported in literature [16]. However, this last reference does not mention the extension of the proposed design to switching cell architecture. The current paper is organized as follows: in section II the design of a buck and a boost cells is depicted, in section III 2D TCAD Sentaurus™ simulations are performed and deeply analyzed, in section IV one of the major technological bricks of the concept is pre-evaluated, and finally in section V a conclusion is drawn.

#### II. CONCEPT OF INTEGRATION APPROACH

The main objective is to design new monolithic power switching cells on silicon carbide (4H-SiC). The proposed vertical monolithic integrated devices should support between 600 and 1200 V voltage and carry a nominal current of 25 A at 300 K.

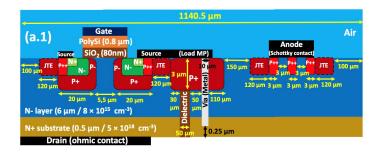

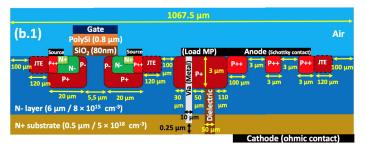

In this context, two original elementary 3-terminal chip versions of Buck-type and Boost-type switching cells have been designed. Each one of the elementary chips co-integrates on the same wafer an efficient JBS diode and a VDMOS transistor in series. The physical and geometrical parameters of the VDMOS and the JBS diode illustrated in Fig. 1 were imposed by the CNM laboratory (Centro Nacional de Microelectrónica) process flow, an experienced and recognized technology center in Europe for SiC technology for more than twenty years and in particular in SiC MOSFETs [17-18].

The technological challenges for the realization of each chip are mainly related to the realization of the full vertical insulation, which combines a deep trench in the die backside filled with a dielectric, and a deep P<sup>+</sup> implementation on the top side above this trench (Fig. 1). This insulation is essential to prevent any lateral current flow in both the N<sup>-</sup> drift layer and the N<sup>+</sup> substrate between the VDMOS-side and the JBS-side. A second challenge is the integration of the metal via, extending from the frontside of the chip to the backside N<sup>+</sup> substrate, through the drift layer. This metallic via provides the electrical interconnection between the midpoint (MP) of the switching cell and the back-side N<sup>+</sup> substrate (Fig. 1). So, the JBS cathode and the VDMOS source are fully internally connected to form a switching cell having an ultra-low stray inductance.

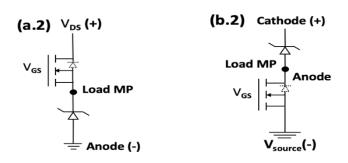

Fig. 1. (a) SiC VDMOS-JBS Buck-type switching cell concept: (a.1) Cross sectional view of the proposed 3-terminal chip with the different technological and geometrical parameters, (a.2) Simplified equivalent electrical circuit. (b) SiC VDMOS-JBS Boost-type switching cell concept: (b.1) Cross sectional view of the proposed elementary 3-terminal chip with the different technological and geometrical parameters, (b.2) Simplified equivalent electrical circuit.

## III. SENTAURUS $^{\text{TM}}$ MIXED MODE SIMULATION RESULTS

In this section, the operating modes of the two proposed monolithic structures were analyzed and validated by 2D Sentaurus™ simulations. Each switching cell was analyzed by observing the current densities, equipotential-lines and electric field distribution in each structure. The main objective is to see that when one section is in on-state and carries the imposed current, the other section is in off-state and withstand the applied voltage. The 2D numerical simulations are carried-out in mixed mode circuit – device using Sentaurus™ and at 300 K [19-20]. The thickness and the doping concentration of the drift region were chosen so that the devices can support a voltage higher than 600 V.

The simulation conditions correspond to a static state: when one section is in the on-state, the other must be in the off-state. A voltage of 600 V is applied and a current of 10 A simulates an ideal load modeled as a current source.

The technological parameters of the insulation area, consisting of an innovative deep trench and a deep P+ well located above this trench, have been chosen to withstand a voltage of 600 V and to prevent any lateral current flow (Fig. 1). These parameters are given in Fig. 1.

#### A. Buck-type switching cells

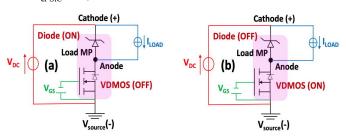

Fig. 1a) represents the 2D cross-sectional view of the elementary 3-pole chip of the Buck-type switching cells. Fig. 2 represents the equivalent electrical schematic of this switching cell.

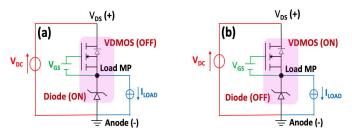

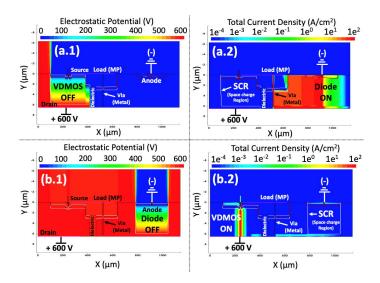

The first validation study on the Buck-type switching cell requires to set the VDMOS in the OFF-state and the diode in the ON-state (Fig. 2a). Fig. 3 gives the corresponding distribution of equipotential lines and current density within the elementary chip. In the cases a) and b), one can notice that the JBS diode is in ON-state and the VDMOS supports the voltage of 600 V. On the other hand, if the VDMOS is ON and the diode is OFF (Fig. 2b), the JBS diode supports a voltage of 600 V (Fig. 3b.1) and the VDMOS carries a current density of 100 A/cm² (Fig. 3b.2). In all cases the maximum electric field peak value inside the structures does not exceed 2.1 MV/cm which is lower than the critical electrical field  $E_{cr SiC} = 2.5$  MV/cm.

Fig. 2. Equivalent electrical schematic of the 3-terminal Buck-type switching cell at  $V_{DC}=600~V,~I_{LOAD}=10~A,~T_{CASE}=300~K;$  (a) VDMOS in the OFF-state and the diode in the ON-state at  $V_{GS}=0~V,$  (b) VDMOS in the ON-state and the diode in the OFF-state at  $V_{GS}=15~V.$

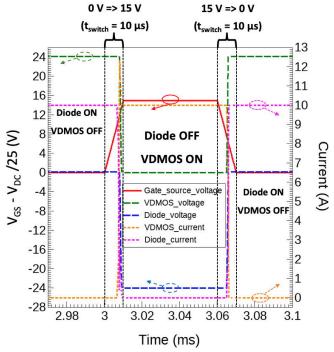

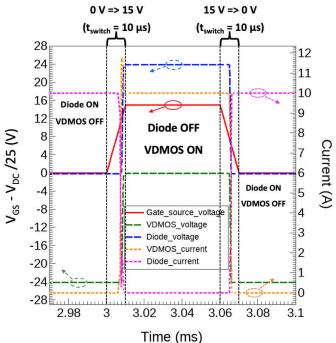

Fig. 4 shows the VDMOS drain-source and gate-source voltage/current waveforms, together with JBS anode-cathode voltage/current waveforms of the Buck-type switching cell. A voltage of 600 V is applied between the MOSFET drain and the JBS anode. A 10A load current is applied between the JBS anode and the midpoint (MP) which is connected to the metal via. An equivalent trapezoidal gate-source voltage was imposed from 0 to 15 V ( $V_{gs} > V_{th}$ ) with a switching time (T<sub>switch</sub>) of 10µs. This time was chosen to ease the convergence of the simulations and to reduce the computation time which resulted four times lower than for a usual switching time of the order of ns. The simulation of the turn-on and turn-off the VDMOS, and the observation of the different electrical parameters within the structure validate theproper functional operation of the Buck switching cell based on the JBS diode and the VDMOS.

Fig. 3. Equipotential lines and current density distribution in the Buck-type switching cell (X to Y ratio: 30). (a) VDMOS in the OFF-state and the diode in the ON-state: (a.1) equipotential line distribution, (a.2) current density distribution. (b) VDMOS in the ON-state and the diode in the OFF-state: (b.1) equipotential line distribution, (b.2) current density distribution. (Leakage current= 6  $\mu$ A) ( $E_{max\,SiC}$  = 2.1 MV/cm)

Fig. 4. VDMOS-part and JBS-part switching waveforms of the proposed 3-pole Buck-type switching cell at  $V_{DC}=600~V,\,I_{LOAD}=10~A,\,V_{GS~max}=15~V,\,T_{CASE}=300~K.$

#### B. Boost-type switching cells

Fig. 1b) represents the 2D cross-sectional view of the elementary 3-terminal chip of the Boost-type switching cell. Fig. 5 shows the simplified equivalent electrical schematics of this switching cell with the biasing conditions at 300 K used for the simulation.

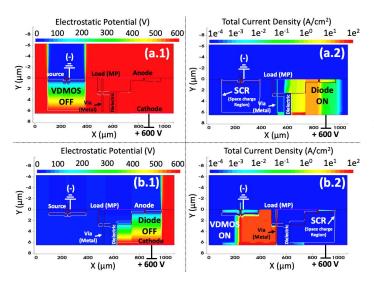

The first validation phase on the 3-terminal Boost-type switching cell requires to put the VDMOS in the OFF-state and the diode in the ON-state (Fig. 5a). According to Fig. 6, which represents the distribution of equipotential lines and the current density in the elementary chip, in the cases a) and b), one can see that the JBS diode is ON and the VDMOS support the desired voltage of 600V. On the other hand, if the VDMOS-part is ON and the diode-part is OFF (Fig. 5b), the JBS is blocked and supports a voltage of 600V (Fig. 6b.1) and the VDMOS carries a current density of 100 A/cm² (Fig. 6b.2). In all cases the maximum electric field peak value does not exceed 2.1 MV/cm which is lower than the critical electrical field  $E_{cr SiC} = 2.5$  MV/cm.

Fig. 5. Equivalent electrical schematic of the 3-terminal Boost-type switching cell at  $V_{\rm DC}=600$  V,  $I_{\rm LOAD}=10$  A,  $T_{\rm CASE}=300$  K: (a) VDMOS in the OFF-state and the diode in the ON-state at  $V_{\rm GS}=0$  V, (b) VDMOS in the ON-state and the diode in the OFF-state at  $V_{\rm GS}=15$  V

Fig. 6. Equipotential lines and current density distribution in the Boost-type switching cell (X to Y ratio: 30). (a) VDMOS in the OFF-state and the diode in the ON-state: (a.1) equipotential line distribution, (a.2) current density distribution. (b) VDMOS in the ON-state and the diode in the OFF-state: (b.1) equipotential line distribution, (b.2) current density distribution. (Leakage current=  $6 \mu A$ ) ( $E_{max \, SiC} = 2.1 \, \text{MV/cm}$ )

Fig. 7 shows the VDMOS drain-source and gate voltage/current waveforms, together with the JBS anodecathode waveforms of the Boost-type switching cell. A supply voltage of 600V is applied between the cathode and the source. A 10 A load current is applied between the diode cathode and the midpoint (MP) which is connected to the metal via. An equivalent trapezoidal gate-source voltage was imposed from 0 to 15 V ( $V_{\rm gs} > V_{\rm th}$ ) for a switching time of 10µs. As in Buck-

type topology case,  $T_{\rm switch} = 10 \mu s$  was chosen to facilitate the convergence of the simulations and to reduce the computation time. It can be seen that the proper turn-on then the turn-off the VDMOS, and the observation of the different electrical quantities within the structure validate the correct functional operation of the switching cell based on the JBS diode and the VDMOS for the elementary chip of the Buck-type switching cell

Fig. 7. VDMOS-part and JBS-part switching waveforms of the proposed 3-pole Boost-type switching cell at  $V_{DC}$  = 600 V,  $I_{LOAD}$  = 10 A,  $V_{GS\;max}$  = 15 V,  $T_{CASE}$  = 300 K.

#### IV. TECHNOLOGICAL BRICKS METAL VIA

In this last part, we highlight the major technological step needed to take the electrical contact from the front face through the epitaxial layer down to the substrate, which is essential to obtain the structures schematized in Fig. 1. We need to connect in series the JBS-cathode in back-side with the source-VDMOS in front side which is named load MP in Fig. 1. Therefore, to perform this embedded connection, we need to have conductive metal filling for the via connecting the upper side with the lower side. The metal tobe used to fill this via must be compatible with SiC technology.

In previous studies, Ni was already used as a mask for SiC etching, as well as metal for ohmic contact [21-22]. In our work we propose to use Ni both as a mask for SiC etching and to fill the via up to the surface of the wafer. To have a good Ni adhesion on the SiC surface, we relied on our previously reported process using the growth of Pd nanoparticles on the SiC surface before Ni electroplating [23].

#### A. Fluorinated Plasma Etching

Fluorinated plasma techniques have been employed to etch SiC using SF<sub>6</sub> gasses. In our etching procedure, we combine both reactive ions etching and plasma etching in order to have a high source of ions and to etch SiC deeply. Previous studies have been carried out to investigate the optimum parameters to have high etch rates and smooth etched surface [22]. Relying on these parameters, we used 10 sccm of SF<sub>6</sub> gasses, 1000 W/180W ICP/RIE at a pressure equal to 8 mtorr and a bias equal to -450V. These parameters allow getting higher energetic ions with minimum collision that allow to have a high-etching rate equal to  $0.6\mu m/min$  avoiding trenching and micromasking.

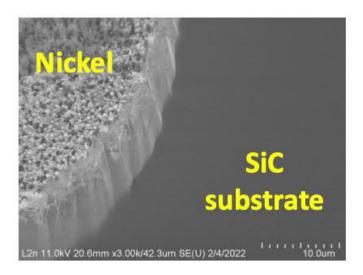

Fig. 8. Scanning electron microscopy (SEM) images of a  $10\mu m$  thickness SiC substrate etched with Ni mask to perform the metallic via between the back-side cathode JBS-part and the front-side VDMOS-part.

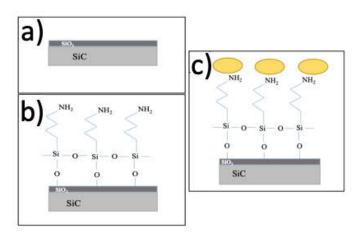

Fig. 9. Electroplating process to fill the via: a) SiO<sub>2</sub> natively presented on SiC, b) APTES functionalized SiC substrate, c) Palladium growth on APTES functionalized SiC.

Fig. 8 shows the scanning electron microscopy image of SiC substrate etched with fluorinated plasma using Ni as a mask, having an etching thickness equal to  $10\mu m$ .

This fluorinated plasma etching experiment allows us to reach the targeted via we need. Such a via etching need a thick layer of Ni metal, which is not possible to be done by e-beam evaporator. Hence, we used advanced electroplating process in order to investigate the thick Ni deposition on top of the SiC substrate [23].

#### B. SiC functionalization and Ni electroplating

Aminopropyl triethoxysilane (APTES) was grafted on the  $SiO_2$  thin layer natively present on the SiC surface. The APTES functionalized SiC was covered with a Pd precursor that allows Pd nanoparticles to grow on the surface as already described in our previous work[23] and shown in Fig. 9.

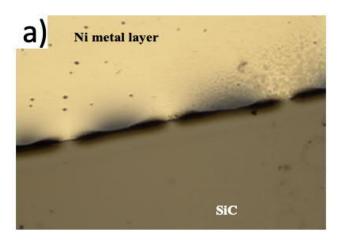

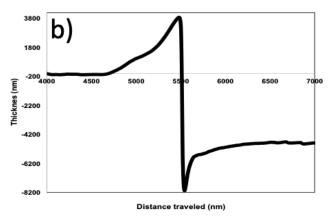

Fig. 10. a) optical image highlights the Ni electroplated layer on the SiC, b) The graph shows the Dektak $^{\text{TM}}$  Profiler measurement for the Ni metal layer performed.

After APTES functionalization and the growth of palladium on the surface of the functionalized SiC, a Ni electroplating process was applied. Concretely, the functionalized SiC was electroplated within a Ni sulfamate bath (plating cell from YAMAMOTO-MS $^{\text{TM}}$ ) at a temperature of 50°C and an applied current of 1.56A, the time of electroplating is 15 min.

The palladium treatment of the SiC substrate before Ni electroplating, allows a more compact and rigid Ni layer on the surface of the palladium treated SiC substrate compared to bare SiC substrate [21]. This electroplated Ni thick layer allows us

to have considerable etching depth [23]. In addition, we used this Ni electroplating method in order to obtain a thick layer of Ni metal in the vias.

Fig. 10 a) points out the micrometric layer of electroplated Ni metal layer on palladium activated SiC substrate. Graph in Fig. 10 b) gives out the thickness measurement of the Ni metal layer equal to approximately 5 µm. This preliminary result allows us to define a process to etch and to fill the via on the surface of the SiC wafer.

#### CONCLUSION

In this paper, a new design perimeter for power switching cells through VDMOS-JBS monolithic vertical integration approach on original multi-terminal SiC power chips is proposed. The operating modes of the 3-terminal Buck-type and Boost-type switching cells were validated using 2D Sentaurus<sup>TM</sup> mixed-mode simulations. Electrical insulation using a deep trench in the back side and a deep P+ implementation above this trench is introduced. For the embedded metallic via connecting the upper side with the lower side, a nickel electroplating process is suggested. This electrodeposition technique is proposed to have a considerable thickness to fill the via trenching on the upper side and therefore to form the switching cell. The first result shows a Ni metal layer of 5µm thick. This promising result allows us to carry-out the etching and filling of the via on the surface of the SiC wafer which is a key technological step to put forward this concept.

#### ACKNOWLEDGMENT

This national inter-lab research work received financial support from the French National Research Agency (ANR). The project name is "MUS2-IC" for Monolithic Ultimate power Switching cell in SIlicon Carbide (n° ANR-21-CE05-0005), over the period 2022 - 2025. This work was supported by LAAS-CNRS and NanoMat micro and nanotechnologies platforms, members of the Renatech french national network.

#### REFERENCES

- [1] Z. John Shen, SiC Research Beyond Power MOSFET: What's Next?, IEEE POWER ELECTRONICS MAGAZINE, June 2021

- [2] E. Imbernon et al., "Flexible technological process for functional integration," 2001 International Semiconductor Conference. CAS 2001 Proceedings (Cat. No.01TH8547), Sinaia, Romania, 2001, pp. 465-468 vol.2, doi: 10.1109/SMICND.2001.967506.

- A. Lale, A. Bourennane, F. Richardeau and H. Tahir, "Realization of a Monolithic Multi-Terminal Si-Power Chip Integrating a 2-Phase Rectifier Composed of Vertical PIN Diodes Insulated by Vertical P+ Walls," 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), Riga, Latvia, 2018, pp. P.1-P.6.

- [4] A. Lale, A. Bourennane, F. Richardeau and H. Tahir, "Realization of a Monolithic Multi-Terminal Si-Power Chip Integrating a 2-Phase Rectifier Composed of Vertical PIN Diodes Insulated by Vertical P+ Walls," 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), Riga, Latvia, 2018, pp. P.1-P.6.

- Y. Seki, Y. Harada, N. Iwamuro and N. Kumagai, "A new IGBT with a monolithic over-current protection circuit," Proceedings of the 6th

- International Symposium on Power Semiconductor Devices and Ics, Davos, Switzerland, 1994, pp. 31-35, doi: 10.1109/ISPSD.1994.583634.

- D. Flores et al., "Investigation on 3.3 kV-50 A IGBT protection against over-voltage conditions," 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 2009, pp. 1-7.

- [7] T. Yamazaki, Y. Seki, Y. Hoshi and N. Kumagai, "The IGBT with monolithic overvoltage protection circuit," [1993] Proceedings of the 5th International Symposium on Power Semiconductor Devices and ICs, USA, 1993, Monterey. CA. pp. 10.1109/ISPSD.1993.297104.

- P. Diaz Reigosa, M. Rahimo, R. Minamisawa and F. Iannuzzo, "Switching Stability Analysis of Paralleled RC-IGBTs With Snapback Effect," in IEEE Transactions on Electron Devices, vol. 68, no. 7, pp. 3429-3434, July 2021, doi: 10.1109/TED.2021.3081614.

- [9] A. Lale, A. Bourennane and F. Richardeau, "RC-IGBT-thyristor structure having trenches filled with dielectric on the backside: Physical analysis and application to the integration of a multiphase generic power converter using the "two-chip" approach," 2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Eurone). Geneva. Switzerland, 2015. pp. 10.1109/EPE.2015.7311704.

- [10] A. El Khadiry, A. Bourennane and F. Richardeau, "Multiphase Power Converter Integration in Si: Dual-Chip and Ultimate Monolithic Integrations," in IEEE Transactions on Electron Devices, vol. 63, no. 5, pp. 1977-1983, May 2016. doi:10.1109/TED.2016.2537212

- [11] A. Lale, N. Videau, A. Bourennane, F. Richardeau and S. Charlot, "Mixed monolithic-hybrid integration of multiphase power converter: Preliminary evaluation of the 3-chip integration concept", 2016 International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles & International Transportation Electrification Conference (IEEE ESARS-ITEC), Toulouse, 2016, pp. 1-

- [12] Series-connection of SiC normally-on JFETs, proceedings of the 27th International Symposium on Power Semiconductor Devices & IC's,

- [13] X. Li , X. Xu , Y. Wen, H. Wu, W.Chen , B.Zhang, "A Novel SiC MOSFET With Embedded Auto-Adjust JFET With Improved Short Circuit Performance", in IEEE Electron Devices Letters, vol. 42, no. 12, pp. 1751-1754, November 2021. 10.1109/LED.2021.3124526.

- [14] M. Barlow, S. Ahmed, A. Matt Francis, H. Alan Mantooth, "An Integrated SiC CMOS Gate Driver for Power Module Integration", IEEE Transcations on Power electronics, , vol. 34, no. 11, November 2019. 10.1109/TPEL.2019.2900324.

- [15] M. Okamoto, A. Yao, H. Sato, S. Harada, "First Demonstration of a Monolithic SiC Power IC Integrating a Vertical MOSFET with a CMOS Gate Buffer", The 33rd International Symposium on Power ICs (ISPSD), Semiconductor Devices and 2021. 10.23919/ISPSD50666.2021.9452262.

- [16] K.Han, A. Agarwal, A. Kanale, B. Baliga, S. Bhattacharya, T. Hsuan Cheng, D. Hopkins, V. Amarasinghe, J.C.W. Ransom, "Monolithic 4-Terminal 1.2 kV/20 A 4H-SiC Bi-Directional Field Effect Transistor (BiDFET) with Integrated JBS Diodes," 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 2020, pp. 242-245, doi: 10.1109/ISPSD46842.2020.9170064.

- [17] V. Soler, "Design and Process Development towards an Optimal 6.5 kV SiC Power MOSFET", Phd Thesis, Universitat Politècnica De Catalunya Barcelonatech, 2019.

- [18] M. Cabello, V. Soler, G; Rius, Josep Montserrat, J. Rebollo, P. Godignon, "Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review", Materials Science in Semiconductor Processing, vol. 78, May 2018, Pages 22-31

- [19] F. Chevalier, P. Brosselard, D. Tournier, G. Grosset, L. Dupuy, D. Planson, "Design and Characterization of a Novel Dual-Gate 3.3 Kv 4H-Sic JFET", Materials Science Forum, 2013, 740-742, pp.938-941. (10.4028/www.scientific.net/MSF.740-742.938). (hal-00803057)

- [20] J. Hasegawa, L. Pace, L. Viet Phung, M. Hatano, D. Planson, "Simulation-Based Study About the Lifetime and Incident Light Properties Dependence of the Optically Triggered 4H-SiC Thyristors

- Operation", IEEE Transactions on Electron Devices, 2017, 64 (3), pp.1203-1208. (10.1109/TED.2017.2657223). (hal-01636430)

- [21] N. Beydoun, M. Lazar, and X. Gassmann, "Surface engineering for SiC etching with Ni electroplating masks," Proc. Int. Semicond. Conf. CAS, vol. 2022-Octob, pp. 119–122, 2022, doi: 10.1109/CAS56377.2022.9934701.

- [22] M. Lazar, F. Enoch, F. Laariedh, D. Planson, and P. Brosselard, "Influence of the masking material and geometry on the 4H-SiC RIE etched surface state," Mater. Sci. Forum, vol. 679–680, no. August 2015, pp. 477–480, 2011, doi: 10.4028/www.scientific.net/MSF.679-680.477.

- [23] F. Zhao, A. Lim, Q. Tran, and C. F. Huang, "4H-sic electrostatic cantilever actuator released by photoelectrochemical etching and application for frequency mixing," 2015 Transducers 2015 18th Int. Conf. Solid-State Sensors, Actuators Microsystems, TRANSDUCERS 2015, no. c, pp. 2009–2012, 2015, doi: 10.1109/TRANSDUCERS.2015.7181349.