### **RF** Neuromorphic Spiking Sensor for Smart IoT Devices

Zalfa Jouni, Thomas Soupizet, Siqi Wang, A. Benlarbi-Delai, Pietro M.

Ferreira

### ▶ To cite this version:

Zalfa Jouni, Thomas Soupizet, Siqi Wang, A. Benlarbi-Delai, Pietro M. Ferreira. RF Neuromorphic Spiking Sensor for Smart IoT Devices. Analog Integrated Circuits and Signal Processing, inPress, 10.1007/s10470-023-02164-w. hal-04133969

### HAL Id: hal-04133969 https://hal.science/hal-04133969v1

Submitted on 28 Jul 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### RF neuromorphic spiking sensor for smart IoT devices

Zalfa Jouni<sup>1,2</sup> · Thomas Soupizet<sup>1,2</sup> · Siqi Wang<sup>1,2</sup> · Aziz Benlarbi-Delai<sup>1,2</sup> · Pietro M. Ferreira<sup>1,2</sup>

#### Abstract

For a ubiquitous sensing in Internet of Things (IoT), a large number of low-cost devices with ultra-low power massive communications are required. Heavy cloud computing pressure and low-intelligent traditional front-end hardware are major challenges for extending sensing in IoT applications. While state-of-the-art is focusing on the cloud-edge platform solutions and the optimization of the performed and transmitted data, this paper proposes an intelligent equipment hardware for smart IoT devices. A radiofrequency (RF) neuromorphic spiking sensor is implemented in BiCMOS 55 nm technology, comprising a wake-up receiver with a spiking pre-processing neural system (artificial synapses and neurons). The proposed system can identify bit patterns of two signals modulated using On–Off Keying at a frequency of 2.4 GHz received from two IoT receivers. Moreover, the system can recognize the orientation of the mobile IoT transmitter. This can be achieved based on the output spiking frequency of the neuron responsiveness over the difference between the input powers. Post-layout simulations demonstrate that the orientation of the source can be detected for various distances between the source and the two receivers. Significant performances are obtained with 1.1 nW of total power consumption and 0.7 fJ/conv of energy efficiency.

**Keywords** Neuromorphic computing  $\cdot$  IoT  $\cdot$  Sensory system  $\cdot$  Spiking neural network  $\cdot$  Artificial neuron  $\cdot$  Energy efficiency  $\cdot$  Ultra-low power

### 1 Introduction

The Internet of Things (IoT) is the vision of the world in which integrated circuits are embedded in everyday objects for collecting, processing, and exchanging useful information. The founding pillar of the IoT concept is the availability of low-cost devices with ultra-low power wireless communications capabilities [1]. Many proprietary wireless technologies [2] and efficient radio hardware [3] have gained much interest in the last few years. For example, LoRaWAN is a promising IoT technology that extends the battery lifetime through a highly efficient use of the radio hardware [4, 5]. The power consumption reduction comes from an intermittent use of the receiver hardware. To meet this requirement, a front-end hardware composed of two receivers is often used [1]. One is the main receiver with high performance, and it is kept in a deep sleep until it is needed. The other is the permanently-on ultra-low-power receiver, a.k.a wake-up receiver. Whenever it detects a communication request, it wakes up the main receiver to execute data.

With the advancements in low-power and miniature electronics, recent years have witnessed a dramatic increase of IoT applications covering a wide range of sensory areas, such as smart home, consumer electronic and industrial monitoring [6]. However, ubiquitous sensing for the IoT requires many more IoT sensors and sensory systems. Thus, the IoT network should be able to cope with a large number of devices connecting to it, which gives the signal processing a progressively substantial role in analyzing, summarizing, and protecting complex data

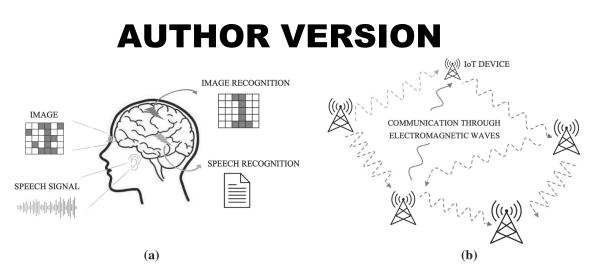

Fig. 1 Exploring Sensor Processing in: **a** the human brain, and in **b** IoT communication

exchanged by connected things [7]. Furthermore, since all the massive data is uploaded to the cloud platform, and with the gradual integration of information and communication technology in IoT, the system suffers from baffling problems. One may cite some of them: network congestion, poor data quality, large data processing delay, intensive computing tasks, and heavy cloud computing pressure [8].

At the same time, traditional front-end sensing equipment is limited by the actual low intelligent and highly consuming hardware. For example, in sensory systems, IoT devices often use protocols based on On–Off Keying (OOK) modulation [9]. Thus, when a device receives a signal, it knows the identity of communication of other devices without any additional information about the incoming signal or the localization of the device with whom it wants to communicate. Therefore, it sends electromagnetic waves in all space which lead to a high-power consumption. Facing all these problems, one solution could be achieved by the introduction of "smart" front-end hardware in IoT communications. Thus, the cloud platform will exchange less processed and analyzed information with an intelligent equipment, which saves power and achieves real-time performance.

To introduce the intelligence in electronic systems and by learning from the biological and physical characteristics of the neocortex system, researchers overcome the build-up of the Von Neuman bottleneck and the end of Moore's law by the introduction of neuromorphic computing approach [10]. As the second generation of artificial intelligence neural networks (ANNs), deep neural networks (DNNs) are rapidly evolving and widely used in many fields [11]. However, due to the large number of operations and computations, DNN can lead to significant power consumption. Therefore, spiking neural networks (SNNs), also known as the third generation of ANNs, greatly bridge the gap between ANNs and biological neural networks. Thanks to their capability to truly mimic the human brain, analog SNNs come to achieve high energy efficiency with low power hardware implementation.

To explore the sensory processing in the brain, neuromorphic engineers have focused on mimicking the retina and the cochlea (Fig. 1.). It is called neuromorphic sensory system [12]. However, IoT devices don't hear or see like the human brain. In sensory applications, IoT devices communicate through electromagnetic waves (Fig. 1b). Thus, a smart vision or audition in IoT requires an RF neuromorphic sensory system, which may drive a new generation of bioinspired signal processing for IoT. The authors have implemented a novel architecture using neuromorphic sensing for IoT communications, called neuromorphic enhanced wakeup radio (NWR) [13]. The proposed system consists of a wake-up radio followed by a neuromorphic pre-processing system (comprising basic blocks of SNNs, a synapse and a spiking neuron). The system can detect and identify bit patterns of a 2.4 GHz OOK-modulated signal. Moreover, the proposal can also observe the electromagnetic environment of IoT since it can recognize the RF input power based on the spiking frequency of the artificial neuron (eNeuron). The system consumes 1.2 nW and achieves an energy efficiency of 1.2 pJ/bit with a minimum detectable signal of - 29 dBm.

This paper extends the work already presented in [13] by proposing: (a) A neuromorphic enhanced wake-up radio (NWR) with two different types of eNeurons, the Moris-Lecar (ML) eNeuron (described in [13]) and the leaky integrate-and-fire (LIF) eNeuron; and (b) A RF neuromorphic spiking sensor (NSS) system. The NSS uses two NWR in a two-layer spiking neural network (SNN). The proposed NSS paves an innovative way to explore new paradigms suitable for a transmitter localization problem in IoT. NSS can estimate the relative position of two IoT receivers fixed at different distances from an IoT source. Thus, the proposal NSS can identify the orientation of the source based on the relation between the RF input power level ( $P_{RF}$ ) and the spiking frequency ( $f_{spike}$ ) of the eNeuron. Post-layout simulations

(PLS) are carried out to highlight both eNeurons (ML and LIF) figure-of-merits, and NSS simulation results validate its functionality with significant performances in terms of power consumption (in nW) and energy efficiency (in fJ/ conv). The proposed NSS is designed in the BiCMOS SiGe 55 nm technology.

This paper is organized as follows. Section 2 presents a literature review of wake-up receivers, analog spiking neural systems, and neuromorphic signal processing implementations. Proposed RF neuromorphic spiking sensor and each stage of it are presented in Sec. 3. In addition, it describes recent work of the NWR system [13] dealing with different types of eNeurons. Section 4 highlights PLS results of the NSS system. Finally, conclusions are drawn in Sect. 5.

### 2 State-of-the-art

This section can be divided in three main parts. Section 2.1 presents an overview of wake-up receivers implemented in low power radio communication followed by a comparison of different solutions in hardware. Section 2.2 describes the neuromorphic computing approach. It is limited to the analog implementation of spiking neural networks. A short state-of-the-art review of basic building blocks of the SNNs, spiking neurons (Sect 2.2.1) and synapses (Sect. 2.2.2) is then explored. Finally, Sect. 2.3 reveals different neuromorphic signal processing architectures presented in literature.

### 2.1 Wake-up radios

IoT offers many opportunities in smart physical objects combining artificial intelligence and signal processing in low-cost context-aware devices. For smart communications, IoT devices require low power consumption. A promising approach to dramatically reduce the power consumption is to use an ultra-low-power receiver, a.k.a wake-up receiver (WuR) [1]. Since its power consumption is several orders of magnitude lower than that of a traditional low-power radio, the WuR can be kept always on. In this setting, the main radio is kept in a deep sleep until it is needed.

For the WuR to operate effectively as a part of the larger system in a multi-user environment, it should consider many design points such as power consumption ( $P_{rms}$ ), minimum detectable signal ( $P_{mds}$ ), data rate (DR), and operating frequency ( $f_{RF}$ ). Energy efficiency is defined as  $E_{eff} = P_{rms}/DR$  (in J/bit). Designers tend to simplify WuRs enabling faster prototyping. Nevertheless, this is dependent on the modulation technique used and the choice of the operating frequency. Most WuRs implemented in hardware for sensor networks use a 2.4 GHz carrier frequency and OOK modulation [9].

Cheng et al. have proposed a wake-up receiver based on direct active RF detection [14]. At the operating frequency of 2.4 GHz with DR = 200 kbps, their RF detector achieves a  $P_{mds} = -50$  dBm while consuming 2.4  $\mu$ W. Besides, their receiver has an energy efficiency of 22.5 pJ/ bit. A wake-up receiver front-end is proposed in [9] with  $E_{eff} = 48$  pJ/bit. The proposal leads to an intrinsic bandpass characteristic that improves the signal-to-noise ratio. It is implemented for a 2.4 GHz band and a DR = 2.5 kbps and consumes 0.12  $\mu$ W with a  $P_{mds} = -48.5$  dBm. At 0.9 GHz and for a DR = 1 kbps, Karami et al. have designed a WuR with a  $P_{mds} = -26$  dBm and a low  $P_{rms} = 5.7$  nW [15]. Based on that,  $E_{eff} = 5.7$  pJ/bit is obtained.

Recently, Mangal et al. have designed a wake-up receiver with gate-biased self-mixers [16]. It consumes only 0.42 nW with an interesting  $P_{mds} = -79.1$  dBm. It achieves an  $E_{eff} = 4.2$  pJ/bit. However, it operates at  $f_{RF} = 434$  MHz with a DR = 0.1 kbps, which are considered as very low frequency and data rate for smart IoT communications. In similar environment, at 113.5 MHz and for a DR = 0.3 kbps, a fully integrated wake-up receiver is proposed in [17]. It is designed using an active rectifier for emerging event-driven low-average throughput applications. The proposal achieves a  $P_{mds} = -69$  dBm with a  $P_{rms} = 4.5$  nW.

Since the envelope detector is the part of the WuR operating in RF, it is usually the main contributor to power consumption. A simple demodulator can be adopted for that purpose, especially when the RF input is an OOK-modulated signal [9]. However, the minimum detectable signal by the receiver is limited by the quadratic non-linearity of such detectors [14]. This paper proposes a simple envelope detector, described in Sec. 3.1.

### 2.2 Analog spiking neuromorphic

Neuromorphic computing appeared in 90s to refer to a variety of brain-inspired computers, devices, and models that contrast Von Neuman architectures [10]. Inherent parallelism, real-time performance, speed in both operation and training, and small device footprint continue to be major motivations for the developments of neuromorphic hardware implementations. Spiking neural networks (SNNs) become among the most researched, in either analog or digital domain. The most distinct property of SNNs is that the information is transmitted as discrete spike events, also referred to as action potential [18]. In contrast to digital neuromorphic systems, analog solutions save significant power, thanks to their capability to faithfully mimic the physical properties of biological systems [19]. The neuromorphic hardware approach consists of a large-scale integration of silicon artificial spiking neurons (eNeurons) and synapses.

#### 2.2.1 Spiking neurons

As the fundamental component of a neural network, the neuron cell is vital to overall performance. Different models for spiking neurons represent their biological inspiration at different levels, which impacts the degrees of complexity, accuracy, and power consumption of hardware implementations. An overview of the types of neuron models implemented in hardware is detailed in [10]. Spiking eNeuron is often compared in the state-of-the-art by its output spiking frequency  $f_{spike}$ , its silicon area, and its power consumption  $P_{rms,N}$ . The energy efficiency of the eNeuron expressed as  $E_{eff,N} = P_{rms,N}/f_{spike}$  (J/spike) is often used as a figure-of-merit. In this paper, two models of eNeurons are explored: the Morris-Lecar (ML) eNeuron and the leaky-integrate-and-fire (LIF) eNeuron.

A. *ML eNeuron* The ML model is one of the simplest models to produce action potential and neural activity among the biological-plausible models. The ML model is described by two coupled first order differential equations. The first one models the evolution of the membrane potential and the second one models the activation of potassium current [20, 21]. ML eNeurons have recently been used in many SNNs implementations, such as performing a spiking modulator for an audio signal processing [22].

Sourikopolous et al. [23] have innovated biomimetic and simplified versions of the eNeuron model based on ML implementation. They have demonstrated an  $E_{eff,N} = 78.3$  fJ/ spike and a relatively constant period by reaching a maximum  $f_{spike}$  of 1.2 kHz for the biomimetic version of 200 µm<sup>2</sup> silicon area. The simplified version of 35 µm<sup>2</sup> silicon area achieves an  $E_{eff,N} = 4$  fJ/spike and a  $f_{spike} = 25$  kHz. Thus, a simplified version is better in speed but in spent of power consumption. Both circuits are implemented using TSMC 65 nm technology. A ML eNeuron of 98.61 µm<sup>2</sup> silicon area is designed in [22] with a high-firing rate to highlight a better  $E_{eff,N}$  trade-off. An  $E_{eff,N} = 1.95$  fJ/spike and a  $f_{spike} = 400$ kHz are obtained. The proposed system is designed in BiC-MOS 55 nm.

*B. LIF eNeuron* The LIF eNeuron is one of the most widely used in SNNs as powerful and efficient computational devices. Despite its abstraction of biological neuron into a small set of essential operations (delay, weighting, summation, temporal integration, and thresholding), the behavior of LIF model retains much of the richness found in biological neural systems [18]. Recently, LIF eNeurons have been used in hardware systems achieving tasks such as visual pattern recognition [24], ultra-fast optical implementation [25] and oriented edge spiking classification [26].

Danneville et al. have designed an ultra-low-power LIF eNeuron using Axon-Hillock topology [27]. Their LIF eNeuron is implemented in 65 nm CMOS technology and in a small surface area  $(34 \ \mu\text{m}^2)$  by using parasitic capacitors

as the membrane capacitance. Its spiking frequency is  $f_{spike} = 15.6$  kHz and its energy efficiency is  $E_{eff,N} = 2$  fJ/ spike. Recently, Besrour et al. have proposed a low power LIF eNeuron in 28 nm CMOS technology [28]. This LIF eNeuron achieves a much higher  $f_{spike} = 343$  kHz in the same silicon area as [27], but in the cost of power. Its energy consumption per event can reach 1.2 fJ/spike. Chen et al. have proposed a LIF eNeuron using TSMC 65 nm standard CMOS technology [11]. This eNeuron generates timedomain signals and achieves an  $E_{eff,N} = 3.5$  pJ/spike. The occupied area of the eNeuron is 126 µm<sup>2</sup> and its spiking frequency is 0.23 kHz.

In the previous paper [13], the authors have redesigned a ML eNeuron from [22] to implement a neuromorphic enhanced wake-up radio (NWR) system. The system has a significant dynamic range due to the high-spiking frequency achieved by this eNeuron. In this paper, both ML and LIF eNeurons are implemented in the NWR system, where compromise in terms of performance is explored.

### 2.2.2 Synapses

Synapses are essential modules in SNNs, as they are used to connect neurons together. Event-based synaptic circuits typically translate pre-synaptic voltage pulses of a pre-neuron into post-synaptic currents. These currents excite or inhibit the membrane potential of a post-neuron with a gain that corresponds to the synaptic weight [29]. Indiveri et al. have been one of the first to propose a silicon synaptic circuit in a spiking neural network. They have designed complex synapse blocks as an array implementation of current mirrors [29], where current mirror gains represent the synaptic weight. One of the synapse implementations focuses on unsupervised learning for synaptic weight updates through the spike-timing-dependent plasticity rules [10]. To build plastic synapses, emerging technologies such as memristors are used [30]. However, issues such as process variation and reliability are presented for unconventional technologies.

Recently, a novel design of weight synapse module based on frequency signals is proposed in [11]. This synapse consists mainly of a voltage-controlled ring oscillator operating under a leakage current, which is composed of a three-stage inverter. Danneville et al. have proposed two synapses [26]. The first design includes both excitatory and inhibitory synapses. It uses inverters to produce a long-synaptic current pulse, along with a transimpedance amplifier and a biased transistor to generate the post-synaptic current. The second design consists of an ultra-low-power synapse. It is similar to the previous design but including two additional inverters with an RC integrator. The latter is designed using an active load connected to a capacitor. In this paper, two types of synapses are proposed. First one is a transconductance

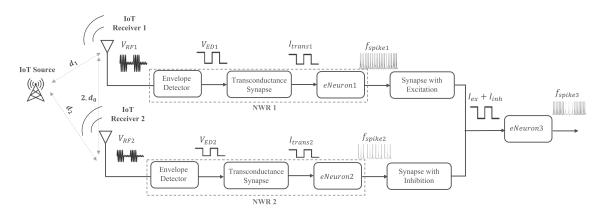

Fig. 2 Proposed Neuromorphic Spiking Sensor (NSS) system level composed of two NWR systems, excitatory and inhibitory synapses and LIF eNeurons. Illustration of the two IoT receivers and the IoT source is added with the appropriate distances

synapse and the second one is a synapse with dual functionality (excitatory and inhibitory).

### 2.3 Neuromorphic signal processing

Neuromorphic signal processing opens a wide range of applications such as motion control, image recognition, and sensory detection [12]. A neuromorphic hardware system for visual pattern recognition is designed in [24]. It consists of an artificial photoreceptor, which converts an image into voltage pulses, a memristor array for synaptic connections, and LIF eNeurons. Cassidy et al. have designed a wireless address event representation (AER) [31]. Cassidy's neuromorphic impulse radio introduced a distributed wireless cortex capability using a digital neuromorphic system (i.e., FPGA) and discrete RF components. A novel digital hardware of an efficient cochlea model is designed in [32]. It is based on non-linear dynamics of the asynchronous cellular automaton.

While state-of-the-art is focusing on digital-oriented solutions, a neuromorphic analog spiking modulator is implemented using artificial ML eNeurons with an 440 Hz input frequency for audio signal processing [22]. The proposed architecture aims at artificial cochlea applications coding an input-signal amplitude in  $f_{spike}$ . Lately, a hardware architecture for moving object detection is implemented on a Kintex 7 FPGA device [33]. Its operating frequency is 250 MHz.

Recently, a neuromorphic integrated sensing and communication with a dual-SNN architecture is proposed in [34]. In this paper, the same impulse radio signal is used for transmission of the data and radar detection of the presence target. This can be useful when a receiver that can operate using efficient analog hardware is implemented. Thus, in smart IoT communications, artificial sensing requires novel radio-frequency architectures for signal classification and real-time processing. However, RF architecture challenges in neuromorphic sensing hardware are not addressed in the state-of-the-art. In this paper, the work focuses on the feasibility of RF neuromorphic system-based applications. Thus, a novel architecture operating at 2.4 GHz is proposed.

### 3 Proposed RF neuromorphic spiking sensor

Traditional approaches to transmitter localization involve multiple sensors and complex signal processing algorithms, which can be computationally power-hungry. This work proposes a system that offers a more-energy-efficient and computationally simple solution based on the neuromorphic approach. Moreover, it enables the real-time detection of RF sources with minimal power consumption. Figure 2 illustrates the architecture of the proposed RF neuromorphic spiking sensor (NSS) system. The proposed system composes a front-end hardware for two IoT receivers. These receivers are supposed to be fixed, spaced by a distance  $2 * d_0$ , and at different distances  $d_1$  and  $d_2$  from a mobile IoT source.

Each IoT receiver collects a 2.4 GHz OOK-modulated signal. This signal on each IoT receiver is transferred to a neuromorphic enhanced wake-up radio (NWR) (Fig. 3b). At the output of the NWR, a frequency  $f_{spike}$  is generated and it is dependent on the input power  $P_{RF}$  of the received signal. Subsequently,  $f_{spike1}$  is converted for the first IoT receiver into an excitation current by an excitatory synapse (Fig. 5). Thus, it increases the  $f_{spike3}$  of the final neuron (LIF eNeuron3). However,  $f_{spike2}$  is converted for the second IoT receiver into an inhibition current by the inhibitory synapse (Fig. 5). Thus, it decreases the  $f_{spike3}$  of the final neuron.

Finally, the LIF eNeuron3 processes the sum of the two currents and generates an  $f_{spike3}$  that depends on the difference between the two received input powers at the two receivers ( $\Delta P = P_{RF2} - P_{RF1}$ ). A relation between  $\Delta P$  and the direction of the source is described in Sec. 3.4. Thus,

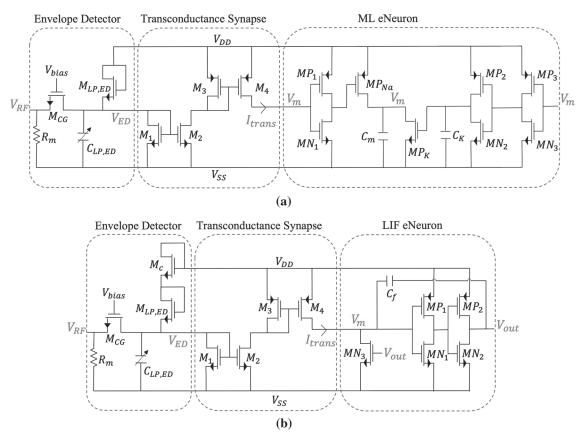

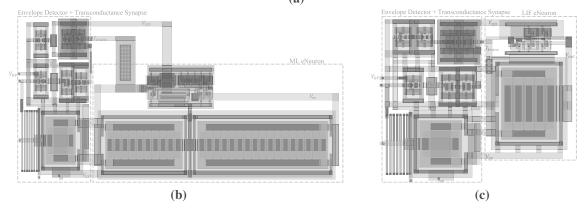

**Fig. 3** Neuromorphic Enhanced Wake-Up Radio **a** NWR with an ML eNeuron ( $V_{DD} = 100 \text{ mV}$  and  $V_{SS} = -100 \text{ mV}$ ), and **b** NWR with an LIF eNeuron ( $V_{DD} = 200 \text{ mV}$  and  $V_{SS} = 0 \text{ V}$ ). NWR with LIF eNeuron is the one used in NSS system

NSS will be able to detect the orientation of the source based on  $f_{spike3}$ .

NSS is designed in the BiCMOS SiGe 55 nm technology from ST Microelectronics, where all transistors are operating in weak-inversion region. In this section, a transistorlevel description of each block of NSS is presented. Firstly, Sec. 3.1 describes the NWR system. The authors detail the blocks composing the NWR system in [13], but with an ML eNeuron. This paper presents the NWR with both ML and LIF eNeurons and a compromise between both systems is explored. Secondly, Sec. 3.2 describes the proposed synapse with the dual functionality in the NSS. Thirdly, Sec. 3.3 recalls the design of both eNeurons. Finally, a description of NSS system in the electromagnetic environment (EM) is explored.

### 3.1 Neuromorphic enhanced wake-up radio

Two neuromorphic enhanced wake-up radio (NWR) are proposed in this section and described in the transistorlevel point of view. The first one is a NWR with a ML eNeuron, as illustrated in Fig. 3a. The second one is a NWR with a LIF eNeuron, as illustrated in Fig. 3b, and it is the one used to implement the NSS system, as shown in Fig. 2. The main difference between both NWR system is the supply voltage. ML eNeuron operates within  $V_{SS} = -100 \text{ mV}$  and  $V_{DD} = 100 \text{ mV}$ . However, LIF eNeuron operates between  $V_{SS} = 0 \text{ V}$  and  $V_{DD} = 200 \text{ mV}$ . For that, the operating voltage range for the NWR is adapted to correspond to each eNeuron.

The NWR system detects and identifies bit patterns of a 2.4 GHz OOK-modulated signal. It can also seize some information from the EM environment, since it generates an output spiking frequency ( $f_{spike}$ ) as a function of the RF input power  $P_{RF}$ . As shown in both figures (Fig. 3a and b), the NWR consists of a wake-up system with a neuromorphic pre-processing system. It is composed of an envelope detector (with a matching network), a transconductance synapse and an eNeuron (ML, LIF). The NWR system, as presented in Fig. 2, detects the RF input signal ( $V_{RF}$ ), demodulates it ( $V_{ED}$ ), and converts it into a synaptic current ( $I_{trans}$ ) connected to the eNeuron. This latter generates action potential, also known as spikes at a frequency  $f_{spike}$ .

A. Envelope detector To address the low-cost on-chip impedance matching challenge, a passive matching circuit is

chosen. A metallic  $R_m = 50 \Omega$  with low parasitic capacitance, at the expense of a higher input noise, is designed. Thus, a noisy envelope detector circuit leads to a high minimum detectable signal  $P_{mds}$ . However, eNeurons have proved to be robust against noisy signal [35]. In general, the RF envelope detector rectifies the incoming OOK-modulated signal  $V_{RF}$ and provides a baseband output  $V_{ED}$  equivalent to the envelope of the original signal. OOK modulation is usually adopted with simple RF envelope detection to achieve low-power consumption. Three popular forms of envelope detector configurations are described in literature [14], the common drain, the common source, and the common gate. In this paper, the chosen envelope detector is a common gate transistor ( $M_{CG}$ ) since it can achieve a maximal conversion gain [9].

The conversion gain of the envelope detector  $CG_{ED}$  is obtained from the ratio between the demodulated output signal  $V_{ED}$  and the RF input signal  $V_{RF}$ . In common gate small-signal analysis, the conversion gain of the envelope detector is expressed as:

$$CG_{ED} = \frac{V_{ED}}{V_{RF}} = \frac{i_{O}r_{O}}{V_{RF}} = \frac{I_{D}r_{o}V_{RF}}{4\phi_{T}^{2}}$$

(1)

where  $r_o$  is the intrinsic output impedance, and  $i_o$  is the demodulated output current represented by the second-order term of Taylor expansion as:

$$\dot{i}_o = \frac{\partial^2 I_D}{\partial V_S^2} \cdot \frac{V_S^2}{2} \tag{2}$$

and  $I_D$  is the drain current expressed in the weak inversion region as:

$$I_{D} = I_{s} \cdot e^{\frac{V_{G} - V_{T0}}{\eta \phi_{T}}} \cdot \left( e^{-\frac{V_{S}}{\phi_{T}}} - e^{-\frac{V_{D}}{\phi_{T}}} \right)$$

(3)

where  $I_s$  is the specific current;  $V_{T0}$  is the bias-independent threshold voltage for  $V_S = 0$ ;  $\eta$  is the subthreshold slope factor ( $\eta \approx 1.34$  for the 55 nm BiCMOS technology);  $\phi_T$  is the thermal voltage ( $kT/q \approx 26$  mV at 27 °C); and  $V_G$ ,  $V_D$ , and  $V_S$  are the voltages on the gate, the source and the drain of the transistor respectively.

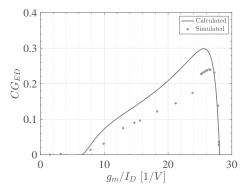

An example of a common gate transistor is studied in Fig. 4 to observe the behavior of its conversion gain as a function of  $g_m/I_D$  of the transistor. The objective behind that is to identify the behavior of the conversion gain in function of the operating region of the transistor. This gives an idea of the choice made to design the transistor. Figure 4 shows two curves: the blue line presents the conversion gain calculated from (1) and the red line presents the conversion gain obtained from PSS simulation.  $CG_{ED}$  is maximized for a  $g_m/I_D \approx 26$  1/V. It corresponds to a transistor operating in the weak inversion region. Therefore,  $M_{CG}$  is designed on

**Fig.4** Conversion gain of the envelope detector as a function of  $g_m/I_D$  for a common gate transistor; the blue line is the calculated one and the red line is the simulated one

this region using an external bias voltage  $V_{bias} = 300 \text{ mV}$ , L = 60 nm and W = 130 nm.

A low-pass filter is then implemented at the output of the envelope detector to remove the high-frequency components. It is composed of a capacitance  $C_{LP,ED}$  and a diode connected transistor  $M_{LP,ED}$ . As shown in Fig. 3b, for an NWR with a LIF eNeuron, an additional diode connected transistor  $M_c$  is implemented in cascode with  $M_1$ . The reason behind that is to maintain the stability of the demodulated voltage, since in the case of NWR with a LIF eNeuron, the supply voltage ( $V_{DD} = 200$  mV and  $V_{SS} = 0$  V) is not the same as in the case of NWR with ML eNeuron ( $V_{DD} = 100$  mV and  $V_{SS} = -100$  mV). To reduce the silicon area of the system, the chosen capacitance is the smallest varicap-based presented on the BiCMOS 55 nm technology. Dimensions are presented in Table 1.

B. Transconductance synapse In literature, the synapse is used in neural systems to translate pre-synaptic voltage spikes into post-synaptic currents to excite a following neuron [26]. In this paper, two types of synapses are designed. The first one is a transconductance synapse implemented in the NWR and used for the RF part of the system (detailed in this part). The second one is the synapse with dual functionality (excitation and inhibition), implemented in the NSS system (and used for the neural part (detailed in Sect. 3.2). The transconductance synapse is used to link between the RF part and the neural part of the system. This synapse converts the demodulated voltage at the output of the envelope detector  $V_{ED}$  into an excitation current  $I_{trans}$  with higher output impedance. This current excites the eNeuron according to the power levels  $P_{RF}$  of the RF input signal. The transconductance synapse is the same for both NWR proposed systems. As shown in Fig. 3, this synapse consists of two current mirrors NMOS and PMOS ( $M_1$  to  $M_4$ ). Synapse sizing depends on the following eNeuron (ML or LIF), thus the corresponding sizes are presented in Table 1.

*C. eNeurons* In this paper, the NWR system is proposed with two different eNeurons, the ML eNeuron (Fig. 3a) and

Table 1 Sizing of transistors in W×L (nm) and for capacitances in number of cells x unity capacitance ( $f\!F)$

| Envelope Detector       | and Transconduct   | ance Synapse           |                 |

|-------------------------|--------------------|------------------------|-----------------|

| M <sub>CG</sub>         | 135×60             | M <sub>c</sub>         | 135×60          |

| $C_{LP,ED}$             | $1 \times 8.5$     | $M_{LP,ED}$            | $135 \times 60$ |

| $M_1$                   | $405 \times 60$    | $M_2$                  | 135*×60         |

| $M_3$                   | 135*×60            | $M_4$                  | 135*×60         |

| Synapse                 |                    |                        |                 |

| $M_{LP,S}$              | 500×3000           | $C_{LP,S}$             | 1×11.9          |

| $M_{T,S}$               | 135×60             | $MP_{S1}$              | $135 \times 60$ |

| $MP_{S2}$               | 135×60             | $MP_{S3}$              | $135 \times 60$ |

| MN <sub>S1</sub>        | 135×60             | $MN_{S2}$              | $135 \times 60$ |

| Morris-Lecar (ML        | ) eNeuron          |                        |                 |

| $MP_1$                  | $135 \times 60$    | $MN_1 200 \times 60$   |                 |

| $MP_2 1200 \times 60$   |                    | $MN_2  135 \times 60$  |                 |

| $MP_3 200 \times 60$    |                    | $MN_{3} 135 \times 60$ |                 |

| $MP_{Na} 800 \times 60$ |                    | $MN_K 1500 \times 60$  |                 |

| $C_m 1 \times 9.83$     |                    | $C_{K} 1 \times 5.53$  |                 |

| Leaky Integrate-ar      | nd-Fire (LIF) eNeu | ron                    |                 |

| $MP_1 135 \times 65$    |                    | $MN_1 135 \times 65$   |                 |

| $MP_2 135 \times 65$    |                    | $MN_2  135 \times 65$  |                 |

| $MN_3$ 135 × 65         |                    | $C_f 1 \times 5.038$   |                 |

\*Width of the transistor multiplied by 3 for NWR with LIF eNeuron

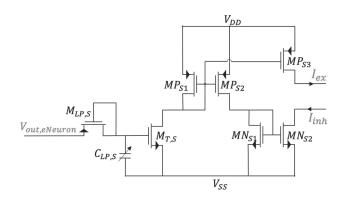

Fig. 5 Proposed Synapse with dual functionality: excitation and inhibition ( $V_{DD} = 200 \text{ mV}$  and  $V_{SS} = 0 \text{ V}$ )

the LIF eNeuron (Fig. 3b). Performance in terms of silicon area, power consumption, minimum detectable signal, and maximum spiking frequency depend on the implemented eNeuron in the NWR system. Both eNeurons design are presented in Sect. 3.3.

### 3.2 Synapses

It is well known that excitatory and inhibitory synapses are the brain's most abundant synapse types. In this paper, a synapse with dual functionality (excitation and inhibition) is proposed. By definition, the synapse receives the spiking membrane voltage of a pre-neuron and delivers a current to a post-neuron. The proposed synapse can behave as a current source by injecting a positive excitation current to the post-neuron. Thus, the spiking frequency of the post-neuron increases. In this case, the synapse is called an excitatory synapse. Otherwise, the proposed synapse can behave as a current sink by providing a negative inhibition current to the post-neuron. Thus, the spiking frequency of the post-neuron decreases. The synapse is then called an inhibitory synapse.

As shown in Fig. 2, the NSS system uses a small neural network, comprising two LIF eNeurons connected to a third LIF eNeuron through two synapses. The LIF eNeuron 1 had on its output a synapse with an excitatory purpose, it can then raise up the spiking frequency of the LIF eNeuron 3. However, the LIF eNeuron 2 had on its output a synapse with an inhibitory purpose, it can then decrease the spiking frequency of the LIF eNeuron 3. For both synapses implemented in NSS, one part (excitatory or inhibitory) is not used, which can increase the power consumption of the system. However, such circuit with dual functionality may be useful for a larger neural network where an eNeuron is connected to more than one eNeuron through synapses performing both tasks.

The proposed synapse is illustrated in Fig. 5. The synapse is composed of an RC filter followed by a transconductance and current mirrors. The filter is made up of a diode connected transistor  $(M_{LP,S})$  and a capacitance  $(C_{LP,S})$ , and it is used to import the information from the output voltage of the pre-neuron  $(V_{out})$ . The latter is then converted into a current through the transconductance transistor  $(M_{T,S})$ . Two current mirrors  $(MP_{S1}, MP_{S2}, MP_{S3} \text{ and } MN_{S1}, MN_{S2})$  are used to perform both excitation and inhibition purposes of the synapse. Thus, the proposed synapse delivers two synaptic currents, the excitation current  $(I_{ex})$  and the inhibition current  $(I_{inh})$ . During the rest of paper,  $I_{syn}$  is considered as a synaptic current that can be either an  $I_{ex}$  or an  $I_{inh}$ .

### 3.3 eNeurons

Morris-Lecar (ML) and leaky-integrate-and-fire (LIF) eNeurons are two different models implemented in hardware. In this paper, the proposal NSS is implemented using LIF eNeurons. This choice is discussed in Sec. 4 where a trade-off between performance of both eNeurons used in NWR subsystem is established.

### 3.3.1 ML eNeuron

The behavior behind the ML eNeuron is described by a ML model [23]. This model can be expressed by two first-order

differential equations. Thus, this model presents the dynamic nonlinear functions of ion channels that can produce the action potential (spikes) of the neuron. Three currents (sodium, potassium, and leakage) in a conductive structure can describe the functionality of these ions in a hardware implementation. The equations of ML model are given by:

$$C_{m} \frac{dV_{m}}{dt} = I_{syn} - G_{Na} m_{ss} (V_{m}) [V_{m} - V_{Na}] - G_{K} n (V - V_{K}) - G_{L} (V_{m} - V_{L})$$

(4)

$$\frac{dn}{dt} = \lambda (V_m) \left[ n_{ss} (V_m) - n \right]$$

<sup>(5)</sup>

where

$$m_{ss}(V_m) = \frac{1}{2} \left[ 1 + Tanh\left(\frac{V_m - V_1}{V_2}\right) \right]$$

(6)

$$n_{ss}(V_m) = \frac{1}{2} \left[ 1 + Tanh\left(\frac{V_m - V_3}{V_4}\right) \right]$$

(7)

$$\lambda(V_m) = \lambda_o Cosh\left(\frac{V_m - V_3}{2V_4}\right) \tag{8}$$

where  $V_m$  is the membrane voltage of the eNeuron;  $C_m$  its membrane capacitance;  $I_{syn}$  the input synaptic current,  $G_{Na,K,L}$  the sodium, potassium, and leakage conductances respectively;  $V_{Na,K,L}$  the potential generated by the sodium, potassium, and leakage channels;  $n_{ss}$  and  $m_{ss}$  are the potassium and the sodium gating variables;  $\lambda$  the constant rate of the potassium channel and  $V_{1,2,3,4}$  are adjustable parameters to tune steady state and time constant.

The transistor level of the ML eNeuron is shown in Fig. 3a. This biomimetic eNeuron has been redesigned from [22] with a high-firing rate to increase the RF system's dynamic range. Briefly, when an input synaptic current is applied, the membrane capacitance  $C_m$  is charged through  $MP_{Na}$  and discharged through  $MN_K$ . This causes a large but brief change in membrane potential  $(V_m)$ , which is referred to as action potentials (spikes) [23]. Indeed, transistors  $MP_{Na}$  and  $MN_K$  mimic the continuous exchange of Na and K ions through the cell membrane in brain activity. Two cascoded inverters  $MP_2/MN_2$  and  $MP_3/MN_3$  with  $MN_K$  implement a negative feedback loop and inverter  $MP_1/MN_1$  with  $MP_{Na}$  implement a positive feedback loop. eNeuron sizing is presented in Table 1.

#### 3.3.2 LIF eNeuron

LIF model is a part of less biological realistic category, however it produces enough complexity in its behavior to be useful in SNNs. Thus, it becomes promising for the

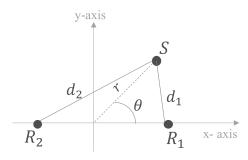

Fig. 6 Localization of the source S and the receivers  $R_1 \mbox{ and } R_2$  in the xy-plane

implementation of real-life applications [18]. A LIF eNeuron can be defined as a leaky integrator coupled with a trigger mechanism to elicit the typical response. It can be modeled by a simple behavior, such as charging and discharging of the membrane capacitance. When the input current integrated in the capacitance reaches a certain threshold, the LIF eNeuron fires by generating the spikes. Thus, a mathematical model can describe its functionality as

$$V_{out} = \frac{1}{C_m} \int i_{syn} \left( e^{\frac{V_{DD} - V_m}{\eta \phi_t}} - e^{\frac{-2V_m}{\eta \phi_t}} \right) dt \text{ for } V_m > V_{th}$$

$$V_{out} = 0 \text{ for } V_m < V_{th}$$

(9)

where  $V_{out}$  is the output voltage generated by the eNeuron,  $V_m$  is the membrane voltage,  $V_{th}$  is a threshold voltage;  $I_{syn}$  the input synaptic current,  $V_{DD}$  is the supply voltage,  $\eta$  is the subthreshold slope and  $\phi_T$  is the thermal voltage.

The transistor level of the LIF eNeuron is shown in Fig. 3b. The LIF eNeuron has been redesigned from [27] to achieve higher spiking frequency and better energy efficiency. The main idea behind the design of this eNeuron is that the parasitic capacitances are used as the membrane capacitance. Besides, this eNeuron can achieve low power consumption with low silicon area. As shown in Fig. 3b, when an input synaptic current is applied, the feedback capacitance  $C_f$  integrates this current (charging mechanism) which progressively increases the membrane voltage  $V_m$  of the eNeuron. When  $V_m$  increases until a threshold level, the inverters  $(MN_1, MP_1 \text{ and } MN_2, MP_2)$  are switched, and  $V_{out}$ rises to  $V_{DD}$ . At the same time, a feedback occurs through  $C_f$ (discharging mechanism) which increases the current flowing into  $MN_3$ . Thus,  $V_m$  decreases and the inverters switch again, forcing Vout to cross 0 V. Optimized eNeuron sizing is presented in Table 1.

### 3.4 Proposed NSS in EM environment

The NSS is a first-step solution for transmitter source localization problem in smart IoT communications. Figure 6 depicts the environment where NSS is implemented.

This scenario is modeled by two direct paths channel model. A system of the coordinate plane (x,y) is defined, where x-axis is the horizontal number line and y-axis is the vertical number line, and O is the origin of the plane. At its input, NSS uses two IoT antennas for receivers ( $R_1$ and  $R_2$ ) at distances  $d_1$  and  $d_2$  away from an IoT source (S). The receivers  $R_1$  and  $R_2$  are fixed points placed in x-axis and spaced by the same distance  $d_0$  from the origin ( $R_1$  in the positive part and  $R_2$  its symmetric). The source S is supposed to be a moving point in the positive plane. Thus, the angle  $\theta$  formed by the source with x-axis can take different values between 0 and  $\pi$ . The distance *r* between the source and the origin of the plane is also assumed to be variable. The proposal can estimate the orientation of the source S. This can be achieved based on the relation between the spiking frequency of the LIF eNeuron3  $(f_{spike3})$  and the difference between input powers received at  $R_1$  and  $R_2$  ( $\Delta P = P_{RF2} - P_{RF1}$ ).

Let it be assumed that the source transmits electromagnetic waves that propagate in free space conditions, and the source and the receivers are co-polarized antennas. Based on Friis equation, the available power at the output terminal of a receiver antenna  $R_i$  can be written as:

$$P_{RFi} = P_T G_T G_{Ri} \cdot \left(\frac{\lambda}{4\pi d_i}\right)^2 \tag{10}$$

where  $P_T$  is the power delivered to the source antenna at its input terminal;  $G_T$  is the gain of the source antenna in the direction of the receiver antenna;  $G_{Ri}$  is the gain of the receiver antenna in the direction of the source antenna *S*;  $d_i$ is the distance between the source and the receiver  $R_i$ ; and  $\lambda$ is the wavelength of the radiation given by  $\lambda = c/f_{RF}$  (*c* the speed of light and  $f_{RF}$  the frequency of the RF signal, in this paper  $f_{RF} = 2.4$  GHz). In the proposed NSS system, identical receivers  $R_1$  and  $R_2$  are considered. Thus, the receivers have the same gain  $G_{R1} = G_{R2} = G_R$ .

Therefore, the relation between the angle  $\theta$  and the input power difference  $\Delta P(\text{in dB})$  is given by:

$$\Delta P = P_{RF2} - P_{RF1} = 10 \log_{10} \left( \frac{r^2 + d_0^2 - 2rd_0 \cos \theta}{r^2 + d_0^2 + 2rd_0 \cos \theta} \right)$$

(11)

If the source is a point in y-axis ( $\theta = \pi/2$ ), both receivers are equally distant from the source and the power obtained at each receiver is the same. Besides, if the source is located at the positive part of x-axis, then  $\Delta P$  is a negative value and  $R_1$  is closer to the source than  $R_2$ , thus  $R_1$  receives a higher input power than  $R_2$ , and vice versa.

Once the spiking frequency  $f_{spike3}$  of the LIF eNeuron3 is obtained and  $\Delta P$  is derived (see Sec. 4.2), the angle  $\theta$  is then calculated from (11). Thus, NSS can detect the orientation of the source. As the resolution of the system is achieved for a 1 kHz of spiking frequency, the minimal difference between input powers  $\Delta P$  that can be detected by NSS is 1 dB (detailed in Sec. 4.2). Thus, the constraint of the system is expressed as  $d_1 > 1.12 d_2$ .

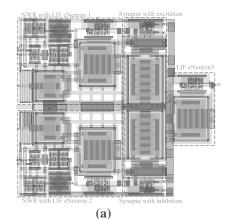

### 4 Results and discussion

A layout of the proposed NSS is shown in Fig. 7a, while a layout of the proposed NWR with ML eNeuron and with LIF eNeuron are presented in Fig. 7b and c respectively. Physical implementation was designed in the BiCMOS SiGe 55 nm technology from ST Microelectronics. The image rendering tool described in [36] is used for a high-quality layout illustration. The proposed NSS occupies  $18.3 \times 20.24 \ \mu m^2$ of silicon area and consumes 1.1 nW of power from a supply voltage equal to 200 mV. The area of the NWR with ML eNeuron is 9.8  $\times$  25.09  $\mu m^2$  and with LIF eNeuron is  $9.03 \times 10.52 \,\mu m^2$ . The NWR with ML eNeuron consumes 1.2 nW while it consumes 0.25 nW with LIF eNeuron. In this work, transmission lines and RF connections are not included in the reported area. Post-layout simulations (PLS) results are carried out to present the performances of both NWR systems (with ML and LIF eNeurons) in Sect. 4.1 and to demonstrate the NSS characteristics in Sect. 4.2. Thus, the system performance is validated using PSS combined with PAC, PNOISE, and PSP Virtuoso Spectre simulations.

### 4.1 NWR simulation results

The analysis of the NWR system is shown for both combination, with ML eNeuron and with LIF eNeuron, and divided into three parts. (4.1.1) To validate the functionality of the system,  $V_{RF}$ ,  $V_{ED}$ ,  $I_{trans}$  and  $f_{spike}$  are shown from a PLS for the bit '1' (4.1.2) The dependency of the system on the input power levels and bits '0' and '1' are then extracted from transient noise PLS. (4.1.3) The system performance is estimated as: the dynamic range, the minimal detectable signal, and the energy efficiency.

### 4.1.1 System validation for bit '1'

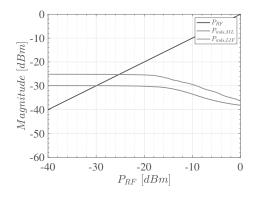

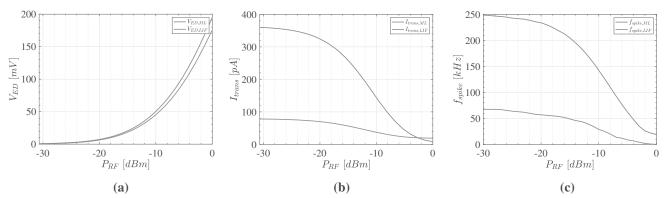

To validate the functionality of the NWR system for the bit '1', a 31-point  $P_{RF}$  sweep is considered from -30 dBm to 0 dBm for a 2.4 GHz input sinusoidal signal. Figure 9 illustrates the gain for the bit '1' at each stage of the system with ML and LIF eNeurons:  $V_{ED}$ ,  $I_{trans}$ , and  $f_{spike}$  versus  $P_{RF}$ .

A. Envelope detector In order to assess the performance of the envelope detector presented in Sect. 3.1-A, the minimum detectable signal  $P_{mds}$  (i.e., the sensitivity of the envelope detector) can be expressed as a function of the input power in dBm as:

**Fig. 7** Physical design of **a** NSS system having  $18.3 \times 20.24 \ \mu m^2$ , **b** NWR with ML eNeuron having  $9.8 \times 25.09 \ \mu m^2$ , **c** NWR with LIF eNeuron having  $9.03 \times 10.52 \ \mu m^2$ .

**Fig.8** Sensitivity of the envelope detector for NWR systems with both eNeurons (ML and LIF): the black line is the RF input power  $P_{RF}$  and its cross with the blue and orange lines are  $P_{mds,ML}$  and  $P_{mds,LIF}$  respectively

$$P_{mds} = NF_{tot} + 10logB - 174 + SNR_{min}$$

(12)

where  $NF_{tot}$  is the overall noise figure of the circuit, *B* is the bandwidth of the envelope detector, and  $SNR_{min}$  is the minimum signal-to-noise required by the OOK modulation for reliable detection. In this case,  $SNR_{min} = -12$  dB and B = 10 MHz are considered.

Figure 8 illustrates the  $P_{mds}$  of the NWR with ML eNeuron ( $P_{mds,ML}$ , blue line) and the NWR with LIF eNeuron  $P_{mds,LIF}$ , orange line). The sensitivity of the envelope detector is obtained from the intersection between the input power ( $P_{RF}$ , black line) and the minimum detectable signal from (12) ( $P_{mds,ML}$  and  $P_{mds,LIF}$ ). For the NWR with ML eNeuron, the envelope detector presents a sensitivity of -29 dBm. However, the envelope detector in the NWR with LIF eNeuron presents a drop into -25 dBm. Therefore, these values limit the gain of the overall system, as demonstrated later in Sect. 4.1.3.

Indeed, Fig. 9a represents the variation of the demodulated voltage  $V_{ED,ML}$  in NWR with ML eNeuron and the demodulated voltage  $V_{ED,LIF}$  in NWR with LIF eNeuron for a  $P_{RF}$  that varies from -30 dBm to 0 dBm. One may notice that the  $P_{RF}$  sweep highlights the  $P_{mds,ML} = -29$  dBm and the  $P_{mds,LIF} = -25$  dBm.

B. Transconductance synapse The exponential relation of  $V_{ED}$  with the input power  $P_{RF}$  shown in Fig. 9a for the bit '1', in addition to the two current mirrors, lead to a decrement dependency of the transconductance current  $I_{trans}$  on the power level as shown in Fig. 9b. When  $P_{RF}$  increases from -30 dBm to 0 dBm,  $I_{trans,ML}$  decreases from 380 pA to 8 pA while  $I_{trans,LIF}$  decreases from 86 pA to 15 pA.

Fig. 9 Post-layout Simulations obtained for the bit '1' for the NWR system with ML eNeuron (blue line) and LIF eNeuron (orange line): a  $V_{ED}$  in mV, b  $I_{trans}$  in pA, and c  $f_{spike}$  in kHz in function of the input power  $P_{RF}$

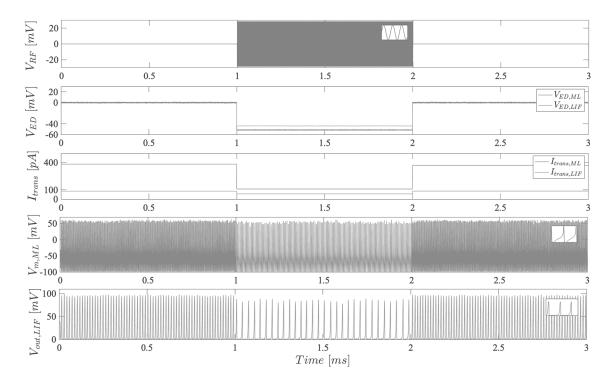

**Fig. 10** Transient noise simulation that shows the response of NWR system for a OOK-modulated signal of three bits [0,1,0] with a  $P_{RF} = -10$  dBm at different stages of the system and for both eNeu-

rons. An inset is added for  $V_{RF}$ ,  $V_{m,ML}$  and  $V_{out,LIF}$  to clarify the sinusoidal and spiking behaviors

*C. ML and LIF eNeurons* When an eNeuron is connected to the system and excited by  $I_{trans}$ , its  $f_{spike}$  depends on the bit value and the input power. For the bit '1',  $f_{spike}$  varies exponentially with the synaptic current  $I_{trans}$ . Figure 9c shows that  $f_{spike,ML}$  decreases from 249 to 19 kHz when  $P_{RF}$  increases from -29 dBm to 0 dBm. However,  $f_{spike,LIF}$  decreases from 65 to 0.12 kHz when  $P_{RF}$  increases from -25 dBm to 0 dBm. The ML is always firing at  $f_{spike,ML} = 250$  kHz for  $P_{RF}$  below -29 dBm, while LIF eNeuron remains with a  $f_{spike,ML} = 67$  kHz below -25 dBm.

### 4.1.2 System validation for an OOK-signal

An OOK-modulated signal  $V_{RF}$  with 1 kbps data rate and 2.4 GHz frequency was connected to the NWR system in both cases (with ML and with LIF eNeurons). The output at each level of the system was observed for three bits [0, 1, 0] with different input powers ( $P_{RF}$ , in dBm). An average over eight transient noise simulations is considered to demonstrate the functionality of the system. An example of an OOK-modulated signal with  $P_{RF} = -10$  dBm is presented in Fig. 10.

Table 2Literature EnvelopeDetector PerformanceComparison

| Ref               | [17]  | [7] | [6]   | [2]  | [8]   | This Work                             |

|-------------------|-------|-----|-------|------|-------|---------------------------------------|

| Techn. (nm)       | 180   | 130 | 65    | 180  | 130   | 55                                    |

| $f_{RF}(GHz)$     | 0.113 | 0.9 | 0.434 | 2.4  | 2.4   | 2.4                                   |

| $P_{rms}(nW)$     | 4.5   | 5   | 0.42  | 2400 | 120   | $1.2^{a}$<br>$0.25^{b}$               |

| $P_{mds}(dBm)$    | - 69  | -26 | -79.2 | -50  | -48.5 | $-29^{a}$<br>$-25^{b}$                |

| $E_{eff}(pJ/bit)$ | 15    | 5   | 4.2   | 22.5 | 48    | 1.2 <sup>a</sup><br>0.25 <sup>b</sup> |

<sup>a</sup>NWR with ML eNeuron, <sup>b</sup>NWR with LIF eNeuron

This figure illustrates the behavior of the NWR system at different stages. Simulations are carried out for the three bits [0, 1, 0] in a window of 3 ms.

As shown in Fig. 10, the OOK-modulated signal  $V_{RF}$ is implemented at the input of the NWR system in both cases. This signal presents a zero voltage for the bit '0' and an RF sinusoidal signal with an amplitude  $V_{RF} = -90$  mV. This signal is then demodulated by the envelope detector. For an NWR system with ML eNeuron or with LIF eNeuron, two voltage levels of the demodulated signal  $V_{ED}$  are shown in Fig. 10: one for the bit '0' ( $V_{ED,ML} = V_{ED,LIF} = 6 \mu$ V, near-zero and constant for any input power  $P_{RF}$ ) and another for the bit '1' data ( $V_{ED,ML} = -44 \, m$  V and  $V_{ED,LIF} = -50 \, m \, \text{V}$  for  $P_{RF} = -10 \, \text{dBm}$ , and varies with the input power as demonstrated in Fig. 9a). The higher level obtained for  $V_{ED,LIF}$  in comparison with  $V_{ED,ML}$  for the bit '1' comes from the additional transistor  $M_c$  implemented in the NWR with LIF eNeuron, which improves the gain of the demodulated voltage (see Sect. 3.1-A).

Therefore, as the demodulated voltage of the OOKmodulated signal is constant for the bit '0' for any input power, the synapse current  $I_{trans}$ , delivered by the transconductance synapse is constant in this case  $(I_{trans,ML} = 382)$ pA and  $I_{trans,LIF} = 86$  pA). However, the synapse will excite the post-neuron differently for the bit '1' since it presents an average value for the bit '1' that differs with the input power (see Fig. 9b). In the case of the Fig. 10, for  $P_{RF} = -10$  dBm,  $I_{trans,ML} = 109$  pA and  $I_{trans,LIF} = 56$ pA. The spiking behavior of the membrane voltage and the output voltage of the ML and LIF eNeurons respectively, are shown on Fig. 10 and can be identified by  $f_{spike}$ . Besides, the spiking frequency of the eNeuron is obtained from the number of spikes in respect to the time (in this case, time duration of a bit is 1 ms). For the bit '0' and for any  $P_{RF}$ , the ML and LIF eNeurons spike with a constant frequency as they are excited by a constant synapse current,  $f_{spike,ML} = 250$  kHz and  $f_{spike,LIF} = 65$  kHz. For the bit '1', the eNeuron fires with a  $f_{spike}$  that differ with  $P_{RF}$ , which is always lower than the spiking frequency for the bit '0' since the highest excitation from the synapse is for

the bit '0'. The reason behind that is to get the best energy efficiency of the eNeuron (in fJ/ spike) for the bit '0' [22].

#### 4.1.3 System performance

NWR system behaves differently depending on the eNeuron implemented in it. Thus, compromises between both NWR systems can be set in terms of performances. Here are some of them:

Dynamic Range: Assuming an uncertainty of 1 kHz spiking frequency between the bit '0' (where  $f_{spike,ML} = 250$  kHz,  $f_{spike,LIF} = 65$  kHz) and the bit '1' in a window of 1 ms, the functionality of the NWR system is validated until  $P_{RF} = -29$  dBm for the NWR with ML eNeuron and until  $P_{RF} = -25$  dBm for the NWR with LIF eNeuron. Thus, the NWR system with ML eNeuron can distinguish signals at 2.4 GHz with input power levels between -29 dBm  $< P_{RF} < 0$  dBm. However, for the same resolution, NWR system with LIF eNeuron achieves lower dynamic range where input powers of the system can vary between -25 dBm  $< P_{RF} < -5$  dBm.

Minimum Detectable Signal: State-of-the-art of envelope detector circuits target narrowband matching for low-noise circuitry, which leads to a low  $P_{mds} \approx -50$  dBm for high DR [14]. Besides, a low  $P_{mds}$  is demonstrated but with a higher  $\mu$  W-range power consumption. Proposed NWR achieves a  $P_{mds} = -29$  dBm when an ML eNeuron is implemented on it for 1.2 nW of total power consumption. However, it achieves a  $P_{mds} = -25$  dBm when it is with a LIF eNeuron, but for only 0.25 nW of power consumption. A better  $P_{mds}$  could be obtained if a narrowband off-chip matching network was chosen. NWR system presents remarkable improvement in energy efficiency due to the neuromorphic enhancement ( $E_{eff} = 1.2$  pJ/bit with ML eNeuron and  $E_{eff} = 0.25$  pJ/bit with LIF eNeuron). Table 2 summarizes a literature comparison of envelope detectors.

It can be also noticed that the spiking detection was evaluated for one bit in an observation window of 1 ms and for a DR = 1 kbps. If a higher DR is chosen, one may reduce the observation window to 0.1 ms (DR = 10 kbps) or 0.01 ms

Table 3Literature eNeuronsPerformance Comparison

| Ref                           | [13] | [4]             |                 | [9]  | This Work |      |

|-------------------------------|------|-----------------|-----------------|------|-----------|------|

| Model                         | LIF  | ML <sup>c</sup> | ML <sup>d</sup> | LIF  | ML        | LIF  |

| Techn. (nm)                   | 28   | 65              | 65              | 65   | 55        | 55   |

| Area ( $\mu$ m <sup>2</sup> ) | 34   | 35              | 200             | 31   | 98.61     | 31.2 |

| $f_{spike}(kHz)$              | 343  | 25              | 1.2             | 15.6 | 400       | 65   |

| $E_{eff,N}$ (fJ/spike)        | 1.2  | 4               | 78.3            | 2    | 1.95      | 1.7  |

<sup>c</sup>simplified ML eNeuron, <sup>d</sup>biomimetic ML eNeuron

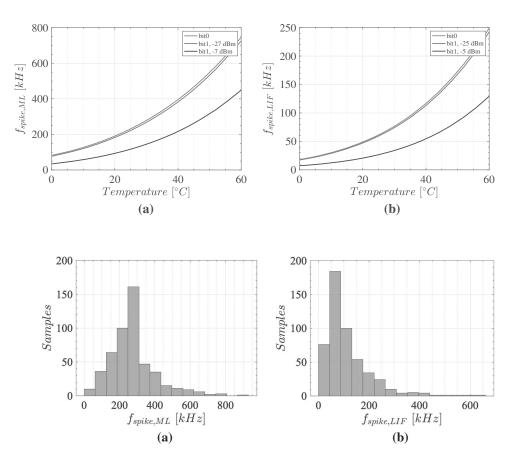

**Fig. 11** The variation of the spiking frequency in function of the temperature for an OOK-modulated signal with bit '0' and with bit '1' and with different input powers **a** for an NWR with ML eNeuron annd **b** for an NWR with LIF eNeuron

Fig. 12 The distribution of the spiking frequency for an OOK-modulated signal with bit '1' and with  $P_{RF} = P_{mds}$  **a** for an NWR with ML eNeuron annd **b** for an NWR with LIF eNeuron. Results are obtained for 500 iterations of transient PLS

(DR = 100 kbps) with no power consumption drawbacks. It is not the case in the state-of-the-art where a low  $P_{rms}$  and an interesting  $P_{mds}$  are achieved but only for a low DR [16, 17].

*Energy Efficiency of eNeuron*: The power consumption of an eNeuron is divided by its spiking frequency to produce the energy consumption per spike (the energy efficiency  $E_{eff,N}$  in J/spike). eNeurons are usually positioned in state-of-the-art by their  $E_{eff,N}$ . ML and LIF eNeurons are redesigned from previous work [22, 27] and their positions are compared with the state-of-the-art in Table 3. ML eNeuron presents an  $E_{eff,N} = 1.95$  fJ/spike while LIF eNeuron achieves an  $E_{eff,N} = 1.7$  fJ/spike. Recently, a LIF eNeuron is proposed in [28] and presents comparable performances but in a smaller area, using a 28 nm technology.

*Temperature Variation*: The variation of the spiking frequency of ML eNeuron and LIF eNeuron in NWR systems are plotted in function of the temperature in Fig. 11a and b respectively. This figure shows that for a temperature varying between 0 and 60°C,  $f_{spike}$  for bit '0' is always the same for any input power, however it changes for bit '1' with different input power signals. The important fact is that, for this range of temperature, NWR system maintains the same  $P_{mds}$  in both cases (ML and LIF eNeurons) since it keeps a difference between  $f_{spike}$  for bit '0' and  $f_{spike}$  for the bit '1' when  $P_{RF} = P_{mds}$ .

*Monte Carlo Simulations*: The distribution of the  $f_{spike}$  of ML eNeuron and LIF eNeuron in NWR systems are plotted in Fig. 12a and b respectively. These figures depict the results of 500 iterations of transient PLS for an RF input signal with bit '1' at  $P_{RF} = P_{mds}$  ( $P_{RF} = -29$  dBm for NWR with ML eNeuron and  $P_{RF} = -25$  dBm for NWR with LIF eNeuron). For these input powers,  $f_{spike,ML} = 249$

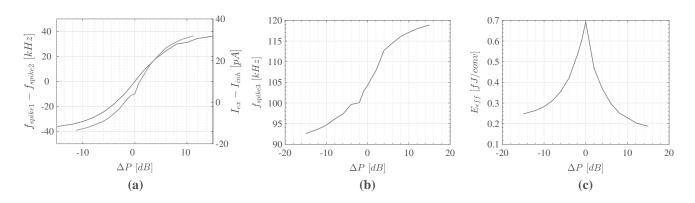

**Fig. 13** Post-layout simulation results of NSS: **a**  $\Delta f = f_{spike1} - f_{spike2}$  in kHz and  $\Delta I = I_{ex} - I_{inh}$  in pA, **b**  $f_{spike3}$  in kHz, and **c**  $E_{eff}$  in fJ/conv in function of  $\Delta P = P_{RF2} - P_{RF1}$  in dB

kHz and  $f_{spike,LIF} = 64$  kHz should be obtained as described in Sect. 4.1.1. The distribution of the  $f_{spike}$  appears to follow Poisson distribution in both cases, where the highest probabilities correspond to the right range of the spiking frequency.

#### 4.2 NSS simulation results

#### 4.2.1 System validation

As shown in Fig. 2, NSS is composed from two NWR systems, two synapses (one excitatory and one inhibitory) and a LIF eNeuron3. Both NWR systems implemented in NSS are designed with LIF eNeurons (LIF eNeuron1 and LIF eNeuron2). The reason behind that is that LIF eNeuron consumes much less power and has lower area in comparison with the ML eNeuron as demonstrated in Sec. 4.1. The objective of the proposed NSS system is to estimate the relative position of two IoT receivers  $R_1$  and  $R_2$ , implemented at its input, from the source *S*, and then identify the orientation of the source. This comes from the fact that NSS system can relate  $f_{spike3}$  of LIF eNeuron3 with the difference between input powers received at  $R_1$  and  $R_2$  ( $\Delta P = P_{RF2} - P_{RF1}$ ).

To validate the functionality of the NSS system, 41point of  $\Delta P$  are simulated. Thus, NSS system receives at its input two powers  $P_{RF1}$  and  $P_{RF2}$  from two receivers  $R_1$ and  $R_2$ . NWR systems get these input powers and deliver two spiking frequencies  $f_{spike1}$  and  $f_{spike2}$  from LIF eNeurons ( $\Delta f = f_{spike1} - f_{spike2}$ ). The synapses convert both  $f_{spike1}$  and  $f_{spike2}$  from previous eNeurons into excitation and inhibition currents. These currents  $I_{ex}$  and  $I_{inh}$  are both transmitted to the LIF eNeuron3 ( $\Delta I = I_{ex} - I_{inh}$ ) with a bias current equal to 100 pA to maintain a certain stability in the NSS system. This latter will be excited or inhibited depending on the sum of the incoming currents from the synapses. Thus, the spiking frequency  $f_{spike3}$  of the LIF eNeuron3 can be provided in function of the difference between the input powers  $\Delta P$ . The energy efficiency of the proposed NSS system can be estimated using Walden's figure-of-merit as [22]

$$FoM = \frac{P_{RMS}}{f_{spike3} \cdot 2^N}$$

(13)

where  $P_{RMS}$  is the total power consumption of the system and N is the full-scale dynamic range.

Figure 13 shows the post-layout simulations of the NSS system for the 41-point sweep of  $\Delta P$ . The difference  $\Delta f$ between the spiking frequencies of LIF eNeuron1 and LIF eNeuron2 and the difference  $\Delta I$  between the excitation and inhibition currents are illustrated in Fig. 13a. The dependency of the spiking frequency  $f_{spike3}$  of the LIF eNeuron3 and its energy efficiency  $E_{eff}$  on  $\Delta P$  are presented in Fig. 13b and Fig. 13c respectively. A  $\Delta P = 0$  means that  $P_{RF2} = P_{RF1}$ and the receivers are at the same distance from the source. In this case, the difference  $\Delta f$  is zero which gives a  $\Delta I$ approximately equal to zero. Therefore,  $f_{spike3} = 105 \text{ kHz}$ and  $E_{eff} = 0.7$  fJ/conv. If  $f_{spike3}$  is lower than 105 kHz, that means that the LIF eNeuron is more inhibited than excited (Fig. 13a). In this case, NSS receives a  $\Delta P < 0$  and thus the receiver  $R_1$  is closer to the source than the receiver  $R_2$ . If  $f_{spike3}$  is higher than 105 kHz, that means a higher effect of excitation, thus  $\Delta P > 0$  and the receiver  $R_2$  is closer to the source than the receiver  $R_1$ . For both cases ( $\Delta P < 0$  or  $\Delta P > 0$ ),  $E_{eff}$  decreases from 0.7 fJ/conv until a minimum of 0.2 fJ/conv.

#### 4.2.2 System behavior in EM environment

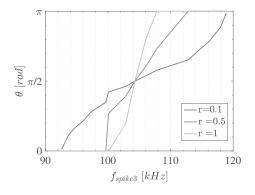

The transmitter source *S* is supposed to be a mobile object in the positive part of (x,y) plane. Thus, the angle  $\theta$  formed by the source with x-axis can take different values between 0 and  $\pi$ . As demonstrated in (11), the variation of the angle  $\theta$  in function of the difference between the input powers  $\Delta P$  depends on the distance *r* between the source *S* and the

**Fig. 14** Variation of the angle  $\theta$  (in radians) in function of the  $f_{spike3}$  (in kHz) for different distance r (in m) between the source S and the origin O

origin *O*, and the distance between the receivers  $R_1$  and  $R_2$ . In this paper, both receivers are equally distant from the origin. A distance  $d_0 = 7$  cm is considered in the simulations.

Figure 14 shows the variation of the angle  $\theta$  in function of the spiking frequency  $f_{spike3}$  of the LIF eNeuron3 for different values of r. The orientation of the source is then deduced based on the output  $f_{spike3}$  of the NSS system, which is extracted from  $\Delta P$  between both receivers (Fig. 13b). As shown in Fig. 14, when the distance r (in m) decreases,  $f_{spike3}$  can have a larger band of values. If the source is close to both receivers (for example, r = 0.1 m),  $f_{spike3}$  varies between 92 and 119 kHz. As the resolution of the NSS system is obtained for 1 kHz, this range of values gives then a precise orientation of the source. However, if the source is far from both receivers (for example, r = 1 m), the spiking frequency can take a value between 100 and 108 kHz, which is a very small band in comparison with the resolution of the system. One may increase the observation window of the spiking behavior to get a higher resolution. Thus, assuming a free space scenario, the system will still be capable of detecting different angles whatever is the distance of the source from the origin. It is clear that multipath may disturb the functionality of such system, but as in biological field, e-Neuron has the capacity of filtering such effects, seen as a stochastic process or noise [35], and future works will explore further these issues.

### 5 Conclusion

With the advancements in low-power and miniature electronics, recent years have witnessed a dramatic increase of IoT applications. For a ubiquitous sensing in IoT, large number of low-cost devices and low-power wireless communications capabilities are required. Challenges such as heavy cloud computing pressure and low-intelligent front-end limits the extend of sensing in IoT. While state-of-the-art is focusing on the cloud-edge platform solutions and the optimization of the performed and transmitted data, this paper proposes an intelligent equipment hardware for smart IoT devices. An RF neuromorphic spiking sensor is designed in BiCMOS 55 nm technology, achieving significant performances such as a low power consumption (1.1 nW) and high energy efficiency (0.7 fJ/conv) are obtained from post-layout simulations. The system is composed of wake-up receivers and spiking preprocessing neural system. The proposal can identify bit patterns of two 2.4 GHz received signals from a mobile source and recognize the orientation of this source. This is achieved based on the relation between the output spiking frequency of the neuron and the input power difference.

### References

- Piyare, R., Murphy, A. L., Kiraly, C., Tosato, P., & Brunelli, D. (2017). Ultra low power wake-up radios: A hardware and networking survey. *IEEE Communications Surveys & Tutorials*, 19(4), 2117–2157. https://doi.org/10.1109/COMST.2017.2728092

- Djiroun, F. Z., & Djenouri, D. (2017). MAC protocols with wakeup radio for wireless sensor networks: A review. *IEEE Communications Surveys & Tutorials*, 19(1), 587–618. https://doi.org/10. 1109/COMST.2016.2612644

- Umbdenstock, E., Schäfer, F., Kleinsteuber, M., & Meyer, H. (2013). Wake-Up-Receiver in energy efficient Wireless Sensor Networks for security applications.

- Cheong, P. S., Bergs, J., Hawinkel, C., & Famaey, J. (2017). Comparison of LoRaWAN classes and their power consumption. *IEEE Symposium on Communications and Vehicular Technology* (SCVT), 2017, 1–6. https://doi.org/10.1109/SCVT.2017.8240313

- Al-Gumaei, Y. A., Aslam, N., Chen, X., Raza, M., & Ansari, R. I. (2022). Optimizing power allocation in LoRaWAN IoT applications. *IEEE Internet of Things Journal*, 9(5), 3429–3442. https:// doi.org/10.1109/JIOT.2021.3098477

- Rejeb, A., Rejeb, K., Simske, S., Treiblmaier, H., & Zailani, S. (2022). The big picture on the internet of things and the smart city: a review of what we know and what we need to know. *Internet of Things*, 19, 100565. https://doi.org/10.1016/j.iot.2022. 100565

- Xu, C., Sun, Y. L., Plataniotis, K. K. N., & Lane, N. (2018). Signal processing and the Internet of Things [From the Guest Editors]. *IEEE Signal Processing Magazine*, 35(5), 13–15. https://doi.org/ 10.1109/MSP.2018.2846838

- Chen, H., Zhou, T., Yang, C., Li, Q., Peng, B., & Cheng, Q. (2022). Cloud-edge collaborative data processing architecture for state assessment of transmission equipments. In: 2022 7th International Conference on Intelligent Computing and Signal Processing (ICSP), pp 458–461. https://doi.org/10.1109/ICSP5 4964.2022.9778298

- Reyes, L., & Silveira, F. (2019). Gain, signal-to-noise ratio and power optimization of envelope detector for ultra-low-power wake-up receiver. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 66(10), 1703–1707. https://doi.org/10.1109/ TCSII.2019.2932767

- Schuman, C. D., Potok, T. E., Patton, R. M., Birdwell, J. D., Dean, M. E., Rose, G. S., & Plank, J. S. (2017). A survey of neuromorphic computing and neural networks in hardware. 1–88. http:// arxiv.org/abs/1705.06963

- Chen, X., Yajima, T., Inoue, H., Inoue, I. H., Byambadorj, Z., & Iizuka, T. (2022). CMOS-based area-and-power-efficient neuron and synapse circuits for time-domain analog spiking neural networks. http://arxiv.org/abs/2208.11881

- Liu, S.-C., & Delbruck, T. (2010). Neuromorphic sensory systems. *Current Opinion in Neurobiology*, 20(3), 288–295. https:// doi.org/10.1016/j.conb.2010.03.007

- Jouni, Z., Soupizet, T., Wang, S., Benlarbi-Delai, A., & Ferreira, P. M. (2022). 1.2 nW Neuromorphic enhanced wake-up radio. 2022 35th SBC/SBMicro/IEEE/ACM Symposium on Integrated Circuits and Systems Design (SBCCI), 1–6. https://doi.org/10. 1109/SBCC155532.2022.9893247

- Cheng, K.-W., & Chen, S.-E. (2017). An ultralow-power wakeup receiver based on direct active RF detection. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 64(7), 1661– 1672. https://doi.org/10.1109/TCSI.2017.2664919

- Karami, M. A., & Moez, K. (2021). An integrated RF-powered wake-up wireless transceiver with -26 dBm sensitivity. *IEEE Internet of Things Journal*, 4662, 1–1. https://doi.org/10.1109/ JIOT.2021.3116208

- Mangal, V., & Kinget, P. R. (2019). Sub-nW wake-up receivers with gate-biased self-mixers and time-encoded signal processing. *IEEE Journal of Solid-State Circuits*, 54(12), 3513–3524. https://doi.org/10.1109/JSSC.2019.2941010

- Wang, P.-H.P., Jiang, H., Gao, L., Sen, P., Kim, Y.-H., Rebeiz, G. M., Mercier, P. P., & Hall, D. A. (2018). A near-zero-power wake-up receiver achieving -69-dBm sensitivity. *IEEE Journal* of Solid-State Circuits, 53(6), 1640–1652. https://doi.org/10. 1109/JSSC.2018.2815658

- Shrestha, A., Fang, H., Mei, Z., Rider, D. P., Wu, Q., & Qiu, Q. (2022). A survey on neuromorphic computing: models and hardware. *IEEE Circuits and Systems Magazine*, 22(2), 6–35. https://doi.org/10.1109/MCAS.2022.3166331

- Mead, C. (1990). Neuromorphic electronic systems. *Proceedings of the IEEE*, 78(10), 1629–1636. https://doi.org/10.1109/5. 58356

- Hayati, M., Nouri, M., Haghiri, S., & Abbott, D. (2015). Digital multiplierless realization of two coupled biological morris-lecar neuron model. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 62(7), 1805–1814. https://doi.org/10.1109/TCSI. 2015.2423794

- Morris, C., & Lecar, H. (1981). Voltage oscillations in the barnacle giant muscle fiber. *Biophysical Journal*, 35(1), 193–213. https://doi.org/10.1016/S0006-3495(81)84782-0

- Ferreira, P. M., Nebhen, J., Klisnick, G., & Benlarbi-Delai, A. (2021). Neuromorphic analog spiking-modulator for audio signal processing. *Analog Integrated Circuits and Signal Processing*, *106*(1), 261–276. https://doi.org/10.1007/s10470-020-01729-3

- Sourikopoulos, I., Hedayat, S., Loyez, C., Danneville, F., Hoel, V., Mercier, E., & Cappy, A. (2017). A 4-fJ/spike artificial neuron in 65 nm CMOS technology. *Frontiers in Neuroscience*, *11*(123), 1–14. https://doi.org/10.3389/fnins.2017.00123

- Chu, M., Kim, B., Park, S., Hwang, H., Jeon, M., Lee, B. H., & Lee, B.-G. (2015). Neuromorphic hardware system for visual pattern recognition with memristor array and CMOS neuron. *IEEE Transactions on Industrial Electronics*, 62(4), 2410–2419. https:// doi.org/10.1109/TIE.2014.2356439

- Kravtsov, K. S., Fok, M. P., Prucnal, P. R., & Rosenbluth, D. (2011). Ultrafast All-Optical Implementation of a Leaky Integrate-and-Fire Neuron. *Optics Express*, 19(3), 2133. https://doi. org/10.1364/OE.19.002133

- Danneville, F., Carpentier, K., Sourikopoulos, I., Paindavoine, M., & Loyez, C. (2021). Sub-0.3V CMOS neuromorphic technology and its potential application. In: 2021 International Conference on Content-Based Multimedia Indexing (CBMI), 1–6. https://doi.org/ 10.1109/CBMI50038.2021.9461899

- Danneville, F., Loyez, C., Carpentier, K., Sourikopoulos, I., Mercier, E., & Cappy, A. (2019). A Sub-35 pW Axon-Hillock artificial neuron circuit. *Solid-State Electronics*, *153*, 88–92. https://doi. org/10.1016/j.sse.2019.01.002

- Besrour, M., Zitoun, S., Lavoie, J., Omrani, T., Koua, K., Benhouria, M., Boukadoum, M., & Fontaine, R. (2022). Analog Spiking Neuron in 28 nm CMOS. In: 2022 20th IEEE Interregional NEWCAS Conference (NEWCAS), 148–152. https://doi.org/10. 1109/NEWCAS52662.2022.9842088

- Qiao, N., & Indiveri, G. (2017). Analog circuits for mixed-signal neuromorphic computing architectures in 28 nm FD-SOI technology. In: 2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), 1–4. https://doi.org/10. 1109/S3S.2017.8309203

- Azghadi, M. R., Linares-Barranco, B., Abbott, D., & Leong, P. H. W. (2017). A hybrid CMOS-memristor neuromorphic synapse. *IEEE Transactions on Biomedical Circuits and Systems*, 11(2), 434–445. https://doi.org/10.1109/TBCAS.2016.2618351

- Cassidy, A., Zhang, Z., & Andreou, A. G. (2008). Neuromorphic interconnects using Ultra Wideband radio. *IEEE Biomedical Circuits and Systems Conference*, 2008, 297–300. https://doi.org/10. 1109/BIOCAS.2008.4696933

- 32. Kubota, I., & Torikai, H. (2021). A Novel Hardware-Efficient Cochlea Model based on Asynchronous Cellular Automaton Dynamics: Two-Tone Suppression and FPGA Implementation. In: 2021 17th International Workshop on Cellular Nanoscale Networks and Their Applications (CNNA), 2021-September, 1–4. https://doi.org/10.1109/CNNA49188.2021.9610787

- Rahiminezhad, A., Reza Tavakoli, M., & Masoud Sayedi, S. (2022). Hardware implementation of moving object detection using adaptive coefficient in performing background subtraction algorithm. 2022 International Conference on Machine Vision and Image Processing (MVIP), 2022-February, 1–5. https://doi.org/ 10.1109/MVIP53647.2022.9738764

- Chen, J., Skatchkovsky, N., & Simeone, O. (2022). Neuromorphic Integrated Sensing and Communications. http://arxiv.org/abs/ 2209.11891

- Querlioz, D., & Trauchessec, V. (2013) Stochastic resonance in an analog current-mode neuromorphic circuit. In: 2013 IEEE International Symposium on Circuits and Systems https://doi.org/10. 1109/ISCAS.2013.6572166

Raposo, J. R., Martins, O., Alves, F., Ferreira, P. M., & Maris, P. (n.d.). *IC-Layout Render: Image rendering tool for integrated circuit layout in Python*. https://doi.org/10.5281/zenodo.561826 with the Chalmers University of Technology, Gothenburg, Sweden, from 2019 to 2021. He has been an Associate Professor with the Sorbonne University, Paris, France, since 2021. He has authored or coauthored more than 30 journal articles and conference papers. His research interests include neuromorphic circuit modeling, spiking neural networks, Internet of Things (IoT), Federated learning, energy efficiency optimization, digital predistortion, and massive multiple input multiple output (MIMO).

Zalfa Jouni received her diploma in Electrical and Electronics Engineering from Lebanese University, Lebanon, and a Master's degree in Integration Circuits and Systems from Université Paris-Saclay, France, both in 2021. She is currently a PhD candidate (2021-2024) in Microelectronics at Université Paris-Saclay, CentraleSupélec. GeePs Laboratory (UMR 8507), France. Her research focuses on the design of analog and RF circuits for ultra-low-power neuromorphic IoT sensors.

Thomas Soupizet is currently a Global Engineering student at Université Paris-Saclay, CentraleSupélec (2021–2024). From 2022 to 2023, he was a researcher intern at GeePs Laboratory (UMR 8507). He is now an Agile Prototyper in Digital Lab. His research interests are Artificial Intelligence, cybersecurity, DevOps and electronics implementation.

Siqi Wang received the B.S. degree from the Huazhong University of Science and Technology, Wuhan, China in 2012, the M.S. degree from the University of Paris-Sud, Orsay, France, in 2014, and the Ph.D. degree from the University of Paris-Est Marne-La-Vallée, Champs-sur-Marne, France, in 2018. He was a Researcher Fellow with GeePs, Centralesupélec, Gif-sur-Yvette, France, from 2018 to 2019. He was a Researcher Fellow

Aziz Benlarbi-Delaï received the Ph.D. degree in electrical engineering and the Habilitation Diriger des Recherches (HDR) in Sciences Physiques from the University of Lille I, Villeneuved'Ascq, France, in 1992 and 2002, respectively. From 1992 to 2006, he was an Assistant Professor with the University of Lille I and was involved as a Researcher with the Institute of Electronic Microelectronic and Nanotechnology (IEMN), Villeneuve-d'Ascq, France, in the field of microwave and microflu-