Reliability and Physics-of-Healthy in Mechatronics Volume 15 – Reliability of Multiphysical Systems Chapter II: Applied Engineering on Physics-of-Healthy and SHM of microelectronic equipment for aeronautic, space, automotive and transport operations. pp.06-53

Alain Bensoussan, Joseph Bernstein, Alain Bravaix

### ▶ To cite this version:

Alain Bensoussan, Joseph Bernstein, Alain Bravaix. Reliability and Physics-of-Healthy in Mechatronics Volume 15 – Reliability of Multiphysical Systems Chapter II: Applied Engineering on Physics-of-Healthy and SHM of microelectronic equipment for aeronautic, space, automotive and transport operations. pp.06-53. ISTE Knowledge. Reliability and Physics-of-Healthy in Mechatronics, 15, WILEY, pp.6-53, 2022, Reliability of Multiphysical Systems Set, 978-1-786-30881-8. hal-04125717

HAL Id: hal-04125717

https://hal.science/hal-04125717

Submitted on 13 Jun 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Reliability and Physics-of-Healthy in Mechatronics

# Volume 15 – Reliability of Multiphysical Systems Set by Abdelkhalak El Hami

(Book ISTE publishing Knowledge – Wiley)

Date: 18 October 2020

Chapter II: Applied Engineering on Physics-of-Healthy and SHM of microelectronic equipment for aeronautic, space, automotive and transport operations.

Bensoussan Alain

Dr.-Ing, Dr-HDR, IEEE senior member

Thales Alenia Space

Meta Competence Center

Toulouse, France

alain.bensoussan@thalesaleniaspace.com

Bernstein Joseph

Professor, IEEE senior member

Laboratory for Failure Analysis and

Reliability of Electronic Systems

Ariel University

Ariel, Israel

josephbe@ariel.ac.il

Bravaix Alain

PhD, HDR, IEEE senior member

REER: Radiation Effects & Electrical

Reliability, IM2NP, ISEN

ISEN Yncrea Mediterranée, Toulon, France

alain.bravaix@isen.fr

### **SUMMARY**

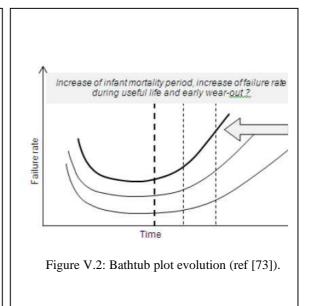

Electronics components and devices, including equipment to systems, are fabricated from materials and structures that degrade with time under normal operational condition. It is necessary to anticipate and quantify system failure occurrence but the goal of "reliability engineering" is to clarify first the failure paradigm in term of statistics and Physics of Failure or simply Part Count approach. Many statistical approaches and underlying mathematics have been developed in the past decades of the last century to describe failure rates and the well-known bathtub curve showing a schematic of failure rate behavior with time.

From Wikipedia definition, predictive (or logical) analysis encompasses a variety of techniques derived from statistics, data extraction and game theory that analyze past and present facts to make predictive assumptions about future events.

In this applied reliability chapter, we would like to share our perception on the experimentally development applied on existing reliability and maintenance paradigms developed since decades by many authors and papers.

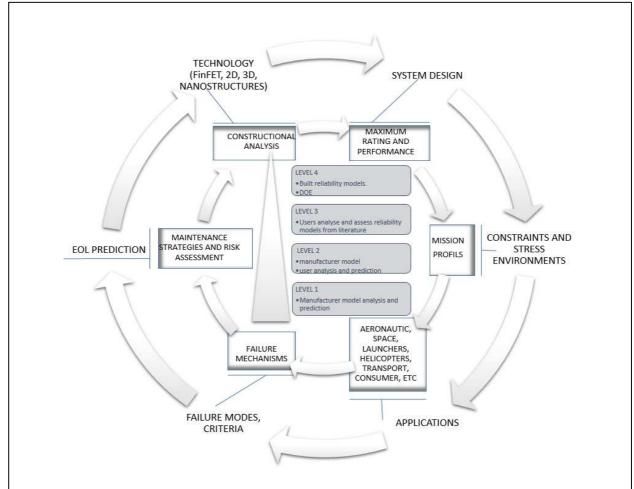

This Part I titled "Reliability Basic Tools for SHM protocols" aims to remind a) how applied engineering in predicting failure and monitoring SHM of electronic equipment and systems are implemented and b) to present basic statistic tools defined for reliability modelling implementation and studies related to active microelectronic parts. The second Part II is dedicated to the experimental application titled "Applied Engineering on Physics-of-Healthy and SHM on microelectronic equipment for aeronautic, space, automotive and transport operation" addressing how innovative technologies and Commercial-Off-The-Shelf (COTS) devices are pondered.

### How to implement predicting failure and monitoring SHM of electronic equipment and systems?

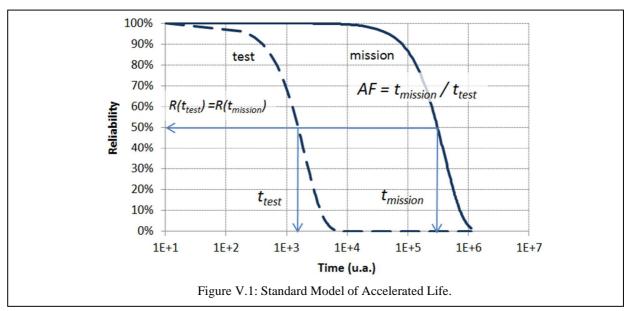

High Temperature Operational Lifetest (HTOL) Standard is relatively poor to predict Mean-Time-To-Failure (MTTF) associated constant failure rate and reveals mostly ineffective for wearout modelling as no failure are observed. Furthermore, the MTTF50% is not a zero-failure guarantee (rather by definition is a 50% lot failure) and we should define rather a MTTF0.1% for high reliability application. At the same time, attention to long-life cycles on the part of manufacturers has nearly vanished due to the relatively overwhelming demand in the consumer market sector.

Three key questions are reviewed including a) How to apply reliability prediction tools to innovative technologies? b) What are the hypotheses made of and methodology implemented in these tools; and to what extent are they able to cover emerging technologies and applications? c) Prognostic Failure Model (PFM) what could be a proposed guideline to organize all concepts? We describe our approach in what is needed to answer these and other fundamental questions as for example:

The goal of reliability engineering is to anticipate and quantify failure occurrence but the science required is to clarify first the paradigm in term of statistics and Physics of Failure [1], [2] or Part Count failure approach [3] [4], [5]. Many questions are raised, and we try to address as listed here:

In term of Physics and Phenomenological Degradation:

What are the existing Standards, their advantages and drawbacks?

How to manage random and wearout failure rate model to implement predictive reliability and maintenance?

What role the "stressors" are playing?

How "indicators" are characterized and which criteria value to define?

How to deal with multiple stresses?

In very complex new technologies (less than 7 nm FinFET, GaN, Carbone NanoTube, ...), what are the new failure mechanisms?

What if multiple failure mechanisms are coexisting? [5]

What is the impact on the accelerating factor (AF) in such complex mixed model (multiple stress, multiple failure mechanism)? [6]

How to apply reliability prediction tools to innovative technologies?

What are the hypotheses made of and methodology implemented in these tools; and to what extent are they able to cover emerging technologies and applications?

How to consider the effect of initial device quality, the influence of use and design options, the effect of mission profiles to model the Robustness [7] and the Reliability of complex systems and new technologies [8], [9], [10]?

*In terms of Application and experiments:*

In very complex new technologies, observed failure mechanisms can often be accelerated simultaneously, causing a dilemma for reliability prediction.

In the domain of telecommunications, automotive, aerospace, satellite, military and the like, the need for accurate reliability prediction is as important as it ever has been. At the same time, attention to long-life cycles on the part of manufacturers has nearly vanished due to the relatively overwhelming demand in the consumer market sector.

How to explore field return and define optimized maintenance survey based on reliability prediction tools?

Assuming a qualification test experiment on 130 samples tested during 2000 hrs of 150°C HTOL with 0 failure observed.

What would be the device operating projected lifetime verified if the operational application is at T=45°C?

What should be the sample size and duration to demonstrate a Cumulative Density Function (CDF) equal of less than 0.1% after 30 years in mission operation?

For Reliability prediction purpose do we need to consider Time-To-Failure for each failure mechanism either for a constant

failure rate based on a Poisson statistic, or for wearout failure mechanism?

What would be the equivalent total  $\lambda_{total}$  and corresponding Time-To-Failure if all failure mechanisms are equally activated?

### What the basic mathematics are?

Thermodynamics modeling established by S. Arrhenius (1896) [11], L. Boltzmann (1886) [12], then M. Evans and M. Polanyi in 1938 [13], E. Winner (1938) [14], S. Glasstone (1941) [15], G. Hammond (1955) [16], R. Drenick (1960) [17], E. Snow (1965) [18], N. Sedyakin (1966) [19], D. Cox (1972) [20] and periodically improved by H. Eyring et al. (1980) [21], J. McPherson (1999) [22] [23], or recently by E. Suhir (2013) [24] [25]. Modelling was supported by series of experimental papers from MIT (D. Jin and Del Alamo) [26], RAC Univ. of Maryland, University of Padova and G. Meneghesso's team [27], INTEL and IBM teams [28]. Since the break of 217<sup>+</sup> standard, FIDES French group guideline is still in place and its next evolution is thought to consider non-constant failure rate model for predictive reliability. Not leaving aside main actors in this paradigm development we have to name most representative experts in the field which have influenced the written of these chapter J. Stathis, V. Huard, A. Bravaix, J. Bernstein, M. Meneghini, H. Zanoni, E. Wu and J. Sune, P.A. Tobias and D.C. Trindade, M. Nikulin and V. Couallier.

The paradigm of the Transition State Theory (TST) developed by E. Wigner in 1934 [14] and by M. Evans, M. Polanyi in 1938 [13] is an approach we can benefit too by adapting the concept of a unified semiconductor reliability model and multiple failure mechanisms related to Physics of degradation. Indeed in the early last century, the TST was applied to chemistry transformations by H. Eyring [21], and S. Glasstone et al. [15] in 1941. The TST was developed in chemistry based on the Hammond's postulate [16] published in 1955 applied to physical organic chemistry.

Multiple failure mechanisms and Physics of degradation in semiconductors may occur in a single set of time-to-failure data but without obvious points of inflection to help separate the mechanisms. J. McPherson in his book 3rd edition of Reliability Physics and Engineering provides the basics of reliability modelling [23], [22] recalled *generally*, *materials/devices exist in metastable states*. These states are referred to as being metastable because they are only apparently stable. Metastable states will change/degrade with time. The rate of degradation of the materials (and eventual time-to-failure for the device) can be accelerated by an elevated stress (e.g., mechanical stress, electrical stress, electrochemical stress, etc.) and/or elevated temperature.

Gibbs free energy diagram recalled in 3<sup>rd</sup> edition of J. McPherson book has provided the main inputs to describe multiple stressors environment effect including entangled accelerating factor picture as fully detailed in Part I. Numerical application for a study case on a FinFET technology assuming three major failure mechanisms defined by the following Arrhenius reliability parameters are also detailed.

These mathematics and physic approaches show how the activation energy is an Eyring model related to the stress and temperature applied and can no-longer be considered as a constant to extrapolate some experiment under high stress to nominal mission operation profile. That's the reason why several end-user Industries and Institutions are very cautious to perform lifetest conditions as close as the nominal conditions because of the change of activation energy attributed sometime wrongly to new (or different) failure mechanism while it is simply explained by the interaction of stress and temperature effect on the measured activation energy or to a best extend to Eyring law.

From these equations we can observe the equivalent activation energy is dependent of the temperature  $T_{\theta}$  and is increasing with temperature. So, under the stress conditions, the failure mechanism model is a non-uniform acceleration mechanism.

<u>The goal of Part I</u> is to present basic statistic tools defined for reliability modelling implementation and studies related to active microelectronic parts (Integrated circuits, power transistors, etc) when exploited in operational environment for long term high reliability application.

Basics mathematics on serie-parallel systems reliability are presented with some approximation considerations for distribution queues statistics.

Conclusion and perspective open the door for the next Part II related to Predictive Reliability supported by experimental and Physics of Failure (PoF) or what we call Physics of Healthy (PoH).

Physics of degradation in semiconductors may occur in a single set of time-to-failure data but without obvious points of inflection to help separating the mechanisms. In his book, J. McPherson titled "Reliability Physics and Engineering provides the basics of reliability modelling" [23], [22] stated "generally, materials/devices exist in metastable states. These states are referred to as being metastable because they are only apparently stable. Metastable states will change/degrade with time. The rate of degradation of the materials (and eventual time-to-failure for the device) can be accelerated by an elevated stress (e.g., mechanical stress, electrical stress, electrochemical stress, etc.) and/or elevated temperature".

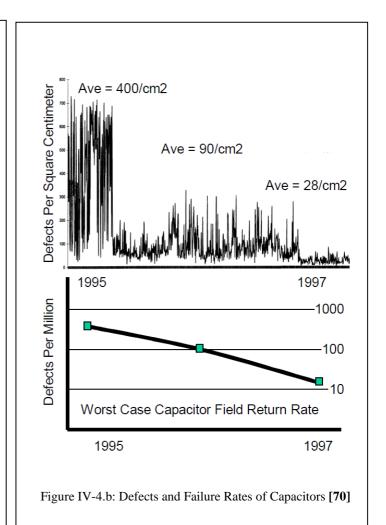

<u>Part II goal</u> is to concentrate on experiment supported by models and field return showing the "true life" observing simultaneous stress environment (various mission profiles) and multiple failure mechanisms.

Keywords— Probabilistic Design-for-Reliability, SHM, Reliability, PoF, PoH, Transition State Theory, Statistics, Semiconductors, Wide Band Gap, Deep Sub-micron, FinFET.

### NOTATION

| D 4.77             | Daltamana Ambanina 771 - 1                                            | 7               | Comment days to best committee as a second to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|-----------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAZ                | Boltzmann-Arrhenius-Zhurkov                                           | $I_{HCG}$       | Current due to hot carrier generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BEOL               | Back End Off Line                                                     | ILD             | Inter-layer dielectric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BTI                | Bias Instability (NBTI or PBTI)                                       | $I_{Sub}$       | peak substrate current during stressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CA                 | Constructional Analysis                                               | $\lambda(t)$ or | Instantaneous Failure Rate or Hazard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |                                                                       | IFR             | function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CCC (or            | Channel Cold Carrier                                                  | k               | Boltzmann's constant (1.3807·10 <sup>-23</sup> J/°K or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CC)                |                                                                       |                 | $8.6174 \ 10^{-5} \ eV/^{\circ}K$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CDF                | Cumulative Distribution Complementary                                 | MESFET          | Metal-semiconductor field effect transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CFET               | Transistors Function                                                  |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CHC or             | Channel Hot Carrier                                                   | MR              | Maximum rating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HC)                | D                                                                     | 3.6             | 16.11.1.61.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.1.101.101.1.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101.101. |

| DIBL               | Drain-Induced Barrier Lowering                                        | M-              | Multi-phySics mulTi-stressOrs predictive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D.E                | Davis and CE and a second                                             | STORM           | Reliability Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DoE                | Design of Experiment                                                  | M-TOL           | Multiple Temperature Overstress life-test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DSM                | Deep-Submicron technology                                             | MVE             | Multi-Vibrational Excitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $c(x_i)$           | Energy factor related to stress parameter $x_i$                       | NAF             | NMOS Acceleration time Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $E_a$              | Activation energy                                                     | NBTI            | Negative bias temperature instability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $E_{a\_effective}$ | effective activation energy related to                                | NTF             | DC NMOS Acceleration Time Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| or $E_{aa}$        | multiple stress reliability test sequence                             |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| EES                | Electron-electron scattering                                          | PAF             | PMOS Acceleration Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ECSS               | European Cooperation on Space                                         | PBTI            | Positive bias temperature instability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| F) (C              | Standardization                                                       |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| EMC                | Electromagnetic compatibility                                         | $P_{BO}$        | Power burnout limit value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EM                 | Electromigration                                                      | PDF             | Probability Density Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ESD                | ElectroStatic Discharge                                               | PDfR            | Probabilistic Design-for-Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EOS                | Electrical Overstress                                                 | PHEMT           | Pseudomorphic High Electron Mobility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ЕОТ                | Environment Oncid Thinks                                              | DMOC            | Transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

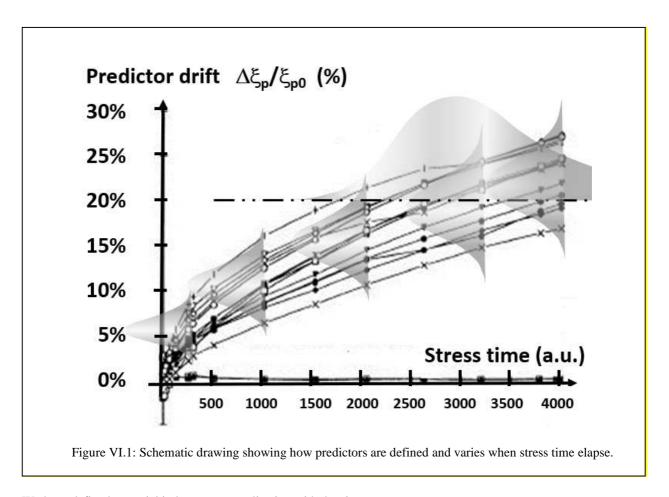

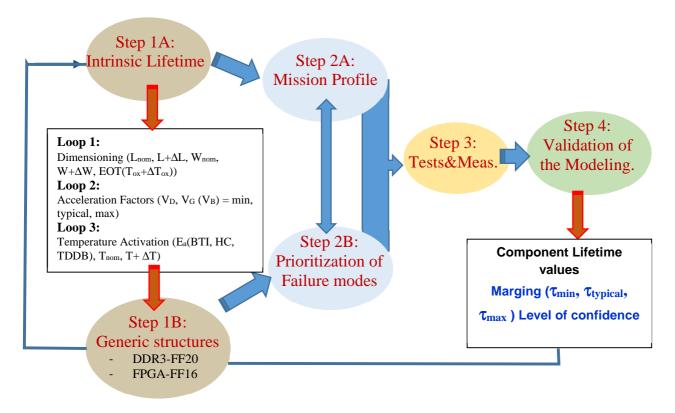

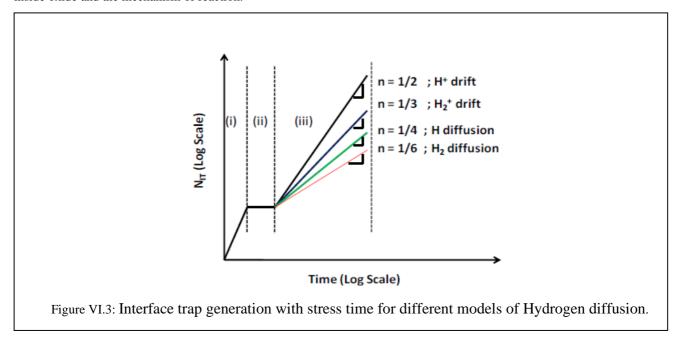

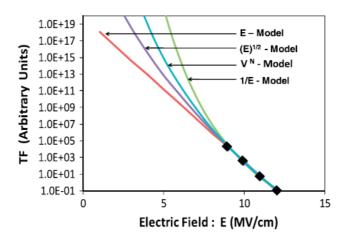

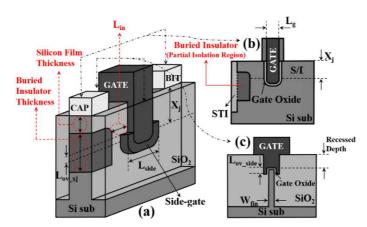

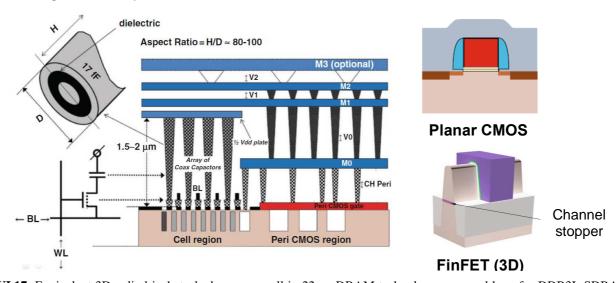

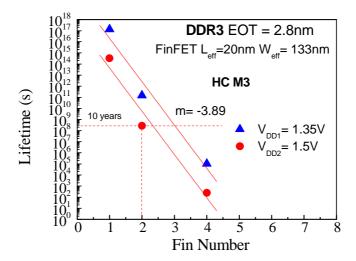

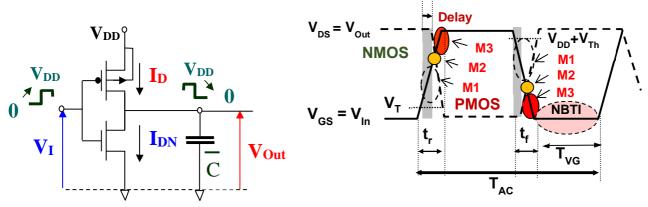

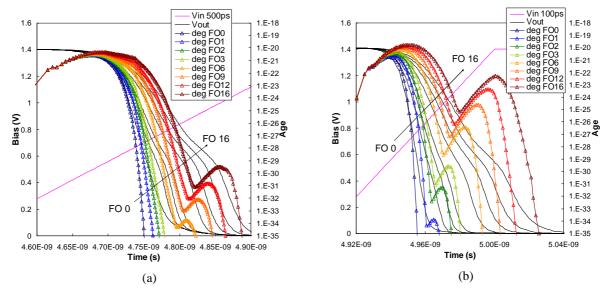

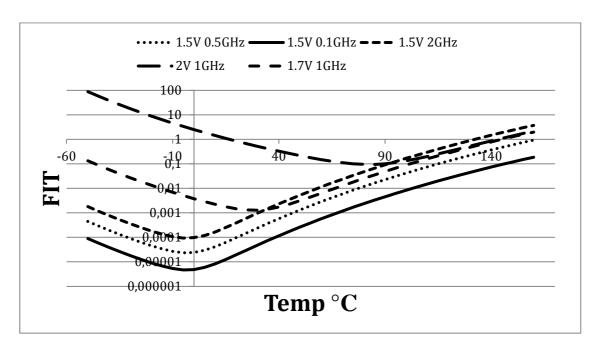

| EOT                | Equivalent Oxid Thickness                                             | PMOS            | P type Metal Oxide Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |