# Compositional Verification of Embedded Real-Time Systems

Mohammed Foughali, Pierre-Emmanuel Hladik, Alexander Zuepke

# ▶ To cite this version:

Mohammed Foughali, Pierre-Emmanuel Hladik, Alexander Zuepke. Compositional Verification of Embedded Real-Time Systems. Journal of Systems Architecture, In press. hal-04125520v2

# HAL Id: hal-04125520 https://hal.science/hal-04125520v2

Submitted on 20 Jun 2023 (v2), last revised 18 Oct 2023 (v3)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Compositional Verification of Embedded Real-Time Systems

Mohammed Foughali<sup>a</sup>, Pierre-Emmanuel Hladik<sup>b</sup>, Alexander Zuepke<sup>c</sup>

<sup>a</sup>Université Paris Cité, CNRS, IRIF, F-75013, Paris, France <sup>b</sup>Nantes Université, CNRS, LS2N, F-44000, Nantes, France <sup>c</sup>Technical University of Munich, D-85748, Garching, Germany

#### Abstract

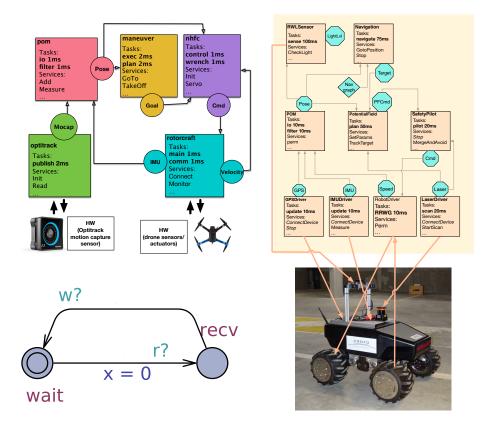

In an embedded real-time system (ERTS), real-time tasks (software) are typically executed on a multicore shared-memory platform (hardware). The number of cores is usually small, contrasted with a larger number of complex tasks that share data to collaborate. Since most ERTSs are safety-critical, it is crucial to rigorously verify their software against various real-time requirements under the actual hardware constraints (concurrent access to data, number of cores). Both the real-time systems and the formal methods communities provide elegant techniques to realize such verification, which nevertheless face major challenges. For instance, model checking (formal methods) suffers from the statespace explosion problem, whereas schedulability analysis (real-time systems) is pessimistic and restricted to simple task models and schedulability properties. In this paper, we propose a scalable and generic approach to formally verify ERTSs. The core contribution is enabling, through joining the forces of both communities, compositional verification to tame the state-space size. To that end, we formalize a realistic ERTS model where tasks are complex with an arbitrary number of jobs and job segments, then show that compositional verification of such model is possible, using a hybrid approach (from both communities), under the state-of-the-art partitioned fixed-priority (P-FP) with limited preemption scheduling algorithm. The approach consists of the following steps, given the above ERTS model and scheduling algorithm. First, we compute fine-grained data sharing overheads for each job segment that reads or writes some data from the shared memory. Second, we generalize an algorithm that, aware of the data sharing overheads, computes an affinity (task-core allocation) guaranteeing the schedulability of hard-real-time (HRT) tasks. Third, we devise a timed automata (TA) model of the ERTS, that takes into account the affinity, the data sharing overheads and the scheduling algorithm, on which we demonstrate that various properties can be verified compositionally, i.e., on a subset of cores instead of the whole ERTS, therefore reducing the state-space size. In particular, we enable the scalable computation of tight worst-case response times (WCRTs) and other tight bounds separating events on different cores, thus overcoming the pessimism of schedulability analysis techniques. We fully automate our approach and show its benefits on three real-world complex ERTSs, namely two autonomous robots

and an automotive case study from the WATERS 2017 industrial challenge.

#### 1. Introduction

#### 1.1. Addressed Problem & Motivation

In an embedded real-time system (ERTS), the software, consisting of a set of *real-time tasks*, executes on an *embedded hardware*. The latter is usually a *multicore shared-memory* one, where "multicore" refers to a small number of cores (contrasted with a higher number of tasks) due to Size, Weight, Power and Costs (SWaP-C) considerations, and shared memory allows tasks to communicate the results of their computations. ERTSs are at the heart of *safety-critical* applications spanning various domains, such as automotive vehicles and mobile robots, where their failure may entail considerable economic losses and even human casualties. Unfortunately, classical *scenario-based testing* proved inefficient as a means to detect faulty executions and thus prevent an ERTS failure. For instance, Toyota vehicles with a major software bug behind the Unintended Acceleration failure, costing 89 human lives and billions of dollars to the automotive manufacturer, have nevertheless successfully passed millions of hours/miles of testing prior to their deployment [48].

It is therefore crucial to formally verify ERTSs as to guarantee their safe behavior. Such verification is typically carried out on an ERTS *model* vis-à-vis important *real-time properties*, such as bounded response and schedulability. For instance, in an autonomous drone, flight missions must obey stringent timing constraints to ensure that e.g., control algorithms perform fast enough to prevent collisions and crashes from happening. In order to obtain useful results, the verified model must take into account the actual hardware-software setting of the underlying ERTS, i.e., software timing parameters (tasks deadlines and execution times) and hardware specificities (concurrent access to data, number of cores). As an example, if the number of cores is ignored in the model, the verification results are only valid under the unrealistic assumption that the ERTS hardware has enough cores to run all tasks in parallel. Formal verification of ERTSs is thus a complex activity; it involves at least two research communities, namely the formal methods community and the real-time systems community.

On the one hand, the formal methods community provides rigorous approaches, such as (real-time) model checking [4, 23], to verify timed systems. In model checking, a mathematical model of the system under scrutiny is verified exhaustively against properties formalized in a logic. Powerful model checking algorithms are implemented within state-of-the-art tools, such as UPPAAL [53], based on timed automata (TA) [6, 43] and a fragment of the timed computational-tree logic (TCTL) [5] for modeling the system and formalizing the properties of interest, respectively. Unfortunately, in the case of ERTSs, model checking suffers from scalability issues due to the state-space explosion problem [24]. Non-exhaustive approaches, such as statistical model checking (SMC) [54] and runtime verification (RV) [9], are more scalable. In SMC, properties are no longer verified with certainty but up to some probability. However, obtaining

a sufficiently high probability (if defined) in a safety-critical setting poses the same scalability issues as SMC tends then towards exhaustive model checking (see e.g., the conclusions of [33, Sect. 7.2.2]). In RV, monitors check the properties satisfiability, and possibly react to their violation at runtime (e.g., à la Fault Detection, Isolation and Recovery FDIR [77, 69]), therefore avoiding the exhaustive exploration of the state space. Nevertheless, RV still faces major challenges in safety-critical settings, in particular the overhead of deploying monitors that may impede timely recovery from property violation (see e.g., the conclusions of [35]). Finally, real-time verification activities within the formal methods community seldom take the hardware actual constraints into account, which restricts the results' validity to unrealistic ERTSs (Sect. 8).

On the other hand, the real-time systems community has a long tradition with the analysis of ERTSs. In particular, schedulability analysis [20] is a well-anchored discipline, where one assesses whether some real-time tasks are schedulable (always finish executing before their deadlines), given a number of cores and a *scheduling algorithm*. Under the schedulability analysis umbrella. Integer Linear Programming (ILP) is extensively used to e.g., find an *affinity* (task-core allocation) that guarantees the schedulability of all tasks, or their subset of hard-real-time (HRT) tasks in an ERTS. Though solving an ILP problem is NP-hard [45], the community provides algorithms that are efficient in practice (see e.g., [80]). However, the more schedulability analyses are scalable, the more pessimistic they get in the periodic setting, as computationally efficient *schedulability tests* are typically sufficient but not necessary, i.e., if the schedulability test holds for some task then it is schedulable, but the converse is not true (more in Sect. 5, 7). Moreover, as its name indicates, schedulability analysis focuses on schedulability properties only. In addition, tasks models used in schedulability analysis are usually overly simplified compared to the ones found in real ERTSs, e.g., in automotive systems and mobile robots (Sect. 3).

To summarize, interdisciplinary formal verification approaches for ERTSs, that promote both realistic modeling and scalable verification, are needed.

#### 1.2. Contributions & Outline

In this paper, we propose a scalable approach to formally verify real-time properties in real-world ERTSs. In particular, our approach joins efforts from both communities to enable compositional model checking, thus alleviating the state-space explosion problem. Moreover, formal models, on which properties can be verified compositionally, are automatically generated from any ERTS following a periodic-task model specified in a high-level format. Our contribution is thus twofold: we (i) provide a fully automated and generic framework to verify real-world ERTSs and (ii) enable scalability through compositional verification. Taming the state-space size comes with the direct advantage of verification feasibility on real-word ERTSs w.r.t. a number of properties where model checking allows, in addition, to compute tight upper bounds of the worst-case response times (WCRTs) of tasks as opposed to the pessimistic ones provided by schedulability tests.

The rest of this paper is organized as follows. First, we introduce formalisms and techniques used in this paper (Sect. 2). Second, we formalize a realistic ERTS, where tasks contain an arbitrary number of jobs and job segments, and hardware specificities are taken into account, then expose the main challenge hindering the compositional verification of such ERTS, namely tasks dependency w.r.t. cores and shared data. We present our overall approach as we show that this challenge can be efficiently tackled under a state-of-the-art scheduling algorithm. namely partitioned fixed-priority (P-FP) with limited preemption (Sect. 3). Consequently, we generalize techniques from the real-time systems community that incorporate data sharing overheads in tasks independently (Sect. 4), then devise an ILP algorithm that computes an affinity guaranteeing the schedulability of all tasks (or at least all HRT tasks) in a real ERTS (Sect. 5). We provide then a TA model for any ERTS under the above scheduling assumption, integrating data sharing overheads (from Sect. 4) and combined with the affinity (computed in Sect. 5), on which we demonstrate that important properties can be verified compositionally (Sect. 6). We validate the scalability of our approach on three real-world case studies featuring two autonomous robots and an automotive system, and show further how compositionality allows a scalable computation of tight WCRTs, therefore overcoming a posteriori the pessimism of the ILP algorithm (Sect. 7). Finally, we compare our approach with related research (Sect. 8) and conclude with future work (Sect. 9).

#### 2. Preliminaries

In this section, we provide definitions of the formalisms and techniques serving as a basis for the approach presented in this paper.

# 2.1. Data Sharing

Concurrent execution in an ERTS requires coordination. A task model describes recurring operations in the ERTS, and a real-time scheduler ensures the timely execution of tasks based on their timing requirements (Sect. 3). Tasks access shared data, so the task model also defines synchronization concepts. Consistent access to shared data happens when executing some job segments, typically non-preemptible pieces of code, i.e., the scheduler never preempts a task inside a job segment. The dependency of tasks on data can often be modeled using producer-consumer patterns. The resulting synchronization allows exclusive (read-write, producer) or shared (read-only, consumer) data access, or provides consistent snapshots of logically coherent data. ERTS can use locks<sup>1</sup>, e.g., fine-grained reader-writer locks [60], which causes blocking to other tasks, or wait-free algorithms [44]. Wait-free algorithms can be further classified as retry-based approaches, e.g., sequence locks in Linux [58], or use multiple buffers, e.g., Simpson's four-slot algorithm [74], to exploit parallelism. In either case, data sharing overheads refer to the maximum time a job segment is delayed by

<sup>&</sup>lt;sup>1</sup>See [18] for in-depth details on locking protocols.

other job segments accessing data concurrently. This corresponds for instance to blocking in lock-based approaches and the *latency* due to retries in retry-based approaches (more in Sect. 4).

#### 2.2. Integer Linear Programming (ILP)

A linear programming (LP) problem consists in *optimizing* (maximizing or minimizing) a *linear objective function subject to linear constraints*. A classical formulation for of an LP is:

Maximize:  $\mathbf{c}^T \mathbf{x}$ , subject to:  $A \mathbf{x} \leq \mathbf{b}, \mathbf{x} \in \mathcal{X}$

where  $\mathbf{c}^T$  is the transpose of matrix  $\mathbf{c}$  and  $\mathbf{c}^T \mathbf{x}$  represents the objective function to optimize with  $\mathbf{x}$  a vector of m unknown variables over the domain  $\mathcal{X}$ ,  $\mathbf{b}$  a vector of known coefficients and A a known matrix of coefficients. The constraints are expressed by the relations  $A\mathbf{x} \leq \mathbf{b}$  and  $\mathbf{x} \in \mathcal{X}$  that specify the polytope over which the objective function is to be optimized. Given this polytope, an LP *solver* finds a point where the objective function has the smallest or largest value through the polytope vertices. LP algorithms are known to be exact. If the unknown variables are all real, i.e.,  $\mathcal{X} = \mathbb{R}^m$ , then the problem can be solved using the classical Simplex method [66].

The LP problem becomes an ILP problem if the variables are all required to be integers, i.e.,  $\mathcal{X} = \mathbb{Z}^m$  (binary variables<sup>2</sup> are considered as integers in the domain  $\{0, 1\}$ ). Though ILP solving is NP-hard [45], many algorithms (e.g., branch-and-bound and branch-and-cut) are mature and well integrated in powerful solvers, such as CPLEX and Gurobi.

# 2.3. Timed Automata (TA)

Timed automata (TA) [6] extend Büchi automata with real-valued *clocks*. A simpler yet equivalent version with location *invariants* instead of accepting locations was introduced in [43] and is at the heart of modern model checkers, such as the state-of-the-art UPPAAL [53] used in this paper. We first define *synchronization-free networks of TA* (TA composed in parallel without synchronizations), mostly simplified from [13].

#### 2.3.1. Synchronization-free Networks

Notation. Let X be a set of real-valued clocks and  $\mathcal{B}(X)$  the set of clock constraints over X. Each clock constraint in  $\mathcal{B}(X)$  is a (possibly empty) conjunction of atomic constraints of the form  $x \sim k$  with  $x \in X, \infty \in \{<, >, \leq, \geq\}$  and  $k \in \mathbb{N}$ . Let  $v: X \mapsto \mathbb{R}_{\geq 0}$  be a valuation function. We write  $v \in c$  to denote that v(x)for each  $x \in X$  satisfies  $c \in \mathcal{B}(X)$ , and v + d ( $d \in \mathbb{R}_{\geq 0}$ ) to denote the valuation v(x) + d for each  $x \in X$ . Moreover, for  $\lambda \subseteq X$ ,  $[\lambda \mapsto 0]v$  denotes the valuation 0 for each  $x \in \lambda$  and v(x) for each  $x \in X \setminus \lambda$ . Finally,  $\mathcal{V}_i$  denotes the  $i^{th}$  element of a vector  $\mathcal{V}$  and  $\mathcal{V}[\mathcal{V}'_i/\mathcal{V}_i]$  the vector  $\mathcal{V}$  in which  $\mathcal{V}_i$  was substituted by  $\mathcal{V}'_i$ .

$<sup>^{2}</sup>$ These can be used to represent Boolean variables or simply the values 1 and 0 to activate or deactivate a constraint (Sect. 5).

Syntax. In a synchronization-free network of TA  $N = (A_1 ||..||A_n), n \in \mathbb{N}$ , each  $A_i$  is a tuple  $\langle L_i, l_{i0}, X_i, E_i, I_i \rangle$  where:

- $L_i$  is a finite set of locations,

- $l_{i0} \in L_i$  is the initial location,

- $X_i$  is a finite set of clocks,

- $E_i$  is a finite set of edges, each edge of the form  $(l, g, \lambda, l')$  with  $l, l' \in L_i$ ,  $g \in \mathcal{B}(X_i)$  a guard, and  $\lambda \subseteq X_i$  a subset of clocks to be reset,

- $I_i: L_i \mapsto \mathcal{B}(X_i)$  a function that assigns an *invariant* to each location.

Note that a guard/invariant can be a tautology, i.e., an empty conjunction of clock constraints  $\top$ . A location is called *invariant free* if its invariant is  $\top$ . Such guards/invariants and resets over the empty set are often omitted in the remainder of this paper.

Semantics. Let  $\mathcal{X} = \bigcup_{i \in 1..n} X_i$  be the set of all clocks in the network. The semantics of a synchronization-free network of TA  $(A_1 || ... || A_n)$  is given over a transition system (TS)  $\langle Q, q_0, \rightarrow \rangle$  where:

- Q is the set of states of the form  $(\mathcal{L}, v)$ , with  $\mathcal{L} \in L_1 \times ... \times L_n$  a vector of locations and  $v : \mathcal{X} \mapsto \mathbb{R}_{>0}$  a clock valuation function,

- $q_0$  is the initial state  $(\mathcal{L}^0, v_0)$ , with  $\mathcal{L}^0 = (l_{10}, \ldots, l_{n0})$  and  $v_0(x) = 0$  for each  $x \in \mathcal{X}$ ,

- $\rightarrow$  is the transition relation. A transition is *enabled* at some state q if it can be *taken* at q. Taking a transition changes the state as follows: (i) delay transitions  $(\mathcal{L}, v) \rightarrow (\mathcal{L}, v + d)$  for some  $d \in \mathbb{R}_{>0}$  if  $v \in \bigwedge_{i \in 1..n} I_i(\mathcal{L}_i)$  and  $(v + d) \in \bigwedge_{i \in 1..n} I_i(\mathcal{L}_i)$ , (ii) discrete transitions  $(\mathcal{L}, v) \rightarrow (\mathcal{L}[\mathcal{L}'_i/\mathcal{L}_i], v')$  if exists an edge  $(\mathcal{L}_i, g, \lambda, \mathcal{L}'_i) \in E_i, v \in g, v' = [\lambda \mapsto 0]v$  and  $v' \in I_i(\mathcal{L}'_i)$ .

Note that the above definitions also apply to a synchronization-free network of networks, i.e., a network  $\mathcal{N} = (N_I || \dots || N_n)$ ,  $n \in \mathbb{N}$  where each  $N_i$  is a network of TA, and there is no synchronization between any couple of TA belonging to two different networks<sup>3</sup>  $N_i$  and  $N_j$  in  $\mathcal{N}$ . Indeed, each  $N_i$  can be viewed as a single TA resulting from the (possibly synchronized) product of all the TA it contains [3], then the semantics above applies to the composition similarly.

<sup>&</sup>lt;sup>3</sup>Here, the TA involved in the same  $N_i$  can be synchronized, in which case a set of *actions* (*channels* in UPPAAL) needs to be defined for these TA.

#### 2.3.2. Timelocks

Timelocks are pathological phenomena that reflect modeling flaws in TA [78, 16]. In other words, the presence of a timelock in the underlying TS of a network of TA is a sign of a modeling mistake. This is because a timelock corresponds to an unrealistic scenario where global time may not evolve beyond some bounded value as we will explain in more details and provide an example next. More formal definitions and proofs are given in Sect. 6.

A network N has a timelock iff it contains at least one *timelock state*. A timelock state  $(\mathcal{L}, v)$  is a state from which (i) no infinite sequence of transitions exists or (ii) each infinite sequence of transitions is bounded in time, i.e., time converges toward some integer. In the case (ii), each infinite sequence of transitions is called a *zeno* run, and  $(\mathcal{L}, v)$  a *zeno-timelock* state. More informally, a network N has a timelock iff there exists a state in the underlying TS from which time may not progress beyond some finite value. Notice that, in [78], only zeno timelocks are called timelocks. Our more generic definition and examples stem from [16], where the impossibility of time progress beyond some global time t is considered a timelock, regardless of zenoness.

*Example.* Consider the singleton network N = A where A has one location  $l_0$  and one clock x.

Consider the case where A has no edges and  $I(l_0) = (x < 2)$ . Here, A timelocks because at least one state in the underlying TS is a timelock state (actually, all states here are timelock states). For instance, the initial state  $(l_0, 0)$  is a zeno-timelock state, since the sum of delays corresponding to any infinite succession<sup>4</sup> of transitions from it is bounded by 2.

Consider now the case where A has no edges and  $I(l_0) = (x \le 2)$ . Here, A timelocks, because there is at least a timelock state in the underlying TS:  $(l_0, 2)$ , for instance, is a (non-zeno) timelock state. Indeed, at such state, no infinite sequence of transitions in possible (actually, no transition is possible at all). The underlying TS is thus "frozen" at state  $(l_0, 2)$ .

Zeno timelocks can stem from discrete transitions as well. Consider the case of A where  $I(l_0) = (x \leq 2)$  and A has one edge  $(l_0, x \leq 2, \emptyset, l_0)$ . Here, at  $(l_0, 2)$ , all possible infinite sequences of transitions contain only discrete transitions (the discrete transition corresponding to the only edge in A is always enabled, and time may no longer progress because of the invariant at  $l_0$ ).  $(l_0, 2)$  is thus a zeno-timelock state.

Timelocks are clearly unrealistic (time always evolves beyond some point in reality). Timelocks (including zeno ones) have unexpected consequences on networks semantics, and they typically result from modeling errors. Networks of TA need to be exempt of these phenomena, as we will see further in Sect. 6.

<sup>&</sup>lt;sup>4</sup>Due to the strict < in the invariant and delays taking their values in  $\mathbb{R}_{>0}$ , an infinite succession of delay transitions is possible from this state without ever reaching the value 2.

#### 2.3.3. UPPAAL TA

In this paper, we deliberately avoid the semantics of synchronization and other extensions, such as priorities, for simplicity. Instead, we will directly explain how these extensions work in UPPAAL, the model checker that we use (some details on UPPAAL TA semantics are provided in [13]). Examples of UPPAAL TA are given in Sect. 6.

*Channels.* UPPAAL allows synchronizations through *handshake* and *broadcast* channels. The former (resp. the latter) are blocking and pairwise (resp. non blocking and multiparty), that is in a handshake (resp. a broadcast) channel, the *sender* synchronizes with only one *receiver* (resp. as many receivers as possible). A synchronization implies taking all edges involved in it simultaneously.

*Priorities.* Channels may have priorities. Priorities affect the semantics of discrete transitions. In brief, if channel c' has a higher priority than channel c, then at any state of the underlying TS, all discrete transitions involving c are disabled as long as there exists an enabled transition involving c'.

*Data variables and functions.* UPPAAL supports integer and Boolean data variables, whose values may be used in guards, and updated in discrete transitions (together with clock resets). Variables can be local (to a TA) or global. A small subset of C-like functions is also supported to ease writing complex updates.

Committed locations. Committed locations implement both an urgency and a priority. That is, in the underlying TS, if at some state  $(\mathcal{L}, v)$  there exists  $\mathcal{L}_i \in \mathcal{L}$  such that  $\mathcal{L}_i$  is committed, then a discrete transition starting from a committed location must be taken immediately, i.e., (i) time may not progress, and (ii) only transitions of the form  $(\mathcal{L}, v) \rightarrow (\mathcal{L}[\mathcal{L}'_i/\mathcal{L}_i], v')$  where  $\mathcal{L}_i$  is committed are enabled. Committed locations are therefore handy to describe sequences of timeless actions that need to be realized immediately regardless of the other actions possible at the same time. This is for example the case of scheduling decisions such as activation and release (Sect. 6).

#### 2.4. Timed Computational Tree Logic (TCTL)

TCTL is a logic that is both *temporal* and *timed*, allowing to reason on the order of, and the amount of time separating the satisfaction of some formulae, respectively. We focus on the fragment of TCTL that UPPAAL supports. A *state formula* is a propositional formula over locations, clocks and data variables, to be evaluated at a TS state. For instance,  $A_i.x < 3$  holds in all states of the TS where the valuation of clock x in TA  $A_i$  is strictly less than 3. *Path formulae* enable quantifying over TS traces. Path formulae in UPPAAL use the operators A (for all paths) and E (there exists a path) combined with the modalities  $\Box$  (necessity, all states) and  $\diamond$  (possibility, some state). For instance, the property  $A \diamond \phi$  (where  $\phi$  is a state formula) translates to "for each path, there exists a state that satisfies  $\phi$ " whereas  $E \Box \phi$  reads "there exists a path in which all states satisfy  $\phi$ ".

Next are the three path formulae (out of five supported by UPPAAL) used in this paper ( $\phi$  and  $\psi$  are state formulae):

- $A\Box\phi$ :  $\phi$  holds in all states of the TS (*safety*),

- $E \diamond \phi$ : there exists a reachable state that satisfies  $\phi$  (*reachability*),

- $A\Box(\phi \Rightarrow A \diamond \psi)$ , denoted using the shorter syntax  $\phi \rightsquigarrow \psi$ : whenever  $\phi$  holds,  $\psi$  eventually holds (*leadsto & bounded response*).

For bounded response, we are also interested in quantifying the maximum amount of time separating the satisfaction of  $\phi$  and  $\psi$ . For this, we use the formula  $\sup\{A_i.l\}: A_i.x$  that computes the maximum valuation of clock x at location l in TA  $A_i$ . This will be handy in computing WCRTs and other important bounds (practical examples are given in Sect. 6, 7).

#### 3. Challenges & Overall Approach

Formal modeling and the feasibility of verification are intimately related: the more the formal model is abstract, the more the verification is likely to scale. However, abstractions should not come at the cost of unrealistic modeling. Formal models should be the closest possible to the reality of the underlying system, i.e., the real hardware-software setting in the case of ERTSs. In this section, we provide a formal description of a realistic ERTS under a couple of state-of-the-art scheduling assumptions (Sect. 3.1), and explain why such a model can be verified in a scalable manner (Sect. 3.2). Then, we present our overall approach accordingly (Sect. 3.3).

# 3.1. ERTS Model

An ERTS is classically modeled as a set of real-time tasks executing on a set of cores following a *scheduling algorithm* [20]. Though models within the real-time systems community take more and more into account the dependency between tasks, e.g., vis-à-vis data sharing [17, 67, 68], they remain typically simple with each task having one *job* associated to a Worst-Case Execution Time (WCET), a *deadline* and possibly a *period*. In real ERTSs, a task is noticeably more complex, it can have several jobs each consisting of a sequence of segments (pieces of code). This is the case, e.g., in mobile robotics and automotive systems, where job segments are called, respectively, runnables [62, 63] and functions/codels [47, 40, 34] (actual examples are given in Sect. 7). As we have shown in [37, 34, 38], this complexity prevents the reuse of *schedulability tests* from the literature. We need therefore a realistic ERTS model which we present next. Our model relies on partitioned fixed priority (P-FP) scheduling with limited preemption. In brief, P-FP scheduling assigns statically each task to one and only one core (partitioned "P") and tasks priorities are fixed beforehand, i.e., they do not depend on the execution dynamics (fixed priority "FP"). As for limited preemption, it refers to the fact that preemption, i.e., putting the execution of a job in a lower priority task temporarily on hold in order to execute

a job in a higher priority task on the same core, is allowed but can happen only at some time instants relative to the execution of the job in the lower priority task. P-FP scheduling with limited preemption is an efficient and widely used scheduling algorithm in ERTS as we will explain further, with the appropriate references, in Sect. 3.2.

Syntax. An ERTS is made of a set of tasks T, a set of shared data L and a set of cores C (|T| > |C| > 0). We assume that all tasks in T are periodic (we discuss in Sect. 7 the implications of this simplification) and the deadlines to be the periods themselves (a classical assumption with periodic tasks).

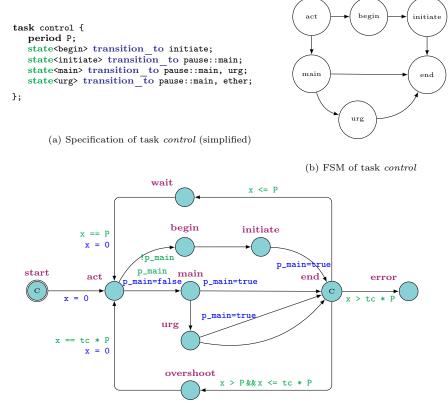

Each task  $\tau \in T$  is a finite-state machine (FSM)  $\langle S_{\tau}, act_{\tau}, end_{\tau}, tr_{\tau} \rangle$  where  $S_{\tau}$  is the set of states with  $act_{\tau}$  and  $end_{\tau}$  the special activation and termination states, respectively, and the remaining states  $S_{\tau} \setminus \{act_{\tau}, end_{\tau}\}$  represent the job segments set  $JS_{\tau}$ , and  $tr_{\tau} \subset S_{\tau} \times S_{\tau}$  is the transition relation. We write  $s \to s'$  if  $(s, s') \in tr_{\tau}$  and  $s \not\to s'$  otherwise. The state  $act_{\tau}$  (resp.  $end_{\tau}$ ) has no predecessors (resp. no successors), formally  $\forall s \in S_{\tau} : (s \not\rightarrow act_{\tau} \land end_{\tau} \not\rightarrow s).$ We call a maximal run in  $\tau$  each run in the FSM starting at  $act_{\tau}$  and ending at  $end_{\tau}$ , denoted  $act_{\tau} \to \cdots \to end_{\tau}$ . All runs in the FSM are finite, i.e., there are no loops. A job is the ordered set of states appearing in a maximal run, excluding  $act_{\tau}$  and  $end_{\tau}$ . Accordingly,  $J_{\tau}$  is the set of jobs in  $\tau$  and  $J = \bigcup_{\tau \in T} J_{\tau}$ (resp.  $JS = \bigcup_{\tau \in T} JS_{\tau}$ ) is the set of all jobs (resp. job segments) in the ERTS. In the remainder of this paper, the shorthand terminology "segment" refers to a job segment, and we drop  $\tau$  subscripts when they are unneeded or understood from the context. The priority function  $\pi: T \mapsto \mathbb{N}$  assigns a priority to each task. The set of HRT tasks  $T_h \subseteq T$  comprises the tasks that are not allowed to miss their deadlines, e.g., defined by the user. Each core  $c \in C$  is associated with a scheduler  $\mathcal{H}_c$  and a prioritized queue  $Q_c$  to sort tasks waiting for their release (see the behavior below).

Next, we define data/core usage and timing constraints.  $dw: JS \mapsto \mathcal{P}(L)$ (resp.  $dr: JS \mapsto \mathcal{P}(L)$ ), with  $\mathcal{P}(L)$  the powerset of L, associates each segment with the elements of data it writes (resp. reads). Note that  $dr(s) \cup dw(s)$  may be empty; our definition remains therefore generic on whether a given segment uses shared data or not. The affinity function  $aff: T \mapsto C$  associates each task to one core, and dually, a partitioning function  $prt: C \mapsto \mathcal{P}(T)$  associates each core c to the set of tasks allocated to it (i.e., the partition  $\{\tau | aff(\tau) = c\}$ ). The function  $p: T \mapsto \mathbb{N}_{>0}$  associates each task with its period, and the function  $wcs: JS \mapsto \mathbb{N}_{>0}$  (resp.  $bcs: JS \mapsto \mathbb{N}$ ) returns for each segment its WCET (resp. Best Case Execution Time BCET). Naturally, the inequality  $bcs(s) \leq wcs(s)$  is verified for every  $s \in JS$ . Finally, the function  $\rho_r : L \mapsto \mathbb{N}_{>0}$  (resp.  $\rho_w : L \mapsto \mathbb{N}_{>0}$ ) assigns each data a reading (resp. writing) penalty, i.e., the maximum time needed to read (resp. write) such data without overhead (i.e., without interference from concurrent readers/writers). Without loss of generality, we assume wcs(s), for any segment s in JS, to include the reading (resp. writing) penalty of each data in dr(s) (resp. dw(s)), which corresponds to the maximum time needed to read (resp. write) such data in the absence of contention with other readers/writers.

These definitions coincide with the informal description of a complex task

with an arbitrary number of jobs, where each job is a finite ordered set of segments, and fall under partitioned scheduling (the codomain of the affinity function *aff* is C, and thus each task is allocated to only one core). Note that our model does not assume a knowledge of BCETs; they can simply be set to 0, if unknown, without loss of generality<sup>5</sup>. Note also that the assumption on the finiteness of each run in a task FSM (absence of loops) is a natural condition since tasks are real-time and therefore must execute each job in a finite (bounded) amount of time. This absence of loops should not be mistaken for a restriction as it induces no loss of generality: the FSM definition above coincides also with real-time tasks with a loop behavior (e.g., implementing control algorithms), as we will show further in Sect. 7.

Behavior. A task  $\tau$  is activated at global time 0 (when the ERTS starts)<sup>6</sup> then at each period  $p(\tau)$ . Activating a task  $\tau$  resets its current state<sup>7</sup> to  $act_{\tau}$ . If c, the core to which  $\tau$  is allocated  $(aff(\tau) = c)$  is free, then  $\tau$  is released immediately, otherwise  $\mathcal{H}_c$  inserts its identifier in  $Q_c$  (by abuse of terminology, we call the identifier also task  $\tau$ ). The insertion algorithm guarantees that tasks in  $Q_c$  are always ordered according to their priorities (resp. their activation time) for tasks with different priorities (resp. same priority). Whenever c is free,  $\mathcal{H}_c$  pops the task at the head of  $Q_c$  and releases it. Upon release,  $\tau$  executes one of its jobs, say  $\iota$ , e.g., chosen at runtime from  $J_{\tau}$ , by traversing the path from  $act_{\tau}$  to  $end_{\tau}$ that corresponds to  $\iota$ .

Let v and v' be two variables in the domain prt(c) that continuously store the task at the head of  $Q_c$  and the task currently executing a job on c, respectively (if any, otherwise they take arbitrary values in their domain). By abuse of notation, we confound in the following these variables with their values at a given time. At each time t an insertion in  $Q_c$  happens<sup>8</sup>,  $\mathcal{H}_c$  compares  $\pi(v)$  with  $\pi(v')$ . If the latter is less than the former, then v' is marked for preemption. The preemption happens as soon as the segment of the job v' was executing at time t, say s. ends, that is at a time t' comprised between t and t + wcs(s) (+ possibly some data sharing overhead).  $\mathcal{H}_c$  then suspends the job v' is executing, inserts v' back in  $Q_c$ , pops v from  $Q_c$  and releases it. Notice that the task released at t' may be different from the one that caused the preemption of v' at t, as the value of v may have changed in between due to an insertion of a higher priority task. A preempted task, when released, resumes at the next segment of the suspended job. The semantics of execution is further formalized in Sect. 6 using TA. Notice that we do not specify here a model for concurrent access to data. The overhead of sharing data is characterized in Sect. 4 as multiples of the reading/writing

$<sup>{}^{5}</sup>$ Though it is still recommended to evaluate BCETs for a better accuracy of the analysis.  ${}^{6}$ While activation at global time zero is not mandatory, it is appropriate here since we do not consider jitters or offsets in this paper.

<sup>&</sup>lt;sup>7</sup>If such current state is  $end_{\tau}$ , otherwise there is a deadline miss and the behavior depends on the task's criticality, Sect. 6.

<sup>&</sup>lt;sup>8</sup>We recall that the insertion of a task captured by v happens only if there is another task captured by v' currently executing on c, otherwise the former would be released immediately.

penalties given by the functions  $\rho_r$  and  $\rho_w$  defined above.

# 3.2. Justifying the Scheduling Choices

Say that we have an ERTS modeled correctly as an UPPAAL network of TA (Sect. 2.3) on which we want to verify a TCTL property (Sect. 2.4). Even if the property is local (e.g., bounded response within one task), the verification must be carried out on the whole UPPAAL model since tasks behaviors depend on one another due to (i) data sharing and (ii) the possibility for a task to migrate between cores. Our goal is to break this bi-dimensional dependency as to enable compositional verification while preserving the correctness of the model. This goal is achievable under P-FP scheduling with limited preemption.

First, partitioned (P) schedulers prevent tasks migration and thus eliminate the second dimension of the dependency. The good news is, P scheduling is widely used, it is even the *de facto* choice in ERTSs [80, 81]. However, it requires computing an affinity beforehand that satisfies some schedulability requirements, which typically boils down to the bin-packing NP-hard problem [45]. Second, limited preemption makes it computationally tractable to integrate data sharing overheads in the WCETs of segments of each job independently, thus getting beyond the first dimension of the dependency. Fortunately, limited preemption is a natural and efficient choice in ERTSs. First, it may be used to prevent preemption inside a job segment (as in our model above), necessary for consist access to shared data (Sect. 2.1). Second, it is proven that, schedulabilityanalysis-wise, limited preemption is a better choice than both *full preemption* and *full non preemption* under P-FP scheduling [21].

### 3.3. Overall Approach

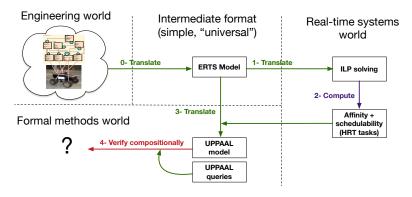

To summarize, compositional verification of ERTS is possible under P-FP scheduling with limited preemption. This requires however (i) a correct integration of data sharing overheads in each task independently and (ii) tackling the (NP-hard) affinity problem beforehand. We present accordingly our approach in Fig. 1. The input of the problem is a realistic ERTS model (Sect. 3.1) in a simple format (more in Sect. 7). Step 0 is optional, it consists in writing translators from given ERTS domains to our input format (we provide two such translators for some robotic and automotive applications, Sect. 7). Step 1 feeds the ERTS model to the ILP algorithm that we devise in Sect. 5 to compute an affinity guaranteeing the schedulability property for all tasks, or, if no such (total) affinity is found, a partial affinity such that at least all HRT tasks are schedulable (Step 2). Then, given the input model, the affinity, and the formal TA model of ERTS that we define in Sect. 6, an UPPAAL model is automatically generated (Step 3). Both the ILP algorithm and the UPPAAL model take into account all information from the input model and the semantics of P-FP scheduling with limited preemption, and integrate data sharing overheads based on the bounds we compute in Sect. 4. In Step 4, important properties are verified compositionally on the generated UPPAAL model, including a tight computation of tasks WCRTs that enables the possibility to counterbalance, a posteriori, the pessimism of the ILP pass (Sect. 6, Sect. 7).

Figure 1: Overall Approach

#### 4. The Data Sharing Problem

In an ERTS, we can model data sharing as producer-consumer patterns comprising m writers and n readers for each data  $l \in L$ . Based on the syntax of ERTS in Sect. 3.1, m and n can be defined formally for some data  $l \in L$  as follows:  $m(l) = |\{s | s \in JS \land l \in dw(s)\}|$  (the number of segments in the ERTS that write l) and  $n(l) = |\{s | s \in JS \land l \in dr(s)\}|$  (the number of segments in the ERTS that read l). We distinguish two cases: single writer (where for each data l in L, all m(l) writers belong to jobs of the same task) and multiple writers (otherwise). Under P-FP scheduling with limited preemption, we can already see that there are certain beneficial scenarios where there will be no blocking at all, i.e., if both writers and readers execute on the same core. We can also see that writers (resp. readers) will update (resp. read) data frequently, but not permanently. In the single writer case, we can therefore assume that a write operation interferes with specific readers at most once, i.e., while the reader is reading, new data arrives. With multiple writers, we can observe similar simplifications. When all writers of data l are allocated to the same core, the write operations will be serialized by the non-preemptive scheduling for free. Only when writers are allocated to different cores, write operations can happen concurrently and therefore must be protected, e.g., by using a spinlock.

For this type of synchronization problem, sequence locks (seqlocks) [42, 50, 58] are a good fit as we explain throughout this section. Seqlocks tend to favor read-heavy workloads under the optimistic assumption that no update/write of the shared data happens at the same time as readers read the data [52]. Otherwise, the read operation has to be retried, and for real-time use cases, the number of retries has to be bounded. We first compute the *total cost* of reading/writing a data, i.e., the maximum time needed to read/write a data in the presence of delays induced by concurrent access to the same data by other writers/readers. This is done through bounding the number of retries (Sect. 4.2, 4.3). Then, we deduce the data sharing overheads (Sect. 4.4). The overheads are for an ERTS under single writer seqlocks (that is, as explained above, each

Algorithm 1: Sequence lock usage (see Section 4.2)

|                             |                                                 | /                       |  |  |  |  |  |

|-----------------------------|-------------------------------------------------|-------------------------|--|--|--|--|--|

| 1 sequence lock state:      |                                                 |                         |  |  |  |  |  |

| 2                           | $s: { m spin} \ { m lock} = uncontended$        | $\lhd$ spin lock        |  |  |  |  |  |

| 3                           | $c: { m unsigned int} = 0$                      | $\lhd$ sequence counter |  |  |  |  |  |

| 4                           | $d: array of bytes = \dots$                     | $\lhd$ shared data      |  |  |  |  |  |

| 5 writer:                   |                                                 |                         |  |  |  |  |  |

| 6                           | lock $(s)$                                      |                         |  |  |  |  |  |

| 7                           | $c \leftarrow c + 1$                            |                         |  |  |  |  |  |

| 8                           | memory barrier: order $write \rightarrow write$ |                         |  |  |  |  |  |

| 9                           | $d \leftarrow \dots$ $\lhd$ update shared data  |                         |  |  |  |  |  |

| 10                          | memory barrier: order $write \rightarrow write$ |                         |  |  |  |  |  |

| 11                          | $c \leftarrow c + 1$                            |                         |  |  |  |  |  |

| <b>12</b>                   | optional artificial delay (see Section $4.3$ )  |                         |  |  |  |  |  |

| <b>13</b>                   | unlock $(s)$                                    |                         |  |  |  |  |  |

| 14 reader:                  |                                                 |                         |  |  |  |  |  |

| 15                          | 15 repeat                                       |                         |  |  |  |  |  |

| 16                          | repeat                                          |                         |  |  |  |  |  |

| <b>17</b>                   | $c_1 \leftarrow c$                              |                         |  |  |  |  |  |

| 18                          | <b>until</b> $c_1$ is even                      | $\lhd$ spin on write    |  |  |  |  |  |

| 19                          | memory barrier: order $read \rightarrow read$   |                         |  |  |  |  |  |

| <b>20</b>                   | $tmp \leftarrow d$                              | $\lhd$ read shared data |  |  |  |  |  |

| <b>21</b>                   | memory barrier: order $read \rightarrow read$   |                         |  |  |  |  |  |

| 22                          | $c_2 \leftarrow c$                              |                         |  |  |  |  |  |

| 23                          | $\mathbf{until} \ c_1 = c_2$                    |                         |  |  |  |  |  |

| 24 <b>return</b> <i>tmp</i> |                                                 |                         |  |  |  |  |  |

|                             |                                                 |                         |  |  |  |  |  |

data l is written by one task at most, i.e., all segments that write l belong to jobs in the same task). Finally, we justify the use of single writer seqlocks, as we (i) compare the computed overheads to those of other state-of-the-art locking protocols and (ii) further explain the fitness of the single writer assumption to ERTS in practice. Our approach remains nonetheless generic, as the overheads from the table given at the end of this section can be used instead for any ERTS using a different data sharing assumption (Sect. 4.5).

#### 4.1. Sequence Locks (Seqlocks)

Seqlocks are a state-of-the-art locking mechanism for read-heavy consistent access to shared data in Linux [42, 50, 58]. Seqlocks were conceived to solve starvation issues with reader-writer locks in certain use cases, such as updating the current system time from an interrupt handler [42]. Alg. 1 shows an implementation. Seqlocks use a sequence counter for reader-writer synchronization and

a spinlock for synchronization of multiple writers<sup>9</sup>. The sequence counter, e.g., a 32-bit unsigned integer initialized to zero, implements the following protocol. At the start of a write operation, the writer first increments the counter, then writes or updates the data, and finally increments the counter again. With this, an odd counter value indicates an ongoing write operation, and the upper bits of the counter define a generation counter. The read side first reads the counter, then reads the data, and then reads the counter again. If both counter values are equal and the value is even, the data was read consistently. Otherwise, the reader repeats. Also, we let the reader spin on the first counter access while the value is odd, i.e., a write operation is currently ongoing. Further, on hardware architectures with weak memory ordering, *memory barriers* are required: two read barriers on the reader side and two write barriers on the writer side to order the reads from writes to resp. the sequence counter and the data accesses.

#### 4.2. Bounding Seqlocks

The two obvious problems of seqlocks w.r.t. predictability are that the reader side can be starved by successive back-to-back writes, and that the reader side can read stale data due to the *ABA problem* when the counter repeats after  $2^{31}$  write operations [29]. Though both are unlikely to happen in real systems, we need to eliminate them to abide by safety-critical standards. To bound the number of retries on the reader side, Kopetz and Reisinger suggest a *minimum inter-arrival time*  $\delta_w$  between two successive write operations [49].

In the following, we denote by  $\hat{\rho}_r(l)$  (resp.  $\hat{\rho}_w(l)$ ) the maximum time of the total cost of reading (resp. writing) data l in the presence of overheads. With non-preemptible segments (Sect. 3.1), a write operation of some data  $l \in L$  takes therefore  $\hat{\rho}_w(l)$  time for a single writer (Lines 7 to 11 in Alg. 1), which is mainly driven by the time to access the shared data (Line 9). Further, we compose the individual steps of a read operation as the spinning part  $\rho_s(l)$  (Lines 16 to 18) and the reading part  $\rho_r(l)$  (Lines 19 to 22).

Under the condition that  $\delta_w > \rho_r(l)$ , we can construct the following worst case with at most one retry of the outer loop (Lines 15 to 23). Assume a read operation is successfully ongoing and reaches the second sequence counter check (Line 22). At the same time, a write operation starts and increments the counter (Line 7). This causes a counter mismatch on the reader side (Line 23), with spinning for the parallel write operation to finish (Lines 16 to 18) for at most  $\rho_w(l)$  time, therefore  $\rho_s(l)$  is upper-bounded by  $\rho_w(l)$ . Afterwards, the reader successfully reads the new data and the loop terminates. This takes at most  $\hat{\rho}_r(l) = \rho_r(l) + \rho_w(l) + \rho_r(l)$ . Under the assumption that both  $\rho_r(l)$ and  $\rho_w(l)$  depend on the actual size of the shared data, i.e., the number of accessed cachelines, and that both reading and writing take the same time on modern computer architectures, we can set  $\rho(l) = \rho_w(l) = \rho_r(l)$  and consequently simplify  $\hat{\rho}_r(l) = 3\rho(l)$ ,  $\hat{\rho}_w(l) = \rho_w(l) = \rho(l)$  and derive a minimum bound for  $\delta_w > \rho(l)$ .

<sup>&</sup>lt;sup>9</sup>The spinlock can be omitted in the single writer case.

#### 4.3. Implication on Task Set

The minimum inter-arrival time  $\delta_w$  between two writes solves both initial issues of bounding the loop and the ABA problem, but requires a guarantee that it is always superior to the minimum bound  $\rho(l)$ . The worst case scenario with a single writer for some data l is then two segments s and s', both writers of l ( $l \in dw(s)$  and  $l \in dw(s')$ ), executing back to back within the same task  $\tau$ . This happens for example when s, the last segment in  $\iota$ , finishes executing at exactly the end of a period of  $\tau$ , followed by immediate activation and release, in the next period, of  $\iota'$  in which s' is the first segment to execute (with  $\iota$  and  $\iota'$  two jobs of  $\tau$ ). In this case, to remain generic (i.e., independent from the execution scenarios), the solution is to *inflate* the execution time of s by  $\rho(l)$ , e.g., by inserting an artificial delay at the end of job  $\iota$ . With multiple writers, the problem gets even more complex (see the overheads summary in Sect. 4.5).

#### 4.4. Deducing Data Sharing Overheads

We can now deduce the overhead for each data l that we need to integrate in the WCETs of segments to account for the delay that they may incur while concurrently accessing l (such overhead is for instance called *blocking bound* in [19]). We introduce thus two new functions  $B_w: L \mapsto \mathbb{N}$  and  $B_r: L \mapsto \mathbb{N}$  that we may define simply as  $B_w(l) = \hat{\rho}_w(l) - \rho(l)$  and similarly  $B_r(l) = \hat{\rho}_r(l) - \rho(l)$ . That is, we simply subtract  $\rho(l)$ , the maximum time needed to read/write data l without contention (already included in segments' WCETs, Sect. 3.1), from  $\hat{\rho}_w(l)$  (resp.  $\hat{\rho}_r(l)$ ), the total cost of writing (resp. reading) l with overheads.

#### 4.5. Comparison to Spinlocks and Reader-Writer Locks

We compare seqlocks to other spinning synchronization mechanisms. We assume a system where readers and writers are distributed on all |C| cores. Table 1 shows the individual overheads of read and write operations as multiples of  $\rho(l)$  for some data l.

Task-fair spinlocks, e.g., ticket locks or MCS locks [59], serialize all read and write operations in FIFO order, so an operation has to wait at most for |C - 1| other operations to complete. We can consider this to be a worst-case baseline.

Task-fair reader-writer locks order arriving requests in FIFO order, but allow adjacent read requests to form a concurrent group until the next write request arrives [60], and the writer has to wait  $\rho(l)$  time for previous readers to finish. Later readers have to wait for the same time plus the writer's execution time.

*Phase-fair reader-writer locks* are another state of the art technique [19]. Here, requests are queued in either read or write request queues, and reader

Table 1: Comparison of data sharing overheads in dependency on  $\rho(l)$  (extending [49, 19]).

| Lock Type             |                  | Single writer                   |                   | Multiple writers   |                    |

|-----------------------|------------------|---------------------------------|-------------------|--------------------|--------------------|

|                       | Write            | $B_w(l) \mid \operatorname{Re}$ | ead $B_r(l)$      | Write $B_w(l)$     | Read $B_r(l)$      |

| Sequence lock         | ρ                | (l)                             | $2\rho(l)$        | $2( C -1)\rho(l)$  | $2\rho(l)$         |

| Task-fair locks       | ( C  -           | $-1)\rho(l)   ( C )$            | $ l  = 1)\rho(l)$ | $( C  - 1)\rho(l)$ | $( C  - 1)\rho(l)$ |

| Task-fair reader-writ | er lock $\rho$   | (1)                             | $2\rho(l)$        | $( C  - 1)\rho(l)$ | $( C  - 1)\rho(l)$ |

| Phase-fair reader-wr  | iter lock $\rho$ | (l)                             | $2\rho(l)$        | $2( C -1)\rho(l)$  | $2\rho(l)$         |

and writer phases alternate. Then, on a phase switch to readers, all waiting readers are released, so readers have to wait at most two phases of  $\rho(l)$  time. This improves the throughput of read requests at the cost of write requests. Note that the timing behavior of phase-fair reader-writer locks with a single writer is the same as for task-fair reader-writer locks.

Summarized, seqlocks behave similar to state-of-the-art locking-based approaches in the worst case, but with an improved best case timing towards the reader side. Further, the single writer assumption is reasonable in practice. This is the case for instance of state-of-the-art frameworks designed for real-time robotics, such as OROCOS [47] and MAUVE [40], and for all of the real-world case studies evaluated in Sect. 7. In the remainder of this paper, we rely therefore on overheads for single writer seqlocks, but any overhead from Table 1 may be used for the corresponding assumptions.

#### 5. Solving the Affinity Problem

In this section, we devise an ILP algorithm to compute the affinity  $aff(\tau)$  for each task  $\tau \in T$  in an ERTS, such that all tasks in T are schedulable. If no solution is found, the algorithm relaxes the constraints by removing some non-HRT task  $\tau$  from  $T \setminus T_h$  and retrying on the subset of T obtained thereof. The process is repeated until a partial affinity is found or the subset of T contains only HRT tasks, in which case it terminates with a failure. Note here that removing some non-HRT tasks does not mean that they will be removed from the application (if a partial affinity is found by the ILP algorithm, we will use it as a basis to try and find a total affinity, relying on tight computations of WCRTs, Sect. 7).

More formally, the algorithm works following the steps given below, where  $sched: T \mapsto \mathbb{B}$  is a function that returns the truth value True iff its input is a schedulable task according to some schedulability test. In sum, the algorithm either succeeds, if a total affinity (with all tasks schedulable) or else a partial affinity (with some tasks, including all HRT tasks, schedulable) is found, or fails, otherwise (more in Sect. 7).

- A. Compute an affinity such that  $\forall \tau \in T : sched(\tau)$ ,

- A.1. If a solution is found, terminate with success and return the affinity,

- A.2. Else, check the equality  $T = T_h$  ( $T_h$  is the set of HRT tasks, defined in Sect. 3.1),

- \* A.2.1. If the equality holds (there are only HRT tasks left), terminate with a failure,

- \* A.2.2. Else, update T with  $T \setminus \{\tau\}$  where  $\tau$  is selected randomly from  $T \setminus T_h$  and repeat at (A).

To specify the ILP algorithm, we need therefore to devise the schedulability tests to characterize the function *sched*. Further, we need to express all timing

constraints as linear constraints in order to enable modeling the affinity problem as an ILP one. We achieve both goals in the remainder of this section, but first we introduce some notations.

Notations. We denote by  $hp(\tau) = \{ \tau' \mid \tau' \in T, \pi(\tau') > \pi(\tau) \}$  the set of tasks with priorities higher than  $\pi(\tau)$  and  $sp(\tau) = \{ \tau' \mid \tau' \in T \setminus \{t\}, \pi(\tau') = \pi(\tau) \}$ the set of tasks (excluding  $\tau$ ) the priorities of which are equal to  $\pi(\tau)$ . Similarly,  $lp(\tau) = \{ \tau' \mid \tau' \in T, \pi(\tau') < \pi(\tau) \}$  denotes the set of tasks with priorities lower than  $\pi(\tau)$ . For a job  $\iota \in J$ , we denote by  $S_{\iota}$  the set of segments of  $\iota$ ; its WCET  $wj(\iota) = \sum_{s \in S_{\iota}} wcs(s)$ ; and the WCET of its final (last) segment final( $\iota$ ). We also denote  $J_{\iota}^{-1} \in T$  the task to which the job  $\iota \in J$  belongs. Further, we abuse the membership relation: we say that a job segment  $s \in JS_{\tau}$  belongs to task  $\tau$ . A task  $\tau \in T$  is characterized by its WCET equal to the WCET of its longest job, that is  $wt(\tau) = \max\{ wj(\iota) \mid \iota \in J_{\tau} \}$ , its utilization factor  $u(\tau) = \frac{wt(\tau)}{p(\tau)}$ , and its maximum segment WCET  $\overline{w}_s(\tau) = \max\{ wcs(s) \mid s \in JS_{\tau} \}$  (the WCET of its longest job segment).

# 5.1. Ignoring Data Sharing Overheads

#### 5.1.1. Schedulability Test

In order to facilitate the understanding of the method, we start by modeling the problem without data sharing overheads. We can therefore, under P-FP with limited preemption, consider the schedulability problem on each core independently (this assumption is obviously false when taking data sharing overheads into account). As a first step, we will therefore consider schedulability as a single-core problem. Davis and Burns propose in [27] a monoprocessor linear upper bound for the WCRT of sporadic tasks scheduled with limited preemption with arbitrary deadlines and release jitters. It is easy to adapt this test to our model, and, by considering that the sum of task utilisation factors is less than 1, a task  $\tau \in T$  is schedulable if the next inequality is verified for each of its jobs  $\iota \in J_{\tau}$ :

$blocking(\tau) + wj(\iota) + \sum_{\tau' \in sp(\tau)} wt(\tau')$

$+\sum_{\tau' \in hp(\tau)} \left[ wt(\tau') + u(\tau') \cdot (p(\tau) - final(\iota) - wt(\tau')) \right] \le p(\tau) \quad (1)$ with  $blocking(\tau) = \max \left\{ \overline{w}_s(\tau') \mid \tau' \in lp(\tau) \right\}.$

In brief, the inequality above compares an upper bound on the WCRT of  $\tau$  (left-hand operand) to the deadline of  $\tau$  (i.e., period of  $\tau$ , right-hand operand). While the original bound in [27] is exact for sporadic tasks, it becomes pessimistic for periodic tasks, and therefore for our case. Notice how, for instance,  $blocking(\tau)$ , which is an upper bound on the maximum time needed to preempt a lower priority task, is defined as equal to the maximum segment WCET of all tasks with priorities lower than  $prio(\tau)$ . This stems from the fact that schedulability tests are based on analytical formulae where one seeks linearity for practical ILP implementations. This results in computationally efficient schedulability tests that are nevertheless pessimistic in the periodic setting.

#### 5.1.2. ILP Formulation & Implementation Considerations

Since the schedulability test is linear, the affinity problem can be easily expressed as an ILP. To represent the affinity, we use  $|T| \cdot |C|$  binary decision variables  $\alpha(\tau, c)$  such  $\alpha(\tau, c) = 1$  if  $\tau \in prt(c)$  ( $\alpha(\tau, c) = 0$  otherwise). The constraints follow directly from the unicity of the task affinity (P scheduling) and the schedulability test (Inequality (1)). To represent that a task can be allocated to only one core, we use the constraint:

$$\forall \tau \in T : \sum_{c \in C} \alpha(\tau, c) = 1 \tag{2}$$

and, to represent that the utilization factor on each core is limited to 1, we use:

$$\forall \tau \in T : \sum_{c \in C} \alpha(\tau, c) \cdot u(\tau) < 1 \tag{3}$$

The only element that is not linear in Inequality (1) is the *blocking* term. To avoid this, we decompose the schedulability test given in Inequality (1) into as many constraints as tasks in  $lp(\tau)$  to get the following inequality for each job  $\iota$  of  $\tau \ (\forall \iota \in J_{\tau})$ , for each task  $\tau''$  with a lower priority than  $\tau \ (\forall \tau'' \in lp(\tau))$  and for each core c of  $C \ (\forall c \in C)$ :

$$\alpha(\tau'',c) \cdot \overline{w}_s(\tau'') + wj(\iota) + \sum_{\tau' \in sp(\tau)} \alpha(\tau',c) \cdot wt(\tau') + \sum_{\tau' \in hp(\tau)} \alpha(\tau',c) \cdot [wt(\tau') + u(\tau') \cdot (p(\tau) - final(\iota) - wt(\tau'))] \le p(\tau) \quad (4)$$

That is, we obtain Inequality 4 by decomposing Inequality (1) through considering  $\overline{w}_s(\tau'')$  separately in each lower priority task, then multiplying each term pertaining to some task  $\zeta$  by  $\alpha(\zeta, c)$  to cancel such term if  $\zeta \notin prt(c)$  (i.e.,  $\alpha(\zeta, c) = 0$ ).

However, the constraints defined in (4) must be verified only if task  $\tau$  is allocated to core c. In other words, they are true if  $\tau$  is not allocated to c, i.e.,  $\alpha(\tau, c) = 0$ . A classical way to deal with this problem is to introduce a term to guarantee that the above condition is always true. This can be achieved by adding  $(\alpha(\tau, c) - 1) \cdot M$  to the left-hand operand of the constraints (from (4)) with a huge value M (known as *big-M constraints*). So if  $\alpha(\tau, c)$  is equal to 0, the constraint is always verified, and if  $\alpha(\tau, c)$  is equal to 1, the effect of M is null. Here, we do not use this technique. Indeed, modern ILP solvers have efficient approaches to model this kind of behavior. As we use Gurobi<sup>10</sup>, we can simply add a condition to activate a constraint; here the condition is simply  $\alpha(\tau, c) = 1$ . More implementation details are given in Appendix A.

# 5.2. Taking Data Sharing Overheads Into Account

#### 5.2.1. Schedulability Test

As explained in Sect. 4, the WCET of a segment can increase if it is not allocated to the same core as other segments with which it shares data. To model this, we need to be careful as to obtain the tightest possible bounds on overheads and avoid unnecessary overpessimism. We first define a *conflict* function  $cf: JS \times L \mapsto \mathcal{P}(T)$  that returns for each segment s and data l the

<sup>&</sup>lt;sup>10</sup>https://www.gurobi.com

tasks to which other segments s' in conflict with s vis-à-vis l belong. The "in conflict" relation is defined similarly to the one in [38] but with regards to each data apart, i.e., two segments s and s' (in two different tasks) are in conflict vis-à-vis data l iff they both use l and at least one of them writes it (simultaneous readings are allowed). Formally, the conflict function is defined as follows (where  $d(-) = dw(-) \cup dr(-)$ ):

$$JS, l \in L : ((\tau' \in cf(s, l)) \Leftrightarrow \exists s' \in JS_{\tau'}, \tau' \neq \tau : (l \in dw(s) \land l \in d(s')) \lor (l \in dw(s') \land l \in d(s)))$$

(5)

Under the single-writer assumption, we can safely replace each d(-) with dr(-) thus alleviating the membership checks.

$\forall s \in$

Once the conflict function is defined, we add a conditional time overhead per data l. This overhead will be computed and integrated in the WCET of a segment s in  $JS_{\tau}$  iff the affinity of some task  $\tau'$  in cf(s, l) is not identical to the affinity of  $\tau$ . In other words, there is no need to consider the overheads related to some data l if all segments in conflict with s vis-à-vis l are executed on the same core as s. An overhead  $B_s(l)$  is thus associated with a segment  $s \in JS_{\tau}$  and the set cf(s, l) such that wcs(s) is increased by  $B_s(l)$  iff the affinity of  $\tau$  is not the same as all tasks in cf(s, l), i.e.,  $\exists \tau' \in cf(s, l) : aff(\tau') \neq aff(\tau)$ . We denote this condition CON(s, l). Accordingly, we define formally the set  $d_{con}(s) \subseteq d(s)$ , the set of data written or read by s for which  $B_s(l)$  must be integrated in wcs(s), as follows:  $d_{con}(s) = \{l | l \in d(s) \land CON(s, l)\}$ , which is simply the definition given by (5) with the further constraint that at least one task in cf(s, l) has an affinity different than that of the task s belongs to, that is:

$$\forall s \in JS, l \in L : ((l \in d_{con}(s)) \Leftrightarrow \exists s' \in JS_{\tau'}, aff(\tau') \neq aff(\tau) : (l \in dw(s) \land l \in d(s')) \lor (l \in dw(s') \land l \in d(s))) \quad (6)$$

Then, the value of the total overhead is the sum of all overheads  $B_s(l)$  for each data l in  $d_{con}(s)$ , formally:

$$wcs^{\star}(s) = wcs(s) + \sum_{l \in d_{con}(s)} B_s(l)$$

<sup>(7)</sup>

With  $B_s(l)$  equal to  $B_w(l)$ ,  $B_r(l)$  (Sect. 4) or their sum, depending on whether s only writes l, only reads l, or writes and reads l, respectively. Notice here that the overheads added to the WCET as devised by Equation 7 may still be not exact. For instance, it is possible that some data l is in  $d_{con}(s)$ , and therefore its overhead is added to the WCET of s (Equation 7). But, when analysing all behaviors of the ERTS, it turns out that s never incurs any delay when accessing l (i.e., all other segments that use l in parallel with s always use l before or after s uses it). Equation 7 is therefore another source of pessimism.

However, we recall, through the same Equation 7, that we add the overhead of data l to the WCET of a segment s iff s is effectively in conflict vis-à-vis l with another segment running on a different core, therefore Equation 7 gives us the tightest possible analytical bounds on overheads (i.e., without analyzing all the ERTS possible executions).

Accordingly, time values associated to a job  $\iota$  become  $wj^*(\iota) = \sum_{s \in S_\iota} wcs^*(s)$ , final<sup>\*</sup>( $\iota$ ) =  $wcs^*(s_{|S_\iota|})$ , and for a task  $\tau$   $wt^*(\tau) = \max\{wj^*(\iota) \mid \iota \in J_\tau\}$ , blocking<sup>\*</sup>( $\tau$ ) =  $\max\{\overline{w_s}^*(\tau') \mid \tau' \in lp(\tau)\}, \overline{w_s}^*(\tau) = \max\{wcs^*(s) \mid s \in JS_\tau\}$ .

Since  $wcs^*(s)$  can be written as a linear expression of CON(s, l) then  $wj^*(\iota)$ ,  $final^*(\iota)$ ,  $blocking^*(\tau)$ ,  $wt^*(\tau')$  are also linear. Rewriting the schedulability test (1), however, the inequality becomes quadratic due to the  $-wt^*(\tau') \cdot (final^*(\iota) + wt^*(\tau'))$  term. By considering  $wt^*(\tau') \ge wt(\tau')$ , we can derivate a linear sufficient schedulability test:

$$blocking^{\star}(\tau) + wj^{\star}(\iota) + \sum_{\tau' \in sp(\tau)} wt^{\star}(\tau') + \sum_{\tau' \in hp(\tau)} wt^{\star}(\tau') \cdot (1 + \frac{p(\tau)}{p(\tau')}) \\ - \sum_{\tau' \in hp(\tau)} \frac{wt(\tau')}{p(\tau')} \cdot (final^{\star}(\iota) + wt^{\star}(\tau')) \le p(\tau) \quad (8)$$

The new schedulability test given by Inequality (8) comprises therefore another source of pessimism due to replacing  $wt^{\star}(\tau')$  by a lower bound in a negative term. All sources of pessimism in the ILP algorithm will be summarized and further discussed at the end of this section.

#### 5.2.2. ILP Formulation & Implementation Considerations

To model the problem with shared data as an ILP, we start by defining the binary variables  $\beta(s, l, c)$ , for each segment  $s \in JS_{\tau}$  and each data l such that  $cf(s, l) \neq \emptyset$ . Then,  $\beta(s, l, c) = 1$  if and only if the task  $\tau$  that contains s and all tasks in cf(s, l) are allocated to the same core c:

$$\beta(s, l, c) = \alpha(\tau, c) \wedge_{\tau' \in cf(s, l)} \alpha(\tau', c) \tag{9}$$

This means that if  $\beta(s, l, c) = 1$  then the data l does not induce additional overhead, i.e.,  $B_s(l)$  should not be considered<sup>11</sup>.

We also introduce new continuous variables  $\gamma(s, c)$  to represent the WCET of a segment  $s \in JS_{\tau}$  on a core c. With Gurobi, we can use conditions to activate a constraint, and so  $\gamma(s, c)$  is constrained by:

$$\gamma(s,c) = \begin{cases} wcs(s) + \sum_{\{l \mid cf(s,l) \neq \emptyset\}} (1 - \beta(s,l,c)) \cdot B_s(l), & \text{if } \alpha(\tau,c) = 1\\ 0, & \text{otherwise} \end{cases}$$

(10)

For each core c, to model  $wj^*(\iota)$  (the worst-case execution time of a job  $\iota$  on core c) and  $final^*(\iota)$  (its final segment execution time), we introduce the continuous variables  $\epsilon(\iota, c)$  (resp.  $\lambda(\iota, c)$ ) constrained by:

$$\epsilon(\iota, c) = \sum_{s \in S_{\iota}} \gamma(s, c) \tag{11}$$

$$\lambda(\iota, c) = \gamma(s_{|S_{\iota}|}, c) \tag{12}$$

<sup>&</sup>lt;sup>11</sup>Remark that logical operators can be easily translated into linear constraints, e.g.,  $a = b \wedge c$  is equivalent to the system  $0 \leq b + c - 2a \leq 1$  and in general  $y = x_1 \wedge x_2 \wedge \ldots \wedge x_n$  is equivalent to the constraint  $0 \leq \sum_{i=1}^n x_i - y \leq n - 1$ . As we use the Gurobi solver, there exists a general constraint that facilitates the writing of logical operators. For instance, the constraint  $r = and_{\{x_1, \ldots, x_n\}}$  states that the binary variable r equals 1 iff all of the binary variables  $x_1, \ldots, x_n$  are equal to 1. Thus, for  $s \in JS_{\tau}$  and for all l such that  $cf(s, l) \neq \emptyset$ , we can simply rewrite in Gurobi the constraint on  $\beta(s, l, c)$  as  $\beta(s, l, c) = and_{\{\alpha(\tau, c), \alpha(\tau', c) \mid \tau' \in cf(s, l)\}}$ .

For modeling blocking<sup>\*</sup>( $\tau$ ) and  $wt^{*}(\tau)$ , we introduce the intermediate continuous variables  $\nu(\tau, c)$ , resp.  $\delta(\tau, c)$ , that represent the blocking time (resp. the worst-case execution time) of a task  $\tau$  on a core c. These new variables are constrained by:

$$\nu(\tau, c) = max \{ \gamma(s, c) \mid s \in JS_{\tau'}, \tau' \in lp(\tau) \}$$

$$(13)$$

$$\delta(\tau, c) = max_{\{\epsilon(\iota, c) \mid \iota \in J_{\tau}\}}$$

(14)

where the global constraint  $max_{-}$ , defined in Gurobi, sets a decision variable to the max of a list of decision variables.

With all these new intermediate variables, Inequality (8) becomes (under the conditional activation  $\alpha(\tau, c) = 1$ ):

$$\nu(\tau'',c) + \epsilon(j,c) + \sum_{\tau' \in sp(\tau)} \delta(\tau',c) + \sum_{\tau' \in hp(\tau)} \delta(\tau',c) \cdot (1 + \frac{p(\tau)}{p(\tau')}) - \sum_{\tau' \in hp(\tau)} u(\tau') \cdot (\lambda(j,c) + \delta(\tau',c)) \le p(\tau) \quad (15)$$

# 5.3. Summary and Discussion

We obtain therefore a complete ILP formulation of the schedulability test that takes into account fine-grained data sharing overheads. This test populates the definition of the *sched* function in the overall algorithm described at the beginning of this section. However, as explained earlier, linear schedulability tests remain pessimistic in the periodic setting. We identify at least three sources of pessimism in the final schedulability test given by Inequality 8:

- Upper-bounding the blocking term, stemming from Inequality 1, as explained under Sect. 5.1.1,

- Lower-bounding the negative term in the left-hand operand to linearize the test, as explained under Sect. 5.2.1,

- Upper-bounding data-sharing overheads, stemming from Equality 7, as explained under Sect. 5.2.1.

We will eliminate a posteriori all sources of pessimism except for the last one (due to upper-bounded overheads) by exploring all the possible behaviors of the ERTS through compositional model checking (Sect. 6, 7). The last source of pessimism remains because such exploration is based on a model where data sharing overheads are integrated in segments' WCETs following Equality 7 (Sect. 6). However, in practice, this last source of pessimism (based on a fine-grained model as explained in Sect. 4 and throughout this section) has a limited effect on WCRTs (and therefore on schedulability) compared to the first two sources of pessimism (more details in Sect. 7). We argue that this is a fair price to pay in order to enable compositional, scalable verification (Sect. 7.4).

# 6. TA Model & Compositional Verification

In this section, we develop a TA model in UPPAAL of a realistic ERTS (following the definitions given in Sect. 3) on which various real-time properties

can be verified compositionally. In Sect. 6.1, we detail our UPPAAL model taking data sharing overheads (Sect. 4, 5) and an affinity (Sect. 5) into account. Then, we show how properties can be verified on our model compositionally (Sect. 6.2). In the remainder of this paper, we simply write wcs(s) to denote the WCET of segment s in which data sharing overheads (Sect. 4, 5) have been integrated. In other words, we use wcs(s) to denote  $wcs^*(s)$  defined in Sect. 5.

#### 6.1. UPPAAL Model

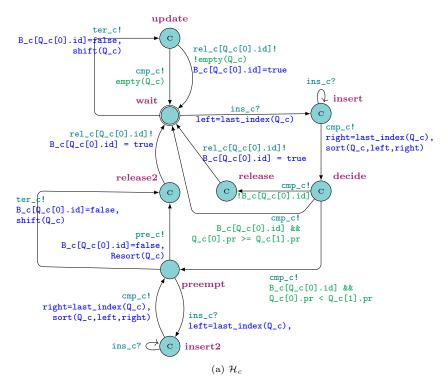

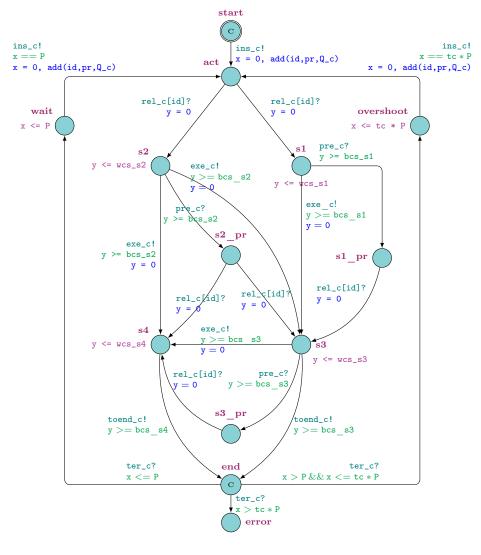

A network  $N = (||_{c \in C} N_c)$  models the ERTS. Each  $N_c = (\mathcal{H}_c||_{\tau \in prt(c)} TA_{\tau})$  is a network with  $\mathcal{H}_c$  (resp. each  $TA_{\tau}$ ) a TA modeling the scheduler of (resp. a task allocated to) core c. We give a generic description of any  $N_c$  with a scheduler and an arbitrary number of tasks allocated to c. We first describe  $TA_{\tau}$  apart, i.e., outside  $N_c$ . Then, we explain how they are composed, using synchronizations via channels and data variables, with  $\mathcal{H}_c$  to get  $N_c$  ( $\mathcal{H}_c$  is universal so there is no need to present it outside of  $N_c$ ) as to comply with the behavior in Sect. 3.1.

# 6.1.1. Task $TA_{\tau}$ (Without Synchronizations)

For each task  $\tau = \langle S_{\tau}, act_{\tau}, end_{\tau}, tr_{\tau} \rangle$  (Sect. 3.1) in prt(c), we want to generate a timed automaton  $TA_{\tau} = \langle L_{\tau}, l_{\tau 0}, X_{\tau}, E_{\tau}, I_{\tau} \rangle$ . For simplicity, we drop  $\tau$  subscripts and write  $l \to l'$  instead of  $(l, g, \lambda, l')$  when the values of g and  $\lambda$  are unimportant or discussed further in the text. We also write  $l \to (\text{resp.} \to l)$  to denote all outgoing (resp. incoming) edges of l. We first give formal definitions interspersed with informal explanations, then provide an example to illustrate.

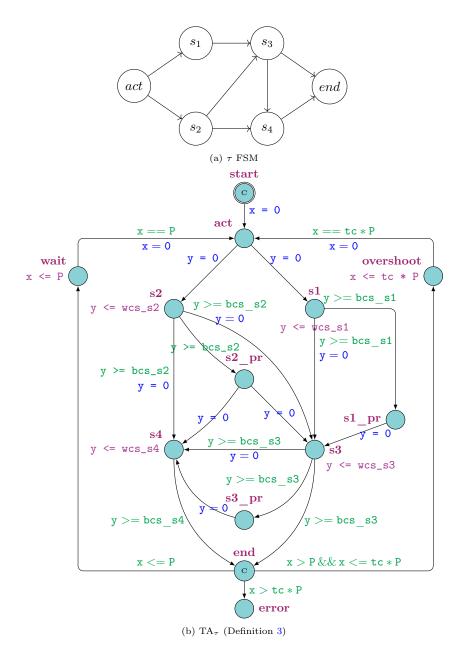

**Definition 1** ( $TA_{\tau}$ : Locations & edges). Locations and edges of  $TA_{\tau}$  are obtained by applying the following rules to  $\tau$ :

(1) Locations: each  $s \in S$  is mapped to a location with the same name in L. Location *end* is committed. Additional locations are *start* (committed), *wait*, and, for each  $s \in S \setminus \{act, end\}$  s.t.  $\exists (s, s') \in tr, s' \neq end$ , a location  $s_{pr}$ . The initial location is *start*.

(2) Edges: each transition  $(s, s') \in tr$  is mapped to an edge  $s \to s'$  in E. Additional edges are (i)  $start \to act$ ,  $wait \to act$ ,  $end \to wait$ , and (ii) for each locations' couple  $(s, s_{pr}), s \to s_{pr}$  and  $s_{pr} \to s'$  for each  $s' \neq end$  successor of s.

$TA_{\tau}$  preserves the structure of  $\tau$ . Added location *start* (resp. *wait*) and its outgoing edge to *act* models activation at time 0 (resp. at each period).

Edge  $s \to s_{pr}$  (resp  $s_{pr} \to s'$ ) models preemption (resp. resuming after preemption) where s' is a successor of s in the underlying FSM. The former is taken after executing s (see below). Locations  $s_{pr}$  are unneeded when  $\tau$  terminates after executing s (hence the condition of having at least one successor different from end, rule (1)). For similar reasons, end is excluded from the successors of  $s_{pr}$  (rule (2), see a more detailed explanation on this aspect in the example below). Note that locations  $s_{pr}$  are superfluous for tasks having the highest priority in prt(c) (as they are never preempted). **Definition 2** ( $TA_{\tau}$ : Clocks & timing constraints). Clocks, guards and invariants in  $TA_{\tau}$  (Definition 1) are defined as follows:

(1) Clocks:  $X = \{x, y\}.$

(2) Guards and resets: For edges  $(s, g, \lambda, act)$ ,  $g = \top$   $(g = (x = p(\tau))$  if s = wait)and  $\lambda = \{x\}$ . For edges  $(s, g, \lambda, s_{pr})$ ,  $g = (y \ge bcs(l))$  and  $\lambda = \emptyset$  and for edges  $(s_{pr}, g, \lambda, s')$ ,  $g = \top$  and  $\lambda = \{y\}$ . For the edge  $(end, g, \lambda, wait)$ ,  $g = (x \le p(\tau))$ and  $\lambda = \emptyset$ . For the remaining edges  $(s, g, \lambda, s')$ ,  $g = (y \ge bcs(l))$  and  $\lambda = \{y\}$ . (3) Invariants:  $I(wait) = (x \le p(\tau))$ . Locations act and  $\{s_{pr} | s \in L\}$  are invariant free. Each location mapping a segment from  $s \in S \setminus \{end, act\}$  (Definition 1) is associated with the invariant  $y \le wcs(s)$ .

Clock y models the execution of a segment s through residing in location s for an amount of time between bcs(s) and wcs(s). Locations  $s_{pr}$  are invariant free as they model preemption for an *a priori* unknown amount of time. Constraints over x ensure that  $\tau$  is activated at exactly each period. Location *end* is committed to allow reactivation as soon as possible.