## Thermal and statistical analysis of various AlN/GaN HEMT geometries for millimeter Wave applications

Nasri Said, Kathia Harrouche, F Medjdoub, N. Labat, Jean-Guy Tartarin, N. Malbert

### ▶ To cite this version:

Nasri Said, Kathia Harrouche, F Medjdoub, N. Labat, Jean-Guy Tartarin, et al.. Thermal and statistical analysis of various AlN/GaN HEMT geometries for millimeter Wave applications. IEEE International Reliability Physics Symposium (IRPS 2023), Mar 2023, Monterey, CA, United States. 10.1109/IRPS48203.2023.10117807. hal-04125371

HAL Id: hal-04125371

https://hal.science/hal-04125371

Submitted on 13 Jun 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thermal and statistical analysis of various AlN/GaN HEMT geometries for millimeter Wave applications

N. Said<sup>1,2</sup>, K. Harrouche<sup>3</sup>, F. Medjdoub<sup>3</sup>, N. Labat<sup>1</sup>, JG. Tartarin<sup>2</sup> and N. Malbert<sup>1</sup>

1. IMS Laboratory-Bordeaux University, France 2. LAAS-CNRS, Toulouse, France 3. CNRS-IEMN, Lille, France

Abstract- Downscaling HEMT devices is nowadays substantial to allow their operation in the millimeter wave frequency domain. In this work, the electrical parameters of three different AlN/GaN structures featuring various GaN channel thicknesses were compared. After a DC stabilization procedure, 96 HEMT devices under test exhibit a minor dispersion in DIBL and lag rates, which reflects an undeniable technological mastering and maturity. Evaluation of the sensitivity of devices with different geometries at temperatures of up to  $200^{\circ}\text{C}$  revealed that the gatedrain distance impacts  $R_{on}$  variation and not  $I_{dss}$  variation with temperature. We also showed that DIBL at moderate electrical field and the drain lags exhibit athermal behavior; unlike gate lag delays which can be thermally activated and exhibit a linear temperature dependence regardless of the size of the gate length.

Keywords- GaN, HEMT, on-resistance Ron, DIBL, traps, Idss

#### I. INTRODUCTION

Modern telecommunication systems such as 5G, military wireless communication and radar amplifiers are applications that imply high power, high temperature and high frequency operation, with high level of confidence on the reliability. GaN technology is the optimal candidate to fulfill these requirements [1]. In order to increase the frequency range to mmWave and maintain a high power-added / output power density combination, downscaling the gate length (L<sub>G</sub>) in HEMT devices is crucial. Decreasing L<sub>G</sub> should therefore be associated to epi-layer downscaling (e.g. channel thickness t<sub>ch</sub>) to ensure strong electron confinement and high electron density in the 2D-Electron-Gas (2DEG). The ultrathin AlN barrier on GaN channel meets these criteria [2-3]. However, a trade-off must be implemented to ensure high reliability of the active device considering the high junction temperature sensitivity, which could lead to transistor degradation, especially under high current and high voltage biasing. In this work, a statistical analysis of relevant electrical parameters of 3 different AlN/GaN structures featuring various tch for 2×100µm gate width transistors was conducted in a safe operating area using and pulsed DC measurement setup. characterization was also carried out to monitor the main electrical parameters variation with temperature (T°).

#### II. DEVICE FABRICATION

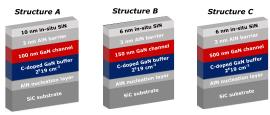

The AlN/GaN-on-SiC HEMT devices previously described in [4] were grown by metal organic chemical vapor deposition. Three different device structures A, B and C that have the same epitaxy but differ in their GaN  $t_{ch}$  (100nm, 150nm and 500nm respectively [**Fig. 1**]) were characterized. Transistors featuring different geometries ( $L_G$  [100nm, 150nm, 250nm, 500nm], gate-to-drain distances  $L_{GD}$  [1.5 $\mu$ m and 2.5 $\mu$ m]) have been developed for each of these 3 technological processes.

#### III. DATA/RESULTS AND DISCUSSION

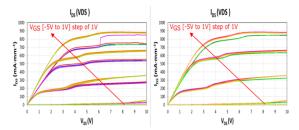

**Electrical Characterization.** Before initiating an exhaustive and systematic statistical characterization procedure, having a stable operating device is mandatory. A dedicated measurement protocol has been developed to ensure the stability of the DC measurements throughout the characterization campaign. We

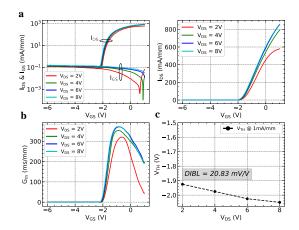

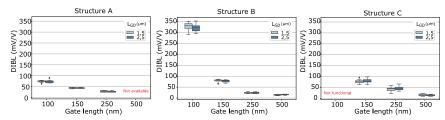

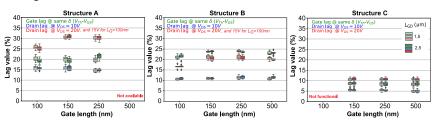

validated its efficiency through the reduction of the measurement dispersion, as illustrated for the output characteristics of 2 twin devices (Fig. 2). Drain Induced Barrier Lowering (DIBL) is extracted, as well as the transconductance profile with V<sub>GS</sub> for different V<sub>DS</sub> voltages (Fig. 3). DIBL values are weakly scattered, with no impact of L<sub>GD</sub> as expected, but with an inverse sensitivity to L<sub>G</sub>, which suggests a less important electron confinement (an effect that is less marked for small tch [Fig. 4]). The availability or functionality of devices of each tch, according to LG, will be discussed in the final paper. In order to quantify lag rates at different quiescent voltages in pulsed DC measurements, we determine the power ratio variation [5] (data not shown). Lag values are less dispersed and mostly depend on  $t_{ch}$ , but not on  $L_G$  nor  $L_{GD}$  (Fig. 5). The activation of traps seems to significantly increase when t<sub>ch</sub> decreases. This effect could arise from the proximity of the carbon-doped region with the 2DEG. Among the 3 studied structures, we find that structure A enables efficient device operation with an L<sub>G</sub>=100nm, but not structure B which exhibits high DIBL, nor structure C that is not functional at this L<sub>G</sub>. Nevertheless, trap activation is highly pronounced in structure A compared to structures B and C.

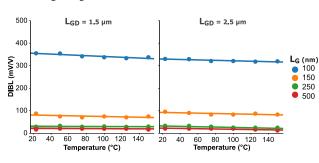

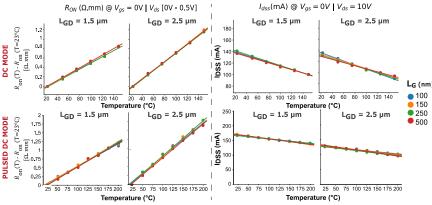

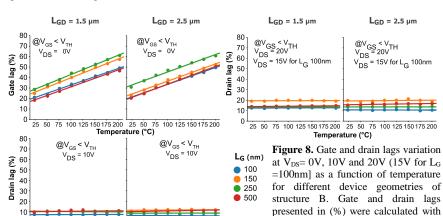

Thermal analysis. We focus the thermal analyses on the intermediate B structure as it encompasses all geometric variations for  $L_G$  and  $L_{GD}$ . The variation of DIBL,  $R_{\text{on}}$ ,  $I_{DSS}$  and lag rates with T° are assessed. DIBL is not significantly changed after exposure to T° of up to 150°C and maintains same levels compared to room  $T^{\circ}$  (**Fig. 6**). These results suggest a high thermal stability, even for devices featuring the smallest L<sub>G</sub>=100nm (which usually exhibit a degraded electron confinement). I<sub>DSS</sub> variation with T° is independent of L<sub>G</sub> and L<sub>GD</sub> and twice greater in DC than in pulsed DC mode, due to the impact of the junction  $T^{\circ}$  on the electron mobility (**Fig. 7**). The relative variation of R<sub>ON</sub> (T°) in the two characterization modes is L<sub>G</sub>-independent but L<sub>GD</sub>-dependent. The variation of ~6.4 m $\Omega$ .mm/°C for L<sub>GD</sub>=1.5 $\mu$ m and 9.3 m $\Omega$ .mm/°C for  $L_{GD}$ =2.5 $\mu$ m is attributed to the access resistances  $T^{\circ}$ dependence (Fig. 7). Finally, Fig. 8 shows that as T° reaches 200°C, only the drain lag rates remain constant. Gate lag rates increase with T°, probably consequently to the positive shifting of threshold voltage with T°. As the transistor is more pinched off, a greater activation of electron traps is involved at the AlN/GaN vicinity of the 2DEG under the gate [6].

#### IV. CONCLUSIONS

This study highlights the strengths and weaknesses of 3 low dispersed AlN/GaN topological structures featuring different  $t_{ch}$ . Adjusting  $t_{ch}$  allows transistor operation at high frequencies while controlling the impact of traps on its electrical behavior. The thermal characterization showed a negligible effect of  $T^{\circ}$  on the DIBL values. We also documented the impact of traps on gate lag, resulting from thermal and electrical activation, and drain lag  $T^{\circ}$  independency. This representative study will be completed with step stress tests to compare structures robustness and identify their safe operating area.

#### REFERENCES

- [1] U.K.Mishra, P.Parikh and Yi-Feng Wu, "AlGaN/GaN HEMTs-an overview of device operation and applications," *Proceedings of the IEEE*, vol.90, no.6, pp.1022-1031.

- [2] T. Zimmermann et al., "AlN/GaN insulated-Gate HEMTs with 2.3 A/mm output current and 480 mS/mm transconductance," *IEEE Electron Device Letters*, vol.29, no.7, pp.661-664, July 2008.

- [3] F.Medjdoub, M.Zegaoui, D.Ducatteau, N.Rolland and P.A.Rolland, "High-performance Low-Leakage-Current AlN/GaN HEMTs grown on silicon substrate," *IEEE Electron Device Letters*, vol.32, no.7, pp.874-876, July 2011.

- [4] K.Harrouche, R.Kabouche, E.Okada and F. Medjdoub, "High performance and highly robust AlN/GaN HEMTs for millimeter-Wave Operation," *IEEE Journal of the Electron Devices Society*, vol.7, pp.1145-1150.

- [5] F.Magnier, B.Lambert, C.Chang, A.Curutchet, N.Labat, N.Malbert, "Investigation of trap induced power drift on 0.15 µm GaN technology after aging tests", Microelectronics Reliability, vol 100–101

- [6] J.G. Tartarin, O. Lazar, A. Rumeau, B. Franc, L. Bary, B. Lambert, "Analysis of drain current transient stability of AlGaN/GaN HEMT stressed under HTOL & HTRB, by random telegraph noise and low frequency noise characterizations"; Elsevier Microelectronics Reliability Volume 114, Nov. 2020.

**Figure 1.** Schematic illustration of different stacked layers of AlN/GaN on SiC epi-taxial structures, all featuring  $2 \times 10^{19}$  cm<sup>-3</sup> Carbon-doped GaN buffer but with different channel thicknesses (A: 100nm, B: 150nm & C: 500nm).

**Figure 2.** Output characteristics  $I_{DS}(V_{DS})$  in mA.mm<sup>-1</sup> of twin devices (2×100µm,  $L_{G}$ =500nm  $L_{GD}$ =2.5µm of structure B) with  $V_{GS}$  swept from -5V to +1V with 1V step, before (left panel) and after stabilization (right panel).

Figure 3. Transfer characteristics with V<sub>DS</sub> sweep [2V to 8V] with a 2V-step, (a) I<sub>DS</sub> and I<sub>GS</sub> in logarithmic scales (mA/mm) and in linear scale, (b) transconductance profile  $g_m(ms/mm)$  and (c) DIBL =  $\frac{\Delta V_{TH}}{\Delta V_{DS}}$  (mV/V).

Figure 4. Statistical dispersion of DIBL values for the different structures as a function of gate length  $L_G$  and gate-to-drain distance  $L_{GD}$ .

Figure 5. Statistical dispersion of gate and drain lag values at different quiescient voltages as a function of gate length  $L_G$  and gate-to-drain distance  $L_{GD}$ . Gate voltage is applied with respect to a negative constant of  $\delta(V_{GS}-V_{TH})$  for all devices (because  $V_{TH}$  changes with  $L_G$ ). Drain voltage  $V_{DS}=0$ V for all gate lag measurements.

Figure 6. DIBL variation as a function of temperature up to  $150^{\circ}\text{C}$  for devices from structure B with different gate lengths L<sub>G</sub>, for L<sub>GD</sub> =1.5 $\mu$ m (left) and L<sub>GD</sub> =2.5 $\mu$ m (right).

**Figure 7.** Relative variation of  $R_{on}$  and  $I_{dss}$  for devices from structure B with different gate lengths  $L_G$  and gate-to-drain distances  $L_{GD}$ , as a function of temperature in DC mode (up to 150°C) and in pulsed DC mode (up to 200°C).

power ratio methods.

Temperature (°C)