# Device Reliability to Circuit Qualification: Insights and Challenges

F. Cacho, Alain Bravaix, T. Garba Seybou, H. Pitard, X. Federspiel, T. Kumar, F. Giner, A. Michard, D. Celeste, B. Miller, et al.

# ▶ To cite this version:

F. Cacho, Alain Bravaix, T. Garba Seybou, H. Pitard, X. Federspiel, et al.. Device Reliability to Circuit Qualification: Insights and Challenges. International Integrated reliability Workshop (IIRW) 2022, Oct 2022, South Lake Tahoe, CA, USA, France. pp.1-7, 10.1109/IIRW56459.2022.10077885. hal-04124032

HAL Id: hal-04124032

https://hal.science/hal-04124032

Submitted on 9 Jun 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Device Reliability to Circuit Qualification: Insights and Challenges

(Invited Paper)

F. Cacho<sup>1</sup>, A. Bravaix<sup>3</sup>, T. Garba Seybou<sup>1,3</sup>, H. Pitard<sup>3</sup>, X. Federspiel<sup>1</sup>, T. Kumar<sup>1</sup>, F. Giner<sup>1</sup>, A. Michard<sup>1</sup>, D. Celeste<sup>1</sup>, B. Miller<sup>1</sup>, V. Dhanda<sup>2</sup>, A. Varshney<sup>2</sup>, V. Tripathi<sup>2</sup>, J. Kumar<sup>2</sup>

<sup>1</sup> ST Microelectronics, 850 rue Jean Monnet, 38926 Crolles, France, Phone: (+33) 438922007, <u>florian.cacho@st.com</u>

<sup>2</sup> ST Microelectronics, Knowledge Park III, Greater Noida, Uttar Pradesh 20130, India

<sup>3</sup> ISEN Yncréa Méditerranée, IM2NP UMR 7334, Maison des technologies, Place G. Pompidou, 83000 Toulon - France Phone: (+33) 607729611, alain.bravaix@isen.fr

Abstract— Aging phenomena are first evidenced at device level to cell level considering a precise knowledge of the leading degradation mechanisms and interactions useful for processing optimization focusing performance vs. reliability requirements. Digital to analog circuits are then studied for product qualification based on the former results that needs specific methodologies adapted case by case with mission profile and the correlation between sensing parameter, accelerating factors for lifetime margin. This represents huge challenges for operational lifetime determination, considering top down and bottom up consistencies for relevant product qualification.

Keywords: Wearout, Bias Temperature Instabilities, Hot carriers, Hard Breakdown, damage interaction, HTOL.

## I. INTRODUCTION

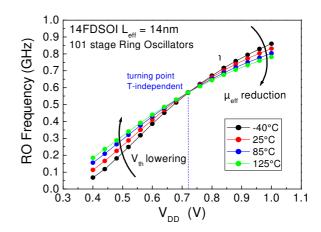

Since the first developments of integrated circuit (IC) processing, CMOS technologies have shown tremendous ability for scaling dimensions (W<sub>G</sub>/L<sub>G</sub>) towards nanometer size, frequency (F<sub>Clk</sub>) increase and consumption (P<sub>Tot</sub>) reduction for low power (LP) applications [1, 2]. The huge investments in optimizing performances in speed, static (P<sub>DC</sub>) and dynamic (P<sub>AC</sub>) power, have faced the necessity to guaranty the reliability of devices and circuits targeting a supply voltage range (V<sub>DDmin</sub>, V<sub>DDmax</sub>) Fig.1, while increasing transistor density and the use of various operational functions for digital and analog applications [3, 4]. Even if  $V_{DD}$  has been reduced accordingly to the device size, the increase in temperature (Fig.1), electric field and current density have raised a great attention for reliability requirements with the need of a good electrostatic control and the strong reduction of equivalent oxide thickness (EOT) for the gate dielectric of Si-bulk to FDSOI planar transistors [1-3]. This consequently moved MOSFET architecture from 2D to 3D and multi-gate FinFETs where lattice temperature, design and contact quality [5] are known to strongly influence the performance and reliability risks [6, 7]. This led the manufacturers to develop front-end reliability tests in order to guaranty the robustness of ICs that need a complete examination of Wearout mechanisms at device level, as hot-carrier damage (HCD), bias temperature instability (BTI) and soft to hard gate-oxide breakdown (SBD, HBD) [8] that may balance their contributions in the overall wearout. This leads to the big challenge of a proper modelling of

**Fig. 1 :** Ring Oscillator (RO) frequency dependence as a function of supply voltage  $V_{DD}$  for different temperatures. The main efffects of  $V_{th}$  shift and mobility reduction ( $\mu_{eff}$ ) is distinguished as the performance criteria on switching speed for digital application in 14nm FDSOI (HKMG) CMOS node.

all mechanisms with the right acceleration factor that takes the lead in MOSFETs, Then, this must be transferred up to digital cells with interacting phenomena [9, 10], chained in the critical paths, forming elementary functions into the block (bottom up approach). However, this methodology which is valid for process optimization presents limitations at the circuit level with the increase in device/cell density and complexity [8, 9]. One can deal with this issue by an accurate analysis of circuit aging (top down approach) using high temperature operational lifetime (HTOL) tests with in-situ monitors that give a precise qualification of products [11].

Invited paper IIRW 2022

In this paper, the main contribution of aging phenomena is studied in section II in different CMOS nodes coming from LP 28nm FDSOI (HKMG gate stack) and smart power extended drain (EDMOS with SiO2 gate oxide). We restricted the work here to HCD, BTI mechanisms which may trigger HBD in some configurations [12]. Drain current reduction ( $\Delta I_{DS}$ ) is described by  $V_{Th}$  shift ( $\Delta V_{Th}$ ), mobility reduction ( $\Delta \mu_{eff}$ ) and source-drain resistance increase ( $\Delta R_{SD}$ ) whereas each contribution depends on the leading damage mechanism (defect density and spread) and on drain to channel architecture. Section III deals with the challenge of device modelling considering the sense effects and temperature impacts [10] through interacting damage mechanisms in switched transistors between Off-mode and Onmode when channel carriers from different energy ranges are involved [12]. The last part (Section IV) gives insights in digital to analog circuits for a realistic reliability determination using HTOL in Ring Oscillators (RO), SRAM cell, Low Drop-Out  $\widehat{\mathfrak{L}}$ regulator (LDO) and ADC circuit that illustrate the product reliability qualification.

## II. AGING PHENOMENA IN PLANAR CMOS NODES

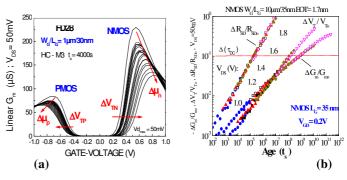

Hot-carrier damage, BTI and soft breakdown are known to be the first consequences of Wearout mechanisms in MOSFETs that may trigger HBD of gate-oxide [13] depending on the structure resistance and power level requirement [14]. A figure of merit for process quality is to determine the worst-case of aging in transistors using accelerated DC stressing that can be transferred to cycling transistors in digital cells with quasi-static modeling under medium frequency range [15]. Time to breakdown was recently reconsidered at high frequency in circuits (1GHz) where a net gain is observed [16]. The persistence of HCD with nominal supply voltage (V<sub>DD</sub>) reduction and size scaling has moved the modeling from lateral of field acceleration to an energy dependence paradigm [17, 18]. As supply voltage V<sub>DD</sub> does not scale accordingly to gate-length (L<sub>G</sub>) reduction due to performance requirements [19], the effective field in the channel strongly rises leading to mobility reduction (Fig.2a) that can be expressed as a function of the distinct scattering phenomena in the channel [20]. It is shown in Fig.2b that for a given HC mechanisms, here at  $V_{GS} > V_{DS}$  (HC-M3) [15], the transistor parameter sensitivity is larger for  $R_{SD}$ increase (gate-drain region), then followed by  $\mu_{eff}$  reduction (channel damage) and V<sub>Th</sub>-shift (extension towards the source).

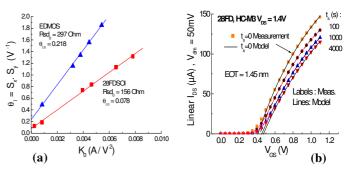

We have modelled the effective mobility  $\mu_{eff}$  as a function of mobility attenuation factors  $(\theta_1(t_s)$ ,  $\theta_2(t_s))$  that can be related to source-drain resistance increase  $(R_{SD}(t_s))$ , using first [21] or second order modelling [22]-[23] that were used in fresh devices. The technique is based on the useful Y-function [24] that allows us to use a self-consistent extraction methodology for  $R_{SD}(t_s)$  extraction during stressing at low-field measuring condition [23]. As the attenuation factor is  $\theta_1(t_o) = \theta_{1o} + K_oR_{SDo}$ , with the geometry factor  $K_o = \mu_{oo} C_{ox} W_G/L_{eff}$ , one can extract for a direct determination in **Fig.3a**  $\theta_{1o}$  (Y-intercept) and  $R_{SDo}$  (slope) in Extended Drain (EDMOS) and 28FD and do it subsequently as a function of stress time  $(t_s)$  in **Fig.3b** for 28nm FDSOI devices.

$$I_{DS} = \frac{K_{eff} \cdot (t_S) V_{GT}(t_S) V_{DS}}{1 + \theta_1(ts) V_{GT}(ts) + \theta_2(ts) V_{GT}^2(ts)}$$

(1)

$$K_{\text{eff}}(t_S) = \mu_{\text{ot}}(t_S) C_{\text{ox}} \frac{W}{L_{eff}}, \qquad (2a)$$

$$\theta_1 = \theta_{1.0} + K_{\text{eff}} (t_S) * R_{\text{SD}}(t_S)$$

(2b)

$$\theta_2 = \theta_{2.0} + K_{\text{eff}}(t_c) \lambda(t_c)$$

(2c)

**Fig. 2 :** (a) Reduction in transconductance  $(G_m)$  due to mobility decrease and  $V_{Th}$  shift in N- and P- channel devices (28FD) under HC mode M3 ( $V_{GS} > V_{DS}$ ). (b) Relationship of N-MOSFET degradation to the Age( $t_s$ ) function expressed as function of the acceleration factor in LP 28nm HKMG stack with equivalent oxide thickness EOT = 1.7nm.

**Fig.3:** (a) Direct extraction of  $\theta_{1o}$  (Y-intercept) and  $R_{SDo}$  (slope) that is compared to the product of Y=  $I_{DS}/G_m^{0.5}$  and X=  $G_m^{-0.5}$  functions [22] in fresh 28FD and EDMOS devices. (b) Corresponding linear  $I_{DS}$  -  $V_{GS}$  dependence in 28FD compared between models (lines) and measurements (labels) under HCD M3 mode ( $V_{GS} > V_{DS}$ ).

Based on  $I_{DS}$  expressed with (1)-(2a-c) and the use of Y- and X- functions, this allows to obtain the  $\theta_1(t_s)$  and  $\theta_2(t_s)$  factors in **Fig.3b** that lead to  $R_{SD}(t)$  extraction considering a fixed sensing  $V_{GT}$  range dedicated to  $\theta_1$  and  $\theta_2$  extraction [22, 23], and assuming constant  $(\theta_{1o}, \theta_{2o})$  values with  $L_G$  variable in (2b)-(2c). Moreover, we have  $K_{eff}(t_s)/K_o(0) = \mu_{ot} / \mu_{oo} = G_m(t_s)/G_m(0)|_{max}$  giving the relationship to low-field peak mobility with time.

As EDMOS HCD structure is limited to  $R_{SD}$  increase in the drift zone [14], short channel FDSOI with  $L_{G}$ = 35-14nm in **Figs.1-3** is rather a combination of strong  $\mu_{eff}$  reduction,  $\Delta V_{T}$  and  $\Delta R_{SD}$  (**Figs.2a,b**) showing the phonon to surface roughness scatterings in conjunction to multi vibrational excitation (MVE)

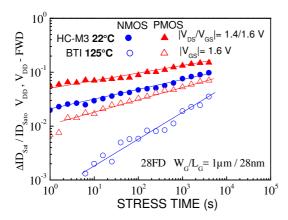

of Si-H and Si-O bonds under HCD in the high  $V_{GS}$  range [19]. The persistence of HCD at low voltage was explained by a general thermal modeling depending on the local heat through self-heating (SH) contribution [5], the bond dissociation probability, dependent on the MVE properties through current driven modeling [15], the implication of a BTI ( $V_{G}$  only) effect into the HCD mechanism [25], or by a coupled modeling between bond dissociation and SH mechanism based on the description of the phonon transport equation [26]. Fig.4 shows that HCD under M3 mode ( $V_{DS}$ = 1.4V) is clearly more degrading the 28FD structure at room temperature than BTI

**Figure 4:** Reduction in drive current  $\Delta ID_{Sat}(V_{DD},V_{DD})$  under BTI stress at 125°C and HC-M3 stress at 22°C in N- and P- channel FDSOI  $W_G/L_G$ = 1 $\mu$ m / 28nm (Low-V<sub>T</sub>, HKMG HfO<sub>2</sub>/SiON) CMOS node.

stress carried out at 125°C. Furthermore, P-channel worsens HCD with channel holes compared to N-channel which is opposite to the classical HCD result. This may be explained by SH or NBTI contribution in P-channel under DC stressing. The distinction between each contribution requires to use alternating DC voltage stressing and AC stressing which is pulse shape dependent (t<sub>r,f</sub> / T<sub>AC</sub>, duty cycle), in order to identify the dominant behavior vs. time and frequency (ts, fAC). This becomes more complicated due to thermal implication whereas HCD increases with temperature [27] which is strongly dependent on the technology scaling, the thermal resistance of the structure and shapes [28], [29] i.e. on the property to maintain local heat (with effective temperature  $T_{eff} > T_{Lat}$ ) or evacuate it by cooling energetic carriers [5]. We propose in the following to describe some examples developed in different CMOS nodes used to assess the role of the main degradation mechanisms.

# III. CHALLENGES OF AGING DEVICE MODELING

The first attention to be paid under accelerating stressing condition is to determine the role of switching MOSFET between Off and On modes as distinct regions are submitted to distinct defect generations which may be related to HBD. Thus, the first subsection 3.A presents some ways to distinguish On to Off mode stressing, then followed by the study of sensing effects (subsection 3.B) with temperature in short channel LP CMOS technologies.

#### A. On and Off mode degradation

HCD in DC "On-state" mode is modelled through a simple model based on physical theories depending on carrier energy related to lateral electric field, and to carrier density related to vertical electric field. Then linear  $\Delta I_{DS}$  modeling has included both contributions using a compact HCD model using (3a) with a balance between degradation and recovery (3b) where defect neutralization and field-assisted detrapping may occur.

$$\Delta IDLin_{on}(t)_{DC} = A \cdot t^n \cdot e^{\beta \cdot V d_{on}} \cdot (V g_{on} - V_{th})^p$$

(3a)

$$\Delta IDLIN_{HL}(t) = \Delta IDLIN_{LL}(t) + \Delta IDLIN_{rec-off}$$

(3b)

$$\Delta IDLIN_{rec-off} = \frac{K_f}{F^{\alpha}} \cdot Vg_{on}^{\gamma} \cdot e^{\delta \cdot Vd_{on}} \cdot \ln(1 + \frac{(t_{off} - t_0)\tau_e}{\tau_c}) \quad (3c)$$

$$\Delta IDLIN_{LL}(t) = \frac{K_f}{F^{\alpha}} \cdot \sum t_{on}^{n} \cdot e^{\beta \cdot V d_{on}} \cdot (V g_{on} - V_{th})^{p}$$

(3d)

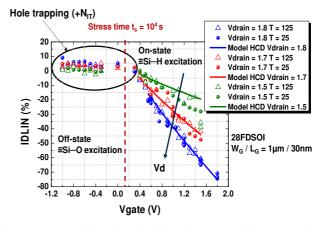

where  $\gamma$ ,  $\delta$  parameters in (3c) are related to the accelerating recovery efficiency as a function of the vertical and lateral electric field, respectively.  $\tau_c$  and  $\tau_e$  are the trapping/detrapping time constant,  $K_f$  is the frequency damage generation rate and  $t_0$  = 50 ns is a time characteristic for hole trapping [12]. Linear drain current degradation ( $\Delta Id_{Lin}$ ) was extracted between 25 °C and 125 °C in Fig.5, in FDSOI N-FET ( $L_G$  = 30nm) under DC HCD On-state (modeling shown in lines) on one hand, and under DC Off-state on the other hand for fixed  $V_{DS}$  = 1.5 to 1.8V and  $V_{GS}$  = -1 up to 1.8V. We note that  $\Delta Id_{Lin}$  during HCD "On-state" mode above  $V_{TH}$  continuously increases (negatively) with  $V_{GS}$

**Fig.5:**  $\Delta Id_{Lin}$  ( $V_{DS} = 50$  mV) in 28FDSOI N-channel  $L_G = 30$  nm extracted at  $t_s = 10^4$  s.  $V_{GS}$  dependence of  $\Delta Id_{Lin}$  under HCD in On and Off modes with  $V_{GS}$  stress between -1 and 1.8 V with the modeling (lines) in On mode, between room temperature (25 °C) and T = 125 °C.

and  $V_{DS}$  and it follows a time power law reported as to be due to interface defects generation ( $\Delta N_{IT}$ ) related to  $\equiv$ Si—H bonds breaking at Si/SiO<sub>2</sub> interface. Under HCD "Off-state" stress,  $\Delta Id_{Lin}$  measured under subthreshold regime is plotted (**Fig.5**) showing positive increase with time and following a logarithmic law dependence [30]. In this case the damage doesn't exceed 10%, which might be related to  $\equiv$ Si—O bonds excitation and breaking due to hole trapping.

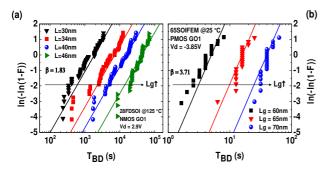

Thin gate oxide breakdown is characterized under DC Off-state TDDB stress with different gate-length  $L_G$  and as a function of drain voltage  $V_{DS}$  and temperature [31]. Even without inversion layer build-up, the carriers can be injected from drain edge by impact ionization and favored by gate-induced drain leakage (GIDL) and band-to-band tunneling (BTBT) combination, which may create defects at the interface and into the volume gate-oxide until triggering dielectric HBD. **Figs.6a,b** show that Off-state TDDB increases with  $L_G$  without changing markedly Weibull slope  $\beta$  value for both N- and P- FET FDSOI devices, where in this latter one have much higher  $\beta$  value.

**Fig.6:** TDDB time to failure distribution for different FET gate lengths at fixed drain voltage (a) 28FDSOI NFETs W =  $1\mu$ m for  $V_{DS}$  = 2.9V and (b) 65nm SOI PFETs  $W_G$  =  $10\mu$ m for  $V_{DS}$  = -3.85V. Breakdown occurs later for longer devices under same stressing voltages.

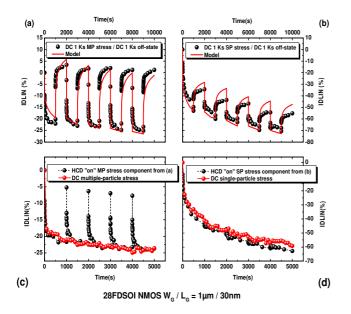

**Fig.7:** Alternating  $t_s$ =  $10^3s$  (DC) sequences performed in low frequency (LF) range compared to the corresponding modelling (red lines) in 28FDSOI NMOS  $L_G$  = 30nm. (a) HCD-MP at  $V_{DS}$ = 0.9V,  $V_{GS}$ = 2.2V alternated to Off mode  $V_{DS}$  =1.8V and  $V_{GS}$  = -1V. (b) HCD-SP at  $V_{DS}$  =1.9V,  $V_{GS}$  =1.4V alternated to Offmode  $V_{DS}$  = 1.8V and  $V_{GS}$  = -1V. Cumulative  $\Delta Id_{Lin}$  are extracted from HCD phases between alternating DC "On/Off" in (a) and (b) and compared to pure DC HCD only. Alternating (c) "MP/Off mode" to DC HCD MP and (d) "SP/Off mode" to DC HCD SP is shown with the corresponding stressing voltage condition

In order to evidence potential interaction between On mode and Off mode, alternated DC (Fig.7) and AC (Fig.8) stress sequences have been done. In this manner, HCD with high energy carriers are involved at  $V_{DS} = 1.9V$  and  $V_{GS} = 1.4V$  under field driven where single particle (SP) leads to classical HCD [17], [18]. Low energy carriers are involved at  $V_{DS} = 0.9V$  and  $V_{GS} = 2.2V$  under current driven phenomenon where multiple particle (MP) mechanism leads to Si-H bond breaking [19], [27], while Off-state stressing is involved at bias  $V_{DS} = 1.8$  and  $V_{GS} = -1V$ . We show the stressing alternance of DC MP to Off mode and from SP to Off mode in Figs.7a,b compared to the modeling (lines) giving relative good agreement with (3a)-(3d). We also compare the extracted HCD MP and SP phases in Figs. **7c,d.** It is shown that Off mode does not introduce aggravation in the successive HCD parts that remain cumulative and matches the DC results only.

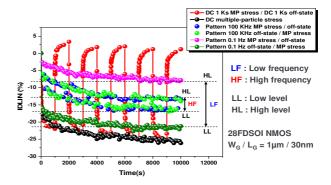

Low frequency (LF) with F= 0.1Hz and high frequency (HF) with F= 100KHz AC stressing have been compared in **Fig.8** to pure DC MP ( $10^4$ s) and to alternated phases using DC MP to Off-state measurements using  $10^3$  s quasi-static sequences [12]. AC pulse trains are composed of successive "On" and "Off" mode stress with two kinds of sequences, either ending with "On mode" stage or else ending by "Off mode" stage. We show that the magnitude of  $\Delta Id_{Lin}$  measured at LF depends on the signal configuration, because AC pulses ending with Off-state characterizes the reached level of the degradation named here high level (HL). This has been calculated quasi-statically with (3b) with respect to the low level (LL), considering a net compensation in  $\Delta Id_{Lin}$  due to hot-hole trapping using expression (3c).

**Fig.8:** Several AC (DC) sequences between 0.1 Hz and 100 kHz, alternating HCD multiple particle ( $V_{\rm GS}$  at high level) and Off-mode stressing (low level) and done in the reverse order, as a function of pulse duration and voltage level of the stressing pulses.

We show in **Fig.8** that when AC signals end with HCD in On-state, the generation of permanent defects become dominant inducing a larger effect on  $\Delta Id_{Lin}$  corresponding to LL dynamics with (3d). Moreover, a maximum of recovery occurs after alternating MP HCD (M3 mode) to "Off mode" with respect to SP HCD switched to Off-mode sequences. In the next subsection a straight method is presented to decouple stress and sensing temperature impact based on  $\Delta Id_{Lin}$  extraction.

#### B. Sensing effects in short channel LP MOSFETs

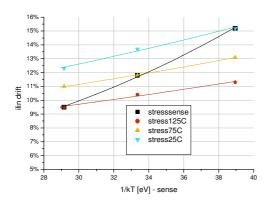

Another challenge in ageing device modeling is the effect of sensing temperature on the residual drift. As a general approach, MOS transistor parameter drift measured at various stress voltages is renormalized to a common junction temperature using an apparent activation energy ( $E_{App}$ ). It comes out that such approach can induce significant errors since the sensing temperature itself can represent up to 50% of the apparent measured  $E_{App}$  value, as previously explained in [10]. For the sake of illustration, the  $Id_{Lin}$  drift is reported in Fig. 9 versus the sensing temperature for N-channel MOSFETs with thick gate-oxide (GO2) obtained from LP 40 CMOS node.

**Fig.9:** Id<sub>Lin</sub> drift vs. sensing Temperature for N-channel thick gate-oxide (GO2) Input/output devices LP 40nm node stressed between 25°C and 125°C.

It has been shown that in general, HCI drift is higher at low stress temperature for N-FET and at high temperature for P-FET. At the same time,  $Id_{Lin}$  drift always increases with sensing temperature, while  $V_{Th}$  drift does not depend so much on sensing temperature for the same stressing type, due to the larger mobility variation with sensing temperature than  $V_{Th}$  [10].

# IV. CIRCUIT RELIABILITY FOR PRODUCT QUALIFICATION

With the increasing requirement of low power SOC design without compromising performance, and vice versa, the need to support Dynamic Voltage Frequency Scaling (DVFS) Technique at SOC is growing. DVFS aims to improve Power-Delay product by adjusting the supply voltage ( $V_{DD}$ ) and frequency ( $F_{AC}$ ). It results the necessity to develop an accurate and predictive impact modeling of reliability for any design of components, and thus a dedicated qualification flow.

# A. Digital and SRAM ilustrations

This section intends to illustrate some examples of reliability effect at digital and SRAM circuit level. The aim is to highlight standard approach of qualification with discussing the current challenges.

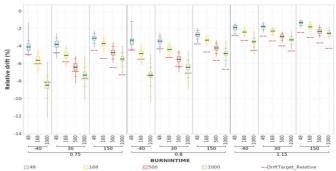

The intrinsic reliability of digital logic function is usually guaranteed through consideration of timing margin (either dedicated corner or global derating factor). At cell level, the adequation between model and measurement in aged state needs to be validated in any process, voltage, temperature (PVT) corners used in implementation. Illustration of this correlation is presented in Fig.10 for a logic cell drift at different  $V_{\rm DD}$ , temperature and ageing time. The challenge is to consider in the device model all the possible stress and relaxation configurations (especially relaxation with positive  $V_{\rm DS}$ ) but also after implementation, the sign-off scenario of the worst-case for hold and setup timing violations.

**Fig.10:** For a given logic cell, evolution of the measured drift (box plot) and ageing simulation for various supply voltage V<sub>DD</sub>, temperature and time.

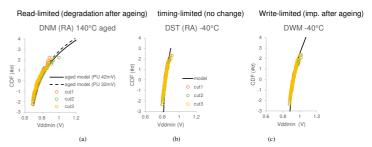

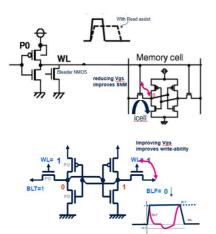

SRAM blocks represent nowadays a large portion of SOC applications. Applying DVFS means to reduce the supply voltage  $V_{\rm DD}$ , but this tends to increase the risk of single bit fail due to degraded stability and writability. The degradation in stability and writability is also dependent on other factors like global, local variations, especially in temperature and ageing. Hence, it is important to analyze the distribution of minimum operational voltage  $(V_{min})$  in SRAM and to determine the limitation of  $V_{min}$  in different stressing and sensing conditions. As shown in **Fig.10**, SRAM  $V_{min}$  can be limited by Dynamic Noise Margin (DNM) during read operation at hot (T= 140°C) or it can be limited due to Dynamic Write Margin (DWM) at cold (-40°C) or room temperature.

**Fig.11:** SRAM  $V_{min}$  distribution at hot can be predicted by the model, read limitation at hot (42mV degradation of pull-up after ageing) (a). With read assist, at cold, it can be self-timing limited (b) and write limited without assist (c).

The advantage of  $V_{\text{min}}$  distribution analysis can be multi-folded in case of a good correlation with silicon, where not only Spice modeling but also memory design & chip design can truly represent CAD behavior. As shown in **Fig.11** in solid lines, using the modulation of some key Spice parameters and design, the silicon  $V_{\text{min}}$  distribution can be represented even at CAD level. Using this approach, the CAD  $V_{\text{min}}$  distribution can be predicted

**Fig.12:** Schematics for the Read assist in memory design with WL lowering (top). Write assist with BL lowering (bottom).

for any mission profile, or it can be further explored to process changes, or design modifications like the usage of Read / Write Assist to improve  $V_{\text{min}}$  distribution. The usage of Read Assist is shown in Fig.12 by reducing the Word Line (WL) Voltage level to improve the SBFs related to DNM, also by using write assist (BL Lowering). The bit cell can thus reach good writability at low voltage. For read-limitation  $V_{\text{min}}$ , read assist can be used to compensate ageing degradation while write-limited  $V_{\text{min}}$  tend to be improved after ageing.

# B. Analog IP illustrations

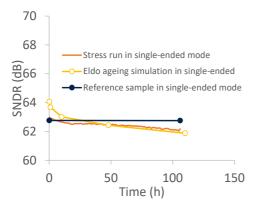

Finally, the last illustration deals with analog circuit. In the context of the examination of analog IP reliability, stressing results are presented in Analog to Digital Converter (ADC). A burn-in is performed during 100h with a dynamic pattern on several samples on three ADCs, two 10 bits 1MSP/s and one 12 bits 5MSP/s ADCs with similar manufacturing processes. Stresses were used by increasing the supply voltage by 40% and 60% and the temperature was raised to 125°C. The subsequent drift was compared to reference samples in order to exclude any influence of the measurement setup. The 1MSP/s devices do not

**Fig.13:** Evolution of SNDR during burn-in time, compared to simulation and to a reference part that remains un-stressed.

exhibit any drift to the stress condition whatsoever. Indeed, the stress was not sufficient to overcome the large design margins. However, the 5MSP/s ADC is showing a sensitivity on output dynamic parameters. Indeed, SNR is known to be sensitive to ageing [32]. A drift in single-ended mode was then observed in Fig.13 and can be explained by the simulations. A deeper analysis shows that comparator noise is degraded during ageing and can affect resulting SNR.

We emphasize that care must be taken to obtain a good correlation with fresh device, to accurately assess both simulations and measurements corresponding variation. Any disparity - sampling, number of harmonics, supply voltage, saturation margins - may easily bring some discrepancies. To help in bridging any offset between measurement and simulation, a noise model was implemented which highlighted a 20% drift in the comparator noise over a period of one month. Although its contribution was overshadowed by quantization noise, it is one of the factors inducing a shift in the ADC performance that will motivate comparator design improvement for the future.

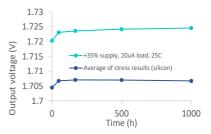

In a similar context, reliability of a regulator for power management is now investigated with an industrial qualification standard. With dedicated analog burning board, 1000h OLT was done in **Fig.14** at 125°C on Low Drop Out (LDO) circuit with static current load and supplied overvoltage. It results in a slight variation of output regulated voltage, which is accurately reproduced by simulation as well.

**Fig.14:** Evolution of output voltage in LDO circuit during 1000 h stress time, comparison is done between measurements versus simulations.

Interestingly, Operational Lifetime Test (OLT) conditions were chosen to induce the strongest possible stress effect that the models would allow, and then related to the drift caused by a differential pair where both transistors were degrading at different speeds, causing an offset, which was then amplified by the closed loop circuit. This explanation is consistent with simulated degradation at device level which matches the output variation, enabling the computation of the end of life for the circuit. As a conclusion, OLT conditions must be carefully chosen to represent a realistic stimulus, and to be confident with the fact that the observed degradation is related to the real stress condition and not triggered by abnormal stressing behaviors.

#### V. CONCLUSION

Last CMOS nodes fabricated with various drain architectures on LP Si-bulk and FDSOI HKMG, have been compared about

aging phenomena under main Wearout mechanisms, represented by BTI, HCD and HBD issues. Accelerated stressing have been presented from DC, alternating DC in MOSFETs, till AC degradation, to decouple the main degradation mechanisms. Cares have been taken to distinguish the sensing effect, neutralization and/or compensation effects for the damage, when these are involved depending on the variation of the stressing signal patterns, or temperature for sensing and stressing. Challenges both at device and circuit level modeling have been enlightened through some examples, that have been discussed using operational lifetime tests for IP qualification based on advanced CMOS nodes for digital and analog applications.

#### REFERENCES

- [1] T. Skotnicki, C. Fenouillet-Beranger, C. Gallon, F. Boeuf, S. Monfray, F. Payet, A. Pouydebasque, M. Szczap, A. Farcy, F. Arnaud, S. Clerc, M. Sellier, A. Cathignol, J.-P. Schoellkopf, E. Perea, R. Ferrant, H. Mingam, "Innovative Materials, Devices, and CMOS Technologies for Low-Power Mobile Multimedia", IEEE Trans. Elec. Dev., Vol. 55, N°1, pp. 96-130, 2008

- [2] G. Groeseneken, F. Crupi, A. Shickova, S. Thijs, D. Linten, B. Kaczer, N. Collaert, M. Jurczak, "Reliability Issues in MUGFET Nanodevices", Proceedings of Int. Reliab. Phys. Symp. (IRPS), pp. 52-60, 2008.

- [3] V. Huard, F. Cacho, L. Claramond, P. Alves, W. Dalkowski, D. Jacquet, S. Lecomte, M. Tan, B. Delemer, A. Kamoun, V. Fraisse, "Advances in industrial practices for optimal performance/reliability/power trade-off in commercial high-performance microprocessors for wireless applications", IEEE Int. Reliability Physics Symposium (IRPS), 3E.5.1 3E.5.1.7, 2013.

- [4] K. B. Sutaria, A. Mohanty, R. Wang, R. Huang, Y. Cao, "Accelerated Aging in Analog and Digital Circuits with Feedback", IEEE Trans. on Device and Materials Reliab., Vol.15, N°3, p. 384, 2015.

- [5] M. A. Alam, B. K. Mahajan , Y.-P. Chen , W. Ahn , H. Jiang, S. H. Shin, "A Device-to-System Perspective Regarding Self-Heating Enhanced Hot Carrier Degradation in Modern Field-Effect Transistors: A Topical Review", IEEE Trans. Electron Devices, Vol. 66, N°. 11, p. 4556, 2019.

- [6] C. Liu, Y. Sun, P. Ren, D. Gao, W. Luo, Z. Chen, Y. Xia, "New Challenges of Design for Reliability in Advanced Technology Node", invited paper, IEEE Proc. of Electron Devices Technology and Manufacturing Conf., 5A-1-5A-4, 2020.

- [7] A. Rahman, P. Bai, G. Curello, J. Hicks, C. –H. Jan, M. Jamil, J. Park, K. Phoa, M. S. Rahman, C. Tsai, B. Woolery, J.-Y. Yeh, "Reliability Studies of a 22nm SoC Platform Technology Featuring 3-D Tri-Gate, Optimized for Ultra Low Power, High Performance and High Density Application", IEEE Int. Reliability Physics Symposium (IRPS), PI.2.1 PI.2.6, 2015.

- [8] V. Huard, D. Angot, F. Cacho, "From BTI variability to product failure rate: A technology scaling perspective", IEEE Int. Reliability Physics Symposium (IRPS), 6B.3.1 – 6B.3.6, 2015.

- [9] M. Saliva, F. Cacho, V. Huard, X. Federspiel., D. Angot, A. Benhassain, A. Bravaix, L. Anghel, "Digital circuits reliability with in-situ monitors in 28nm fully depleted SOI", Design, Automation & Test in Europe Conf. & Exhibition (DATE), p. 441, 2015.

- [10]X. Federspiel; A. Camara; A. Michard; C. Diouf; F. Cacho, "HCI Temperature sense effect from 180nm to 28nm nodes", IEEE Int. Reliability Physics Symposium (IRPS), XT.1-1, XT1-5, 2021.

- [11] S. Mhira, V. Huard, A. Jain, F. Cacho, D. Meyer, S. Naudet, A. Bravaix, C. Parthasarathy, "Mission Profile Recorder: An Aging Monitor for Hard Events", IEEE Int. Reliability Physics Symposium (IRPS), 4C3-1 4C3-5, 2016.

- [12]T. Garba-Seybou, A. Bravaix, X. Federspiel, F. Cacho, "Modeling hot carrier damage interaction between on and off modes for 28 nm AC RF applications", Microelectronics Reliab., Vol. 126, p. 114342, 1-9, 2021.

- [13]S. Kupke, S. Knebel, J. Ocker, S. Slesazeck, R. Agaiby, M. Trentzsch, T. Mikolajick, "Experimental Proof of the Drain-Side Dielectric Breakdown of

- HKMG nMOSFETs Under Logic Circuit Operation", IEEE Electron Dev. Lett., Vol. 36, p. 430, 2015.

- [14]S. Li, A. Bravaix, E. Kussener, D. Ney, X. Federspiel, F. Cacho, "Hot-Carrier Degradation in P- and N- Channel EDMOS for Smart Power Application", Microelectronics Reliab., Vol. 114, p. 113811-6, 2020.

- [15] A. Bravaix, C. Guérin, V. Huard, D. Roy, J.-M. Roux, E. Vincent, "Hot-Carrier Acceleration Factors for Low Power Management in DC-AC stressed 40nm NMOS node at High Temperature", IEEE Int. Reliability Physics Symp. (IRPS) Proc., p. 531, 2009.

- [16] M. Arabi, X. Federspiel, F. Cacho, M. Rafik, A.-P. Nguyen, X. Garros, G. Ghibaudo, "New Insights on Device Level TDDB at GHz Speed in Advanced CMOS Nodes", IEEE Trans. on Devices and Materials Reliab., Vol. 19, N°2, p.255, 2019.

- [17] S.E. Rauch, "The Energy Driven Paradigm of NFET Hot Carrier Effects", Proc. of Int. Reliab. Phys. Symp. (IRPS), pp. 1-5, 2005.

- [18] La Rosa, S. E. Rauch, "Channel hot carrier effects in n-MOSFET devices of advanced submicron CMOS technologies", Microelec. Reliability, vol. 47, p. 552, 2007.

- [19] C. Guérin, V. Huard, A. Bravaix, "The Energy Driven Hot-Carrier Degradation Modes in NMOSFETs", IEEE Trans. on Device and Materials Reliability, Vol. 7, No. 2, p. 225, 2007.

- [20] G. Reichert, T. Ouisse, "Relationship between empirical and theoretical mobility models in silicon inversion layers", IEEE Trans. Electron Devices, Vol. 43, N°. 9, p. 1394, 1996.

- [21] C. Nguyen-Duc, S. Cristoloveanu, G. Ghibaudo, "Low-temperature mobility behaviour in submicron MOSFETs and related determination of channel length and series resistance", Solid-State Elec., Vol. 29, N°. 12, p. 1271, 1986.

- [22] A. Cros, S. Harrison, R. Cerutti, P. Coronel, G. Ghibaudo, H. Brut, "New extraction method for gate bias dependent series resistance in nanometric double gate transistors", IEEE Int. Conf. on Microelec. Test Structures (ICMTS), Vol. 18, p. 69, 2005.

- [23]D. Fleury; A. Cros; H. Brut; G. Ghibaudo,"New Y-function-based methodology for accurate extraction of electrical parameters on nano-scaled MOSFETs", IEEE Int. Conference on Microelec. Test Structures (ICMTS), p. 160, 2008.

- [24]G. Ghibaudo, "New method for the extraction of MOSFET parameters", Electron. Lett., Vol. 24,  $N^{\circ}$ . 9, p. 543, 1988.

- [25] E. Amat, T. Kauerauf, R. Degraeve, R. Rodríguez, M. Nafría, X. Aymerich, G. Groeseneken, "Gate voltage influence on the channel hot carrier degradation of High-k-based devices", IEEE Trans. on Devices and Materials Reliab., Vol. 11, N°1, p. 92, 2011.

- [26] S. Tyaginov, A. Makarov, A. Chasin, E. Burya, M. Vandemaele, M. Jeche A. Grill, A. De Keersgietera, D. Linten, B. Kaczer, "The impact of self-heating and its implications on hot-carrier degradation – A modeling study", Microelectronics Reliab., Vol. 122, p. 114156, 2021.

- [27] A. Bravaix, V. Huard, D. Goguenheim, E. Vincent, "Hot-Carrier to Cold-Carrier Device Lifetime Modeling with Temperature for Low power 40nm Si-Bulk NMOS and PMOS FETs", IEEE International Electron Device Meeting (IEDM) Proc., p. 622, 2011.

- [28] H. Jiang, S.H. Shin, X. Liu, X. Zhang, M. A. Alam, "Characterization of Self-heating Leads to Universal Scaling of HCI Degradation of Multi-Fin SOI FinFETs", IEEE Int. Reliability Physics Symposium (IRPS), 2A-3-1 -2A-3-7, 2016.

- [29] A. Chasin, J. Franco, E. Bury, R. Ritzenthaler, E. Litta, A. Spessot, N. Horiguchi, D. Linten, B. Kaczer, "Relevance of fin dimensions and high-pressure anneals on hot-carrier degradation", IEEE Int. Reliability Physics Symposium (IRPS), pp. 1 -6, 2020.

- [30] T. Garba-Seybou, X. Federspiel, A. Bravaix, F. Cacho, "Analysis of the interaction of HCD under "On" and "Off" state modes for 28nm FDSOI AC RF modelling", IEEE Int. Reliability Physics Symp. (IRPS), pp. 31 1-5, 2021.

- [31] T. Garba-Seybou, X. Federspiel, A. Bravaix, F. Cacho, "New Modelling Off-state TDDB for 130nm to 28nm CMOS nodes", IEEE Int. Reliability Physics Symp. (IRPS) Proc., 11A.3 1-7, 2022.

- [32] R. Lajmi, F. Cacho, O. David, J.P. Blanc, E. Rouat; S. Haendler, P. Benech; E. Lauga Larroze, "Reliability assessment of 4GSP/s interleaved SAR ADC", IEEE Int. Reliability Physics Symposium (IRPS), P-CR-5.1, 2018.