## Validation of IC Conducted Emission and Immunity Models Including Aging and Thermal Stress

Qazi Mashaal Khan, Mohsen Koohestani, Jean-Luc Levant, Mohamed Ramdani, Richard Perdriau

## ▶ To cite this version:

Qazi Mashaal Khan, Mohsen Koohestani, Jean-Luc Levant, Mohamed Ramdani, Richard Perdriau. Validation of IC Conducted Emission and Immunity Models Including Aging and Thermal Stress. IEEE Transactions on Electromagnetic Compatibility, 2023, pp.1-14. 10.1109/TEMC.2023.3253385. hal-04123013

HAL Id: hal-04123013

https://hal.science/hal-04123013

Submitted on 12 Jun 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Validation of IC Conducted Emission and Immunity Models Including Aging and Thermal Stress

Qazi Mashaal Khan<sup>©</sup>, *Graduate Student Member, IEEE*, Mohsen Koohestani<sup>©</sup>, *Senior Member, IEEE*, Jean-Luc Levant, Mohamed Ramdani<sup>©</sup>, *Senior Member, IEEE*, and Richard Perdriau<sup>©</sup>, *Senior Member, IEEE*

Abstract—Environmental factors, such as aging and thermal stress, can seriously impact the electromagnetic compatibility behavior of an integrated circuit (IC). The standardized IC emission  $model\ for\ conducted\ emission\ (ICEM-CE)\ and\ IC\ immunity\ model$ for conducted immunity (ICIM-CI) can be used in industry to predict electromagnetic behavior at the IC and the printed circuit board level. However, these do not take into account the effect of aging and extreme temperature variations. In this article, a custom IC designed in silicon-on-insulator technology, containing several independent analog blocks, is used to characterize the influence of aging and temperature on conducted emission and immunity through measurements and transistor-level simulations. The highly accelerated temperature and humidity stress test (HAST) was performed to evaluate aging and its influence on IC parameters. The results show that the passive distribution network is only influenced by thermal stress and not HAST aging. The latter mainly affects the active elements in the IC and reduces the conducted emission and immunity levels through intrinsic permanent degradation mechanisms. Furthermore, thermal stress mainly causes drifts in the transistor characteristics (such as threshold voltage and effective mobility), which affect the conducted emission and immunity levels and resulting in soft failures. All drifts/tolerances collected from measurements and simulations are characterized in a way that makes it possible to include them in potential future versions of the ICEM-CE and ICIM-CI standards.

Index Terms—Highly accelerated temperature and humidity stress test (HAST) aging, integrated circuit (IC), integrated circuit emission model for conducted emission (ICEM-CE), integrated circuit immunity model for conducted immunity (ICIM-CI), thermal stress.

Manuscript received 25 November 2022; revised 19 January 2023 and 22 February 2023; accepted 3 March 2023. This work was supported by the European Union's Horizon 2020 research and innovation program under the Marie Sklodowska-Curie Grant 812790 (MSCA-ETN PETER). (Corresponding author: Qazi Mashaal Khan.)

Qazi Mashaal Khan was with the Department of Electrical and Electronic Engineering, ESEO School of Engineering, 49107 Angers, France, and also with the Department of Electronics Engineering, Institut National des Sciences Appliquées, 35708 Rennes, France. He is now with the Microwave Electronics Laboratory, Department of Microtechnology and Nanoscience, Chalmers University of Technology, 412 96 Gothenburg, Sweden (e-mail: qazimashaal.khan@eseo.fr).

Mohsen Koohestani, Mohamed Ramdani, and Richard Perdriau are with the Department of Electrical and Electronic Engineering, ESEO School of Engineering, 49107 Angers, France, and also with the Institute of Electronics and Telecommunications of Rennes, University of Rennes 1, 35042 Rennes, France (e-mail: mohsen.koohestani@eseo.fr; mohamed.ramdani@eseo.fr; richard.perdriau@eseo.fr).

Jean-Luc Levant is with the Microchip, 44300 Nantes, France (e-mail: jlucle-vant@gmail.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TEMC.2023.3253385.

Digital Object Identifier 10.1109/TEMC.2023.3253385

## I. INTRODUCTION

NTEGRATED circuits (ICs) are essential components in nearly every modern electronic system. A vital factor in the design process of ICs is estimating if their functionality and electromagnetic compatibility (EMC) characteristics can be guaranteed over their entire lifetime [1]. In that context, both electromagnetic (EM) emission and immunity of ICs are critical for reducing interference risks at the system level, where several mitigation techniques to suppress emission [2], [3], [4] and improve immunity [5], [6] of printed circuit boards (PCBs) are reported in the literature. Furthermore, it is necessary to analyze and predict the EMC of ICs in harsh environments (e.g., extreme temperatures, humidity, and electrical overstress) before the manufacturing stage [7].

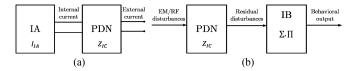

The International Electrotechnical Commission (IEC) has proposed several models to assess the EMC performances of ICs, such as the IC emission model for conducted emission (ICEM-CE) and the IC immunity model for conducted immunity (ICIM-CI), which are published in IEC62433-2 [8] and IEC62433-4 [9], respectively. Those models can be generated either through a black box or a white box approach. The former does not require the knowledge of the internal structure of the IC, while the latter approach provides the models in a simulatable form [10]. As shown in Fig. 1(a), the ICEM-CE model consists of a passive block called the passive distribution network (PDN) and an active block known as the internal activity (IA). The former describes the power supply network of an IC and shows the significant coupling paths from the noise source to the external pins of the IC [11], whereas the IA describes the activity of the internal block of the IC as a current source.

As observed in Fig. 1(b), the PDN of the ICIM-CI model is identical to that of the ICEM-CE and can be modeled using lumped passive elements. In addition, the immunity model also comprises the immunity behavior (IB) block, which is usually characterized as a lookup table that can be coupled to a comparator to output a pass/fail criterion based on the injected power [12]. The main limitations of these models are that they do not include the relevance of aging and thermal stress that can cause a drift in the EM conducted emission and susceptibility levels.

Owing to natural aging, ICs can be affected by intrinsic failure mechanisms, such as gate oxide defect, electromigration, hot carrier injection (HCI), and negative bias temperature instability (NBTI) [13], [14]. The latter two are the most prevalent permanent degradation effects and can be analyzed by accelerated life

Fig. 1. Modeling framework of (a) ICEM-CE and (b) ICIM-CI.

tests [15]. Furthermore, temperature variations can temporarily influence MOSFET parameters such as threshold voltage  $(V_{\rm th})$  levels, effective mobility  $(\mu_{\rm eff})$ , transconductance, and saturation currents [16]. These can trigger soft failures and can have significant impact on the stability parameters (leakage current, noise margin, jitter, operating frequency, etc.) of the IC [17].

In the literature, researchers have developed conducted emission models using de-embedding measurement techniques [18] and simulation tools [19] for microcontrollers and phase-locked loops (PLLs). Few researchers have also introduced an alternative approach to model the IA block for oscillators [20]. In addition, some works have been carried out to develop ICEM models up to 3 GHz, and the impact of high temperature on the emission levels has been analyzed [21], [22]. The effect of aging on the conducted emission of switches was studied in [23], and reliability models for field-programmable gate arrays (FPGAs) were developed in [24] and [25] to predict failures over their entire life cycle.

As far as immunity is concerned, some researchers developed multiport models to extract the conducted immunity profiles of analog circuits [26], [27]. The ICIM-CI model has also been extended to include the effect of transient EM disturbances [28]. Moreover, conducted immunity models were proposed to predict the long-term immunity of PLLs using accelerated life tests [29]. A recent study proposed an EM thermal model to characterize the conducted immunity of an input/output (I/O) element for FPGAs [30].

To the best of the authors' knowledge, the influence of both aging and thermal stress on EMC models applicable on silicon-on-insulator (SOI) ICs has not been investigated so far. Therefore, in the current study, the ICIM-CI and ICEM-CE models were developed for independent analog circuits that were integrated into a custom-designed IC. Through measurements and transistor-level simulations, the effect of extreme temperature deviations and accelerated aging was included into either the passive or active blocks of the proposed models.

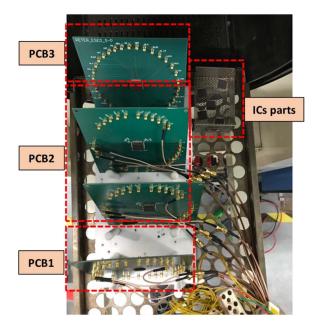

The rest of this article is organized as follows. Section II describes the custom-designed IC and PCB variants as well as the independent analog blocks used for conducted immunity and emission testing. This section also outlines the measurement setups for accelerated life tests and immunity/emission measurements under thermal stress. Sections III and IV present the experimental and simulation/modeling results for conducted emission and immunity, respectively. Finally, Section V concludes this article.

#### II. MATERIALS AND METHODS

This section introduces the IC and PCB variants designed for the purpose of this study. Then, the circuits designed for conducted emission and immunity are described. It is followed by the highly accelerated life testing performed to represent the aging of the custom IC. Furthermore, the experimental test setup to characterize the IC conducted emission and immunity is also described.

#### A. Design Description of Custom IC and PCB Variants

For the purpose of this study, a 1.52 mm  $\times$  1.52 mm chip (PETER ESEO) [31], including various analog structures, was fabricated in SOI CMOS 180-nm 5-V technology. The design and layout of all the integrated blocks were performed using Cadence Virtuoso. The core is surrounded by a core-limited pad ring that is powered by the global power supply  $(V_{\rm DDO})$ . It consists of 52 pads with identical N-MOS-based electrostatic discharge (ESD) protection devices connected to both  $V_{\rm DDO}$  and the global ground  $(G_{NDO})$ . All the structures have an isolated power supply pad  $(V_{\rm DDI})$  and a separate ground  $(G_{\rm NDI})$ , due to the use of SOI technology. The output of each circuit is connected to an analog pad and an ESD protection circuit that will clamp the generated signals that are not within the 0–5.5 V range. The internal ESD circuits of the  $V_{\rm DDI}/G_{\rm NDI}$  and analog I/O pads include N-MOS transistors with gate-to-source resistors to reduce the overall gate leakage current.

The die samples were packaged in a 64-pin ceramic quad flat package. All the power supply and ground pads were bonded to the package pins with spacing in between them to minimize the effect of mutual inductive coupling. This makes it possible to not only inject more power into the supply pads but also to monitor high-frequency signals [32].

To test the conducted emission and immunity of the IC, a  $13~\rm cm \times 13~\rm cm$  four-layer FR4 PCB was designed according to IEC 61967-4 [33] and IEC 62132-4 [34] using Altium Designer. The PCBs were not overloaded with nonlinear components to restrict uncontrolled radio frequency (RF)/EM behavior [35]. All the isolated grounds of the IC were connected to the global ground. Specifically, for the circuits tested for immunity, a 470- $\Omega$  resistor was added in series to its output pin in order to limit high-voltage signals from being reinjected into the IC or the oscilloscope. Only for the conducted emission circuit, the  $G_{\rm NDI}$  pin was connected to 49- and 1- $\Omega$  resistors in compliance with the 1- $\Omega$  method of IEC 61967-4 [33].

In addition, a second 13 cm  $\times$  13 cm four-layer FR4 PCB variant was designed to measure the (scattering) S-parameters of the IC pins. The IC was mounted at the center of the PCB with its pins connected to several microminiature coaxial (MMCX) through-hole female connectors with a characteristic impedance of 50  $\Omega$  covering a frequency range from dc to 4 GHz. Instead of the standard SMA connectors, MMCX connectors were used due to their compact size, which makes it practicable to test all IC pins on the same PCB. The injection traces were placed radially in a circle, with a 47-mm individual primary length, to keep the distance between each MMCX and IC pin equal. More details of the designed PCB can be found in [32].

For accurate S-parameter measurements, it is essential to design a calibration board. This makes it possible to extract the impedance profile of the IC pin without the effect of the

PCB traces. A  $10~\rm cm \times 10~\rm cm$  four-layer FR4 calibration PCB was designed and panelized with the same PCB substrate as the S-parameter board. The calibration technique adopted was the short-open-load-thru (SOLT), generally providing an accuracy of up to 4 GHz [36]. The primary length of the short, open, and load traces was set to 47 mm, while the thru trace was fixed to 94 mm. As far as the load is concerned, a high-precision 50- $\Omega$  (0402) resistor was used for termination.

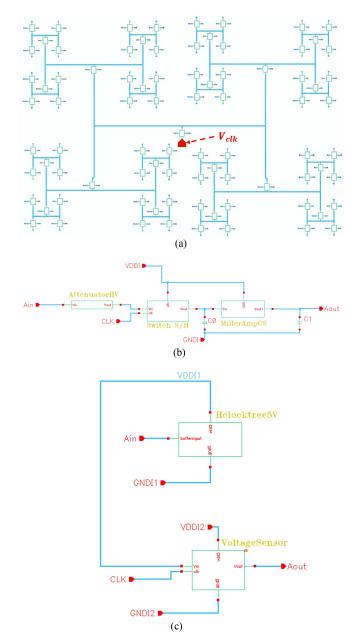

## B. Conducted Emission Circuit Design

To investigate conducted EM emission at IC level, an H-clock tree noise circuit was included in the PETER\_ESEO die. It consists of 85 analog noninverting buffers with identical aspect ratios. It has a total of four stages and 64 output branches, which were left floating. The schematic is displayed in Fig. 2(a). One branch of the H-clock tree was connected to the input analog pad, and the clock signal ( $V_{\rm clk}$ ) was injected externally through it. The routing of the circuit was kept highly symmetrical in order to maintain equal propagation delays in each branch of each level. Noninverting buffers were used instead of simple inverters to provide better sensitivity and ensure that all routed signals remain in-phase, as well as to further avoid noise cancellation [37].

When a clock signal is provided to the input of the *H*-clock tree, it generates high-frequency conducted EM disturbances, specifically in its power supply and ground rails. An on-chip sample and hold (*S&H*) voltage sensor based on deep downsampling was also included in the IC to characterize these coupled EM disturbances by transposing them to much lower frequencies [38]. The voltage sensor is made up of the following blocks (see Fig. 2(b), from input to output):

- 1) a resistive divider including compensation capacitors and an attenuation ratio fixed to 1/2;

- a sampling cell containing a storage capacitor and a CMOS pass gate driven by an external clock, with a 1-GHz bandwidth;

- a unity-gain differential Miller amplifier including a current source and a start-up circuit with a 100-MHz bandwidth.

The voltage sensor principle is based on intentional aliasing, operating much below the Nyquist criteria, in order to transpose high-frequency signals down to a few megahertz. The influence of parasitic elements, such as the pad capacitance, package, and bonding, can be excluded at such low frequencies [39]. Hence, the output signal amplitude is a linear function of the input signal amplitude. The Miller amplifier aspect ratios were optimized according to Jespers and Murmann sizing methodology provided in [40] using predetermined SPICE generated lookup tables and explicit MATLAB functions [41].

As illustrated in Fig. 2(c), the supply rail  $V_{\rm DDII}$  of the H-clock tree noise circuit is connected to the analog input of the S&H voltage sensor. When a square signal with a constant frequency is injected into the  $A_{\rm in}$  of the H-clock tree, the switching activity of the buffers produces conducted noise, which propagates to  $V_{\rm DDII}$  or  $G_{\rm NDII}$ . Conducted emission measurements were carried out using the 1- $\Omega$  probe [33] placed at  $G_{\rm NDII}$  pin of the H-clock

Fig. 2. Conducted emission schematics. (a) H-clock tree. (b) S&H voltage sensor. (c) Combined emission circuit.

tree. Furthermore, the S&H output peak voltage is directly proportional to the conducted emission generated in  $V_{\rm DDI1}$ .  $V_{\rm DDI2}$  and  $G_{\rm NDI2}$  of the voltage sensor were entirely isolated from the conducted noise and was verified to have no impact on the emission analysis.

## C. Conducted Immunity Circuit Design

To analyze the conducted EM immunity, two independent analog blocks integrated into the IC were selected. Those are a three-stage current-starved voltage-controlled oscillator (CSVCO) and an analog set/reset (*S-R*) latch. The former is an integral part of mixed-signal ICs, such as PLLs, and the latter is utilized in sequential memory circuits. The power supply of

Fig. 3. Conducted immunity test circuits. (a) Three-stage CSVCO. (b) Analog S-R latch.

the mentioned structures is prone to conducted electromagnetic interference (EMI), which affects their performance characteristics [42]. Both circuits have separated  $V_{\rm DDI}$  and  $G_{\rm NDI}$  rails to avoid any interference or coupling during immunity testing.

As displayed in Fig. 3(a), the CSVCO topology includes externally biased MOSFETs that control the current provided to its inverter stage. The biasing supply  $(V_C)$  is connected to those MOSFETs to minimize power consumption and tune the frequency range [43]. For this study,  $V_C$  is biased to 1.8 V and the three-stage CSVCO generates a stable sinusoidal signal operating at 703 MHz.

A three-stage digital frequency divider (FD) circuit is added at the output stage of the oscillator to lower the fundamental frequency of the generated signal. The FD is powered by  $V_{\rm DDO}$ , which is isolated from the oscillator individual power supply and allows monitoring the frequency at the analog output pad without filtering effects caused by the parasitic pad capacitance. The maximum operating clock frequency of the FD was equal to 900 MHz.

Latches are single bit storage elements used in computing and data storage. The S-R latch is an asynchronous bistable multivibrator, which works independently of the control signals and relies only on the S and R inputs [44]. The latch comprises two NOR gates with a cross-feedback loop from the outputs Q

Fig. 4. Aging of ICs in the HAST chamber.

and QB [see Fig. 3(b)]. All the used MOSFETs have identical aspect ratios. An analog version of the *S-R* latch was designed to be able to utilize an isolated power supply and ground. To test the conducted immunity of the latch, EMI was injected into the power supply, whereas both the outputs were monitored to check if the latch enters into a metastable state.

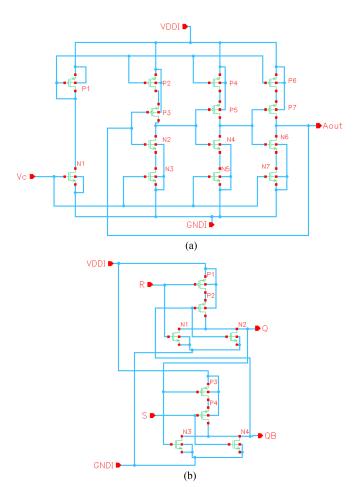

## D. Aging of ICs

To investigate the impact of aging on the emission and IB of ICs, accelerated life tests are usually performed in industry. High-level stress conditions, such as extreme high temperature or voltage, are applied for a short period of time to accelerate the damage rate for relevant wear-out failure mechanisms, such as NBTI and HCI [45]. The most frequently used accelerated tests to induce such degradation mechanisms are high- and low-temperature operating life tests [46] and temperature humidity bias (THB) test [47]. The latter is a method of electronic reliability testing using temperature and relative humidity (RH) as the environmental parameters. The test is carried out at 85 °C and 85% RH continuously for 1000 h to predict the operational lifetime of the device up to 25 years.

The highly accelerated temperature and humidity stress test (HAST) is a more accelerated version of the THB test (causing equivalent failure modes) and is performed at 130 °C and 85% RH continuously for only 96 h [48]. The purpose of the HAST is to evaluate the humidity resilience of a component or an encapsulated IC by increasing the water vapor pressure to an extremely high level above the partial water vapor pressure inside the IC. Hence, this test causes a rise in component contact resistance due to moisture corrosion and insulation deterioration.

The HAST was selected herein as the accelerated life test to evaluate the effect of aging on the conducted emission and immunity of the PETER\_ESEO IC. As illustrated in Fig. 4, the immunity/emission and S-parameter PCB variants along

Fig. 5. DPI experimental test setup

with several packaged ICs were placed in an HAST chamber (ESPEC EHS-412M) at a constant 130 °C temperature and 85% RH for 96 h. For the entire duration of the test, the global power supply and the isolated supplies of the *H*-clock tree, *S&H* voltage sensor, *S-R* latch, and the CSVCO circuits in the IC were biased to 5 V using external dc power supplies through high-temperature cables. At the end of the test, all PCBs and ICs were still operational with no visible damages. The only noticed observable effect was that the PCB traces connected to the biased IC pins had different colors changing from green to black due to corrosion.

## E. Conducted Immunity and Emission Measurement Test Setup

The direct power injection (DPI) method is commonly used to characterize the conducted immunity of the IC from 150- to 1-GHz frequency spectrum [34]. The IB of ICs is established based on the minimum transmitted power level that is required at a specific frequency within a given RF range to cause IC failure [49]. The DPI measurement setup is depicted in Fig. 5. The test bench includes an RF generator (Agilent N5183A), a series power meter (Agilent E4419B), a bidirectional coupler, a RF power amplifier (Prana AP32DT120), a multichannel dc power supply (N6700B), a bias tee (ZFBT-6GW+), an oscilloscope (Keysight DSOS204A), an arbitrary waveform generator (Agilent N9010A), extreme temperature cables (Amphenol-RF 095-902-466-004), and a SATIMO thermal oven.

The analog *S-R* latch and the CSVCO were tested using this setup in order to analyze their conducted IB. The RF generator produces the continuous-wave EM disturbance that flows through the bidirectional coupler and is superimposed over 5 V

Fig. 6. Simulated internal transient current (IA) generated by the H-clock tree and monitored at  $V_{\rm DDI}$ .

provided by one of the dc power supply channels via a bias tee into the  $V_{\rm DDI}$  pin of the tested circuit. The remaining channels of the dc supply were connected to the global  $V_{\rm DDO}$  and  $V_{C}$ of the CSVCO at 5 and 1.8 V, respectively. The power meter provided the injected power from the measured forward and reflected power magnitudes. The amplifier was used to stabilize the injected signals at higher power levels (above 20 dBm). The device under test (DUT) was placed inside the oven, and the output pin of the tested circuit was connected to the oscilloscope  $(1 \text{ M}\Omega)$  via high-temperature cables. The LabView interface was used to control the entire test setup and apply a failure criterion on the output signal using mask testing. The latter involved fixing a mask up to a tolerance limit on the output signal in both directions (lower and higher). Then, the statistical failure rate, i.e., the output signal leaving the area of the oscilloscope mask, was averaged over a specific time slot.

An ac decoupling capacitor was not used and routed on the tested DPI PCB variants. This was specifically done to avoid any additional effects caused by external components when subjected to thermal stress, seeing that no external components were required to ensure the proper operation of the integrated blocks. In the DPI method, RF power was injected into the IC power supply pins using external bias tees.

The abovementioned measurement setup was also utilized for conducted emission testing. The  $V_{\rm DDI}$  rails of the H-clock tree and voltage sensor were biased to 5 V. One of the channels of the arbitrary wave generator was utilized to inject a square wave into the analog input pin of the H-clock tree and the second channel generated the clock signal for the S&H voltage sensor. The current activity of  $G_{\rm NDI}$  of the noise circuit and the output peak voltage of the S&H sensor were monitored through the oscilloscope channels at 50  $\Omega$  and 1  $M\Omega$ , respectively.

## III. RESULTS AND DISCUSSION OF CONDUCTED EMISSION

This section deals with the conducted emission analysis of the *H*-clock tree and the extraction of the ICEM-CE model, comprising the PDN and IA blocks. Furthermore, the effect of aging and thermal stress is analyzed in measurements and included in the emission model. The H-clock tree was subjected to a square wave input of 50-MHz frequency, 50% duty cycle, 10-ns rise/fall times, and 5-V amplitude. The clock of the S&H voltage sensor was set to 999-kHz frequency, 3% pulsewidth, and 5-V amplitude. The voltage sensor with these clock characteristics transformed the 50-MHz switching activity emitting from the H-clock tree to a 50-kHz output voltage signal. To characterize the effect of aging, all the measurements of the fresh and aged DUTs were carried out at ambient temperature (25 °C). Conversely, to analyze the effect of thermal stress on the conducted emission of the noise circuit, measurements were performed on fresh DUTs at ambient and extreme temperatures (i.e., -40 and 120 °C). The respective minimum and maximum temperatures were chosen since they conform to the temperature limits of all the components soldered on the tested PCBs.

## A. Extraction of the ICEM-CE Model

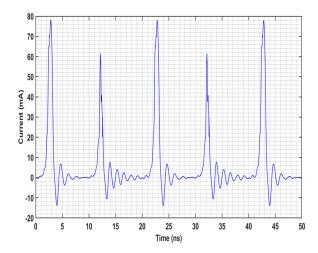

For the ICEM-CE modeling of a commercial IC, where the latter is considered a black box, an image of the internal current is extracted using measurement tools and impedance profiles from the external current. However, since the IC under test is custom designed, the internal current was extracted using Cadence Virtuoso (simulation-based transistor-level approach). A hierarchical parasitic extraction was performed for the IC to better approximate the realistic behavior of the dynamic current. The switching of the analog buffers in the H-clock tree generates a conducted noise emitted through its  $V_{\rm DDI}$  or  $G_{\rm NDI}$  rail. Owing to a stable input frequency of 50 MHz, the IA dynamic current emission waveform consists of periodic spikes having the same fundamental frequency. The internal current profile of the Hclock tree is shown in Fig. 6. The IA time-domain characteristics exhibit a 1-ns rise time  $(t_r)$ , a 20-ns period, a 2.5-ns pulsewidth, and an overall peak-to-peak current of 94.5 mA. Each period has two consecutive current spikes with an amplitude of 78.4 and 61.3 mA. The extracted internal current was then fed as a netlist to the independent current source to model the IA block of the ICEM-CE model.

The electrical behavior of the PDN is given by its complex impedance and can be modeled using lumped passive R, L, and C elements. To determine which passive elements are required to model the PDN up to a certain frequency,  $t_r$  of the internal current is a critical parameter. The bandwidth capable of dealing with this  $t_r$  can be determined using [18]

$$F_{\text{max}} = \frac{0.35}{t_r}.\tag{1}$$

Harmonics above  $F_{\rm max}$  are considered low enough not to generate considerable emission levels. Hence, the frequency limitation of the PDN is equal to 350 MHz.

A vector network analyzer (VNA) was used to measure the one-port S-parameters ( $S_{11}$ ) of the  $V_{\rm DDI}$  pin of the H-clock tree. Furthermore, a calibration board, adopting the SOLT method, was utilized to accurately measure the correct  $S_{11}$  profile between 10 MHz and 3 GHz. The impedance parameters ( $Z_{11}$ ) results were then extracted from  $S_{11}$ . The impedance profile

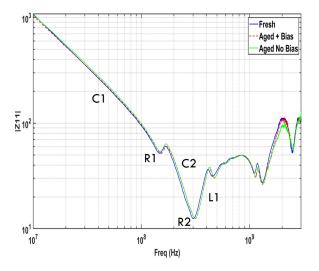

Fig. 7. Measured impedance profile of  $V_{DDI}$  of H-clock tree with aging.

Fig. 8. ICEM-CE simulation setup.

of the H-clock tree power supply network is shown in Fig. 7. The frequency response of the impedance up to 350 MHz is divided into several parts. Below 120 MHz, the impedance is capacitive (C1). The impedance becomes resistive at 150 MHz (R1) and 315 MHz (R2). The latter has a lower value and is the actual impedance at the resonant frequency, where the phase crosses zero. Between 150 and 300 MHz, a steeper capacitive (C2) impedance effect is observed. The reason for the parasitic resonance is due to the  $V_{\rm DDI}$  rail of the H-clock tree connected inside the IC to the input of the voltage sensor. The first stage of the sensor includes an attenuator with compensation capacitors, which causes the parasitic resonances noticed in the impedance profile. From 320 until 400 MHz, the impedance becomes inductive (L1) and can be computed at a given frequency within this range.

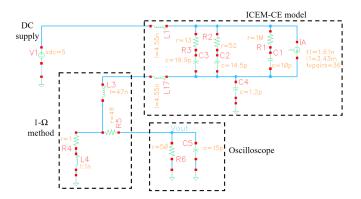

The ICEM-CE simulation setup is depicted in Fig. 8. It includes an independent current source, which represents the IA block of the ICEM model. The block capacitance (C1) was measured through the VNA when the  $V_{\rm DDI}$  rail of the H-clock tree was biased with 5 V. The difference in the capacitance from the unbiased version was found to be 10 pF. The first-order R, L, and C parameters (R2, C2, R3, C3, L1, and L2) were extracted from the  $Z_{11}$  profile, and they make up the PDN of the ICEM

Fig. 9. Comparison of the external current extracted through the ICEM simulation setup and 1- $\Omega$  measurement.

model. Furthermore, to have a better correlation between the conducted emission measurements and the model, the die to ground capacitance (C4) of 1.2 pF was included in the latter. The ICEM-CE simulation setup also includes a 5-V dc source and a  $1-\Omega$  resistor (R4) in series with its 1-nH parasitic inductance (L4) connected to the ground. Since the PCB trace has a length of 47 mm, it can generate a 47-nH (1 nH/mm) parasitic inductance (L3), which was added in series to the  $49-\Omega$  resistor (R5). Finally, the oscilloscope was modeled by a  $50-\Omega$  resistor (R6) and its 15-pF parasitic capacitance (C5), which affects the peak of the output signal in measurements.

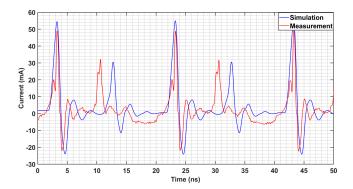

The external current activity extracted from the ICEM-CE simulation setup and through measurement using the 1- $\Omega$ method are illustrated in Fig. 9. A significant correlation between the extracted and measured current was noticed. The maximum peak-to-peak current of the former was 2.6% higher than the latter. However, the measured current included some minor parasitic inductance effects noticed at the consecutive spikes, which could be due to measurement uncertainty. Interestingly, the peak-to-peak internal current (see Fig. 6) was only 20.3% (16 mA) higher than the measured external peak-to-peak current (see Fig. 9). In comparative literature, the ICEM-CE model's internal current (IA) is considerably higher (120% or above [10], [18], [19], [20], [24]) than the measured external current extracted through the 1- $\Omega$  method. The filtering effect of the PDN is responsible for such lower peak values of the external current. Hence, for our custom-designed IC, the PDN has a lower filtering effect (20.3%) on the internal switching current.

## B. Influence of Aging on Conducted Emission

As mentioned in Section II-D, HAST testing was performed on the DUT (biased and unbiased) to evaluate the effect of aging on the conducted emissions generated by the H-clock tree. All the S-parameter and conducted emission measurements were carried out at ambient temperature on fresh and aged ICs to find out if the PDN or/and the IA blocks of the ICEM model are impacted by aging. Results shown in Fig. 7 demonstrate that HAST aging in both biased and unbiased ICs causes negligible variation in the  $Z_{11}$  profile over the entire frequency range. There exists a minor variation in  $Z_{11}$  for frequencies above 1 GHz, but this can be discarded due to measurement uncertainty. These

TABLE I Variation in Conducted Emissions With Aging (HAST)

| Sample | External<br>peak-to-peak<br>current | Internal<br>peak-to-peak<br>current | S&H sensor<br>peak-to-peak<br>voltage |

|--------|-------------------------------------|-------------------------------------|---------------------------------------|

| Fresh  | 78.54 mA                            | 94.50 mA                            | 1.46 V                                |

| Aged 1 | 70.95 mA                            | 85.35 mA                            | 1.39 V                                |

| Aged 2 | 71.81 mA                            | 86.39 mA                            | 1.40 V                                |

| Aged 3 | 72.32 mA                            | 87.01 mA                            | 1.42 V                                |

| Aged 4 | 72.03 mA                            | 86.66 mA                            | 1.41 V                                |

The italic values are extracted by extrapolation from measurements.

results demonstrate that aging due to HAST has no considerable impact on the PDN of the ICEM-CE model.

Contrarily, the conducted emission measurement results using the 1- $\Omega$  method revealed the induced effect by aging due to HAST on the external maximum peak-to-peak current levels. For the duration (96 h) of the HAST aging test, the power supply of some circuits was connected/biased to a 5-V power supply (Aged 1, Aged 2), while some ICs were left unconnected/unbiased (Aged 3, Aged 4). This was done to figure out if voltage biasing while aging has an impact on the conducted emission levels. Several ICs were tested for the sake of repeatability.

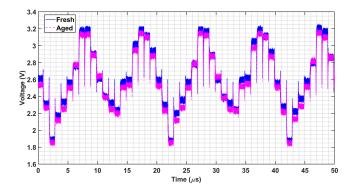

The time-domain characteristics of the fresh and aged samples were the same but with reduced peak current levels for the aged ones (see Table I). The average external peak-to-peak current of all the aged samples (71.52 mA) was 9.8% lower than the fresh version (78.54 mA). Since aging had no impact on the PDN, the only possible explanation for the reduced external conducted emission levels is due to the decreased amplitude of the internal current. Aging is due to the HAST triggered degradation mechanism NBTI, impacting the switching activity of the buffers in the H-clock tree and, hence, impacting the internal current emission levels. Since HAST aging was performed at elevated temperatures, HCI did not occur since it degrades MOSFETs characteristics at minimum temperatures. As indicated in Table I, the peak-to-peak internal current values of the aged samples were extrapolated from measurements. Voltage biasing had no impact on the reduced current emission levels after aging.

The S&H voltage sensor was used in random acquisition mode and intentionally undersampled the 50-MHz current switching activity of the H-clock tree down to 50 kHz. Although it was not possible to reconstruct the shape of the input signal in random acquisition mode, the histogram-type output voltage signal could indicate RF distortions in the conducted emission signal. The output voltage waveform of the fresh and aged sensors is shown in Fig. 10. No such distortions were observed in the output waveform. More importantly, the average output peak-to-peak voltage of the aged samples (1.40 V) was 60 mV lower than the fresh samples (1.46 V) (see Table I).

To validate that aging only affected the internal switching activity of the H-clock tree, a separate/identical S&H voltage sensor (integrated into the IC) was tested after aging. No considerable variation in amplitude or dc offset was observed in the output signal when subjected to a 50-MHz input sine wave. This verified that the reduction in peak output voltage amplitude

Fig. 10. Effect of aging on the clocked output voltage of the sensor.

was due to the H-clock tree. It was checked that the spectral content of the external current did not vary with aging. Since the PDN does not change with aging either, a constant coefficient of proportionality can be established between the external and the internal (IA) peak values whatever the IC state (fresh/aged). This coefficient can be extracted from simulations of the fresh IC and reused for aged ICs, which cannot be simulated. Therefore, the IA block could be modified to include that coefficient of aging.

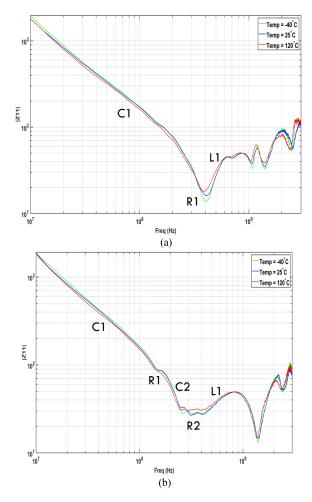

## C. Influence of Thermal Stress on Conducted Emission

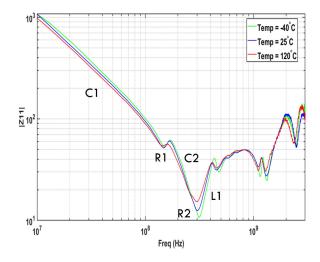

In comparison with aging, thermal stress can temporarily raise junction temperatures of CMOS transistors in the tested circuit and create a drift in their  $V_{\rm th}$ ,  $\mu_{\rm eff}$ , and drain current levels [50]. Although no permanent degradation mechanisms occur, these drifts can cause unexpected conducted emission levels. As described in Section III-A, S-parameter measurements were performed on fresh PCBs at ambient and extreme temperatures (-40 and 120 °C) to characterize the effect of thermal stress on the  $Z_{11}$  profile of  $V_{\rm DDI}$  of the H-clock tree. This time, the VNA was calibrated by placing the calibration board at extreme temperatures as well, to exclude thermal influence on the cables, the PCB traces, and the MMCX connectors.

The values of passive elements, which define the PDN block of the ICEM model, are measured till 400 MHz to extract the first-order circuit. The lumped parameters in Fig. 11 directly correspond to the ICEM-CE schematic in Fig. 8. As seen in Fig. 11, the R, L, and C values of  $Z_{11}$  increase with rise in temperature. Interestingly, the effect of thermal stress on  $Z_{11}$  over the entire frequency range was significant (38% span for R2), which could not be discarded. This implies that thermal stress has an impact on the PDN of the ICEM model, and all the extreme values (shown in Table II) of the passive elements need to be included.

Similar to aging, the conducted emission measurement results using the  $1-\Omega$  method revealed a variation of the maximum external peak-to-peak current levels due to thermal stress. As noticed from Table III, a rise in temperature substantially decreased the external peak current levels. With respect to ambient temperature, a deviation of +14% and -26% of the external peak-to-peak current was observed at -40 and 120 °C, respectively.

Fig. 11. Influence of temperature on the measured impedance profile of  $V_{\rm DDI}$  of the H-clock tree.

TABLE II DEVIATIONS IN PDN PARAMETERS EXTRACTED AT  $V_{\mathrm{DDI}}$  of the  $H\text{-}\mathrm{Clock}$  Tree Due to Thermal Stress

| Component | <i>T</i> = -40 °C | <i>T</i> = 25 °C | <i>T</i> = 120 °C |

|-----------|-------------------|------------------|-------------------|

| C1        | 13.2 pF           | 14.5 pF          | 15.9 pF           |

| R1        | 51.5 Ω            | 52 Ω             | 54 $\Omega$       |

| C2        | 17.7 pF           | 19.9 pF          | 21.5 pF           |

| R2        | 11 Ω              | 13 Ω             | 16 Ω              |

| L1        | 8.6 nH            | 9.1 nH           | 9.7 nH            |

TABLE III

VARIATION IN CONDUCTED EMISSIONS WITH THERMAL STRESS

| Temperature | External<br>peak-to-peak<br>current | Internal<br>peak-to-peak<br>current | S&H sensor<br>peak-to-peak<br>voltage |

|-------------|-------------------------------------|-------------------------------------|---------------------------------------|

| −40 °C      | 89.55 mA                            | 99.71 mA                            | 1.49 V                                |

| 25 °C       | 78.54 mA                            | 94.50 mA                            | 1.46 V                                |

| 120 °C      | 58.09 mA                            | 83.44 mA                            | 1.38 V                                |

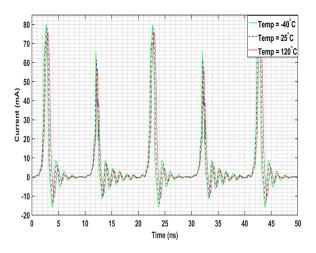

To further verify that thermal stress affects not only the PDN but also the IA block of the ICEM model, transistor-level simulations were carried out in Cadence Virtuoso for different temperatures including the thermal behavior of external passive elements. The internal current at the  $V_{\rm DDI}$  node of the H-clock tree was monitored at nominal and extreme temperatures. As illustrated in Fig. 12, the amplitude of the internal current was found to have an inverse variation with thermal stress. Furthermore, the internal peak-to-peak current found at extreme temperatures through simulations is included in Table III. Although variations in the internal current exist due to temperature, the deviations are lower compared to the externally measured current. Therefore, the dependence of the PDN and the 1- $\Omega$  output resistor on temperature enhances the effect of thermal stress on the external peak current levels. Indeed, the same method as the one related to aging can be applied for thermal using another coefficient of proportionality for extreme temperatures.

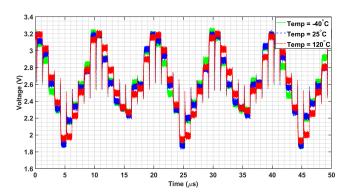

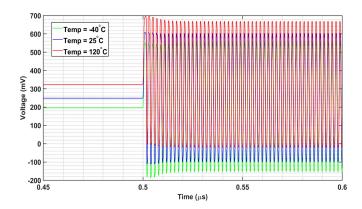

The output voltage waveform of the *S&H* voltage sensor is shown in Fig. 13. Similar to aging, no distortions were noticed

Fig. 12. Influence of temperature on the simulated internal transient current (IA) generated by the H-clock tree and monitored at  $V_{\rm DDI}$ .

Fig. 13. Influence of thermal stress on the clocked output voltage of the sensor.

in the output signal. The output peak-to-peak voltage levels were 30 mV higher and 80 mV lower compared to that of the nominal temperature, at -40 and 120 °C, respectively. Further simulations were performed on the voltage sensor to analyze how thermal stress caused variation in the output voltage in steady-state conditions. It was found that the output dc offset of the voltage sensor varied with temperature only by  $\pm 150\,\mathrm{mV}$  for input frequencies lower than 550 MHz.

Moreover, it was verified in Cadence Virtuoso that the input attenuator was the root cause for the dc offset. Fig. 14 shows the simulated output response of the dc attenuator when subjected to a sine wave input signal of 500-MHz frequency and 1-V peak voltage at nominal and extreme temperatures. It can be observed that thermal stress causes only a dc offset (±65 mV), and there is no observable change in the peak output voltage. Furthermore, it was found out that for input frequencies above 550 MHz, the peak output voltage was reduced at 120 °C. This is due to the filtering effect of the compensation capacitors. Since conducted emission tests were performed at much lower frequencies, thermal stress did not affect the peak output voltage of the sensor. Although there exists a dc offset due to temperature variation, it was checked that the reduction of the output peak-to-peak voltage levels of the sensor at maximum temperature was due

Fig. 14. Influence of thermal stress on the S&H voltage sensor attenuator for an input sine wave of 500 MHz.

to decreased internal peak-to-peak current levels of the H-clock tree.

To sum up, in this case study, the PDN of the ICEM model is not influenced by HAST aging. However, thermal stress does have an impact on the PDN, causing deviations in its lumped passive elements. The IA block of the ICEM model is influenced by both aging and thermal stress, due to different physical mechanisms, though. Aging reduces the IA amplitude, and the conducted emission levels demonstrate an inverse variation with temperature. Since the IC under test is custom designed in SOI technology, the developed ICEM-CE model cannot be compared directly with other ICs. The main difference from standardized models is the inclusion of HAST aging and thermal stress in the parameters of the proposed model.

## IV. RESULTS AND DISCUSSION OF CONDUCTED IMMUNITY

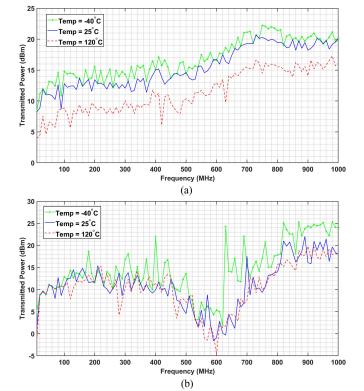

This section deals with the conducted immunity analysis of two independent analog blocks, i.e., *S-R* latch and three-stage CSVCO integrated into the tested IC. The extraction of two separate PDNs via *S*-parameter measurements and IB blocks through the DPI lookup table technique is explained. Moreover, the effects of HAST aging and thermal stress at -40 and 120 °C are analyzed in measurements and incorporated in the ICIM-CI model.

The DPI measurement setup mentioned in Section II-E was used to evaluate the susceptibility profiles of each tested circuit. The incident power was varied from 1 to 30 dBm with a step size of 1 dBm, while the frequency was changed from 1 MHz to 1 GHz in 10-MHz steps. For both the tested structures, the continuous-wave EM disturbance was superimposed over a 5-V dc bias only into its isolated power supply. The failure criterion considered for the S-R latch was  $\pm 10\%$  of the dc offset with a dwell time of 1 s. Similarly, the  $\pm 10\%$  changes in frequency or in the peak-to-peak voltage of the CSVCO was considered as its DPI failure criteria. All the selected tolerance limits were similar to industry standards. Moreover, a dwell time of 3 s was set for the latter in order to allow it enough time to stabilize after each power/frequency increment.

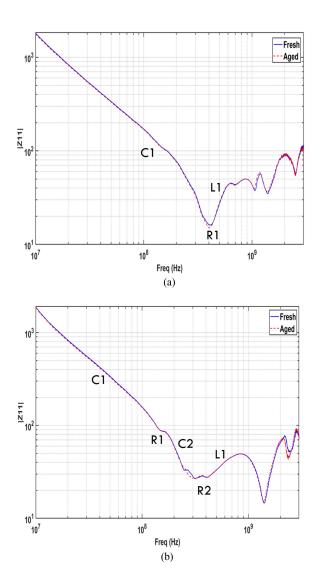

Fig. 15. Impact of aging on measured impedance profile of  $V_{\rm DDI}$  of (a) analog S-R latch and (b) three-stage CSVCO.

## A. Influence of Aging on Conducted Immunity

As highlighted in Section I, the PDN blocks of the ICIM-CI and the ICEM-CE are identical and were extracted from S-parameter measurements. Hence, the same notation as the ICEM-CE schematic was reused for the impedance profiles of the tested immunity circuits. Two independent  $Z_{11}$  impedance profiles of  $V_{\rm DDI}$  of the analog S-R latch and the three-stage CSVCO are shown in Fig. 15(a) and (b), respectively. Even though both circuits have identical pads, their impedance profiles are entirely different. The reason for this is due to the distinct mutual coupling, since the  $V_{\rm DDI}$  pad of the S-R latch is closer to its  $G_{\rm NDI}$  pad compared to the CSVCO. No parasitic resonance was observed in Fig. 15(a); therefore, R2 and C2 are nonexistent in the PDN of the S-R latch compared to the CSVCO. Similar to the  $Z_{11}$  profile of the H-clock tree, the impedance profiles of both immunity test circuits were not impacted by aging.

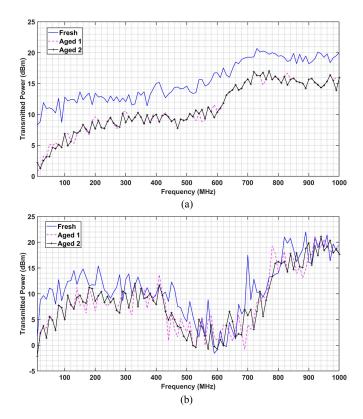

The IB block of the ICIM-CI model was constructed using lookup tables, which correspond to the amount of transmitted

Fig. 16. Effect of aging on the DPI profile of (a) analog S-R latch and (b) three-stage CSVCO.

power in the IC pin that can cause its malfunction. This can be extracted using DPI measurements. The transmitted power  $(P_t)$  is measured by the power meter and corresponds to the power injected at the PCB input. It depends on the input pin impedance and can also be calculated using  $P_{\rm inc} \times (1-|S_{11}|^2)$ , where  $(P_{\rm inc})$  is the incident power. Hence,  $P_t$  is the actual power that couples into the IC pin and is used to determine the conducted immunity profile.

To construct two separate IB blocks, DPI testing was performed by injecting conducted EM disturbances into the  $V_{\rm DDI}$  pins of the S-R latch and the CSVCO. The power  $P_t$  to induce malfunction was determined using each circuit  $S\text{-}{\rm parameters}$ . Fig. 16(a) shows the conducted immunity profile of the analog S-R latch. The failure criterion applied for the S-R latch was the dc offset of the output signal monitored at the Q pin. The immunity profile for the fresh DUT shows a gradual increase in  $P_t$  from 8 dBm at 1 MHz to 20 dBm at 1 GHz. This behavior demonstrates that the S-R latch is more susceptible at lower frequencies. Therefore, the combined effect of the package and the capacitance of the input pad results in filtering effects, hence attenuating power in higher frequency.

The frequency and the peak-to-peak voltage of integrated oscillators are important parameters to determine their stability. Thus, for the DPI testing of the CSVCO, both the parameters were considered as the failure criteria. The conducted immunity profile of the CSVCO is visible in Fig. 16(b). The IB of the CSVCO is very different compared to the *S-R* latch. Overall, the package and input pad capacitance effect is demonstrated

here as well, since the highest conducted immunity is observed above 850 MHz. However, the CSVCO is the most susceptible between 600 and 700 MHz. The reason for this could be due to the injected frequency being close to the operating frequency (703 MHz) of the CSVCO. As mentioned in Section II-C, the FD circuit is added at the output stage of the CSVCO in order to reduce the output frequency (62.5 MHz). Although the power supply of the FD is entirely isolated from EMI, it may still impact the conducted immunity evaluation. Since the CSVCO is a nonlinear circuit, a small deviation in transistor characteristics due to aging may have a higher impact on the immunity profile [comparing Aged 1 and Aged 2 in Fig. 16(b)] than for a similar pseudo circuit as the S-R latch.

DPI testing was performed on several aged DUTs, at ambient temperature, having the same failure criteria for both tested blocks. In general, aging due to HAST induced a decrease in the conducted immunity levels of both the tested circuits. The immunity profile waveforms remained the same with reduced immunity power levels. As seen in Fig. 16(a), the average  $P_t$  levels of the aged samples were 6 dB lower than the fresh sample within the tested frequency spectrum. Hence, aging only impacted the IB block of the ICIM-CI model of the S-R latch. The lower  $P_t$  and corresponding frequency values were then updated in the IB lookup table to include the effect of aging in the ICIM model.

To verify the assertion that aging affects the IB block and lowers the  $P_t$  levels that can trigger a failure, the conducted immunity of the CSVCO was compared with respect to aging [see Fig. 16(b)]. In this case, the aged  $P_t$  levels were slightly reduced (4.5 dB), compared to the fresh version, in particular in frequencies below 200 MHz. At higher frequencies, the immunity levels of the fresh and aged samples were comparable. The degradation mechanisms (NBTI) occurring in the CSVCO and the S-R latch are not the same. Since both the circuits have different functionalities and failure criteria, the impact of aging is distinct. However, it can be concluded that aging due to HAST reduces conducted immunity levels in a given frequency range for both tested analog blocks. These aged power levels can be updated in the IB block of each ICIM model to include the effect of aging. This may be achieved by means of specified deviations on IB lookup tables or different IBs according to the fresh/aged state of the block.

## B. Influence of Thermal Stress on Conducted Immunity

To validate the impact of thermal stress on the PDN of both the S-R latch and the CSVCO, S-parameter measurements were performed on fresh PCBs at extreme temperatures (-40 and 120 °C). As expected, the  $Z_{11}$  profiles of  $V_{\rm DDI}$  of the S-R latch [see Fig. 17(a)] and the CSVCO [see Fig. 17(b)] exhibited variations with thermal stress over the entire frequency range. Those deviations could not be neglected, and all tolerances were involved in the PDN block of the individual ICIM-CI models of the S-R latch (see Table IV) and the three-stage CSVCO (see Table V).

Thermal stress influences the MOSFET characteristics in ICs and can vary the robustness of an analog circuit. For the analog

Fig. 17. Influence of thermal stress on measured impedance profile of  $V_{\rm DDI}$  of (a) analog S-R latch and (b) three-stage CSVCO.

TABLE IV DEVIATIONS IN PDN PARAMETERS EXTRACTED AT  $V_{

m DDI}$  of the Analog S-R Latch Due to Thermal Stress

| Component  | <i>T</i> = -40 °C | <i>T</i> = 25 °C | T = 120 °C |

|------------|-------------------|------------------|------------|

| <i>C</i> 1 | 8.6 pF            | 9.2 pF           | 10.1 pF    |

| R1         | 15 Ω              | $17 \Omega$      | 19 Ω       |

| L1         | 8.4 nH            | 9.1 nH           | 10 nH      |

S-R latch, the 5-V (25 °C) dc level of the output was increased to 5.3 V (-40 °C) and 4.7 V (120 °C) with temperature variations. Hence, it was considered that the  $V_{\rm th}$  levels of the MOSFETs in the latch were the root cause of the change in dc output levels. For the CSVCO, the operating frequency was verified in simulations to be inversely proportional to temperature. Its output frequency after the FD was found to be 62.5 MHz at nominal temperature and varied to 68.3 and 53.8 MHz at -40 and 120 °C, respectively. For the CSVCO, the shift in frequency meant that  $V_{\rm th}$  and  $\mu_{\rm eff}$  were influenced by temperature.

To validate the effect of thermal stress on the IB block, multiple fresh DUTs were subjected to DPI testing at nominal and extreme temperatures, by injecting into  $V_{\rm DDI}$ s of the S-R latch and the CSVCO. Similar failure criteria considered for

TABLE V DEVIATIONS IN PDN PARAMETERS EXTRACTED AT  $V_{\rm DDI}$  of the Three-Stage CSVCO Due to Thermal Stress

| Component | T = -40 °C  | <i>T</i> = 25 °C | <i>T</i> = 120 °C |

|-----------|-------------|------------------|-------------------|

| C1        | 8.8 pF      | 9.6 pF           | 10.6 pF           |

| R1        | 87 Ω        | 88 Ω             | 89 Ω              |

| C2        | 12.2 pF     | 13.3 pF          | 15 pF             |

| R2        | $27 \Omega$ | 28 Ω             | $32 \Omega$       |

| L1        | 9.2 nH      | 10.6 nH          | 11.9 nH           |

Fig. 18. Influence of thermal stress on the DPI profile of (a) analog *S-R* latch and (b) three-stage CSVCO.

the nominal temperature were applied at extreme temperatures for both the circuits. The influence of thermal stress on the conducted immunity profiles of the S-R latch and the three-stage CSVCO is illustrated in Fig. 18(a) and (b), respectively. For the S-R latch, the increase in temperature lowered the conducted immunity  $P_t$  levels. As observed in Fig. 18(a), compared to the nominal temperature, the average  $P_t$  levels were improved by 1.8 dB at minimum temperature, while they were lowered by 5.1 dB at maximum temperature. Owing to the drift in  $V_{\rm th}$  levels of the MOSFETs in the latch, the conducted immunity of the latter was extensively influenced by the thermal stress.

In the case of the CSVCO [see Fig. 18(b)], the conducted immunity profile approximately remained the same at 120 °C across the entire frequency spectrum. However, at -40 °C, the average  $P_t$  levels improved substantially by 9.2 dB between 600 and 700 MHz. It continued to be slightly higher (1 dB) than the  $P_t$  levels at 25 °C for frequencies between 700 MHz and 1 GHz. The conducted immunity of the CSVCO was found to be resilient to higher temperatures; however, lower temperatures

had an impact on its conducted immunity due to the drift in  $\mu_{\rm eff}$  and  $V_{\rm th}$  levels. Hence, for both the circuits, the thermal stress influenced their respective IB blocks of the ICIM-CI models. Similarly to aging, deviations can be applied to the IB lookup tables as a function of temperature.

To summarize, the PDN blocks of the two tested circuits, i.e., S-R latch and CSVCO, were shown to be influenced by thermal stress rather than aging. It was also verified that HAST aging lowers the immunity power levels of each circuit's IB block for a specific frequency range. Intrinsic degradation mechanisms, such as NBTI, are the cause of that behavior. Furthermore, the conducted immunity levels of the S-R latch were demonstrated to inversely vary with thermal stress, while the CSVCO's immunity was impacted only at lower temperatures. This is due to thermal stress causing a drift in  $\mu_{\rm eff}$  and  $V_{\rm th}$  levels of the latter. Further explanation of the influence of temperature on physical transistor parameters, i.e.,  $V_{\rm th}$  and  $\mu_{\rm eff}$ , as well as their relation to the EMC behavior of the integrated blocks can be found in [50].

#### V. CONCLUSION

The concept of involving environmental effects, such as aging and thermal stress on the conventional conducted emission (ICEM-CE) and immunity (ICIM-CI) models, was put into practice herein through measurements and transistor-level simulations. HAST testing was performed for the first time on a custom-designed IC developed in SOI technology, comprising several independent analog CMOS structures such as *H*-clock tree, *S&H* voltage sensor, *S-R* latch, and three-stage CSVCO, to characterize the effect of aging on conducted emission and immunity levels. It considered the combined effect of environmental stresses i.e., temperature and humidity that caused deviations in IC parameters. Furthermore, extreme temperature tests were performed on several packaged ICs in order to extensively analyze the influence of thermal stress on the conducted susceptibility and emission levels.

Unlike with HAST aging, the PDN block of the developed models was influenced by thermal stress causing variations in its lumped passive elements, which must be included in the models for improved accuracy. However, HAST aging caused the permanent degradation mechanism (NBTI), while thermal stress temporarily impacted the MOSFET characteristics (i.e.,  $\mu_{\rm eff}$  and  $V_{\rm th}$ ) that could cause IC soft failures. Those mechanisms were demonstrated to almost exclusively influence the active blocks (i.e., IA and IB) of the conducted emission and immunity models.

A simulation-based transistor-level approach was used to develop the IA block of the ICEM-CE model, providing a good correlation with measurements. By applying conducted emission measurements using the 1- $\Omega$  method on the H-clock tree, it was demonstrated that the external current emission levels would degrade with aging and temperature increase. This effect was traced back to the variation in the internal current (IA) in case of thermal stress. Therefore, it was shown that constant proportionality coefficients extracted from simulations (temperature) and measurements (aging) could be included into the IA blocks of the models.

Using DPI measurements on two independent S-R latch and CSVCO analog circuits, it was shown that aging due to HAST increases the conducted susceptibility levels as a function of frequency depending on the functionality of the analog block. Moreover, high-temperature stress was found to also reduce their conducted immunity levels depending on the drifts in  $V_{\rm th}$  and  $\mu_{\rm eff}$  levels. Specified deviations in the lookup tables can be applied to include the influence of aging and thermal stress on the IB block.

For the considered scenarios, the developed ICEM-CE and ICIM-CI models were demonstrated to quantify conducted emission and immunity levels with enough accuracy under aging and thermal stress. This paves the way to the inclusion of such deviations in future revised versions of those standards.

#### ACKNOWLEDGMENT

This article reflects only the authors' view, exempting the European Union from any liability. Project website: http://etn-peter.eu/.

#### REFERENCES

- [1] A. Boyer and E. Sicard, "A case study to apprehend RF susceptibility of operational amplifiers," in *Proc. 12th Int. Workshop Electromagn. Compat. Integr. Circuits*, 2019, pp. 13–15.

- [2] B. Mohajer-Iravani and O. M. Ramahi, "Suppression of EMI and electromagnetic noise in packages using embedded capacitance and miniaturized electromagnetic bandgap structures with high-k dielectrics," *IEEE Trans. Adv. Packag.*, vol. 30, no. 4, pp. 776–778, Nov. 2007.

- [3] J. Zhang, D. Pommerenke, and J. Fan, "Determining equivalent dipoles using a hybrid source-reconstruction method for characterizing emissions from integrated circuits," *IEEE Trans. Electromagn. Compat.*, vol. 59, no. 2, pp. 567–575, Apr. 2017.

- [4] M. Koohestani, A. K. Skrivervik, and M. Ramdani, "An analytical approach for the estimation of the far-field reduction obtained by placing closed conductor loops in proximity to a chip," *IEEE Trans. Electromagn. Compat.*, vol. 63, no. 5, pp. 1384–1394, Oct. 2021.

- [5] B. Pu, J. Fan, and W. Nah, "Immunity enhancement of the power distribution network in integrated circuits with coplanar meander lines in package," *IEEE Trans. Electromagn. Compat.*, vol. 62, no. 5, pp. 2238–2246, Oct. 2020.

- [6] R. Peng et al., "Noise immunity improvement in high voltage gate driver IC," in *Proc. 14th IEEE Int. Conf. Solid-State Integr. Circuit Technol.*, 2018, pp. 1–3.

- [7] N. Czepl, B. Deutschmann, and A. Michalowska-Forsyth, "Influence of ionizing radiation on the conducted electromagnetic emission of integrated circuits," *Microelectron. Rel.*, vol. 126, 2021, Art. no. 114335.

- [8] EMC IC modeling—Part 2: Models of Integrated Circuits for EMI Behavioral Simulation—Conducted Emissions Modeling (ICEM-CE), 2.0 ed., IEC Standard IEC62433-2:2017, Jan. 2017.

- [9] EMC IC Modeling—Part 4: Models of Integrated Circuits for RF Immunity Behavioral Simulation—Conducted Immunity Modeling (ICIM-CI), 1.0 ed., IEC Standard IEC62433-4:2016, May 2016.

- [10] S. R. Rao et al., "Black-box behavioral DC-DC converter IC emission model," in *Proc. IEEE Int. Symp. Electromagn. Compat. Signal/Power Integr.*, 2022, pp. 570–574.

- [11] J. Koo et al., "A nonlinear microcontroller power distribution network model for the characterization of immunity to electrical fast transients," *IEEE Trans. Electromagn. Compat.*, vol. 51, no. 3, pp. 611–619, Jul. 2009.

- [12] W. Mao, W. Li, Y. Tian, B. Vrignon, J. Shepherd, and R. Wang, "A pad ICIM model for EMC immunity simulation," in *Proc. Asia-Pacific Symp. Electromagn. Compat.*, 2012, pp. 397–400.

- [13] E. A. Amerasekera and F. N. Najm, Failure Mechanisms in Semiconductor Devices, 2nd ed. Hoboken, NJ, USA: Wiley, 1997.

- [14] M. White, D. Vu, D. Nguyen, R. Ruiz, Y. Chen, and J. B. Bernstein, "Product reliability trends, derating considerations and failure mechanisms with scaled CMOS," in *Proc. IEEE Int. Integr. Rel. Workshop*, 2006, pp. 156–159.

- [15] W. H. Parker and W. Tustin, "The case for combining EMC and environmental testing," in *Proc. Interference Technol. Engineer's Master*, 2002, pp. 54–60.

- [16] C. Fiegna, Y. Yang, E. Sangiorgi, and A. G. O'Neill, "Analysis of self-heating effects in ultrathin-body SOI MOSFETs by device simulation," *IEEE Trans. Electron Devices*, vol. 55, no. 1, pp. 233–244, Jan. 2008.

- [17] X. Gao et al., "Modeling static delay variations in push–pull CMOS digital logic circuits due to electrical disturbances in the power supply," *IEEE Trans. Electromagn. Compat.*, vol. 57, no. 5, pp. 1179–1187, Oct. 2015.

- [18] J.-L. Levant, M. Ramdani, and R. Perdriau, "ICEM modeling of microcontroller current activity," *Microelectron. J.*, vol. 35, no. 6, pp. 501–507, Jun. 2004.

- [19] L. Yuanhao, X. Shuguo, and C. Yishu, "A new methodology to build the ICEM-CE model for microcontroller units," in *Proc. IEEE Int. Workshop Electromagn.: Appl. Student Innov. Competition*, 2022, pp. 1–3.

- [20] N. Berbel, R. Fernàndez-Garcia, I. Gil, B. Li, S. Ben-Dhia, and A. Boyer, "An alternative approach to model the internal activity of integrated circuits," in *Proc. 8th Int. Workshop Electromagn. Compat. Integr. Circuits*, 2012, pp. 88–92.

- [21] N. Berbel, R. Fernandez-Garcia, and I. Gil, "Characterization and modeling of the conducted emission of integrated circuits up to 3 GHz," *IEEE Trans. Electromagn. Compat.*, vol. 56, no. 4, pp. 878–884, Aug. 2014.

- [22] N. Berbel, R. Fernandez-Garcia, and I. Gil, "Characterization of conducted emission at high frequency under different temperature," in *Proc. 9th Int.* Workshop Electromagn. Compat. Integr. Circuits, 2014, pp. 147–151.

- [23] A. Boyer, A. C. Ndoye, S. B. Dhia, L. Guillot, and B. Vrignon, "Characterization of the evolution of IC emissions after accelerated aging," *IEEE Trans. Electromagn. Compat.*, vol. 51, no. 4, pp. 892–900, Nov. 2009.

- [24] C. Ghfiri, A. Boyer, A. Durier, and S. Ben Dhia, "A new methodology to build the internal activity block of ICEM-CE for complex integrated circuits," *IEEE Trans. Electromagn. Compat.*, vol. 60, no. 5, pp. 1500–1509, Oct. 2018.

- [25] C. Ghfiri, A. Boyer, A. Bensoussan, A. Durier, and S. B. Dhia, "A new methodology for EMC prediction of integrated circuits after aging," *IEEE Trans. Electromagn. Compat.*, vol. 61, no. 2, pp. 572–581, Apr. 2019.

- [26] S. H. Airieau, T. Dubois, G. Duchamp, and A. Durier, "Multiport ICIM-CI modeling approach applied to a bandgap voltage reference," in *Proc. Int. Symp. Electromagn. Compat.*, 2016, pp. 526–531.

- [27] Z. Dongyao, Z. Changlin, Y. Daojie, L. Shuang, H. Kai, and Z. zhilong, "Immunity model of the embedded CAN controller to conducted interferences," in *Proc. 12th Int. Workshop Electromagn. Compat. Integr. Circuits*, 2019, pp. 186–188.

- [28] A. Durier, P. Fernandez-Lopez, J.-L. Levant, and C. Marot, "ICIM-CPI: Integrated circuits immunity model: Conducted pulse immunity: Description, extraction and example," 2018 IEEE Int. Symp. Electromagn. Compat. and 2018 IEEE Asia-Pacific Symp. Electromagn. Compat. (EMC/APEMC), 2018, pp. 695–700.

- [29] A. Boyer, S. Ben Dhia, B. Li, C. Lemoine, and B. Vrignon, "Prediction of long-term immunity of a phase-locked loop," *J. Electron. Testing*, vol. 28, no. 6, pp. 791–802, Nov. 2012.

- [30] J. Cheng, C. Zhou, D. Yu, Z. Xu, and D. Zhang, "An ICIM-CI-T model for EMI prediction of IO element on typical FPGA with temperature effect considered," *IEEE Trans. Electromagn. Compat.*, vol. 62, no. 3, pp. 755–764, Jun. 2020.

- [31] Q. M. Khan, A. Ramezani, M. Koohestani, M. Ramdani, and R. Perdriau, "A comparison among DPI immunities of multi-stage CSVCOs and ring oscillators," in *Proc. 13th Int. Workshop Electromagn. Compat. Integr. Circuits*, 2022, pp. 123–127.

- [32] Q. M. Khan et al., "Experimental characterization of multitone EM immunity of integrated oscillators under thermal stress," *IEEE Access*, vol. 10, pp. 83898–83915, 2022.

- [33] Integrated Circuits—Measurement of Electromagnetic Emissions—Part 4: Measurement of Conducted Emissions—1 ohm/150 ohm Direct Coupling Method, 2nd ed., Standard IEC 61967, Mar. 2021.

- [34] Integrated Circuits—Measurement of Electromagnetic Immunity 150 kHz to 1 GHz—Part 4: Direct RF Power Injection Method, 1st ed., Standard IEC 62132, 2006.

- [35] H. Pues and D. Pissoort, "Design of IEC 62132-4 compliant DPI test boards that work up to 2 GHz," in *Proc. Int. Symp. Electromagn. Compat.*, 2012, pp. 1–4.

- [36] A. Ramezani, Q. M. Khan, and H. Pues, "A new TRL/TRM PCB-based calibration method for on-board devices under test (DUTs)," in *Proc. 13th Int. Workshop Electromagn. Compat. Integr. Circuits*, 2022, pp. 112–116.

- [37] F. Fiori and F. Musolino, "Investigations on the correlation between IC-conducted emission and chip-level power supply current," *IEEE Trans. Electromagn. Compat.*, vol. 47, no. 1, pp. 28–33, Feb. 2005.

- [38] S. Delmas-Bendhia, E. Sicard, and F. Caignet, "A new method for measuring signal integrity in CMOS ICs," *Microelectron. Int. J.*, vol. 17, pp. 17–21, 2000.

- [39] A. Boyer, S. Ben Dhia, C. Lemoine, and B. Vrignon, "An on-chip sensor for time domain characterization of electromagnetic interferences," in *Proc.* 8th Int. Workshop Electromagn. Compat. Integr. Circuits, 2012, pp. 251– 256.

- [40] P. G. A. Jespers and B. Murmann, Systematic Design of Analog CMOS Circuits: Using Pre-Computed Lookup Tables. Cambridge, U.K.: Cambridge Univ. Press, 2017.

- [41] Q. M. Khan, R. Perdriau, M. Ramdani, and M. Koohestani, "A comparative study of on-chip CMOS S&H voltage sensors for power integrity: SOI vs. bulk," *IEEE Int. Joint Symp. EMC/SI/PI EMC Eur.*, 2021, pp. 911–616.

- [42] I. P. Tolić, J. Mikulić, G. Schatzberger, and A. Barić, "Design of CMOS temperature sensors based on ring oscillators in 180-nm and 110-nm technology," in *Proc. 43rd Int. Conv. Inf., Commun. Electron. Technol.*, 2020, pp. 104–108.

- [43] B. Razavi, "Oscillators," in *Design of Analog CMOS Integrated Circuits*. New York, NY, USA: McGraw-Hill Educ., 2001, ch. 15.

- [44] K. Mbarek, S. Ghedira, F. O. Rziga, and K. Besbes, "Design and analysis of nonvolatile memristor-based S-R Latch," in *Proc. IEEE Int. Conf. Des. Test Integr. Micro Nano-Syst.*, 2020, pp. 1–5.

- [45] H. Liu, T. Claeys, D. Pissoort, and G. A. E. Vandenbosch, "Characterizing EMI-filters' deviations caused by the capacitors ageing based on complex impedance analysis," in *Proc. Int. Symp. Electromagn. Compat.*, 2020, pp. 1–5.

- [46] W.-T. K. Chien, J. X. Luo, and M. Zhang, "The competing aging effects on SRAM operating life tests," *IEEE Trans. Device Mater. Rel.*, vol. 19, no. 2, pp. 416–425, Jun. 2019.

- [47] C. Zorn and N. Kaminski, "Acceleration of temperature humidity bias (THB) testing on IGBT modules by high bias levels," in *Proc. 27th Int. Symp. Power Semicond. Devices IC's*, 2015, pp. 385–388.

- [48] Semiconductor Devices—Mechanical and Climatic Test Methods—Part 4: Damp Heat, Steady State, Highly Accelerated Stress Test (HAST), 2.0 ed., IEC Standard IEC60749-4:2017, Mar. 2017.

- [49] A. Boyer, "A low-cost RF detector to enhance the direct power injection conducted immunity setup," *IEEE Lett. Electromagn. Compat. Pract. Appl.*, vol. 4, no. 4, pp. 108–113, Dec. 2022.

- [50] Q. M. Khan, M. Koohestani, and R. Perdriau, "Influence of temperature on the EFT immunity of multistage integrated oscillators," *IEEE Trans. Electromagn. Compat.*, vol. 65, no. 1, pp. 138–148, Feb. 2023.

Qazi Mashaal Khan (Graduate Student Member, IEEE) received the B.Sc. degree (summa cum laude) in electrical engineering from the National University of Computer and Emerging Sciences, Islamabad, Pakistan, in 2016, the EU-funded Erasmus + Joint M.Sc. degree (with distinction) in smart systems integration from Heriot-Watt University, Edinburgh, U.K., University of South-Eastern Norway, Notodden, Norway, and Budapest University of Technology and Economics, Budapest, Hungary, in 2019, and the Ph.D. (Hons.) degree in electronics engineering from the

Institut National des Sciences Appliquées, Rennes University, Rennes, France, in 2023.

His master thesis focused on digital system design concepts and was hosted at eesy-IC GmbH, Erlangen, Germany. His doctoral work was funded by the EU Horizon 2020 MSCA ETN PETER project and was carried out at the Department of Electrical and Electronic Engineering, ESEO School of Engineering, Angers, France. He is currently a Postdoctoral Researcher with the Microwave Electronics Laboratory, Department of Microtechnology and Nanoscience, Chalmers University of Technology, Gothenburg, Sweden. He has authored or coauthored several peer-reviewed scientific journal and conference publications. His main research interests include multiphysical thermal modeling, microwave packaging, electromagnetic compatibility design, and reliability characterization of integrated circuits.

Mohsen Koohestani (Senior Member, IEEE) received the Ph.D. (Hons.) degree in electromagnetics from the École Polytechnique fédérale de Lausanne, Lausanne, Switzerland, and the Universidade de Lisboa, Lisbon, Portugal, in 2014.

From 2014 to 2018, he was a Senior Research Fellow with the Institut d'Electronique et de Télécommunications de Rennes, University of Rennes 1, Rennes, France, working mainly on biomedical applications of wireless power transfer systems. Since 2018, he has been an Associate Professor with the ESEO School

of Engineering, Angers, France. He is also an Associate Researcher with the Institute of Electronics and Telecommunications of Rennes (UMR CNRS 6164), University of Rennes 1. He has authored more than 70 peer-reviewed scientific papers. His main interests include antennas, microwaves, electromagnetic compatibility (EMC), and biomedical engineering.

Dr. Koohestani is an official Member of the IEC standardization working groups (WG2 and WG9) in the SC47A French subcommittee on the EMC for integrated circuits.

**Jean-Luc Levant** received the Ph.D. degree in electronics from the Institute National des Sciences Appliques, Rennes, France, in 2007.

He is in retirement and a Senior Electromagnetic Compatibility (EMC) Expert with Microchip, Nantes, France. His research interests include integrated circuits modeling, power and signal integrity, and electrical fast transient analysis.

Dr. Levant was a Member of the IEC standardization working group in the SC47A subcommittee on the EMC for integrated circuits.

Mohamed Ramdani (Senior Member, IEEE) received the Ph.D. degree in microelectronics from Université Paul Sabatier, Toulouse, France, in 1989, and the "Habilitation á Diriger des Recherches" (Accreditation Degree) from Université de Rennes 1, Rennes, France, in 2004.

From 1991 to 2008, he was an Associate Professor of Microelectronics and Microwave Electronics with the ESEO School of Engineering, Angers, France, where he became a Full Professor in 2008. He has authored several book chapters and many peer-reviewed

scientific papers. His research interests include electromagnetic compatibility (EMC) of integrated circuits and integrated circuit design.

Dr. Ramdani is a Member of the Union Technique de l'Electricité et de la communication (French section of the International Electrotechnical Commission). He was a General Chair of 2017 International Symposium on Electromagnetic Compatibility, Angers. He was the elected Vice-Chair of the IEEE France Section in 2016.

Richard Perdriau (Senior Member, IEEE) was born in Angers, France, in 1971. He received the Engineering degree in electronics and computer science from ESEO Angers—Grande Ecole d'Ingénieurs Généralistes, Angers, France, in 1992, the Ph.D. degree in applied sciences from Université Catholique de Louvain, Louvain-la-Neuve, Belgium, in 2004, and the Habilitation á Diriger des Recherches (Accreditation degree) in electronics from the Université de Rennes 1, Rennes, France, in 2012.

From 1992 to 2012, he was an Associate Professor of Microelectronics and Embedded Systems with the ESEO School of Engineering, Angers, where he became a Full Professor in 2013. His research interests include electromagnetic compatibility (EMC) of integrated circuits, mixed-signal hardware description languages, and integrated circuit design.

Dr. Perdriau was the Vice-Chair and the Technical Program Co-Chair of 2017 International Symposium on Electromagnetic Compatibility. In January 2020, he was elected as the Secretary of the IEEE France Section.