# Formally Verifying Optimizations with Block Simulations

Léo Gourdin, Benjamin Bonneau, Sylvain Boulmé, David Monniaux, Alexandre Bérard

## ▶ To cite this version:

Léo Gourdin, Benjamin Bonneau, Sylvain Boulmé, David Monniaux, Alexandre Bérard. Formally Verifying Optimizations with Block Simulations. Proceedings of the ACM on Programming Languages, 2023, 7 (OOPSLA2), pp.59-88. 10.1145/3622799. hal-04102940v3

# HAL Id: hal-04102940 https://hal.science/hal-04102940v3

Submitted on 21 Sep 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Copyright

## Formally Verifying Optimizations with Block Simulations

LÉO GOURDIN, Univ. Grenoble Alpes, CNRS, Grenoble INP, Verimag, France BENJAMIN BONNEAU, Univ. Grenoble Alpes, CNRS, Grenoble INP, Verimag, France SYLVAIN BOULMÉ, Univ. Grenoble Alpes, CNRS, Grenoble INP, Verimag, France DAVID MONNIAUX, Univ. Grenoble Alpes, CNRS, Grenoble INP, Verimag, France ALEXANDRE BÉRARD, Univ. Grenoble Alpes, CNRS, Grenoble INP, Verimag, France

CompCert (ACM Software System Award 2021) is the first industrial-strength compiler with a mechanically checked proof of correctness. Yet, CompCert remains a moderately optimizing C compiler. Indeed, some optimizations of "gcc -01" such as *Lazy Code Motion* (LCM) or *Strength Reduction* (SR) were still missing: developing these efficient optimizations together with their formal proofs remained a challenge.

Cyril Six et al. have developed efficient formally verified translation validators for certifying the results of superblock schedulers and peephole optimizations. We revisit and generalize their approach into a framework (integrated into CompCert) able to validate many more optimizations: an enhanced superblock scheduler, but also *Dead Code Elimination* (DCE), *Constant Propagation* (CP), and more noticeably, LCM and SR. In contrast to other approaches to translation validation, we co-design our untrusted optimizations and their validators. Our optimizations provide hints, in the forms of *invariants* or *CFG morphisms*, that help keep the formally verified validators both simple and efficient. Such designs seem applicable beyond CompCert.

CCS Concepts: • Computer systems organization  $\rightarrow$  Reduced instruction set computing; • Software and its engineering  $\rightarrow$  Compilers; Retargetable compilers; Semantics; • Theory of computation  $\rightarrow$  Logic and verification; Automated reasoning; Higher order logic.

Additional Key Words and Phrases: Formal verification of compiler optimizations, the Coq proof assistant, Translation validation, Symbolic execution.

**Note**: this documents extends with appendices the peer-reviewed article

Léo Gourdin, Benjamin Bonneau, Sylvain Boulmé, David Monniaux, and Alexandre Bérard. 2023. Formally Verifying Optimizations with Block Simulations. *Proc. ACM Program. Lang. 7*, OOPSLA2, Article 224 (October 2023), 30 pages. https://doi.org/10.1145/3622799

#### 1 CONTEXT AND MOTIVATIONS

Compilers are complex pieces of software, and are thus likely to contain bugs. Some bugs result in the compiler crashing or aborting, some in missed optimizations, and some, more annoyingly, result in miscompilation: the generated code is incorrect. Many miscompilation bugs have been found in the optimization phases of major compilers such as GCC and LLVM [Zhou et al. 2021].

Authors' addresses: Léo Gourdin, Univ. Grenoble Alpes, CNRS, Grenoble INP, Verimag, 38401, France, Leo.Gourdin@grenoble-inp.org; Benjamin Bonneau, Univ. Grenoble Alpes, CNRS, Grenoble INP, Verimag, 38401, France, Benjamin. Bonneau@univ-grenoble-alpes.fr; Sylvain Boulmé, Univ. Grenoble Alpes, CNRS, Grenoble INP, Verimag, 38401, France, Sylvain.Boulme@univ-grenoble-alpes.fr; David Monniaux, Univ. Grenoble Alpes, CNRS, Grenoble INP, Verimag, 38401, France, David.Monniaux@univ-grenoble-alpes.fr; Alexandre Bérard, Univ. Grenoble Alpes, CNRS, Grenoble INP, Verimag, 38401, France, Alexandre.Berard2@univ-grenoble-alpes.fr.

Translation validation, as coined and popularized by Pnueli et al. [1998], is a defensive approach for ruling out miscompilation. It consists in validating, during or after compilation, that the *target code* (of a single transformation or even for a whole compilation run) matches the *source code*. Hence, the correctness of the compiler is reduced to that of the validators. This is likely simpler and more maintainable than proving the correctness of each individual optimization, since a given validator may be robust to optimization tuning, or may even validate a whole class of transformations.

Checking semantic equivalence between two code fragments is undecidable in general. Yet, two major successes of software formal verification have leveraged translation validation. Comp-Cert [Leroy 2009a] uses a specialized validator to check register allocation [Rideau and Leroy 2010]. The validator is specific to this compilation phase. In contrast, seL4 [Sewell et al. 2013] attempts to automatically match the C source and object code of the seL4 kernel (itself proved correct w.r.t. a high-level specification); the resulting verification conditions are discharged by an SMT solver.

These two projects had very different constraints. The seL4 validation team had to work with an existing compiler, which was not to be modified; but they could write the software to be compiled in a certain way that helped with the "matching", and they could tune per-module optimization options if needed. Their scheme is unlikely to work with other programs, or even with other compiler versions, unless these programs or the matching scheme are manually modified. In contrast, CompCert was (informally) expected to compile arbitrary source programs without failure; but code transformations and validators were designed together. In such a context, it is possible to have the code transformation leave hints to the validator. The validator is then likely to be more robust (it need not guess how source and target match), simpler, and to perform fewer computations.

However, according to Leroy [2011], special-purpose translation validation is not a "silver bullet" either. Indeed, developing specific validators is tedious and expensive: they should be formally proved yet reasonably efficient, two characteristics that may be contradictory. Moreover, between ultra-specialized validators and fully-general ones, there is a continuum that remains to be systematically explored. Paving this way, Necula [2000] proposed a general-purpose but *predictable* translation validator (without a formal proof) combining *symbolic execution* [King 1976; Samet 1976] and *normalized rewriting*. Tristan and Leroy [2008] showed how to build a formally verified instruction scheduler from formally verified symbolic execution. Yet, their validator did not scale.<sup>3</sup> Then, they proposed [Tristan and Leroy 2009, 2010] formally verified translation validations of lazy code motion and other optimizations. None of their extensions were integrated into the public releases of CompCert.<sup>4</sup> Tatlock and Lerner [2010] designed an extensible CompCert by translation validation, but their validator was not formally verified, hence significantly augmenting the Trusted Computing Base.<sup>5</sup> The register allocator introduced by Rideau and Leroy [2010] was the first formally verified optimization by translation validation to be integrated into mainline CompCert. Its validator uses a specialized formally verified data-flow analysis, still used in current releases.

Since these works, from more than a decade ago, the efficiency of formally verified translation validation for advanced optimization, in particular in CompCert, did not progress a lot (see related works in §9), despite the interest in improving the performance of the generated code—a sign of the difficulty of the task. Recently, Boulmé, Monniaux and Six designed an efficient formally verified

<sup>&</sup>lt;sup>1</sup>According to [Sewell et al. 2013, §4.2], the translation validation of seL4 is very unstable w.r.t. the version of GCC.

<sup>&</sup>lt;sup>2</sup>This is another argument against general-purpose translation validation based on SMT-solving for compilation of many different and evolving code bases: SMT solvers tend to be brittle, changes in solver version or minor changes in the source program may result in the solver timing out on validation problems that it could previously discharge.

<sup>&</sup>lt;sup>3</sup> Source code for their extensions at https://github.com/jtristan/CompCert-Extensions. Tristan and Leroy [2008, §7] mention two important algorithmic issues (including lack of hash-consing) that were solved in [Six et al. 2022].

<sup>&</sup>lt;sup>4</sup>https://github.com/AbsInt/CompCert

<sup>&</sup>lt;sup>5</sup>See [Monniaux and Boulmé 2022] for an extensive discussion of CompCert's TCB.

translation validation by symbolic execution thanks to formally verified hash-consing [Boulmé 2021; Six et al. 2020]. Then Six et al. [2022] extended the approach for validating an efficient superblock scheduling with peephole optimizations in CompCert.<sup>6</sup>

This paper generalizes the translation validation techniques of Six et al. [2022] to support a larger class of optimizations, including Lazy Code Motion (LCM) [Knoop et al. 1995, 1992] and Lazy Strength Reduction (LSR) [Knoop et al. 1993] which were not yet provided by CompCert. First, §2 gives a high-level introduction to our translation validators. Second, §3 details our central contribution: a new IR (Intermediate Representation) called BTL (Block Transfer Language), along with a symbolic simulation validator, dedicated to "inter-block transformations", a concept introduced in §2.2.2. Then, three sections apply our validators to a distinct optimization: §4 to superblock scheduling, §5 to LCM, and §6 to LSR. Last, §7 briefly discusses how the translations need to be instrumented for being validated, §8 gives an experimental evaluation, §9 describes related works and §10 concludes on our main insights. Our implementation, called Chamois CompCert (or simply Chamois), 7 represents around 12Kloc of Coq and 5Kloc of OCaml oracles, without comments and excluding the code that we directly reused from Six-et-al.

## 2 INTRODUCTION TO OUR VALIDATORS

We consider optimizations over RTL code [Leroy 2009b]. RTL (Register Transfer Language) is an IR of CompCert's backend representing each function as a CFG (Control Flow Graph) of instructions, themselves operating over an unbounded set of pseudo-registers. These pseudo-registers are allocated to the actual machine registers by a subsequent pass, called register allocation [Rideau and Leroy 2010], to another IR called LTL. Hence, RTL is convenient for "middle-end" optimizations, because they can easily introduce fresh (pseudo)registers for storing intermediate results.

We mainly combine two kinds of translation validators: the first one, described §2.1, targets code duplications or factorizations; the second one, described §2.2, targets what we call *inter-block transformations*. At high-level, each of our optimizations can be viewed as a composition of several transformations on the RTL code, with generally "preprocessing passes" (e.g. loop-unrolling or register renaming), the core of the optimization (e.g. superblock scheduling) and possibly some "post-processing passes" (e.g. code factorization). Each transformation must be checked by a validator. Distinct transformations may be checked by the same validator. If each transformation in a sequence can be checked by the same validator, then the oracles performing them can sometimes be composed into a single oracle requiring a single validator run at the end.

In CompCert, the correctness of a backend pass is established by a *forward simulation proof* [Leroy 2009b]. Each of our validators is thus formally proved to establish a forward simulation of the source code by the target code. Validation is helped by *hints* provided by oracles: information easy for the oracle to yield, but that would be hard to have the validators reconstruct.

## 2.1 CFG Morphisms for Duplications or Factorizations

By specialization of the notion of *graph homomorphism*, we define a *CFG morphism* between two RTL CFG as a mapping between the nodes of the CFG preserving the instruction contents with the successor relationship (and the successor orders), and also preserving the CFG entry point. Almost trivially, two CFG related by a CFG morphism are bisimulable (they are semantically equivalent).

<sup>&</sup>lt;sup>6</sup>Mullen et al. [2016] formally verified peephole optimizations for x86-32 within CompCert, based on the integer representation of pointers. Such low-level optimizations are out-of-scope of our work. In contrast, they do not support instruction reordering, nor loop optimizations. Moreover, they introduced a peephole execution engine with formally verified rewriting rules, but in a direct style, without translation validation.

<sup>&</sup>lt;sup>7</sup>https://gricad-gitlab.univ-grenoble-alpes.fr/certicompil/Chamois-CompCert

Checking that a given function is a CFG morphism is also very easy. Hence, we reuse the CFG morphism checker, initially introduced by [Six et al. 2022, §4.4].

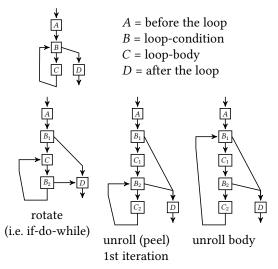

Indeed, Six noticed that many code duplications useful for superblock scheduling—e.g. tail duplication, loop-unrollings—are CFG morphisms: their mapping is the function associating each duplicated node in the target CFG to its origin in the source CFG. Fig. 1 depicts various loop-unrollings on an abstract CFG: their CFG morphism corresponds to the mapping that forgets numeric indices on node contents.

Our first improvement is to notice that the reverse transformations, i.e. code factorizations, can also be verified with the same validator (thanks to the reverse simulation). In particular, we formally verify a CFG minimization pass which mimics Moore's algorithm for DFA (deterministic finite automaton) minimization.

We have also generalized the notion of CFG morphism for mappings from BTL—our new IR

Fig. 1. Three loop-unrollings of a "while-do" loop

detailed in §2.2—to RTL. Roughly speaking, in BTL, a CFG node syntactically corresponds to a loop-free fragment of a RTL CFG: a BTL program partitions a RTL program into blocks. A variant of Six's CFG morphism checker [Six et al. 2022, §4.4]—called the *BTL projection checker*—validates the selection of these blocks in the RTL code, modulo code duplication or insertion of *synthetic nodes*<sup>8</sup>. While these transformations are validated during the RTL to BTL translation, the factorization from our minimization oracle is validated on the way back to RTL.

## 2.2 Block-by-Block Symbolic Simulation Modulo Invariants

Given a RTL CFG, we characterize a *block of this CFG* as a loop-free sub-CFG that has a single entry-point from the remainder of the surrounding CFG, and where only exit-points may emit observational events. Replacing a block by a semantically equivalent one does not change the global CFG semantics. More generally, by partitioning the CFG into blocks, we decompose the "global" simulation proof between two CFGs into a finite conjunction of "local" simulation proofs between block pairs. Then, by means of invariant annotations, the "local" simulations are aggregated at the global level, making sure that changes are consistent between blocks. Validation of these block simulations is fully automated by comparing their *symbolic executions* [Six et al. 2020].

2.2.1 Intra-Block Transformations. Symbolic execution of both blocks amounts to computing the final contents of registers and of the memory as symbolic expressions over their initial contents. If these expressions are structurally equal, then these concrete executions are observationally equivalent, assuming these executions do not trap. Since certain processor operations may trap (e.g. reading from invalid memory locations, division by zero), the symbolic execution of each block also computes a symbolic precondition (represented as a conjunction of symbolic clauses) such that the concrete execution traps if and only if the precondition is not satisfied. We require that the precondition of the source code implies the one of the target code. For compilation efficiency,

<sup>&</sup>lt;sup>8</sup> Synthetic nodes are "no-op" blocks inserted in the CFG in preprocessing of code motion [Knoop et al. 1992, §3.1].

<sup>&</sup>lt;sup>9</sup>In CompCert, certain actions, such as calls to external functions and volatile variable accesses, generate *events*. Global correctness amounts to preserving observable event sequences. In contrast, registers etc. are internal affairs of the program.

structural equivalence of expressions is reduced to pointer equality through hash-consing (i.e. memoizing expressions such that two structurally equal expressions are uniquely allocated in each compiler run). See Ex. 2.1.

Example 2.1 (Symbolic simulation of basic blocks). Consider two basic blocks B<sub>1</sub> and B<sub>2</sub>:

- $(B_1)$   $r_1 := r_1 + r_2$ ;  $r_3 := load[m, r_1]$ ;  $r_3 := r_1$ ;  $r_1 := r_1 + r_3$

- $(B_2)$   $r_3 := r_1 + r_2$ ;  $r_1 := r_3 + r_3$

Both  $B_1$  and  $B_2$  lead to the same parallel assignment:

$$r_1 := (r_1 + r_2) + (r_1 + r_2) \parallel r_3 := r_1 + r_2.$$

$B_1$  is preconditioned by OK(Read,  $r_1 + r_2$ )—meaning "the location at address  $r_1 + r_2$  is readable"—whereas  $B_2$  has a true precondition. Hence,  $B_2$  simulates  $B_1$ , but not the converse.

When applicable, this approach is very powerful, because it is simple, efficient and **does not require hints** from oracles (after the CFG is partitioned into blocks). A typical application is *instruction scheduling*, which reorders instructions to improve parallelism in the processor pipeline.

In their first work on instruction scheduling, [Six et al. 2020] only considered *basic blocks* (sequence of instructions with only one exit-point) of assembly code, and relied on a specific DSL (Domain-Specific Language) for symbolic execution. They later generalized their symbolic simulation validator to *superblocks* (sequence of instructions with intermediate conditional exit-points plus a final exit-point) to validate *superblock scheduling* [Six et al. 2022]. In some further improvements of their system, the source superblock may be transformed into an *extended block* (a sequence of trees without internal joins) which is not a superblock. They overcame the limitation of their symbolic simulation to superblocks with an intricate sequence of passes combining ad-hoc validators [Justus Fasse 2021].

In contrast, one of our contributions is to define our symbolic simulation validator on a very general syntax for blocks, even if its current applications only apply it to extended blocks. We have introduced an IR called BTL (Block Transfer Language) for representing CFGs of RTL blocks: it replaces the "RTLpath"—a decoration of RTL defining a block semantics—of [Six et al. 2022]. In contrast to RTLpath, BTL represents the control-flow within each block structurally (with an usual abstract syntax tree), instead of an explicit sub-CFG. This makes our symbolic simulation test both simpler and more efficient. <sup>10</sup> Proving the passes between RTL and the CFG of blocks becomes however less trivial: this leads us to generalize the notion of CFG morphism as sketched in §2.1.

2.2.2 Inter-Block Transformations. The simulation test sketched above is only applicable if the transformation preserves the semantics of each block. Indeed, it uses the equality of the source and target states (that is, the registers and memory) at the entry of each block as a simulation invariant. Inter-block transformations cannot be validated using this invariant for two reasons. Firstly, a transformation only needs to consider initial states at the block entry that are reachable by the program, whereas the above simulation test requires proving the preservation for any values of the registers and memory at the block entry. Secondly, the source and target states at the entry of the block dot not need to be equal. For instance, *Dead Code Elimination* (DCE) only maintains the equality of the live registers; some transformations use auxiliary registers, which hold meaningful values only in the target program.

To validate such global transformations, we generalize the *invariants* relating the source and target states at block entries. We progressively explain this idea, with the help of Fig. 2, providing a transformation on C pseudocode. <sup>11</sup> Both the source and the target code are CFGs of two (extended)

<sup>&</sup>lt;sup>10</sup>Our representation also slightly generalizes the "tree-based representation" of [Tristan and Leroy 2008, §5.1], because in ours, "sequences of trees" are blocks.

<sup>&</sup>lt;sup>11</sup>Implicitly, all arithmetic computations operate on unsigned long.

blocks, labeled by Entry (their entry-point) and Loop. The target is obtained after a combination of *Constant Propagation* (from a=7) and *Strength Reduction*: the multiplication originally within Loop is moved to Entry and reduced in Loop to an addition on a *fresh* register i\_a. The target also benefits from DCE, since register a and its assignment are eliminated.

To account for the differences between the source and target registers at the beginning of the block, we allow our symbolic expressions to mention the initial memory, the initial source registers (denoted with an "S" subscript) and the initial target registers (denoted with a "T" subscript). An invariant is then the conjunction of the equality of the source and target memories, a precondition expressed as a symbolic proposition, and equalities between some registers and symbolic expressions. The symbolic proposition and equalities are produced by our untrusted oracles for each block. Fig. 2 represents the equalities attached to each block of the target code, all preconditions are trivially true in this example.

#### Target CFG Entry: Source CFG // $i_T = i_S \wedge n_T = n_S$ s = 0;Entry: $i_a = i*7$ ; s = 0;goto Loop; a = 7;Loop: goto Loop; // $a_S = 7 \wedge i_T = i_S$ Loop: $// \ \land i\_a_T = i_S * 7$ if (i > n) $// \wedge n_T = n_S \wedge s_T = s_S$ return s; if (i > n)s += i\*a; return s; i += 3; += i\_a; goto Loop; i += 3; i\_a += 21; goto Loop;

Fig. 2. Simulation modulo invariants

The simulation modulo invariants is validated by sym-

bolic execution. For each block, we use the invariant at the entry to build an initial symbolic value for each register in the source and target programs. We then perform the symbolic execution of both the source and target blocks, and we compare their respective results through the invariant associated to every block exit. Let us detail this process for the Loop block of Fig. 2:

- For the source block, the symbolic execution starts from symbolic state "a := 7" itself deduced from the invariant at the block entry. It thus computes the following symbolic assignments at the "goto Loop" exit: "a :=  $7 \parallel i := i_S + 3 \parallel s := s_S + i_S * 7$ ".

- For the target block, the symbolic execution deduces from the invariant at block entry the following initial symbolic state: " $i := i_S \parallel i_a := i_S * 7 \parallel n := n_S \parallel s := s_S$ ". Then, it obtains for this same exit: " $i := i_S + 3 \parallel i_a := i_S * 7 + 21 \parallel n := n_S \parallel s := s_S + i_S * 7$ ".

- We then compare those symbolic values according to the invariant at the exit point (here again, the invariant at the Loop entry). After substituting the symbolic expressions of the source and target registers within this invariant, we check the following syntactic equalities: (1) 7 = 7, for equation  $a_S = 7$ ; (2)  $i_S + 3 = i_S + 3$  for  $i_T = i_S$ ; (3)  $i_S * 7 + 21 = (i_S + 3) * 7$  for  $i_A = i_S * 7$ ; (4)  $i_A = i_A * 7$ ; (5)  $i_A = i_A * 7$ ; (6)  $i_A = i_A * 7$ ; (7)  $i_A = i_A * 7$ ; (8)  $i_A = i_A * 7$ ; (9)  $i_A = i_A * 7$ ; (10)  $i_A = i_A * 7$ ; (11)  $i_A = i_A * 7$ ; (12)  $i_A = i_A * 7$ ; (23)  $i_A = i_A * 7$ ; (13)  $i_A = i_A * 7$ ; (14)  $i_A = i_A * 7$ ; (15)  $i_A = i_A * 7$ ; (15)  $i_A = i_A * 7$ ; (16)  $i_A = i_A * 7$ ; (17)  $i_A = i_A * 7$ ; (18)  $i_A = i_A * 7$ ; (19)  $i_A$

In order to prove equality (3), the symbolic execution is extended with rewriting rules normalizing affine expressions (see §6.3). Expressions on both sides are normalized into "21 +  $7 \cdot i_S$ ". The rewriting engine within symbolic execution is similar to the one of [Six et al. 2022]: it is simply defined more modularly. Now, each transformation may independently define its own rewriting rules, over a common underlying architecture.

In contrast to [Six et al. 2022], we do not use an ad-hoc validation of register liveness. While our oracles generate only invariants for live registers of the *target* program, the validation of this liveness analysis implicitly results from the preservation of equational invariants between source and target registers. An incorrect liveness analysis will result in an invariant that is invalid after substitution of the target registers, because it will still involve a target register not itself bound to a symbolic expression of source registers.

This implicit liveness validation is strictly more expressive than the explicit liveness validation of [Six et al. 2022]: we express each register "r" considered live by Six-et-al as an equation " $r_T = r_S$ ". This enabled us to port their superblock scheduling to BTL (and even improve it) as detailed in §4. Moreover, because they only validate a weak liveness analysis of the source program, their

```

\begin{split} f &:= (sig, \overrightarrow{r_{arg}}, cfg, pc_{entry}, \cdots) & ib ::= \mathsf{Bnop} \\ cfg &:= (pc \mapsto ib) & |\mathsf{Bop}(op, \overrightarrow{r_{arg}}, r_{dst}) \\ f &:= \mathsf{Bgoto}(pc) & \cdots \\ |\mathsf{Breturn}(\epsilon|r) & |\mathsf{Bcall}(sig, (r|id), \overrightarrow{r_{arg}}, r_{dst}, pc_{ret}) \\ &\cdots & |\mathsf{BF}(fi) \end{split}

```

Fig. 3. Syntax of BTL internal functions

```

If (x >= y) goto L;

x = z << 2;

return x;</pre>

Bseq(Bcond(_>=_, [x;y], BF(Bgoto(L)), Bnop),

Bseq(Bop(_<<2, [z], x),

BF(Breturn(x))))

```

Fig. 4. A superblock in C syntax and its BTL representation

```

\begin{array}{lll} sv ::= \operatorname{Sinput}((\operatorname{Src}|\operatorname{Trg}), r) & sfv ::= \operatorname{Sgoto}(pc) \\ & |\operatorname{Sop}(op, \overrightarrow{sv_{arg}}) & |\operatorname{Sreturn}(\epsilon|sv) \\ & \cdots & |\operatorname{Scall}(sig, (sv|id), \overrightarrow{sv_{arg}}, r_{dst}, pc_{ret}) \\ sm ::= \operatorname{Sinit} & \cdots \\ & |\operatorname{Sstore}(sm, chunk, addr, \overrightarrow{sv_{arg}}, sv_{src}) & ss ::= \operatorname{Scond}(cond, \overrightarrow{sv_{arg}}, ss_{then}, ss_{else}) \\ sis ::= (pre, (r \mapsto sv), sm) & |\operatorname{Sfinal}(sis, sfv)| \end{array}

```

Fig. 5. Syntax of the symbolic representations

framework is unable to validate any kind of DCE. In contrast, as shown on Fig. 2, ours validates some DCE "for free" (i.e. just from liveness equations as above).

#### 3 BTL AND ITS SYMBOLIC SIMULATION

The abstract syntax of BTL functions—given Fig. 3—is largely inspired by the one of RTL [Leroy 2009b]. Each (internal) function f is associated to a CFG cfg and an entry-point  $pc_{entry}$  in this CFG. Such a CFG is a map from labels pc to instruction blocks ib. Syntactically, a block ib may be composed of two sub-blocks, either sequentially with Bseq or through a kind of "if-then-else" written Bcond. A block may be reduced to a *basic instruction*: either Bnop that skips, or Bop that assigns the result of " $op(\overrightarrow{r_{arg}})$ " to register  $r_{dst}$ , or a few others. Last, it may also be a *final instruction* named fi that stops the current block execution, such as Bgoto that enters another block of label pc and Breturn that returns from the current function. In order to cope with CompCert simulation proofs, we impose that function call—written Bcall—is a final instruction, branching to  $pc_{ret}$  after the call. See Fig. 4 for an example in BTL syntax.

Similarly to RTL, the formal semantics of BTL programs and functions is a small-step operational semantics, where each step emits at most one single event. In contrast to RTL where a step runs at most one single instruction, each BTL block is run in one big-step. By construction, such a block big-step necessarily ends just after the RTL-style small-step of a final instruction. <sup>12</sup>

## 3.1 Symbolic Representations

Symbolic execution operates on symbolic representations of the dynamic values involved in the semantics of BTL. Fig. 5 presents the syntax of the main symbolic representations. They express the dynamic values as functions of the context, which fixes the values of the source and target registers at the entry of the block, represented by Sinput, and the common memory at the entry,

$<sup>^{12}</sup>$ If no final instruction is present, the block cannot step. See our source code online for the Coq definitions.

represented by Sinit. An internal symbolic state *sis* represents the pair of a register state and a memory, using a symbolic memory *sm* and by associating a symbolic value *sv* to each register. It also contains a symbolic proposition *pre* (such as the OK precondition of Ex. 2.1), so that the symbolic state does not represent any concrete state if this proposition is not satisfied. Our paper often writes internal symbolic states as parallel assignments such as the one of Ex. 2.1.

#### 3.2 Compact Invariants

A symbolic value represents the value of a register r after a sequence of concrete BTL assignments. As introduced in §2.2.2, our invariants themselves contains symbolic values. However, Ex. 2.1 illustrates on block  $(B_2)$  that the symbolic values may contain (exponential) term duplications w.r.t. a sequential representation. Because invariants are syntactically provided by the oracle under validation, we design a *compact* syntax which represents them as sequences of assignments from the source state. A first sequence, the *history invariant*  $\mathcal{H}$ , provides symbolic expressions for the source registers. A second sequence, the *gluing invariant*  $\mathcal{G}$ , provides symbolic expressions for the target registers. The preconditions of the operations of the sequences are used to define the precondition of the invariant.

Fig. 6 provides our abstract syntax for compact invariants. A compact invariant ci is a sequence of assignments of invariant values iv to registers  $r_{dst}$  together with a set of output registers. An invariant value iv may read a register r, optionally with a prefix "input" indicating that the input value is considered instead of the current

```

\begin{array}{lll} ci & ::= & (\overrightarrow{r_{dst}} := \overrightarrow{iv}, \overrightarrow{r_{output}}) \\ iv & ::= & \operatorname{input?} r \\ & | & \operatorname{Iop}(op, \overrightarrow{\operatorname{input?}} r) \\ & | & \operatorname{Iload}(chunk, addr, \overrightarrow{\operatorname{input?}} r) \end{array}

```

Fig. 6. Syntax of compact invariants

one (within the assignment sequence). It may also represent an operation involving current or input registers, or a load from the *current* memory. Initially, current and input registers are the registers of the source. In the rest of this document, we will note sequential invariants as "([a1:=v1;a2:=v2;...;aK:=vK],  $\{o1,o2,...,oN\}$ )", where the "ai:=vi" are the assignments and where the set of output registers is between braces.

```

Example 3.1. Interpreted as gluing invariants, the two following compact invariants "([a:=y[5]; z:=a+input x; x:=a+input z], {x,z,t})" and "([z:=y[5]; x:=z+input z; z:=z+input x], {x,z,t})" both represent the equations "x_T = y_S[5] + z_S \land z_T = y_S[5] + x_S \land t_T = t_S" with precondition "OK(Read, y[5])".

```

Given a symbolic internal state representing the source state, the simulation checker performs a hash-consed symbolic execution of a compact invariant to obtain symbolic representations of the right-hand side expressions of the invariant and its precondition. At the entry of the block, we complete the result of this execution using trivial equalities  $r_S = r_S$  or  $r_T = r_T$  to obtain a symbolic value for each register.

The symbolic validation exploits two properties of those invariants: (1) Given some invariants  $\mathcal{H}$  and  $\mathcal{G}$ , we build symbolic internal states representing any pair of concrete states related by those invariants and reflecting the properties they enforce. We start with an empty symbolic state representing trivially the source state (using  $r \mapsto r_S$  for the registers). We execute  $\mathcal{H}$  to obtain a new representation of the source state that enforces the equalities and the precondition of  $\mathcal{H}$ . Then we execute  $\mathcal{G}$  from this new symbolic state to obtain a state representing the target state. Finally, we refine the source symbolic state by adding the precondition of  $\mathcal{G}$ . (2) Given a pair of source and

<sup>&</sup>lt;sup>13</sup>The term "gluing invariant" is inspired by Abrial [1996]. Our "gluing invariants" have also similarities with "simulation invariants" of Rinard and Marino [1999], and our "history invariants" with their "standard invariants".

Fig. 7. Symbolic execution in CPS

target symbolic internal states, we check that an invariant  $\mathcal{H}$  (resp.  $\mathcal{G}$ ) holds by executing it from the source state and comparing the symbolic values obtained for the right-hand sides with those associated to the same register by the source (resp. target) symbolic states. We also check that the precondition of the invariant is implied by the precondition of the source symbolic state.

## 3.3 Symbolic Execution with Trace-Partitioning By Continuation-Passing

Our theory of symbolic execution improves upon Six et al. [2022]'s with mainly two features. First, as explained in §2.2.2, the oracle provides invariants that allow the validation of inter-block transformations. Second, BTL symbolic execution supports arbitrary nested sequences of "if-thenelse" instead of superblocks only. This required both a more general representation of the *symbolic states* generated by symbolic execution and a kind of trace-partitioning within it.

A symbolic state represents all possible block steps of given BTL block. Fig. 5 defines a *symbolic state ss* as a binary decision tree, where each branch represents one possible execution path of the block. A "Scond" node represents the choice between two branches. Leaves are "Sfinal(*sis*, *sfv*)" where *sis—a symbolic internal state—*represents the state of the program when it reaches the exit of the block, and *sfv—a symbolic final-value—*represents the final instruction of the exit (where registers have been substituted by their final symbolic values).

Fig. 7 sketches the Coq code of the symbolic execution. Here, sstate and sistate are respectively the types of symbolic state ss and symbolic internal state sis. Function set\_sreg updates the current sis by assigning a new symbolic value to register dst. The symbolic execution of the register list args into a symbolic value list is delegated to function lmap\_sv.

The symbolic execution—named <code>sexec\_rec</code>—computes over block ib recursively. The initial (internal) state is <code>sis</code>. The trace partitioning is here realized in Continuation Passing Style (CPS). Continuation k represents how symbolic execution should continue on updates of internal state. It is initialized as "<code>error\_sstate</code>", which returns a state with a false precondition, reflecting the fact that each BTL block step must reach a final instruction.

## 3.4 Symbolic Simulation Modulo Invariants

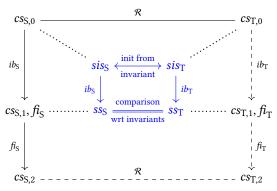

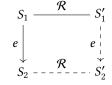

The blue subdiagram in Fig 8 represents the computations performed by our symbolic simulation validator. The surrounding diagram (in black color) represents its correctness proof wrt concrete executions. Hence, we deduce the lock-step forward simulation  $^{14}$  of the source BTL code by the target one from their simulation block-by-block, and check the latter by comparing the symbolic states produced by the symbolic execution of each block. Our simulation relation  $\mathcal R$  relates pairs of

<sup>&</sup>lt;sup>14</sup>Thanks to deterministic target languages, the correctness of CompCert's backend passes reduces to a *forward simulation* [Leroy 2009b].

states at the same program location, using the invariants provided by the oracle for this location. In the formal proof, we also need to relate the call stacks of the two programs (see Appendix A.1).

Since we prove a forward simulation, we consider a pair of source and target states  $cs_{S,0}$  and  $cs_{T,0}$  at the entry of the block and related by the invariant defined by the oracle for the block. We assume that the source program take a step to  $cs_{S,2}$ , and we have to prove that the target program can take a corresponding step to some state  $cs_{T,2}$  related to  $cs_{S,2}$ .

Because  $cs_{S,0}$  and  $cs_{T,0}$  are related by the invariant of the block, we can build from it two symbolic internal states  $sis_S$  and  $sis_T$  representing the source and target initial states. The validator perform the symbolic

Fig. 8. Simulation step using symbolic simulation

execution of the blocks to obtain two symbolic states  $ss_S$  and  $ss_T$  representing the outcomes of the executions of the blocks. It then performs a comparison of those two decision trees. It checks that they have the same structure with the same conditions. For each corresponding leaves, it checks that (1) the symbolic final values and symbolic memories are identical; (2) the symbolic precondition of the source outcome implies the one of the target; (3) the simulation relation is satisfied after an execution of the common final instruction. For this last condition, it checks the invariants associated to all the blocks the final instruction can jump to. In the case of a final value "Scall(sig, (sv|id),  $\overrightarrow{sv_{arg}}$ , o,  $pc_{ret}$ )", it also checks that those invariants do not constrain the memory and the output register o, possibly modified by the call: it only allows "liveness" equation  $o_T = o_S$ .

The step of the source block can be decomposed into an execution up to a final instruction  $fi_S$  followed by an execution of this final instruction. By the correctness of sexec,  $ss_S$  represents the state of the source program before the execution of  $fi_S$ . In particular, its precondition is satisfied. The comparison ensures that the precondition of  $ss_T$  is also satisfied, hence by the correctness of sexec, the target program can take a step-up to a final instruction  $fi_T$ . Since  $fi_S$  and  $fi_T$  are represented by the same symbolic final value, we can simulate the execution of  $fi_S$  by an execution of  $fi_T$  to a state  $cs_{T,2}$ . Because of the comparison performed between the symbolic states, the simulation relation holds between  $cs_{S,2}$  and  $cs_{T,2}$ .

Besides this block-to-block simulation, we also need to ensure that invariants at the CFG entry do not constrain any register, except by liveness equations. Indeed, in our intra-procedural verification, the value of parameters must be considered as unknown.

#### 3.5 Refinement with Hash-Consing and Normalized Rewriting

In our Coq development, the code in Fig. 7 specifies the symbolic state that the symbolic execution should produce modulo semantic equivalence. This specification is refined with normalized rewriting and hash-consing in the impure monad of Boulmé [2021]. Rewriting reduces comparisons (of symbolic values) modulo a set of equations to structural equalities [Kirchner and Kirchner 2014]. Hash-consing reduces these structural equalities to pointer equalities. Hence, §3.4 gives itself a specification of our validator which compares symbolic values using pointer equality of OCaml. Here, we adapt the technique of Six et al. [2022] with much more complex rewriting rules. See §6.3.

BTL may be annotated with results of verified static analyses. See Appendix A.3. These annotations are taken into account in the semantics and used to justify some rewritings. In particular, we

rely on a non-alias analysis to overcome our symbolic representation of the memory as a single variable (see Appendix B), and an interval analysis enables an integer promotion pass (see §6.5).

#### 3.6 Limitations of our Simulation Checker

Our simulation checker has two kinds of limitations: performance ones (impacting CompCert running times) and expressivity ones (restricting the class of simulations that can be validated).

Performance. While in theory, any piece of code without loops may be represented as a BTL block, in practice our symbolic execution performs a naive trace partitioning: it is thus exponential over the number of *internal joins* of the input block (i.e. such that two branches of a given block join at a point which is not a block entry). Because we currently only apply our checker to extended blocks, which, by definition, do not have such joins, this is not an issue. Furthermore, for blocks with a bounded number of internal joins, and without rewriting rules, our symbolic execution is linear in the size of invariants and blocks (see §8.3). In the general case, its cost depends on the normalization system. For example, for the normalization of affine forms (for SR), it is expected to be quadratic in the worst case. Lastly, the comparison of symbolic states costs  $O((l+t) \times e)$  where l (resp., t) is the maximal number, by execution path, of live-out registers (resp., trapping instructions) and e is the number of execution paths (coinciding with the number of exits for blocks without internal joins). Block selection is a way to finely control e, and thus checker performance.

Expressivity. The relative simplicity and efficiency of our checker comes at a price: its expressive power is limited. (1) Our invariants only support equations of the form "r = sv" but not the more general " $sv_1 = sv_2$ ": this limitation avoids the need of costly saturation techniques. (2) Our simulation checker performs no reasoning on conditions. It simply checks that the two symbolic states under comparison have the same binary decision tree structure, with syntactically equals conditions on nodes. Future works include supporting conditions within invariants with a more expressive comparison of decision trees and preconditioned rewriting rules. (3) Our invariants implicitly express that their trapping expressions are actually safe in the execution context. This forbids the target to anticipate traps with respect to the source. Avoiding this restriction would require prophecies [Abadi and Lamport 1991] ensuring that these traps will eventually be observed on the source before any subsequent observable event. Besides generalizing the semantics of our invariants, this would need introducing a notion of "decreasing variant" forbidding never-realized prophecies. Currently, we partly overcome this restriction with the help of CFG morphisms. See §5.1. (4) The invariants presented here require the source and target memories to be equal at BTL block boundaries. We can however generalize the invariants while keeping the formalism of §3.4. This enables for example validating the loop invariant code motion of a memory update after a loop.

#### 4 APPLICATION TO SUPERBLOCK SCHEDULING

In-order processor cores execute assembly instructions in their syntactic order. If one instruction computes a register used by the next one, then the core stalls until the value computed becomes available, which may take several clock cycles. Optimizing compilers thus reorder instructions to minimize stalling: e.g. prioritizing instructions with high latencies and impacting many other instructions. For example, the superblock scheduler of Six et al. [2022, §6] attempts to minimize the running times of the execution path covering the whole superblock, even if it may increase running times of early exiting paths, but without increasing register usage beyond the point where the subsequent register allocation would be forced to spill registers to memory. This scheduler is based on a solver that reorders the superblock without code duplication.

We ported the Six et al.'s superblock scheduler from RTLpath to BTL. We now explain, on a variant of their example [Six et al. 2022, Fig. 10], how the design of BTL makes the implementation

much easier. This example applies a *weak* form of *software pipelining*, that they call *if-lifting*, and targets ARM Cortex-A53 (AArch64), a dual-issue in-order processor with two ALUs. In Fig. 9, we optimize the top source C code by parallelizing computations between two successive iterations of the loop body. The left-hand side represents the BTL code of the loop body, after a loop-rotate and unroll-body (see Fig. 1). Hence, the "Loop" superblock (which is a loop body containing two iterations of the original loop) is scheduled as the BTL block represented on the right-hand side: the two floating-point computations of the first iteration (in violet color) have been moved below the intermediate exit in order to be interleaved with those of the second iteration. The scheduler predicts<sup>15</sup> that the target loop body will run in at most 22 cycles instead of 32 cycles for the original one (e.g. more than 30% gain of running time). However, preserving the semantics requires *register renamings* with fresh registers (in red color) and insertion of *compensation code* (in blue color) at the intermediate exit. Because of this insertion, the target block is an extended block.

This whole transformation is directly validated by our simulation checker, with gluing invariants reduced to a conjunction of liveness equations " $r_T = r_S$ ", over all registers r of the live sets given on the right-hand side (in yellow color). On the contrary, because RTLpath can only represent superblocks, validating this transformation with Six's design required an "intricate combination of passes" [Six et al. 2022, Footnote 10].

Our implementation of the oracle is also quite simple. First, register renamings are performed backward in a preliminary pass (we avoid forward renamings of [Six et al. 2022, §5.3] because they tend to pollute the superblock under scheduling with compensation renamings). Then, we invoke the scheduling solver on a *fake superblock*, with an empty live set on intermediate side exits. Last, we insert the necessary com-

```

double sumsq(double *x, unsigned long len) {

double s = 0.0;

for (unsigned long i=0; i<len; i++) s+=x[i]*x[i];

return s;

}</pre>

```

```

Loop: // live: x1, x2, x3, x4

Loop:

x7 = float64\Gamma x2+x3 << 31

x11 = float64[x2+x3<<3]

x6 = x7 *f x7

x8 = x3 + 1 1

x4 = x4 + f x6

if (x8 >= lu x1) {

x10= x11 *f x11

x3 = x3 + 1 1

if (x3 >= lu x1)

x9 = x4 + f x10

goto Exit

x4 = x9

// start second iteration

goto Exit // live: x4

x7 = float64[x2+x3<<3]

x6 = x7 *f x7

x3 = x8 + 1 1

x4 = x4 + f x6

x7 = float64[x2+x8<<3]

x3 = x3 + 1 1

x10 = x11 *f x11

if (x3 >= lu x1)

x6 = x7 *f x7

goto Exit

x9 = x4 + f x10

goto Loop

x4 = x9 + f x6

if (x3 >= lu x1)

goto Exit // live: x4

Exit:

return x4

goto Loop

```

Fig. 9. Interleaving of unrolled loop-bodies on AArch64.

pensation code in the side exits, following Justus Fasse [2021]'s heuristic. We then compare the makespan (total estimated time) of this scheduling to the standard one (computed on the *original superblock* with correct liveness and without compensation code). If the ratio of the size of the compensation code over the makespan gain is greater than a given threshold, we keep the standard one instead. Hence, compiler users may control this scheduling heuristic by tuning the threshold on the command line.

We have also refined this formally verified scheduler with reordering of non-interfering load or store w.r.t store for some non-alias analyses (see Appendix B). Yet, we measured a gain only on a few benchmarks.

<sup>&</sup>lt;sup>15</sup>This estimation occurs at an abstract level and thus cannot be precise. First, the subsequent register allocation could introduce unexpected spills. Second, this estimation assumes that there is no cache miss. Third, the pipeline model is inexact.

#### APPLICATION TO LAZY CODE MOTION

Code motion consists in anticipating some instructions in order to remove redundant computations. For example, by data-flow analysis, we may detect expressions remaining constant within a loop and anticipate their computation before the loop: this is LICM (Loop Invariant Code Motion). However, if done carelessly, this transformation may anticipate a loop-invariant expression that traps (e.g. a memory load from a potentially invalid pointer, or a division operation on some architectures), whereas this computation is unreachable in the original loop. Safe elimination of such computations—that are redundant on some but not all program paths—is called PRE (Partial Redundancy Elimination). According to Bodík et al. [1998], "to achieve a complete PRE, control flow restructuring must be applied. However, the resulting code duplication may cause code size explosion." They propose to guide these CFG restructuring with path-profiling and data-flow frequency analysis.

Lazy Code Motion [Knoop et al. 1995, 1992] performs safe and optimal PRE without CFG unrolling, while limiting the register pressure induced by code motion. Instructions are safely anticipated but not earlier than the minimum necessary to reach computational optimality (i.e. with a minimal average running time for PRE without CFG unrolling). In other words, among computationally optimal code motions, LCM selects those that minimize register pressure. Below, we present

```

double approx(double *a) {

double r = 2;

2

if (a[0] < 2) return 2;</pre>

3

while (r < a[1])

if (r >= a[2]) r -= a[0];

5

else r *= 7;

6

7

}

8

```

Fig. 10. Four candidates for LICM

our formally verified PRE within the CompCert compiler: §5.1 combines LCM with simple CFG unrollings on the example in Fig. 10; §5.2 details the validation of our LCM oracle on this example.

## Performing LICM by PRE on an Example

Figure 11 presents an extract of the RISC-V code produced by CompCert with CSE3 of [Monniaux and Six 2021, 2022] activated for the source C code in Fig. 10. The computation of a[0] has been factorized in f3 register over the whole program. But, computations (in violet color) of a[1] in f0 and a[2] in f2, and loading of floating-point 7 in f1 is performed at each iteration of the loop of label .L102.

In contrast, in Fig. 12 (the four first lines are omitted because identical), after unrolling the first iteration (see Fig. 1) our LCM moves all these computations before the loop, starting now at label .L106. Remark that if the condition of the loop is initially false, a[2] is not computed by the original loop, but may trap if the address is invalid. Thus, simply anticipating the computation of a[2] before the loop is incorrect: unrolling the first iteration gives a simple workaround.

```

f1d

f3,0(x10)

... # Same prolog

fld

f10,.L100,x31

fld

f0,8(x10)

x31,f3,f10

flt.d

x31,f10,f0

flt.d

x31,x0,.L101

x31,x0,.L101

bea

bne

.L102: #

Loop Entry

f1d

f2,16(x10)

fld

f0,8(x10)

fle.d

x31,f2,f10

x31,f10,f0

x31,x0,.L103

flt.d

bne

fld

f10,.L105,x31

x31,x0,.L101

bea

f1d

f2,16(x10)

.L102

i

fle.d

x31,f2,f10

.L103:

fsub.d f10, f10, f3

bne

x31,x0,.L103

f1d

f1,.L104,x31

.L102:

fmul.d f10, f10, f1

fld

f1,.L104,x31

.L106: # Loop Entry

j

.L102

flt.d x31,f10,f0

.L103:

fsub.d f10, f10, f3

beq

x31,x0,.L101

.L102

x31,f2,f10

i

fle.d

.L104: ...# 7.0 in hexa

bne

x31,x0,.L107

.L100: ...# 2.0 in hexa

fmul.d f10.f10.f1

i

.L106

.L107:

fsub.d f10,f10,f3

j

.L106

.L105: ...# 14.0 in hexa

.L104: ...# 7.0 in hexa

```

However, it may not suffice. For example, in Fig. 10, if the test on line 3 was omitted, then simply

Fig. 12. Unroll+LCM

unrolling the first iteration would not suffice to allow a[0] to be moved before the loop. Indeed, if r < a[2] at the first iteration, then a[0] is not computed and may still trap afterward. Actually,

Fig. 11. CSE3 alone

following [Bodík et al. 1998], we may find an unrolling (validated by Six's CFG morphism checker) that enables it. But this would cost even more code duplications than those of Fig. 12.

Let us now explain why LCM is more powerful than CSE. Applying CSE3 after unrolling produces almost the same code as the one of Fig. 12 except that the load of floating-point 7 is not factorized. <sup>16</sup> This is due to the fact that some execution path of the first iteration does not load floating-point 7 into f1. Indeed, CSE3 can only eliminate computations that are available on all incoming paths. Thus, CSE3 only performs some *FRE* (*Full Redundancy Elimination*): it misses FRE if the same value is available on different incoming paths, but in different registers. In contrast, LCM is able to perform any FRE and even non-trapping PRE *without unrolling*. On Fig. 10 example, the load of floating-point 7 is anticipated even without any loop unrolling. In the original version of [Knoop et al. 1995], LCM also safely moves a[1] out of the loop without any loop transformation: this is a FRE, since a[1] is present in the condition of the loop, which is at least run once. Nevertheless, due to the current design of our simulation checker (see §3.6), anticipating trapping code w.r.t. the original program does not pass validation: our LCM can only eliminate a[1] within the loop, after at least a loop-rotation (see Fig. 1). This is not an issue on this very simple example: after applying our CFG minimization, we still finally achieve the FRE of a[1] without any code duplication.

## 5.2 Formally Validated LCM

Code motion moves computations from one block to another, and is thus global over the CFG. Figure 2 illustrates how invariants propagate information between blocks. Our simulation modulo invariants also validates our LCM, as now detailed on the previous example.

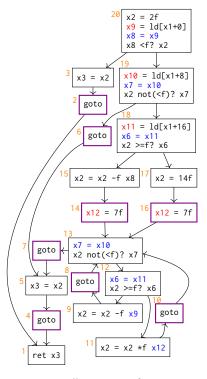

Our LCM oracle optimizes a BTL CFG of basic blocks. The CFG of the example is represented in Fig. 13, where each node is identified by a unique number (in yellow), and where synthetic nodes (explained in Footnote 8) are denoted with a violet border. The four candidates detected by the oracle have been inserted at their optimal points, by assigning them to a fresh variable (in red).

For instance, the load of floating-point 7 illustrates this "lazy" behavior of LCM as it is inserted in two different blocks (14 and 16) to minimize the live range. The calculation is therefore duplicated on two branches, and both chosen blocks are the last possible ones before the loop. However, this code duplication does not appear in the final assembly code of Fig. 12, because it is factorized by our subsequent CFG minimization pass. In Fig. 13, it also appears that some fresh variables, such as x10 and x11, are duplicated through a compensation move (in blue). This behavior will be explained §6. Note that these pseudo-register duplications do not increase the actual live range since they will be removed by the subsequent register allocator.

Fig. 13. Full BTL CFG of Fig. 12

<sup>&</sup>lt;sup>16</sup>The original CSE of CompCert does not even eliminate the redundant "a[0]". This contrast with gcc -01 (version 9.4.0) which performs a PRE with slightly less code duplications than ours on this example. However, the original CSE of CompCert factorizes the load of floating-point 2 into register "f10". Such a "trivial" CSE is required by the LCM algorithm: block-based LCM cannot exempt from, at least, an intra-block CSE. See [Knoop et al. 1995].

Now let us detail how the invariants are generated by our LCM oracle before sending the whole result to the verifier. Our LCM only requires gluing invariants: thus, history invariants remain trivially empty here. Invariants are generated in the sequential representation of §3.2. As explained at the end of §3.4, the invariant of the entry block (here block 20) is always reduced to a liveness set. Besides liveness sets, invariants are updated for each candidate just after they appear in code: at the entry of block 19, we have " $([x9:=ld[x1+0]], \{x1,x2,x8,x9\})$ " to remember the load, and because these four variables are live. The second (resp. third) load is added to the gluing invariant at block 18 (resp. blocks 15 and 17). Thus, for all blocks with a label in 14...17, the invariant contains the same sequence of assignments (but the sets of live variables are different): "x9:=ld[x1+0]; x10:=ld[x1+8]; x11:=ld[x1+16]". From block 13 and up to block 8 (included), we append to this list the assignment "x12:=7f". Finally, blocks 1 to 7 only contain pure-liveness invariants, as the verification need not remember the values of candidates anymore.

Example 5.1. Validating symbolic simulation for block 14 (with the validator described in §3.4).  $G(14) = ([x9:=ld[x1+0]; x10:=ld[x1+8]; x11:=ld[x1+16]], \{x2,x9,x10,x11\})$  This leads to the following initial states:

```

\begin{aligned} \textit{sis}_S &= (\textit{pre}, \epsilon) \\ \textit{sis}_T &= (\textit{pre}, x2 \coloneqq x2_S \| x9 \coloneqq 1d_S[x1_S + \emptyset] \| x1\emptyset \coloneqq 1d_S[x1_S + 8] \| x11 \coloneqq 1d_S[x1_S + 16]) \\ \text{where } \textit{pre} &= \mathsf{OK}(\mathsf{Read}, 1d_S[x1_S + \emptyset]) \land \mathsf{OK}(\mathsf{Read}, 1d_S[x1_S + 8]) \land \mathsf{OK}(\mathsf{Read}, 1d_S[x1_S + 16]) \\ \text{After the symbolic execution of the blocks:} \end{aligned}

```

$ib_s = \mathsf{BF}(\mathsf{Bgoto}(13))$  and  $ib_t = \mathsf{Bseq}(\mathsf{Bop}(7\mathsf{f},[],\mathsf{x}12),\mathsf{BF}(\mathsf{Bgoto}(13)))$

we obtain:

```

\begin{aligned} ss_S &= \texttt{Sfinal}(sis_s, \texttt{Sgoto(13)}) \\ ss_T &= \texttt{Sfinal}((\textit{pre}, \texttt{x2} \coloneqq \texttt{x2}_S || \texttt{x9} \coloneqq \texttt{ld}_S [\texttt{x1}_S + \texttt{0}] || \dots || \texttt{x12} \coloneqq \texttt{7f}), \texttt{Sgoto(13)}) \end{aligned}

```

The two decision trees have the same structure and their unique leaves match. In particular, the gluing invariant of the successor block 13 is satisfied:

```

\mathcal{G}(13) = ([x9:=ld[x1+0]; x10:=ld[x1+8]; x11:=ld[x1+16]; x12:=7f], \{x2,x9,x10,x11,x12\}) For instance, the right-hand side expression for x9 evaluates to ld_S[x1_S+0] in ss_S, which matches the value of x9 in ss_T.

```

We further detail in §10 the comparison of our formally verified LCM w.r.t. [Monniaux and Six 2021, 2022; Tristan and Leroy 2009].

#### 6 APPLICATION TO LAZY STRENGTH REDUCTION

Strength-reduction (SR) consists in replacing (sequences of) computations by semantically equivalent—but more efficient—ones. Simple forms of strength reduction, for instance replacing a multiplication by a power of two with a left shift, are already implemented in CompCert. Here we tackle a much more advanced approach: Lazy Strength Reduction [Knoop et al. 1993], a generalization of LCM that reduces computations while moving them. For instance, an expensive multipli-

```

slli x6,x11,3

add x6,x10,x6

ld x6,0(x6)

```

Fig. 14. AArch64 (top) vs. RISC-V (bottom) addressing

cation  $C \times i$  within a loop with loop index i may be replaced by accumulation  $(C \times (i+1) = C \times i + C)$ .

#### 6.1 Motivations for RISC-V

Some architectures provide instructions or addressing modes for commonly found patterns, such as array addressing. In truly reduced instructions sets, such as RISC-V, these patterns instead result in a multi-cycle sequence of instructions, amenable to SR. Figure 14 shows the single AArch64 load generated for array access "x = a[i]" (with an addressing mode that shifts an index by three bits

and adds it to a base address) compared to the succession of RISC-V instructions that shift, add, then load. The lack of SR for such sequences may explain why CompCert performs more poorly compared to GCC on RISC-V than on other architectures.

### 6.2 SR on a Realistic Example

We specialized and extended our LCM algorithm in order to strength-reduce multiplicative and additive computations on the RISC-V (64 bits) backend. Our contribution generalizes the LSR algorithm of [Knoop et al. 1993] to operate over basic blocks, and is also validated via our general-purpose framework. Note that for LSR, both types of invariants are exploited, because the simulation have to remember the value of constants when verifying the correctness of newly inserted instructions. Since the feasibility of SR for a given candidate is conditioned by the existing dependencies on its variables, we apply a pass of *move forwarding* in the first place. The latter removes read-after-write dependencies coming from move instructions, that might be obstacles to the LSR.

The C code of Figure 15 multiplies a slice [i, n) of a vector x by a scalar 1, and contains two candidates to be reduced. Indeed, in addition to the product itself, the addressing computation to access x[i] can be rewritten as well. The original and optimized BTL codes are set side-by-side in Figure 16. The yellow comment on the left gives the correspondence between registers and variables from the source C program. The multiplication "1 \* i" corresponds to "x1 \*1 x4" in both codes, and, on the left code, the sequence "x8 = x1 << 13;  $x6 = x3 + 1 \times 8$ " calculates into x6 the address of x[i]. Synthetic nodes are still denoted in violet, fresh variables in red, and compensation code in blue. We omitted blocks 14 and 1 in the optimized BTL code, as they are identical.

Our oracle significantly improves the original LSR algorithm of Knoop et al. [1993] by (1) *sorting* (and processing) candidates according to their topological order of appearance<sup>17</sup>; (2) *substituting*

```

void init_slice(long *x, long n, long i) {

long l = 10;

for(; i < n; i++) x[i] = l * i;

}

</pre>

```

Fig. 15. Two candidates for LSR

```

Variables:

\mathcal{H}: ([x4:=10], {x4})

G: ([], \{x1, x2, x3, x4\})

x1 = i; x2 = n;

12: x9 = x1 <<1 3

x3 = x; x4 = 1

x10 = x3 + 1 x9

14: x4 = 10L

x11 = x1 *1 x4

goto 12

goto 11

12: goto 11

\mathcal{H}: ([x4:=10], {x4})

G: ([x9:=x1<<3; x10:=x3+x9;

11: if (x1 >= 1s x2)

x11 := x1 * x4],

goto 1

{x1,x2,x3,x10,x11})

goto 9

11: if (x1 >=1s x2) goto 1

goto 9

9: x8 = x1 << 1 3

x6 = x3 + 1 x8

\mathcal{H}\!\!\!\&\mathcal{G}\!\!\!: see block 11

x7 = x1 *1 x4

9: int64[x10 + 0] = x11

int64[x6 + 0] = x7

x10 = x10 + 1 8

x1 = x1 + 11

x11 = x11 + 1 10

goto 3

x1 = x1 + 11

goto 3

3: goto 11

\mathcal{H}\&\mathcal{G}\colon see block 11

1: return

3: goto 11

```

Fig. 16. Original (left) and reduced (right) BTL

freshly introduced variables; (3) inferring the history ( $\mathcal{H}$ ) and gluing ( $\mathcal{G}$ ) invariants required for validation (in the Figure, those for block 9 and 3 have been omitted, because they are identical to those of block 11). Applied to our example after moving the left shift instruction from block 9 to block 12, the old destination (here x8) is replaced in the instructions following the original position of the candidate (in block 9) with the newly allocated variable (x9)<sup>18</sup>. This enables then to also strength-reduce the addition originally assigning to x6 in block 9 (it is moved to block 12 as the assignment to x10). Note that the substitution of x8 by x9 is fundamental here: if we had simply

$<sup>^{17}</sup>$ Sorting is made possible thanks to a prior post-order CFG renumbering, which also accelerates fixed point calculations.  $^{18}$ When the original variable is live in successors or read in the final instruction, the oracle inserts a move before the last read (or the end of the block) to compensate.

$$c \cdot (v_1 + v_2) = (c \cdot v_1) + (c \cdot v_2) \qquad c_1 \cdot (c_2 \cdot v) = (c_1 c_2) \cdot v \qquad c_1 \cdot c_2 = c_1 c_2$$

$$v_1 + v_2 = v_2 + v_1 \qquad (v_1 + v_2) + v_3 = v_1 + (v_2 + v_3) \qquad 0 + (v_1 + v_2) = v_1 + v_2 \qquad 0 + (c \cdot v) = c \cdot v$$

$$(c_1 \cdot v) + (c_2 \cdot v) = (c_1 + c_2) \cdot v \qquad (c \cdot v) + v = (c + 1) \cdot v \qquad v + v = 2 \cdot v$$

Fig. 17. Affine arithmetic of CompCert 64-bit integer operators on values

$$0 + v = v$$

$0 \cdot v = 0$   $1 \cdot v = v$   $(v + v) - v = v + (v - v)$

Fig. 18. Examples of invalid equalities for CompCert 64-bit integer operators

$$\pi ::= v \mid c \cdot v \qquad \qquad \phi ::= v \mid c + \Sigma_{i=1}^n \pi_i \quad \text{where } n \geq 0 \text{ and } (\pi_i)_{i \geq 1} \text{ is strictly increasing}$$

Fig. 19. Representation of our affine forms

inserted a move directly in place of the shift instruction, the data-flow analysis over the addition would have been blocked because of the write access to one of the arguments within the block. The multiplication originally in block 9 is moved out as in the standard way of Knoop et al. [1993].

Of course, it is necessary to update the registers of all these anticipated computations as the x1 argument is incremented inside the loop. To handle this, we keep a map from registers to affine forms which is updated during the candidates' detection phase. For example, the left shift operation associates x9 (formerly x8) to affine form "8 · x1" (knowing that  $x \ll n = 2^n \cdot x$ ). When the subsequent addition is selected as a candidate, a new affine form for x10 (formerly x6) is created, and by substitution of existing affine forms, its value is "x3 + 8 · x1". The normalization of affine forms in the oracle follows the theory given §6.3.

Finally, every affine form "injured" within the loop needs to be incremented (resp. decremented) by the product of the constant factor—within the form—of the concerned variable by its increment (resp. decrement) step in the "injuring" operation (e.g. the loop induction variable). In this specific example, incrementing x1 by one corresponds to increment the affine forms of x9 and x10 by 8. Thus, the oracle inserts assignments "x9 = x9 +1 8" and "x10 = x10 +1 8" in the loop, before the injuring operation. The exact same method applies to the affine form " $10 \cdot x1$ " associated to x11 (formerly x7).

For the sake of simplicity, this updating phase of our LSR oracle does not track whether the x9 variable is read afterward (either in the current block or in a successor). At the end, after having updated the liveness information to complete the invariant mapping with a set of "output" variables, the LSR oracle eliminates the dead assignments previously generated through an untrusted DCE pass, local to the block. In this example, the update "x9 = x9 + 18" is safely removed.

## 6.3 Overview of our Formally Verified Rewriting on (Pseudo) Affine Forms

Equational Theory. Our SR is validated in the variant of affine arithmetic given in Fig. 17, where c represents a 64-bit integer constant and v is a CompCert value. Actually, we consider this theory extended with specific operators such as  $v \ll c = 2^c \cdot v$ . However, note that some usual equations—such as those given in Fig. 18—do not hold. For example, if one of their argument is not a long integer or not a pointer—e.g. a float—64-bit integer operations return the absorbing Vundef value. <sup>19</sup> Moreover, operation "+" also performs pointer arithmetic in the abstract CompCert model of pointers (and our LSR leverages this opportunity). In this model, on a 64-bit architecture, if v is a pointer, then

<sup>&</sup>lt;sup>19</sup>Vundef represents an undefined value (e.g. of an uninitialized register) that is not a failure unless it is observable.

$v+v' \neq V$  undef if and only if v' is a 64-bit integer (in this case, v' is seen as a relative offset w.r.t v). And  $c \cdot v = V$  undef if v is a pointer. This explains why we never identify v and v0. But, if v0 is a pointer, then v0 + v0 = V undef and we still have v1 + v2 = v3.

Normal Forms. Since our symbolic values are evaluated to CompCert values (for a given block execution context), Fig. 17 also induces semantic equalities about symbolic values. As noticed in §3.5, normalized rewriting (when applicable) reduces such semantic equalities to structural equalities. Our representation of normal (i.e. canonical) forms is given in Fig. 19, where v represents now a variable (representing itself a symbolic value). Due to the commutativity of "+", normal forms depend on a total order over variables. Let us assume such an order. Because  $1 \cdot v$  may not be v, we introduce a notion of pseudo-product, written  $\pi$  (see Fig. 19). We then lift the total order over variables to a total preorder over pseudo-products. We then define a normal form, written  $\phi$ , as either a variable v or as the sum of a scalar v (possibly null) with a strictly increasing sequence (possibly empty) of pseudo-products (see Fig. 19). Last, the affine normalization is mainly reduced to two operations "v0" and "v1" (detailed in §6.4 below) preserving normal forms by applying Fig. 17 equations.

Implementation. Following the principles described in Six et al. [2022, §7.6], rewritings are handled during both symbolic executions of source and target blocks: we apply a normalization procedure to every right hand-side of an assignment. Its formal correctness expresses that given a symbolic value  $sv_1$ , it returns a symbolic value  $sv_2$  such that for all register and memory states, if evaluation of  $sv_1$  does not fail, then  $sv_2$  evaluates to the same value as  $sv_1$ . Its implementation depends on the architecture. Currently, our affine normalization procedure is only implemented for RISC-V. Moreover, our framework has several—potentially overlapping—sets of rewriting rules, so each instantiation of the symbolic execution is parametrized with one of these sets: the scheduling pass does not need any rule, while the SR is configured with our affine normalization procedure. Selecting rules according to oracles avoids slowing down the verifier with useless rewritings.

Our affine normalization needs to integrate affine forms with symbolic values that do not represent pure affine computations. In particular, affine variables in Fig. 19 actually reify symbolic values whose root is not an affine computation (i.e. neither a 64-bit immediate, nor a "-", nor a "+"). In practice, we do not introduce explicit affine variables, but rather define a total order on the reified symbolic values. Thanks to hash-consing, each symbolic value stores in its root an integer that is expected to uniquely identify it [Boulmé 2021, §3.3.2]. This identifier gives a simple and efficient total order over symbolic values that we do not even need to prove correct. Similarly to [Boulmé 2021; Six et al. 2022], the correctness of our normalization modulo hash-consing is only derived from a sound Coq model of OCaml pointer equality.<sup>21</sup>

To facilitate the proof of recursive operations over affine forms and future extensions, we extend the representation sv of symbolic values (sketched Fig. 5) with a dedicated constructor, written "Sfoldr(op,  $\overrightarrow{sv_i}$ ,  $sv_0$ )", and semantically equivalent to "Sop(op, [ $sv_0$ , Sop(op, [ $sv_1$ , . . .])])". This enables us to represent affine forms written " $c + \Sigma \overrightarrow{\pi}$ " in Fig. 19 as "Sfoldr(+,  $\overrightarrow{\pi}$ , c)" in our implementation, as explained just below.

#### 6.4 Formally Verified Normalization over our (Pseudo) Affine Forms

In order to normalize an affine operation " $c \cdot sv$ " or " $sv_1 + sv_2$ ", we first define a function  $\mathcal{A}$ , which maps any symbolic value sv to an affine form and satisfying the equations below (where " $[\![.]\!]$ " is the

<sup>&</sup>lt;sup>20</sup>Last, if v and v' are two pointers in the same block, then v-v' computes their relative offset. Thus, if v is a pointer, then v+(v-v)=v but (v+v)-v=v undef. This lack of associativity of operator "-" within sums explains why it is not yet supported in our LSR.

<sup>&</sup>lt;sup>21</sup>A bug in the hash-consing mechanism makes—at worse—the verifier fail to prove some expected equalities.

evaluation function from symbolic to concrete values).

$$\llbracket c \cdot sv \rrbracket = \llbracket c \cdot \mathcal{A}(sv) \rrbracket \qquad \qquad \llbracket sv_1 + sv_2 \rrbracket = \llbracket \mathcal{A}(sv_1) + \mathcal{A}(sv_2) \rrbracket$$

In other words, within the context of an affine operation, the normal forms returned by  $\mathcal{A}$  preserve the semantics. <sup>22</sup> In practice, since the normalization is applied after each assignment (see §6.3),  $\mathcal{A}$  only needs to perform a simple case analysis on the root of its argument. It is simply defined by:

$$\mathcal{A}(sv) = \begin{cases} sv & \text{if } sv \text{ matches } \mathsf{Sfoldr}(+,\_,\_) \\ \mathsf{Sfoldr}(+,[],c) & \text{if } sv \text{ matches } \mathsf{Sop}(c,[]) \text{ where } c \text{ is a } 64\text{-bit integer} \\ \mathsf{Sfoldr}(+,[sv],0) & \text{otherwise} \end{cases}$$

Then, the normalization of " $c \cdot \mathcal{A}(sv)$ " (resp. " $\mathcal{A}(sv_1) + \mathcal{A}(sv_2)$ ") reduces to a computation of the form " $c \cdot \mathsf{Sfoldr}(+, \overrightarrow{\pi}, c_0)$ " (resp. " $\mathsf{Sfoldr}(+, \overrightarrow{\pi_1}, c_1) + \mathsf{Sfoldr}(+, \overrightarrow{\pi_2}, c_2)$ ").

The computation of " $c \cdot \text{Sfoldr}(+, \vec{\pi}, c_0)$ " returns "Sfoldr $(+, c \cdot \vec{\pi}, c_0)$ " where " $c \cdot \vec{\pi}$ " is an instance of a "list-map" operation over pseudo-product list  $\vec{\pi}$  (and is verified by applying the three equalities at the top line in Fig. 17).

The computation of "Sfoldr(+,  $\overrightarrow{\pi_1}$ ,  $c_1$ ) + Sfoldr(+,  $\overrightarrow{\pi_2}$ ,  $c_2$ )" returns "Sfoldr(+,  $\overrightarrow{\pi_1}$  +  $\overrightarrow{\pi_2}$ ,  $c_1$  +  $c_2$ )", where " $\overrightarrow{\pi_1}$  +  $\overrightarrow{\pi_2}$ " is very similar to the merge of sorted lists  $\overrightarrow{\pi_1}$  and  $\overrightarrow{\pi_2}$  for the pseudo-product preorder, except that when two compared pseudo-products are equivalent for the preorder, they are themselves merged by an operation described just below. The equivalence test on pseudo-products, described in Figure 20, uses pointer equality "==" to validate that two pseudo-products can be merged. In Figure 17, the three equations on the bottom line (from left to right) correspond to the three cases of *equiv* (from top to bottom). Each of this case in *equiv* is thus associated to a rewrite rule that merge the pseudo-products by applying the corresponding equation from left to right. For instance, supposing we have  $equiv(\pi_1, \pi_2) = true$  for the third case, then the merge of this two pseudo-products is  $2 \cdot \pi_1$ , because then we know that  $\pi_1 = \pi_2$  and that  $\pi_1$  is a "reified" symbolic value (i.e. not having an affine computation at its root).

$$equiv(\pi_1, \pi_2) \stackrel{\text{def}}{=} \begin{cases} sv_1' == sv_2' & \text{if } (\pi_1, \pi_2) \text{ matches } (c_1 \cdot sv_1', c_2 \cdot sv_2') \\ sv == sv' & \text{else if } (\pi_1, \pi_2) \text{ matches } (sv, c \cdot sv') \text{ or } (c \cdot sv, sv') \\ \pi_1 == \pi_2 & \text{otherwise} \end{cases}$$

Fig. 20. Testing the equivalence induced by the preorder over pseudo-products

## 6.5 Strengthening our Strength-Reduction with a Prior Integer Promotion

Currently, our formally-verified strength-reduction is still embryonic. Its scope is limited to affine arithmetic on long (signed and unsigned ones) for RISC-V 64 bits architectures. We now sketch how we mitigate this limitation (Appendix A.2 describes other obstacles to generalizing our SR).

On 64-bit architectures, a 32-bit index (int) must be cast to 64 bits before being scaled and added to the base address. Due to overflows, it can be wrong to strength-reduce the scaling. We overcame this limitation of our SR by combining a preliminary pass that combines two techniques: (1) a formally verified interval analysis able to justify the absence of overflow—for instance, under a loop condition of the form "i < n" for some n, then we know that the increment of i cannot overflow<sup>23</sup> (2) the use of the intervals found by this static analysis within an oracle in order to validate the

<sup>&</sup>lt;sup>22</sup>Because of the invalid equations in Fig. 18, it would be too strong to simply require " $[\![\mathcal{A}(sv)]\!] = [\![sv]\!]$ ".

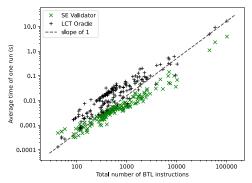

<sup>&</sup>lt;sup>23</sup>In C, overflow has undefined behavior in signed arithmetic, so if the loop index is signed (int), as it often is, we could simply assume overflow does not occur. Signedness information is however not available at that stage in CompCert (this is explained in the penultimate paragraph of §10).