## Methodology for active Junction profile extraction in thin film FD-SOI enabling performance driver identification in 500°C devices for 3D sequential integration

Tadeu Mota Frutuoso, Xavier Garros, Perrine Batude, Laurent Brunet, Joris Lacord, Benoit Sklenard, Valérie Lapras, Claire Fenouillet-Beranger, Mickael Ribotta, Alexandre Magalhaes-Lucas, et al.

## ▶ To cite this version:

Tadeu Mota Frutuoso, Xavier Garros, Perrine Batude, Laurent Brunet, Joris Lacord, et al.. Methodology for active Junction profile extraction in thin film FD-SOI enabling performance driver identification in 500°C devices for 3D sequential integration. VLSI 2022 - 2022 IEEE Symposium on VLSI Technology and Circuits, Jun 2022, Honolulu, United States. pp.332-333, 10.1109/VLSITechnologyandCir46769.2022.9830504 . hal-04069091

## HAL Id: hal-04069091 https://hal.science/hal-04069091v1

Submitted on 10 Apr 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Methodology for Active Junction Profile Extraction in thin film FD-SOI Enabling performance driver identification in 500°C devices for 3D sequential integration

T. Mota Frutuoso, X. Garros, P. Batude, L. Brunet, J. Lacord, B. Sklenard, V. Lapras, C. Fenouillet-Béranger, M. Ribotta, A. Magalhaes-Lucas, J. Kanyandekwe, R. Kies, G. Romano, E. Catapano, M. Casse, J. Lugo-Alvarez, P. Ferrari\*, F. Gaillard CEA, Leti, Minatec Campus, and University Grenoble Alpes, 17 rue des Martyrs, 38054 Grenoble, France \*Univ. Grenoble Alpes, Grenoble INP, RFIC-Lab, 38000 Grenoble, France tadeu.motafrutuoso@cea.fr

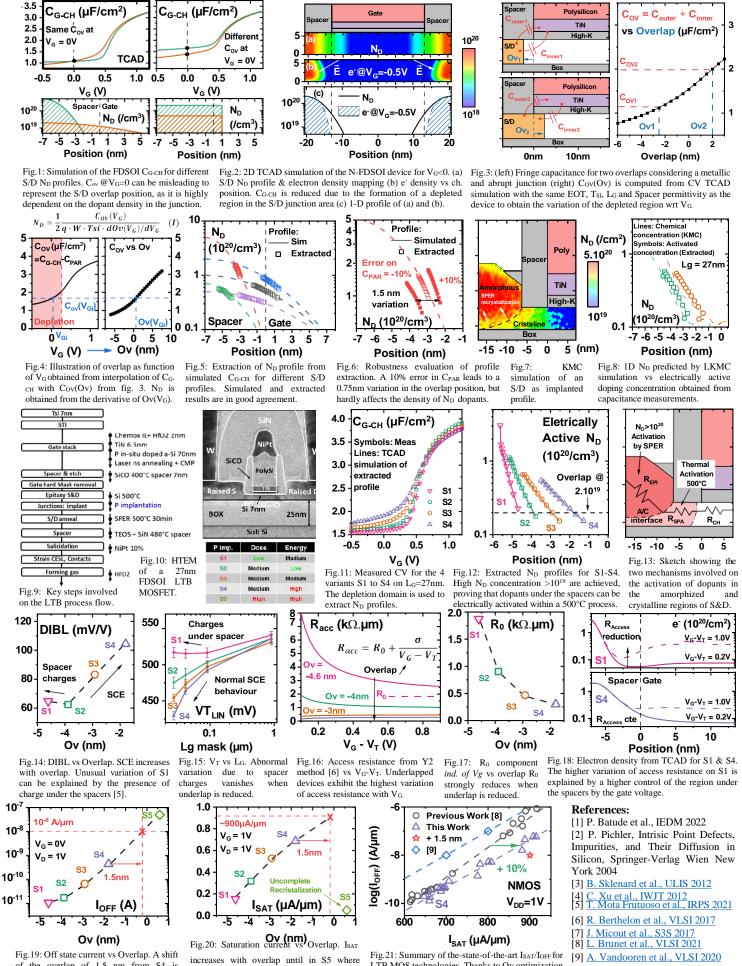

**Abstract** - We present, for the first time, a new CV based technique to extract the Active Dopant Profile under the spacer in thin film FDSOI devices (CV-AJP). The methodology is successfully applied to FDSOI devices fabricated at 500°C for 3D sequential integration. It shows that the Ion/ Ioff trade-off relies mainly on the chemical dopant introduction below the offset spacer, as the activation level obtained with thermal activation is found to be high enough. The LT device demonstrated in this work, already outperforms the literature. The active profile extraction also allows to draw guidelines for further device performance improvement: using a scaled SiCO spacer (5,5nm) allows to circumvent the negligible dopant diffusion at 500°C without dynamic performance penalty due to its low-k dielectric value.

Introduction - 3D sequential integration requires that the top device is processed at Low Temperature (LT) (≤500°C) [1]. At this temperature, a key challenge is the activation of Raised S&D (RSD) dopants done by Solid Phase Epitaxy Regrowth (SPER). However, dopants located beneath the offset spacers are thermally activated. Literature on the activation level at 500°C is very poor and extrapolations of activated levels at 500°C lead to widely scattered values [2]. In addition, the activation level is highly dependent on the Si interstitial concentration present in the region. Due to the specific proximity of the interstitial sinks in thin FDSOI accesses [3,4], the activation level can vary significantly. To evaluate the efficiency of LT activation under the spacers, we developed a novel technique called CV-AJP to extract the junction active profile in FDSOI devices using Capacitance Measurements combined with pure electrical TCAD simulations.

Extraction of junction active profile - The measure of (Cov), i.e. the Gate to Channel capacitance (C<sub>G</sub>-C<sub>H</sub>) in the depletion regime, is frequently used to compare the position of the junction between devices with equivalent geometries. This is generally done by extracting a single Cov value at V<sub>G</sub>=0V (Fig. 1). However this method can be misleading as C<sub>ov</sub> is not constant over V<sub>G</sub>. It strongly depends on the dopant concentration profile as explained in Fig.2. Basically when V<sub>G</sub> is reduced, a depleted region is formed beneath the spacers shifting the conductive region in the direction of the S/D. This phenomenon results in a reduction of the inner and outer field capacitance, all the more important as the doping is low (Fig. 1 (right)). Interestingly, this effect can be used to extract the true junction profile on FD-SOI devices, as illustrated in Fig. 3 & 4. To do that, we first compute, the variation of Cov as the function of the Overlap position (Ov), by means of 2D electrostatic simulations using the same values of EOT, T<sub>SI</sub>, L<sub>G</sub> and spacer permittivity as the device. The S/D junction is here considered as abrupt and metallic, leading to a single value of Cov, independent of V<sub>G</sub>, at each given Ov (Fig. 3). Then, this unique relation Cov vs Ov is combined to measured values of CG-CH, subtracted from the parasitic capacitance (CPAR), to deduce Ov(VG) (Fig. 4). CPAR denotes mainly the V<sub>G</sub>-independent 3D Gate-to Contact parasitic capacitance, and is directly deduced from the difference between measured & simulated CV in the inversion regime. Finally, we derive the dopant concentration as the function of the overlap, from the derivative of  $Ov(V_G)$  in the depletion regime  $(V_{G} < V_T)$  using Eq. (I). Fig 5 highlights the suitability of the technique to extract the dopant profile (ND) in FD-SOI devices: the simplified expression (I) perfectly reproduces the Gaussian profiles entered as inputs in TCAD simulations. Moreover, Fig. 6 reports the sensitivity of the technique to the C<sub>PAR</sub> evaluation, the only parameter of the method. A 10% error in CPAR leads to a 0.75nm variation in the overlap position, but hardly affects the density of N<sub>D</sub> dopants. This demonstrates the robustness of the CV- AJP method for the quantitative

assessment of the true concentration of electrical active dopants. The potential of the method is further highlighted in Fig. 8. The profile of active dopants extracted with the CV- AJP technique well agree with the as-implanted chemical profiles (Fig.7) given by KMC simulation.

**LT Device fabrication** — Fig. 9 shows the LT ( $\leq$ 500°C) N-FDSOI device process flow fabricated with <100> oriented channel ( $T_{si}$ =6,5nm). The gate stack consists of a HFO<sub>2</sub>/TiN (EOT=0.91nm) with UV nanoseconds laser anneal (UV-NLA) for poly-Si activation. Low-k SiCO spacers ( $\epsilon_r$ =4.5), Si Raised Source Drain (RSD) epitaxy followed by SPER activation @ 500°C are carried out. Various implantations conditions (energy and dose) using phosphorous (S1-S5) have been studied (Fig.10). High Pressure Deuterium (HPD<sub>2</sub>) and a tensile CESL are also included. Final device ( $L_G$ =27nm) cross-section HRTEM is displayed in Fig.10.

Optimization of LT junction profile – Fig. 11 & 12 show the CV capacitances measured for four (S1-S4) variants and the corresponding active donor profiles extracted with our CV-AJP technique. The key features are that (1) increasing the energy or the dose allow the dopants to extend closer to the gate while reducing the abruptness of the junction (2) the majority of dopants implanted on the crystalline region are thermally activated (N<sub>D</sub>>2.10<sup>19</sup> cm<sup>-3</sup>) by the 500°C anneal (Fig. 13). The technique is then used to analyze the device performance and to draw guidelines to improve it. Fig. 14 &15 first shows that extending the junction over the spacer (reduced underlap region) also increases DIBL and V<sub>T</sub>(L) magnitude because of the increase of SCE. For S1, an abnormal behavior is yet observed, and due to the fact that this device with the lowest  $N_D$ density becomes highly sensitive to the repealing effect produced by a small amount negative charges in the spacer [5]. Then, access resistance Racc is extracted using the modified Y2 method [6] and plotted as the function of the junction position for the 4 splits (Fig 16 &17). The benefit to reduce the device underlapping by optimizing the P implant is twofold on R<sub>acc</sub>. It allows to (1) strongly decrease the R<sub>0</sub> component independently of V<sub>G</sub> & (2) also to reduce the sensitivity of this resistance to gate bias, resulting from a reduced control of the gate potential over the spacer region (Fig. 18). Finally, Fig. 19 & 20 show new FOMs of I<sub>OFF</sub> and I<sub>ON</sub>, plotted as the function of overlap position. The key feature is that both follows a single trend with Ov. IOFF exponentially increases as SCE becomes important, while I<sub>ON</sub> rises almost linearly mainly due to the combined effect of R<sub>ACC</sub> & V<sub>T</sub> reduction. From this picture, we could predict that reducing the underlap of 1.5nm could lead to I<sub>OFF</sub>=10<sup>-8</sup> A/µm & Ion=900µA/µm for this LT technology. This can be achieved either by increasing energy/dose of P implant or by reducing the thickness of the spacer of 1.5nm. However, the first solution attempted here (S5) has not been successful leading to partially recrystallized access. Indeed an almost vertical amorphous/crystalline interface below the spacer cannot properly acts as a seed for the SPER at 500°C [7]. Nevertheless, the optimization made here with the S4 variant leads Ion=940µA/µm @IoFF=100nA/µm that already outperforms our former and literature results for LT technology [8] (Fig. 20).

**Conclusions -** The CV- AJP method proposed in this paper offers the unique opportunity to quantify directly the density of electrically active dopants in thin film FDSOI device junctions with nanometer resolution, which is not possible so far even with complex and costly physicochemical characterizations like SSRM. Thanks to the technique, it is shown that a high activation level can be achieved without preamorphization of the thin critical region in LT devices, and that junction can be finely optimize to achieve record  $I_{\rm ON}/I_{\rm OFF}$  performance compared to the state of the art for Low Temperature technologies [8,9] (<500°C).

Fig. 19: Off state current vs Overlap. A shift of the overlap of 1.5 nm from S4 is estimated to obtain  $I_{OFF}$  equals to  $10^{-8}$  A/ $\mu$ m.

increases with overlap until in S5 where implant condition is too strong for complete recrystallization [7].

Fig.21: Summary of the-state-of-the-art I<sub>SAT</sub>/I<sub>OFF</sub> for LTB MOS technologies. Thanks to Ov optimization (S4), record I<sub>ON</sub> @I<sub>OFF</sub>100nA/μm is achieved.