# Design and characterization of a novel 3.3 kV 4H-SiC JFET

Florian Chevalier, Pierre Brosselard, D. Tournier, Grégory Grosset, Lionel Dupuy, Dominique Planson

### ▶ To cite this version:

Florian Chevalier, Pierre Brosselard, D. Tournier, Grégory Grosset, Lionel Dupuy, et al.. Design and characterization of a novel 3.3 kV 4H-SiC JFET. Proceedings of the 2012 European Conference on Silicon Carbide and Related Materials ECSCRM, Sep 2012, Saint-Pétersbourg, Russia. 4p. hal-04048180

# HAL Id: hal-04048180 https://hal.science/hal-04048180

Submitted on 27 Mar 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Design and characterization of a novel 3.3 kV 4H-SiC JFET

<u>F. Chevalier</u><sup>a</sup>, P. Brosselard<sup>a</sup>, D. Tournier<sup>a</sup>, G. Grosset<sup>b</sup>, L. Dupuv<sup>b</sup> and D. Planson<sup>a</sup>

Email: florian.chevalier@insa-lyon.fr

<sup>a</sup> Université de Lyon, Ampère Laboratory, INSA de Lyon, 69621 Villeurbanne CEDEX, France

<sup>b</sup> Ion Beam Services, avenue Gaston Imbert prolongée, 13 790 Peynier, France

**Keywords:** Junction Field Effect Transistor, high voltage device, dual gate JFET, lateral channel, vertical channel

Abstract. This paper presents the methodology for the design of a novel 4H-SiC JFET structure able to sustain 3.3 kV. Comparisons between simulation and characterization res will be made. Taken into account the process limitation, we will also discuss the critical steps and their impact on the electrical characteristics. A design methodology based on Baliga's criterion is proposed to obtain the optimal structure. A 50 nm thick thermal oxide grown above vertical channel and the use of a buried  $p^+$  layer as second gate electrode are brand new in front of what is found in literature.

#### Introduction

In the context of more electrical transports, mechanical devices tend to be replaced by their smaller electrical counterparts. However the device itself must support harsh environment and electrical constraints (high voltage, high temperature) thus making existing silicon devices inappropriate. Silicon Carbide (SiC) is today's favorite candidate for the fabrication of devices able to sustain high voltage with a high integration level. Thanks to its 3.3 eV wide band gap energy and its 2.5 MV·cm<sup>-1</sup> high critical field, 4H-SiC allows to design a 3.3 kV Junction Field Effect Transistor (JFET).

A study of a single vertical channel structure leads us to conclude that this structure is not the best for the high voltage we have to sustain. Structures with a buried implanted  $p^+$  area add a lateral channel to the vertical channel are more suitable to reach high voltage. The vertical channel still exists between an aperture in the  $p^+$  area.

Such a structure depends of many parameters, that need to be optimized. Since the influence of the variation of each parameter could not be isolated, we tried to

find mathematical methods to emphase optimal values leading to set an optimization criterion, inspired from Baliga's works [1].

#### Limitations of single channel JFET

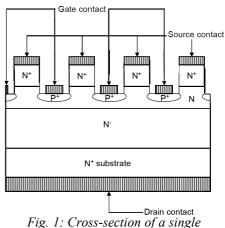

Fig. 1 shows the cross-section of a single channel vertical JFET designed by Semisouth in 2006. The main benefit of this structure is its low on-state resistance (about 2.86 m $\Omega$ ·cm<sup>2</sup>) [2]. So it enables high current levels with a low rise of temperature. Moreover it is easy to make a normally-off device with such a structure by narrowing the channel width. Nonetheless our

channel vertical JFET [2]

simulation results show an important drawback. The high voltage on device backside goes up to the source through the vertical channel. The gate is still protected by the reverse junction. Thus, while this structure is really efficient for 1200 V, it cannot be led to 3.3 kV without important leakage current in blocking mode.

#### Design of lateral and vertical device

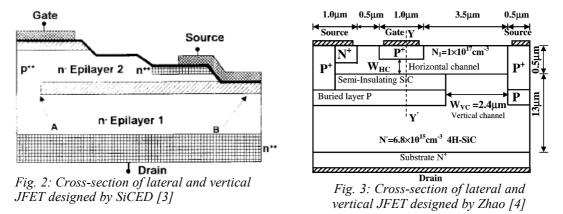

State of the art. As it can be seen in Fig. 2 and 3, a buried  $p^+$  layer is frequently used. This layer is related to the source electrode [3-4]. Thus, it is always at a constant (and often null) potential, and it can be used as a free-wheeling diode. The interest of such a configuration is that the vertical channel is no more a limitation and just protect the source electrode against the spread of high drain voltage. But its drawback is that the blocking capabilities depends only on the surface gate electrode. Consequently an efficient channel blocking depends on a thin lateral channel (that leads to high channel resistivity) or on a high (in absolute value) blocking voltage.

Our challenge was designing a lateral channel with a low on-state resistivity, low pinch-off voltage and high breakdown voltage.

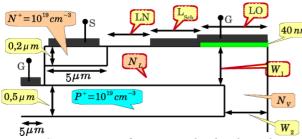

**Technological elements and innovative advances.** In order to perform a 3.3 kV, we first optimized the first epilayer with a  $10^{15}$  cm<sup>-3</sup> doping level and 40 µm thick. For this optimization, we have taken into account the edge termination and the passivation efficiency. The vertical channel needs a  $10^{16}$  cm<sup>-3</sup> doping level ( $N_V$ ), which will be realized by a second epilayer. Known as  $W_2$  in Fig. 4, it will be 3 µm wide. Then we implant double charge of aluminum (Al) at 320 keV to perform a 0.5 µm thick  $p^+$  layer, that will make the burried layer after a  $W_I = 3$  µm @  $N_L = 10^{16}$  cm<sup>-3</sup> third epilayer. Prior to the etching of this layer to access the buried layer, we implant a single charge of nitrogen (N) at 180 keV energy that will make the 0.2 µm thick  $n^+$  source layer.

The high electrostatic potential can flow from the backside drain electrode through the drift region to the third epilayer *via* the vertical channel, even if it is designed to avoid high potential in lateral channel. So we decided to protect the surface gate with a 50 nm thick thermal oxide above vertical channel [5]. It is brand new in front of what is found in literature.

As it has been explained above, the buried  $p^+$  layer is traditionally related to source electrode to set a constant potential. If this layer is related to the gate electrode, it can be helpful to block the lateral channel, hence reduce the pinch-off voltage. That is why we decided to use it as a buried gate electrode.

#### The structure and its parameters.

Fig. 4 shows the parameters we have to optimize.  $W_1$  and  $W_2$  are the widths of lateral and vertical channel respectively, while  $N_L$  and  $N_V$  their respective doping levels. LN is the margin between the

Fig. 4: Cross-section of a JFET with a low lateral channel on-state resistivity and high blocking facilities

<sup>40</sup>*nm*</sub> source and the surface gate contacts,  $L_{Sch}$  is the length of the Schottky surface gate contact and LO is the length of the protecting oxide.

Those last three parameters form the length of the lateral channel. They can vary from 3 to  $5 \mu m$ , respectively the shorter we can fabricate and the longer to reduce lateral channel resistivity.

To make a more efficient and reliable device, we have to find the optimal values for those seven parameters. To this end, we performed simulations with

Sentaurus<sup>TM</sup> software which is based on the finite elements method. Electrical characteristics that have to be increased is the breakdown voltage  $V_{BR}$  and to be decreased, the pinch-off voltage  $V_{GS-off}$  and the on-state resistance  $R_{on}$ . So we have used a criterion inspired from Baliga's one [1]:

$$max \left| \frac{V_{BR}^2}{V_{GS-off} \cdot R_{on}} \right|$$

LN=3 μm LN=4 μm

Ė

Tab. 1 : Optimal parameters values and related electrical characteristics

| $W_1$ | $W_2$ | $N_L$            | $N_V$     | LO | LN | L <sub>Sch</sub> | $V_{BR}$ | Ron   | $V_{GS-off}$ |

|-------|-------|------------------|-----------|----|----|------------------|----------|-------|--------------|

| μm    |       | cm <sup>-3</sup> |           | μm |    |                  | kV       | mΩ•cm | V            |

| 3     | 3     | 1016             | 1016      | 5  | 3  | 4                | 4,3      | 171   | -19.5        |

| 3     | 3     | 1016             | $10^{16}$ | 5  | 4  | 3                | 4,3      | 171   | -20          |

Device's length is compound by 5  $\mu$ m for gate contact and 5  $\mu$ m for source contact. In Fig. 5, it can be seen that for a 20  $\mu$ m long device, it left only 10  $\mu$ m for LN+LO+Lsch. So if LN = 3  $\mu$ m, then LO+Lsch = 7  $\mu$ m=3+4 or 4+3. That is why two crosses can be found at the 20  $\mu$ m point.

While the result given by this criterion is not homogeneous, we will focus only on the absolute value. E.g. in fig. 5, we can clearly see that  $3 \mu m$  is the best value for *LN*.  $3 \mu m$  is the low technological limit. Over  $5 \mu m$ , the lateral channel will be to long to have make a low on-state resistance. Therefore, we must choose values between 3 and 5  $\mu m$ , and 3  $\mu m$  is the best.

25

#### Fabrication and characterization

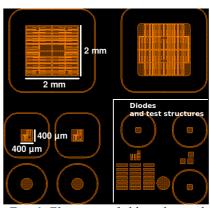

The mask layer set was designed according to optimal parameters. To fabricate this transistor, 14 photolithography levels have been performed. Fig. 6 shows an elementary field where two 4 mm<sup>2</sup> JFETs and four 0.16 mm<sup>2</sup> JFETs are implemented. Test structures like vertical diodes in order to evaluate the vertical breakdown voltage were also implemented. Electrical measurement are shown on figure 7. The devices have been manufactured at IBS.

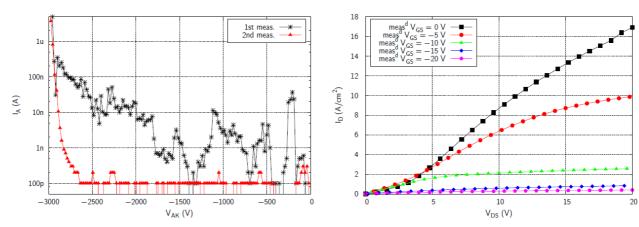

Blocking voltage of gate-drain junction is about 3 kV. This measure has been performed in vacuum at ISL [6].

Fig. 6: Elementary field on the mask set

#### Parametric optimization.

3 < LO < 5 μm

< 1 sch < 5 um

21

Fig. 5: Example of criterion value curve for LN

22

Device length  $(\mu m)$

23

24

6.5

6.0

5.5

5.0

4.5

4.0

3.5

19

Criterion value  $|V_{BR}^2/R_{on}.V_{off}|$  .  $10^6$

Fig. 8 shows the electrical characteristics  $J_{DS}(V_{DS})$  with different  $V_{GS}$  at 25°C. The increase of control voltage  $V_{GS}$  clearly affects the channel modulation. To block the JFET, -20 V as  $V_{GS}$  are sufficient. Fig. 9 shows a clear trend of JFET effect : a channel modulation affected by the increase of control voltage  $V_{GS}$  from 0 V to – 20 V. Measurements have been performed under probes without thick metal layer. So the on-state resistance is lower than expected value.

*Fig.* 7 : *Electrical characterization of 3.3 kV bipolar test diode equivalent to gate-drain junction*

Fig. 8 : Measured  $J_{DS}(V_{DS})$  for different  $V_{GS}$  at 25°C for a 4mm<sup>2</sup> fabricated JFET

#### Summary

Actually existing vertical JFET are generally unable to sustain high voltage due to an inadequate gate topology. To address this issue, we presented a novel JFET structure that is able to sustain voltage up to 3.3 kV. The optimal design of such a structure is obtained thanks to the introduction of a modified Baliga criterion. Characterization results confirms simulation results, reaching over than 3 kV, and thus validate the design methodology.

#### Acknowledgment

Authors want to thanks DGA, the French Weapon Delegation for the financial support of the PhD. thesis and ISL, French-German research institute for the measurement facilities.

#### References

[1] Baliga, B. J., Fundamentals of power semiconductors devices, Springer, 2008

[2] Cheng, L.; Casady, J.; Mazzola, M.; Bondarenko, V.; Kelley, R.; Sankin, I.; Merrett, J. & Casady, J. Fast switching (41 MHz), 2.5 m $\Omega \cdot \text{cm}^2$ , high current 4H-SiC VJFETs for high power and high temperature applications, *Materials Science Forum*, **2006**, *527-529*, 1183-1186

[3] Friedrichs, P.; Mitlehner, H.; Schörner, R.; Kaltschmidt, R.; Dohnke, K.-O. & Stephani, D., Influence of the buried *p*-layer on the blocking behavior of vertical JFETs in 4H-SiC, *Materials Science Forum*, **2001**, 353-356, 695-698

[4] Zhao, J.; Li, X.; Tone, K.; Alexandrov, P.; Pan, M. & Weiner, M., Design of a novel planar noramlly-off power VJFET in 4H-SiC, *Solid-State Electronics*, **2003**, 47, 377-384

[5] Tournier, D.; Brosselard, P. & Chevalier, F., Structure semi-conductrice pour interrupteur électronique de puissance, French patent BR67419/CPI/VP, **2010**

[6] Vergne, B.; Pâques, G.; Maurer, C.; Scharnholz, S.; Brosselard, P. & Planson, D., PASChAC, système automatisé de caractérisation de composants sur wafer, *EPF2012*, **2012**