# Quasi-Flying Gate Concept Used for Short-Circuit Detection on SiC Power MOSFETs Based on a Dual-Port Gate Driver

Mathis Picot-Digoix, Frédéric Richardeau, Jean-Marc Blaquière, Sébastien Vinnac, Stéphane Azzopardi, Thanh-Long Le

## ▶ To cite this version:

Mathis Picot-Digoix, Frédéric Richardeau, Jean-Marc Blaquière, Sébastien Vinnac, Stéphane Azzopardi, et al.. Quasi-Flying Gate Concept Used for Short-Circuit Detection on SiC Power MOS-FETs Based on a Dual-Port Gate Driver. IEEE Transactions on Power Electronics, 2023, pp.1-4. 10.1109/TPEL.2023.3258640 . hal-04039921

# HAL Id: hal-04039921 https://hal.science/hal-04039921v1

Submitted on 21 Mar 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Quasi-Flying Gate Concept Used for Short-Circuit Detection on SiC Power MOSFETs Based on a Dual-Port Gate Driver

Mathis Picot-Digoix, Frédéric Richardeau, Jean-Marc Blaquière, Sébastien Vinnac, Stéphane Azzopardi and Thanh-Long Le

Abstract—The proposed dual-port gate driver architecture relies on a quasi-flying gate concept to protect SiC power MOSFETs against short-circuit events. Hard Switching Faults (HSF) extract charges from the gate by causing a leakage current towards the source, while Faults Under Load (FUL) lead to charge injection into the gate through the reverse transfer capacitance ( $C_{GD}$ ). Such phenomena lead to perturbations of the gate-source voltage (V<sub>GS</sub>) which are amplified by the gate resistor, acting as an enhancer of short-circuit signatures. Thus, a small gate resistance is used to ensure high switching dynamics, while a larger one is switched on during PWM on-state operation to identify possible faults. A dual-port gate driver is then proposed to ensure fast switching with HSF and FUL monitoring. The fault detection scheme relies on comparing two thresholds to V<sub>GS</sub> relative changes to the nominal gate voltage. Experimental results using TO-247 package 1.2kV/36A SiC MOSFETs exhibit promising inverter leg shortcircuit detection and protection against faults in less than 300ns.

### I. INTRODUCTION

SiC MOSFETs afford high efficiency and density of medium to high power range converters [1]. Beyond usual first plan characteristics, the power chip's ability to withstand extreme operating conditions is critical in a certification approach, to comply with a broad application spectrum [2]. In short-circuit operation, a critical and irreversible failure mode would happen in only a few microseconds [3]. Shortcircuit protection methods [4] rely exhaustively on either the ruggedness of the power transistor itself - which is still at an early development stage [5], on a current limiting inpackage hybridization [6], [7] - increasing conduction losses, or on detection methods such as desaturation, gate charge integration or absence of Miller plateau [8], [9], all showing a compromise between reactivity, complexity, and ruggedness. As of today, no solution clearly complies with all three criteria. The proposed approach consists in reconsidering the gate capacitance not only as a control element (turn-on/turnoff management), but also as an on-state high-sensitivity monitoring sensor providing low gate voltage fluctuations that do not impede normal operation thanks to intrinsic properties of SiC MOSFETs.

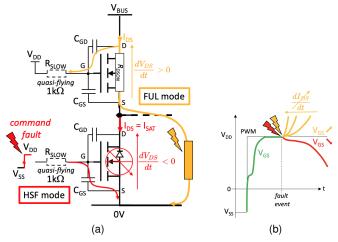

In HSF mode [10] (Fig. 1 in red color line), an internal Schottky emission thermionic gate leakage current arises at high temperatures and discharges  $C_{GS}$ , in turn decreasing the quasi-flying  $V_{GS}$ , naturally limiting the channel current.

In FUL mode [11] (Fig. 1 in yellow color line), the DUT is initially in an on-state. Its drain-source voltage  $V_{\rm DS}$  is therefore

Fig. 1. HSF Schottky gate leakage current in red color and FUL gate charge injection in yellow color illustration (a), influence on gate-source voltage (b)

low, which makes  $C_{GD}$  exhibit a high value. On the other hand, the MOSFET still being in its ohmic region, the faulty drain current  $I_{DS}$  rise creates an ohmic  $dV_{DS}/dt$  through its drain-source on-resistance  $R_{DSON}$ . The strong capacitive coupling between  $C_{GD}$  and this  $V_{DS}$  rise injects charges from drain to gate, back to the driver through the gate resistance. This increases  $V_{GS}$ , thus extending the MOSFET ohmic region and high  $C_{GD}$  value. In this case, a gate clamp is needed not to damage the  $SiO_2$  gate oxide layer.

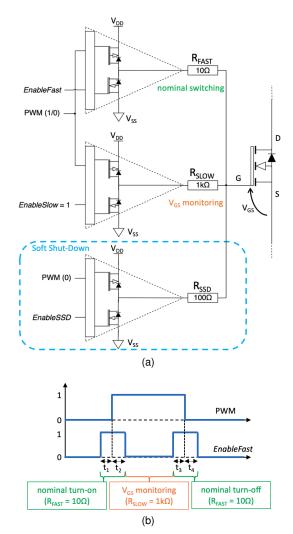

Both these mechanisms prove to enhance fault detection sensitivity and ruggedness during on-state operation using a very large external gate resistance to virtually isolate the gate between turn-on and turn-off events. However, switching dynamics would then be greatly impeded. The use of different gate resistors is mandatory for switching and for on-state operation using a dedicated switched-resistors gate driver architecture (Fig. 2a), as generically introduced in [12].

### II. CONCEPT HARDWARE IMPLEMENTATION

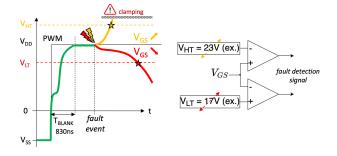

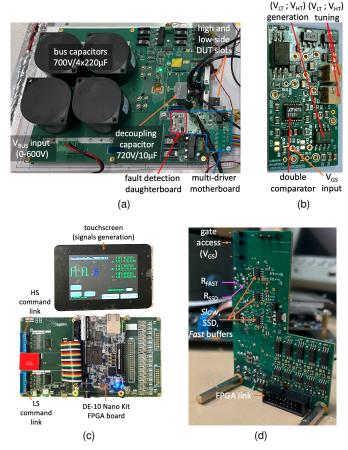

It appears in Fig. 1b that comparing the quasi-flying on-state  $V_{GS}$  to upper  $(V_{HT})$  and lower  $(V_{LT})$  thresholds would allow the detection of all short-circuit events. Commercial 3-lead TO-247 package Gen. 2  $80m\Omega$  1200V/36A SiC MOSFETs underwent short-circuit tests in an inverter leg configuration on a 600V capacitor-bank-based power bench (Fig. 4a). Short-circuit detection is then made possible thanks to a proposed

Fig. 2. Multi-port switched gate driver architecture (a) and *Fast* low resistance buffer control signals (b)  $(V_{DD} = 20V, V_{SS} = -5V, t_1 = 50ns, t_2 = 830ns, t_3 = 50ns, t_4 = 830ns)$

Fig. 3.  $V_{GS}$  double threshold comparison short-circuit detection principle

double threshold on  $V_{GS}$  (Fig. 3) and a double-comparator-based daughterboard (Fig. 4b) plugged into a multi-port gate-driver-based motherboard (Fig. 4d) to ensure fast switching ("Fast" buffer), increased fault detection sensitivity ("Slow" quasi-flying buffer), and Soft Shut-Down protection (SSD buffer). Fast mode should be long enough to allow for complete charge and discharge of the gate capacitances, and to protect the complementary MOSFET during turn-on events against  $C_{GD}$  coupling. Both Fast and Slow buffers receive

Fig. 4. Setup: short-circuit test bench (a), double threshold detection daughterboard (b), FPGA-based control board (c) and multi-buffer motherboard (d)

the same PWM signal. For practical reasons, the *Slow* buffer is always active, while the *Fast* one is only enabled during switching events and otherwise in high impedance during static states as shown in Fig. 2b. A FPGA-based control board (Fig. 4c) generates PWM and *EnableFast* signals, introduces a blanking time and receives the V<sub>GS</sub> comparison result to the two thresholds and imposes the *EnableSSD* signal accordingly.

### III. EXPERIMENTAL RESULTS AND ANALYSIS

### A. Hard Switching Faults

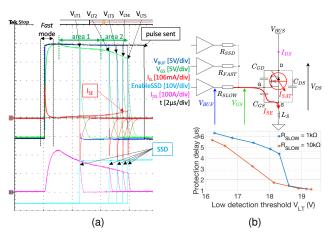

HSF faults happen following an undesirable turn-on (Fig. 1a) thus generating an extreme temperature rise, which gives way to a Schottky emission current leakage ( $I_{SE}$ ) through the gate oxide [13].  $I_{SE}$  causes  $V_{GS}$  to drop proportionally to  $R_{SLOW}$  a few microseconds after the appearance of the fault (Fig. 5a area 2). This natural  $V_{GS}$  drop participates in shrinking the MOSFET channel, limiting the saturation current, and thus the chip temperature rise. In the case of a HSF, this phenomenon provided by the proposed gate architecture ensures that should the above-mentioned protection method fail, the MOSFET would still enter into a safe failure mode characterized by a gate-to-source short, thus naturally turning off the switch [14]. Once  $V_{GS}$  falls below the low detection threshold  $V_{LT}$ , the FPGA sends the SSD order and enables the SSD buffer while setting all PWM signals to 0.

Fig. 5. HSF gate behavior (a), equivalent schematic and protection delay results (b) ( $V_{BUS}$  = 600V,  $R_{FAST}$  = 47 $\Omega$ ,  $R_{SLOW}$  = 1k $\Omega$ ,  $R_{SSD}$  = 82 $\Omega$ )

Moreover, Fig. 5a shows an advantageous decrease in V<sub>GS</sub> as soon as the fault happens (area 1) thanks to a high R<sub>SLOW</sub> value (1k $\Omega$ ) likely to result from the chip source wires and lead stray inductance (L<sub>S</sub>) coupling due to the high inrush fault current, and probably also from a pre-thermal phenomenon. The SSD total protection delay is measured between the instant the fault appears and the effective turn-off. The closer the low detection threshold to the nominal on-state gate voltage, the faster the protection. However, the low detection threshold  $V_{\rm LT}$ can only be increased so much before risking false detections, hence a trade-off between protection speed and robustness. This compromise can be solved by increasing R<sub>SLOW</sub> and making V<sub>GS</sub> area 1 drop even lower, as illustrated in Fig. 3 red curve. A HSF protection delay of 1.2µs is achieved including a total inherent propagation delay of 230ns partly due to optocouplers between the FPGA and the SSD buffer. This protection delay is well inferior to the MOSFET shortcircuit withstand time (T<sub>SCW</sub>) of 8µs and limits the dissipation of energy to 140mJ (20% of the critical energy of 0.7J [15]) in the power transistor. In comparison, although the desaturation method can theoretically achieve fast short-circuit protection, in industrial applications, blanking windows are implemented as a safety margin to avoid false detections. It also still requires expensive and non-integrable high-voltage sensing diodes. The expression (1) of the maximum V<sub>GS</sub> transient drop in HSF mode shows both contributions in areas 2 and 1 of Fig. 5a:

$$|\delta V_{GS}|_{HSF} = \underbrace{R_{SLOW}I_{SE}}_{area\ 2} + \underbrace{L_{S}\frac{dI_{DS}}{dt}}_{(1)}$$

With I<sub>SE</sub> the Schottky emission current defined in (2).

$$I_{SE} = A_0 \frac{4\pi q k^2 m_{ox}}{h^3} T^2 \cdot exp\left(\frac{-\Phi_B + \sqrt{\frac{q^3 E}{4\pi \epsilon_r \epsilon_0}}}{kT}\right)$$

(2)

Where T is the temperature and  $A_0$  is the chip active surface. Other physical parameters are defined in [13].

### B. External Faults Under Load

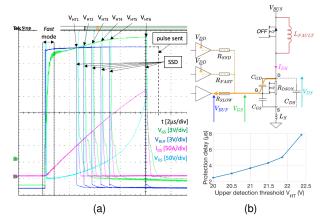

External FUL are characterized by a current rise through an on-state switch following the appearance of an inductive path

Fig. 6. External FUL gate behavior (a), schematic and protection results (b) ( $V_{BUS} = 600V$ ,  $R_{FAST} = 47\Omega$ ,  $R_{SLOW} = 10k\Omega$ ,  $R_{SSD} = 82\Omega$ ,  $L_{FAULT} = 11.6\mu H$ )

(Fig. 1a). This additional current creates a  $V_{DS}$  ohmic rise and participates in increasing  $V_{GS}$  by injecting charges back to the driver through  $C_{GD}$ , thus further extending the MOSFET ohmic region – the region of interest, as the thermal stress is the lowest. Although the fault current rise is slow,  $R_{SLOW}$  acts as a gain amplifier and makes it possible for this gate driver architecture to also detect this type of fault as shown in Fig. 6a. Effective protection happens in 2.5 $\mu$ s (Fig. 6b), including 190ns of propagation delay, in the MOSFET ohmic region. The associated dissipated energy is only 2.2 $\mu$ J (0.3% of 0.7J). This guarantees a correct safety margin as the chip will be able to withstand several repeated short-circuits.

$$|\delta V_{GS}|_{ext.FUL} = R_{SLOW}C_{GD}(V_{DS})\frac{dV_{DS}}{dt}$$

(3)

Equation (3) shows external-FUL-induced  $V_{GS}$  overvoltage. It should be noted that, in this case,  $L_S$  has a negligible effect due to the slow current rise.

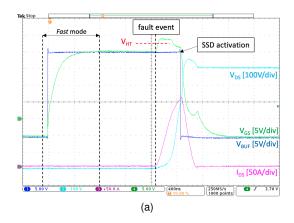

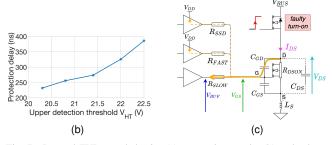

### C. Internal Faults Under Load

Internal FUL are characterized by the failure of a complementary switch in an inverter leg or an erratic command, leading to an extreme sudden drain current rise in an initially on-state switch. The current rise is now only limited by the faulty switch  $V_{\rm GS}$  slew rate. This ensures a strong and dynamic coupling with the gate through  $L_{\rm S}$  in addition to  $C_{\rm GD}$  capacitive coupling, as in external FUL, as shown in (4).

$$|\delta V_{GS}|_{int.FUL} = (R_{SLOW}C_{GD_{MAX}}R_{DS_{ON}} + L_S)\frac{dI_{DS}}{dt}$$

(4)

Given the large value of  $R_{SLOW}$ , the gate-source stray inductance is not considered as  $V_{GS}$  transients show no ringing. Fig. 7 shows effective protection against internal FUL in 250ns only. The extreme channel current rise and the large value of  $R_{SLOW}$  are sufficient to generate an overvoltage on  $V_{GS}$  that triggers the detection circuit even before the MOSFET reaches its saturation area. During the on-state, the *Fast* and SSD buffers are in a high-impedance state and the gate voltage excursion is naturally clamped by their high-side PMOS body diodes as illustrated in Fig. 2a, thus protecting the gate. In

Fig. 7. Internal FUL gate behavior (a), protection results (b) and schematic (c) ( $V_{BUS}=600V,\,R_{FAST}=47\Omega,\,R_{SLOW}=10k\Omega,\,R_{SSD}=82\Omega,\,V_{HT}=22.4V$ )

internal FUL, the gate charge injection is sudden and intense which requires great reactivity and sensitivity of the detection system, while in external ones, it is considerably slower and more moderate. The inductive effect provided by  $L_{\rm S}$  is predominant and adds to the contribution of  $C_{\rm GD}$  solicited by the drain-to-source voltage rise.

### D. Implementation and concept properties in an inverter leg

For a practical implementation in an inverter leg, the faulty turn-on (HSF) and the subsequent extreme current rise happening in one switch will impact its already-on counterpart that, in turn, endures a HSF-induced internal FUL. This property allows the detection of HSF faults thanks to a FUL detection on the complementary switch gate driver. It is thus possible to detect HSF faults with the same dynamics as internal FUL.

### IV. CONCLUSION

This paper demonstrates a comprehensive short-circuit protection method provided through an original SiC MOSFET dual-port gate driver architecture. A small gate resistance channel is used during switching events, and a large gate resistance channel handles fault event monitoring. The detection relies on putting the gate into a quasi-flying state to enhance its sensitivity to possible gate charge variations, which are short-circuit signatures, and turn it into a fault sensor. The measure of the MOSFET gate-source voltage effectively allows the protection of an inverter leg against HSF-type faults in 1.2µs, and against internal FUL in 250ns. In the case of HSF faults, the coupling of high-side and low-side protections puts them into competition allowing the fastest to protect the inverter leg. This redundancy significantly decreases HSF protection time

and adds a layer of robustness. The proposed fault detection scheme relies on gate-source low voltage fluctuations and is thus highly integrable with analog IC technology.

### ACKNOWLEDGMENTS

The authors would like to thank Wadia Jouha for his contribution to the development of the multi-buffer motherboard.

### REFERENCES

- [1] Z. J. Shen, "SiC Research Beyond Power MOSFET: What's Next? [Happenings]," *IEEE Power Electronics Magazine*, vol. 8, no. 2, pp. 14–23, 2021.

- [2] A. O. Adan, D. Tanaka, L. Burgyan, and Y. Kakizaki, "The Current Status and Trends of 1,200-V Commercial Silicon-Carbide MOSFETs: Deep Physical Analysis of Power Transistors From a Designer's Perspective," *IEEE Power Electronics Magazine*, vol. 6, no. 2, pp. 36–47, 2019

- [3] A. Castellazzi, A. Fayyaz, G. Romano, M. Riccio, A. Irace, J. Urresti-Ibanez, and N. Wright, "Transient out-of-SOA robustness of SiC power MOSFETs," in 2017 IEEE International Reliability Physics Symposium (IRPS), 2017, pp. 2A–3.1–2A–3.8.

- [4] S. Musumeci, R. Pagano, A. Raciti, G. Belverde, and A. Melito, "A new gate circuit performing fault protections of IGBTs during short circuit transients," in *Conference Record of the 2002 IEEE Industry Applications Conference. 37th IAS Annual Meeting (Cat. No.02CH37344)*, vol. 4, 2002, pp. 2614–2621 vol.4.

- [5] G. Romano, M. Riccio, L. Maresca, G. Breglio, A. Irace, A. Fayyaz, and A. Castellazzi, "Influence of design parameters on the short-circuit ruggedness of SiC power MOSFETs," in 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2016, pp. 47–50.

- [6] A. Kanale and B. J. Baliga, "Theoretical Optimization of the Si GSS-DMM Device in the BaSIC Topology for SiC Power MOSFET Short-Circuit Capability Improvement," *IEEE Access*, vol. 9, pp. 70039–70047, 2021.

- [7] X. Li, X. Deng, X. Li, X. Xu, Y. Wen, H. Wu, W. Chen, and B. Zhang, "A Novel SiC MOSFET With Embedded Auto-Adjust JFET With Improved Short Circuit Performance," *IEEE Electron Device Letters*, vol. 42, no. 12, pp. 1751–1754, 2021.

- [8] J. Schmitz, M. Meissner, and S. Bernet, "Rugged and fast short circuit detection method for GaN HEMT based on saturation detection," in CIPS 2022; 12th International Conference on Integrated Power Electronics Systems, 2022, pp. 1–6.

- [9] Y. Barazi, N. Rouger, and F. Richardeau, "CMOS Gate Driver with fast short circuit protection for SiC MOSFETs," in 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2020, pp. 94–97.

- [10] J. Sun, H. Xu, X. Wu, and K. Sheng, "Comparison and analysis of short circuit capability of 1200V single-chip SiC MOSFET and Si IGBT," in 2016 13th China International Forum on Solid State Lighting: International Forum on Wide Bandgap Semiconductors China (SSIChina: IFWS), 2016, pp. 42–45.

- (SSLChina: IFWS), 2016, pp. 42–45.

[11] M. Cui, J. Li, Y. Du, and Z. Zhao, "Behavior of SiC MOSFET under Short-Circuit during the On-State," IOP Conference Series: Materials Science and Engineering, vol. 439, no. 2, p. 022026, nov 2018.

- [12] M. Wang, W. J. Zhang, J. Liang, W. T. Cui, W. Tung Ng, H. Nishio, H. Sumida, and H. Nakajima, "A Smart Gate Driver for SiC Power MOSFETs with Aging Compensation and Ringing Suppression," in 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2021, pp. 67–70.

- [13] F. Boige, D. Trémouilles, and F. Richardeau, "Physical Origin of the Gate Current Surge During Short-Circuit Operation of SiC MOSFET," *IEEE Electron Device Letters*, vol. 40, no. 5, pp. 666–669, 2019.

- [14] W. Jouha, F. Richardeau, and S. Azzopardi, "Towards a safe failure mode under short-circuit operation of power SiC MOSFET using optimal gate source voltage depolarization," *Microelectronics Reliability*, vol. 126, p. 114258, 2021, proceedings of ESREF 2021, 32nd European Symposium on Reliability of Electron Devices, Failure Physics and Analysis.

- [15] A. E. Awwad and S. Dieckerhoff, "Short-circuit evaluation and overcurrent protection for SiC power MOSFETs," in 2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), 2015, pp. 1–9.