## Technical Design Report for the ATLAS inner Tracker pixel detector

N.G. Allemandou, P. Barroca, N. Berger, A.M. Burger, F. Costanza, O. Dartsi, P.Y. David, P. Delebecque, M. Delmastro, L. Di Ciaccio, et al.

#### ▶ To cite this version:

N.G. Allemandou, P. Barroca, N. Berger, A.M. Burger, F. Costanza, et al.. Technical Design Report for the ATLAS inner Tracker pixel detector. ATLAS-TDR-030, CERN. 2018. hal-03978880

### HAL Id: hal-03978880 https://hal.science/hal-03978880v1

Submitted on 8 Feb 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution - NoDerivatives 4.0 International License

ATL-TDR-030 · LHCC-2017-021

# Inner Tracker Pixel Detector

# **Technical Design Report**

# Technical Design Report for the ATLAS Inner Tracker Pixel Detector

Reference:CERN-LHCC-2017-021<br/>ATLAS-TDR-030Created:15th June 2018Prepared by:The ATLAS Collaboration

© 2018 CERN for the benefit of the ATLAS Collaboration. Reproduction of this article or parts of it is allowed as specified in the CC-BY-4.0 license.

#### Abstract

This is the second of two Technical Design Report documents that describe the upgrade of the central tracking system for the ATLAS experiment for the operation at the High Luminosity LHC (HL-LHC) starting in the middle of 2026. At that time the LHC will have been upgraded to reach a peak instantaneous luminosity of  $7.5 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>, which corresponds to an average of about 200 inelastic proton-proton collisions per beam-crossing. The new Inner Tracker (ITk) will be operational for more than ten years, during which time ATLAS aims to accumulate a total data set of 4000  $fb^{-1}$ . Many of the features of the tracker have already been presented in the first Technical Design Report that detailed the construction of the ITk Strip Tracker. That report was published in April 2017. This document focuses on the ITk Pixel Detector. A baseline design is described in detail, and the motivations for the chosen technologies are illustrated. In some cases, alternative solutions are also illustrated. In this case, we indicate the advantage in pursuing the other designs, and describe the time line for a decision. The design, construction and expected performance are set out in detail. When considering performance we pay particular attention to those parameters that are determined by the performance of the Pixel Detector. We describe in detail the design and construction of the Pixel Detector, including the results of measurements of prototype modules and associated support structures and we explain the status of the plans for their mass production. We present details of the decommissioning of the existing tracking detector and the replacement of the inner layers of the ITk Pixel Detector part way through the lifetime of the High Luminosity LHC. Finally, we describe: the costing and schedule, including major milestones, to construct the detector.

#### The ATLAS Collaboration

#### Argentina

Departamento de Física, Universidad de Buenos Aires, Buenos Aires Instituto de Física La Plata, Universidad Nacional de La Plata and CONICET, La Plata

#### Armenia

Yerevan Physics Institute, Yerevan

#### Australia

Department of Physics, University of Adelaide, Adelaide School of Physics, University of Sydney, Sydney School of Physics, University of Melbourne, Victoria

#### Austria

Institut für Astro- und Teilchenphysik, Leopold-Franzens-Universität, Innsbruck Fachhochschule Wiener Neustadt, Wiener Neustadt

#### Azerbaijan

Institute of Physics, Azerbaijan Academy of Sciences, Baku

#### Belarus

B.I. Stepanov Institute of Physics, National Academy of Sciences of Belarus, Minsk Research Institute for Nuclear Problems of Byelorussian State University, Minsk

#### Brazil

*Brazil Cluster*: Departamento de Engenharia Elétrica, Universidade Federal de Juiz de Fora (UFJF), Juiz de Fora; Universidade Federal do Rio De Janeiro COPPE/EE/IF, Rio de Janeiro; Universidade Federal de São João del Rei (UFSJ), São João del Rei; Instituto de Física, Universidade de São Paulo, São Paulo

#### Canada

Department of Physics, Simon Fraser University, Burnaby BC Department of Physics, University of Alberta, Edmonton AB Department of Physics, McGill University, Montreal QC Group of Particle Physics, University of Montreal, Montreal QC Department of Physics, Carleton University, Ottawa ON Department of Physics, University of Toronto, Toronto ON Department of Physics, University of British Columbia, Vancouver BC TRIUMF, Vancouver BC; Department of Physics and Astronomy, York University, Toronto ON Department of Physics and Astronomy, University of Victoria, Victoria BC

#### CERN

European Organization for Nuclear Research, Geneva, Switzerland

#### Chile

*Chile Cluster*: Departamento de Física, Pontificia Universidad Católica de Chile, Santiago; Departamento de Física, Universidad Técnica Federico Santa María, Valparaíso

#### China

*China IHEP-NJU-THU Cluster*: Institute of High Energy Physics, Chinese Academy of Sciences, Beijing; Department of Physics, Nanjing University, Nanjing; Physics Department, Tsinghua University, Beijing

*China USTC-SDU-SJTU Cluster*: Department of Modern Physics and State Key Laboratory of Particle Detection and Electronics, University of Science and Technology of China, Hefei; Institute of Frontier and Interdisciplinary Science and Key Laboratory of Particle Physics and Particle Irradiation (MOE), Shandong University, Qingdao; School of Physics and Astronomy, Shanghai Jiao Tong University, KLPPAC-MoE, SKLPPC, Shanghai; Tsung-Dao Lee Institute, Shanghai

*Hong Kong Cluster*: Department of Physics, Chinese University of Hong Kong, Shatin, N.T., Hong Kong; Department of Physics, University of Hong Kong, Hong Kong; Department of Physics and Institute for Advanced Study, Hong Kong University of Science and Technology, Clear Water Bay, Kowloon, Hong Kong

#### Colombia

Centro de Investigaciónes, Universidad Antonio Nariño, Bogota

#### **Czech Republic**

Palacký University, RCPTM, Joint Laboratory of Optics, Olomouc Charles University, Faculty of Mathematics and Physics, Prague Czech Technical University in Prague, Prague Institute of Physics, Academy of Sciences of the Czech Republic, Prague

#### Denmark

Niels Bohr Institute, University of Copenhagen, Copenhagen

#### France

LAPP, Université Grenoble Alpes, Université Savoie Mont Blanc, CNRS/IN2P3, Annecy LPC, Université Clermont Auvergne, CNRS/IN2P3, Clermont-Ferrand DRF/IRFU, CEA Saclay, Gif-sur-Yvette LPSC, Université Grenoble Alpes, CNRS/IN2P3, Grenoble INP, Grenoble CPPM, Aix-Marseille Université, CNRS/IN2P3, Marseille LAL, Université Paris-Sud, CNRS/IN2P3, Université Paris-Saclay, Orsay LPNHE, Sorbonne Université, Paris Diderot Sorbonne Paris Cité, CNRS/IN2P3, Paris

#### Georgia

*Georgia Cluster*: E. Andronikashvili Institute of Physics, Iv. Javakhishvili Tbilisi State University, Tbilisi; High Energy Physics Institute, Tbilisi State University, Tbilisi

#### Germany

Institut für Physik, Humboldt Universität zu Berlin, Berlin Physikalisches Institut, Universität Bonn, Bonn Lehrstuhl für Experimentelle Physik IV, Technische Universität Dortmund, Dortmund Institut für Kern- und Teilchenphysik, Technische Universität Dresden, Dresden Physikalisches Institut, Albert-Ludwigs-Universität Freiburg, Freiburg II. Physikalisches Institut, Justus-Liebig-Universität Giessen, Giessen II. Physikalisches Institut, Georg-August-Universität Göttingen, Göttingen Deutsches Elektronen-Synchrotron DESY, Hamburg and Zeuthen Kirchhoff-Institut für Physik, Ruprecht-Karls-Universität Heidelberg, Heidelberg; Physikalisches Institut, Ruprecht-Karls-Universität Heidelberg, Heidelberg Institut für Physik, Universität Mainz, Mainz Fakultät für Physik, Ludwig-Maximilians-Universität München, München Max-Planck-Institut für Physik (Werner-Heisenberg-Institut), München Department Physik, Universität Siegen, Siegen Fakultät für Mathematik und Naturwissenschaften, Fachgruppe Physik, Bergische Universität Wuppertal, Wuppertal Fakultät für Physik und Astronomie, Julius-Maximilians-Universität Würzburg, Würzburg

#### Greece

National Centre for Scientific Research "Demokritos", Agia Paraskevi Physics Department, National and Kapodistrian University of Athens, Athens Department of Physics, Aristotle University of Thessaloniki, Thessaloniki Physics Department, National Technical University of Athens, Zografou

#### Israel

Department of Physics, Technion, Israel Institute of Technology, Haifa Department of Particle Physics, Weizmann Institute of Science, Rehovot Raymond and Beverly Sackler School of Physics and Astronomy, Tel Aviv University, Tel Aviv

#### Italy

INFN Sezione di Bologna; Dipartimento di Fisica e Astronomia, Università di Bologna, Bologna

INFN e Laboratori Nazionali di Frascati, Frascati

INFN Sezione di Genova; Dipartimento di Fisica, Università di Genova, Genova INFN Sezione di Lecce; Dipartimento di Matematica e Fisica, Università del Salento, Lecce INFN Sezione di Milano; Dipartimento di Fisica, Università di Milano, Milano INFN Sezione di Napoli; Dipartimento di Fisica, Università di Napoli, Napoli INFN Sezione di Pavia; Dipartimento di Fisica, Università di Pavia, Pavia INFN Sezione di Pisa; Dipartimento di Fisica E. Fermi, Università di Pisa, Pisa INFN Gruppo Collegato di Cosenza, Laboratori Nazionali di Frascati; Dipartimento di Fisica, Università della Calabria, Rende

INFN Sezione di Roma; Dipartimento di Fisica, Sapienza Università di Roma, Roma INFN Sezione di Roma Tor Vergata; Dipartimento di Fisica, Università di Roma Tor Vergata, Roma

INFN Sezione di Roma Tre; Dipartimento di Matematica e Fisica, Università Roma Tre, Roma

INFN-TIFPA; Università degli Studi di Trento, Trento

INFN Gruppo Collegato di Udine, Sezione di Trieste, Udine; ICTP, Trieste; Dipartimento di Chimica, Fisica e Ambiente, Università di Udine, Udine

#### Japan

Research Center for Advanced Particle Physics and Department of Physics, Kyushu University, Fukuoka Faculty of Applied Information Science, Hiroshima Institute of Technology, Hiroshima Graduate School of Science, Kobe University, Kobe Faculty of Science, Kyoto University, Kyoto Kyoto University of Education, Kyoto Department of Physics, Shinshu University, Nagano Nagasaki Institute of Applied Science, Nagasaki Graduate School of Science and Kobayashi-Maskawa Institute, Nagoya University, Nagoya Faculty of Science, Okayama University, Okayama Graduate School of Science, Osaka University, Osaka Department of Physics, Tokyo Institute of Technology, Tokyo Graduate School of Science and Technology, Tokyo Metropolitan University, Tokyo International Center for Elementary Particle Physics and Department of Physics, University of Tokyo, Tokyo Waseda University, Tokyo Division of Physics and Tomonaga Center for the History of the Universe, Faculty of Pure and Applied Sciences, University of Tsukuba, Tsukuba KEK, High Energy Accelerator Research Organization, Tsukuba

#### Morocco

*Morocco Cluster*: Centre National de l'Energie des Sciences Techniques Nucleaires (CNESTEN), Rabat; Faculté des Sciences Ain Chock, Réseau Universitaire de Physique des Hautes Energies - Université Hassan II, Casablanca; Faculté des Sciences Semlalia, Université Cadi Ayyad, LPHEA-Marrakech; Faculté des Sciences, Université Mohamed Premier and LPTPM, Oujda; Faculté des sciences, Université Mohammed V, Rabat

#### Netherlands

Nikhef National Institute for Subatomic Physics and University of Amsterdam, Amsterdam

Institute for Mathematics, Astrophysics and Particle Physics, Radboud University Nijmegen/Nikhef, Nijmegen

#### Norway

Department for Physics and Technology, University of Bergen, Bergen Department of Physics, University of Oslo, Oslo

#### Poland

AGH University of Science and Technology, Faculty of Physics and Applied Computer Science, Krakow; Marian Smoluchowski Institute of Physics, Jagiellonian University, Krakow

Institute of Nuclear Physics Polish Academy of Sciences, Krakow

#### Portugal

*Portugal Cluster*: Laboratório de Instrumentação e Física Experimental de Partículas - LIP; Departamento de Física, Faculdade de Ciências, Universidade de Lisboa, Lisboa; Departamento de Física, Universidade de Coimbra, Coimbra; Departamento de Física, Universidade do Minho, Braga; Departamento de Física Teorica y del Cosmos, Universidad de Granada, Granada (Spain); Dep Física and CEFITEC of Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa, Caparica

#### Romania

*Romania Cluster*: Transilvania University of Brasov, Brasov; Horia Hulubei National Institute of Physics and Nuclear Engineering, Bucharest; National Institute for Research and Development of Isotopic and Molecular Technologies, Physics Department, Cluj-Napoca; Department of Physics, Alexandru Ioan Cuza University of Iasi, Iasi; University Politehnica Bucharest, Bucharest; West University in Timisoara, Timisoara

#### Russia

D.V. Skobeltsyn Institute of Nuclear Physics, M.V. Lomonosov Moscow State University, Moscow

Institute for Theoretical and Experimental Physics (ITEP), Moscow

National Research Nuclear University MEPhI, Moscow

P.N. Lebedev Physical Institute of the Russian Academy of Sciences, Moscow Novosibirsk State University Novosibirsk; Budker Institute of Nuclear Physics, SB RAS, Novosibirsk

State Research Center Institute for High Energy Physics, NRC KI, Protvino Konstantinov Nuclear Physics Institute of National Research Centre "Kurchatov Institute", PNPI, St. Petersburg

Tomsk State University, Tomsk

#### JINR

Joint Institute for Nuclear Research, Dubna, Russia

#### Serbia

Institute of Physics, University of Belgrade, Belgrade

#### Slovak Republic

*Slovak Republic Cluster*: Faculty of Mathematics, Physics and Informatics, Comenius University, Bratislava; Department of Subnuclear Physics, Institute of Experimental Physics of the Slovak Academy of Sciences, Kosice

#### Slovenia

Department of Experimental Particle Physics, Jožef Stefan Institute and Department of Physics, University of Ljubljana, Ljubljana

#### South Africa

*South Africa Cluster*: Department of Physics, University of Cape Town, Cape Town; Department of Mechanical Engineering Science, University of Johannesburg, Johannesburg; School of Physics, University of the Witwatersrand, Johannesburg

#### Spain

Institut de Física d'Altes Energies (IFAE), Barcelona Institute of Science and Technology, Barcelona

Departamento de Física Teorica C-15 and CIAFF, Universidad Autónoma de Madrid, Madrid

Instituto de Física Corpuscular (IFIC), Centro Mixto Universidad de Valencia - CSIC, Valencia

#### Sweden

Fysiska institutionen, Lunds universitet, Lund Department of Physics, Stockholm University; Oskar Klein Centre, Stockholm Physics Department, Royal Institute of Technology, Stockholm Department of Physics and Astronomy, University of Uppsala, Uppsala

#### Switzerland

Albert Einstein Center for Fundamental Physics and Laboratory for High Energy Physics, University of Bern, Bern

Département de Physique Nucléaire et Corpusculaire, Université de Genève, Genève

#### Taiwan

Department of Physics, National Tsing Hua University, Hsinchu Institute of Physics, Academia Sinica, Taipei

#### Turkey

*Ankara Cluster*: Department of Physics, Ankara University, Ankara; Istanbul Aydin University, Istanbul; Division of Physics, TOBB University of Economics and Technology, Ankara *Bogazici Cluster*: Bahcesehir University, Faculty of Engineering and Natural Sciences, Istanbul; Istanbul Bilgi University, Faculty of Engineering and Natural Sciences, Istanbul; Department of Physics, Bogazici University, Istanbul; Department of Physics Engineering, Gaziantep University, Gaziantep

#### **United Kingdom**

School of Physics and Astronomy, University of Birmingham, Birmingham Department of Physics and Astronomy, University of Sussex, Brighton Cavendish Laboratory, University of Cambridge, Cambridge Department of Physics, University of Warwick, Coventry Particle Physics Department, Rutherford Appleton Laboratory, Didcot SUPA - School of Physics and Astronomy, University of Edinburgh, Edinburgh Department of Physics, Royal Holloway University of London, Egham SUPA - School of Physics and Astronomy, University of Glasgow, Glasgow Physics Department, Lancaster University, Lancaster Oliver Lodge Laboratory, University of Liverpool Department of Physics and Astronomy, University College London, London School of Physics and Astronomy, University of Manchester, Manchester Department of Physics, Oxford University, Oxford Department of Physics and Astronomy, University of Sheffield, Sheffield

#### **United States of America**

Physics Department, SUNY Albany, Albany NY Department of Physics and Astronomy, University of New Mexico, Albuquerque NM Department of Physics and Astronomy, Iowa State University, Ames IA Department of Physics, University of Massachusetts, Amherst MA Department of Physics, University of Michigan, Ann Arbor MI High Energy Physics Division, Argonne National Laboratory, Argonne IL Department of Physics, University of Texas at Arlington, Arlington TX Department of Physics, University of Texas at Austin, Austin TX Physics Division, Lawrence Berkeley National Laboratory and University of California, Berkeley CA Department of Physics, Indiana University, Bloomington IN Department of Physics, Boston University, Boston MA Laboratory for Particle Physics and Cosmology, Harvard University, Cambridge MA Enrico Fermi Institute, University of Chicago, Chicago IL Ohio State University, Columbus OH Physics Department, Southern Methodist University, Dallas TX Department of Physics, Northern Illinois University, DeKalb IL Department of Physics, Duke University, Durham NC Department of Physics and Astronomy, Michigan State University, East Lansing MI Center for High Energy Physics, University of Oregon, Eugene OR

University of Iowa, Iowa City IA Department of Physics and Astronomy, University of California Irvine, Irvine CA Nevis Laboratory, Columbia University, Irvington NY Department of Physics, University of Wisconsin, Madison WI Department of Physics and Astronomy, Tufts University, Medford MA Department of Physics, Yale University, New Haven CT Department of Physics, New York University, New York NY Homer L. Dodge Department of Physics and Astronomy, University of Oklahoma, Norman OK Department of Physics, University of Pennsylvania, Philadelphia PA Department of Physics and Astronomy, University of Pittsburgh, Pittsburgh PA Physics Department, University of Texas at Dallas, Richardson TX Louisiana Tech University, Ruston LA Santa Cruz Institute for Particle Physics, University of California Santa Cruz, Santa Cruz CA Department of Physics, University of Washington, Seattle WA SLAC National Accelerator Laboratory, Stanford CA Department of Physics, Oklahoma State University, Stillwater OK Departments of Physics and Astronomy, Stony Brook University, Stony Brook NY Department of Physics, University of Arizona, Tucson AZ Physics Department, Brookhaven National Laboratory, Upton NY Department of Physics, University of Illinois, Urbana IL Department of Physics, Brandeis University, Waltham MA

# Contents

| Та | ble o | f Conte | ents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ix |

|----|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1  | Intr  | oductio | on and a second s | 1  |

| 2  | The   | Pixel I | Detector Layout and Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3  |

|    | 2.1   | Descri  | iption of the ITk Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3  |

|    |       | 2.1.1   | Methods used to optimised the ITk Detector Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5  |

|    |       | 2.1.2   | Description of the Inclined Duals Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7  |

|    | 2.2   | Simula  | ation of the ITk Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12 |

|    |       | 2.2.1   | Description of the Strip Detector in Geant4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15 |

|    |       | 2.2.2   | Description of the Pixel Detector in Geant4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16 |

|    |       | 2.2.3   | The Digitisation, Clustering and Track Reconstruction Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19 |

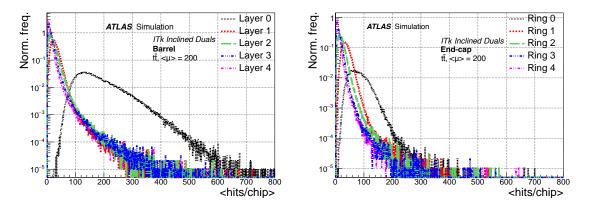

|    |       | 2.2.4   | Occupancies in Pixels from Simulation Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26 |

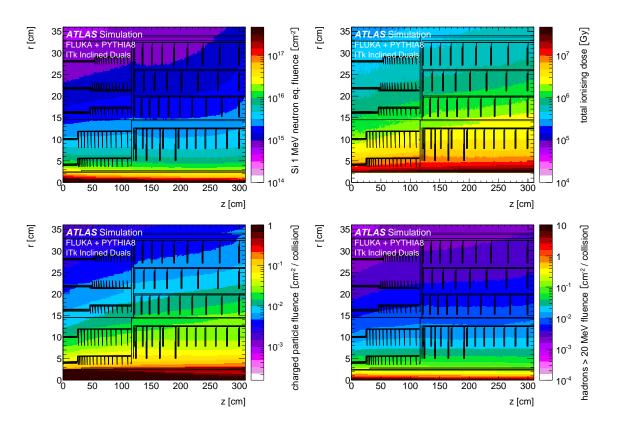

|    | 2.3   | Fluend  | ce and Radiation Dose Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30 |

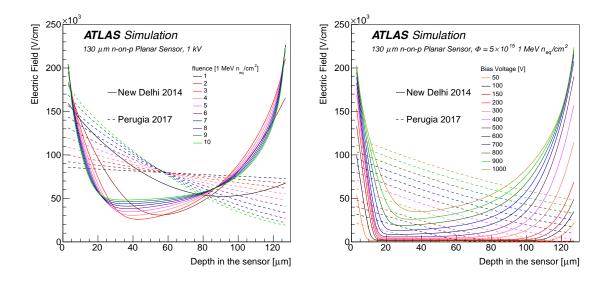

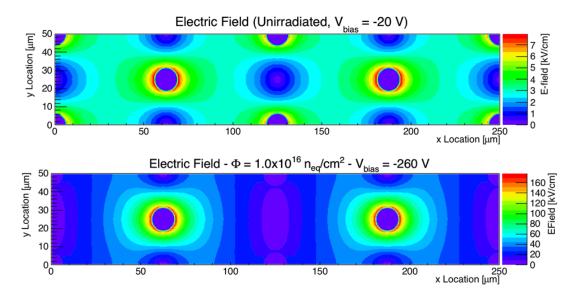

|    |       | 2.3.1   | Pixel Sensor Radiation Damage Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32 |

|    |       | 2.3.2   | Implications of a High Granularity Timing Detector on the ITk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35 |

| 3  | Trac  | king aı | nd Physics Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39 |

|    | 3.1   | Tracki  | ng and Vertexing Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40 |

|    |       | 3.1.1   | Tracking Efficiency and Fake Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40 |

|    |       | 3.1.2   | Track Parameter Resolutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44 |

|    |       | 3.1.3   | Alignment Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47 |

|    |       | 3.1.4   | Detector Performance Stability with Ageing and Component Failures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50 |

|    |       | 3.1.5   | Tracking in Dense Environments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52 |

|    |       | 3.1.6   | Primary Vertex Reconstruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55 |

|    | 3.2   | Physic  | cs Object Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60 |

|    |       | 3.2.1   | Photon Conversion Reconstruction Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 60 |

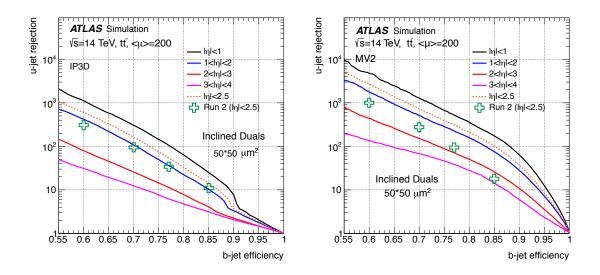

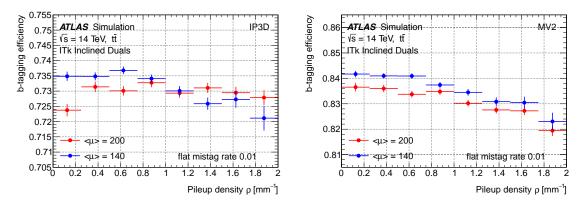

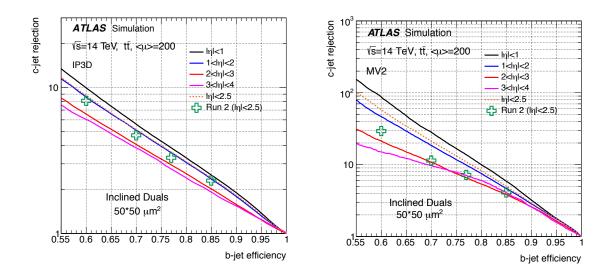

|    |       | 3.2.2   | Flavour Tagging Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 62 |

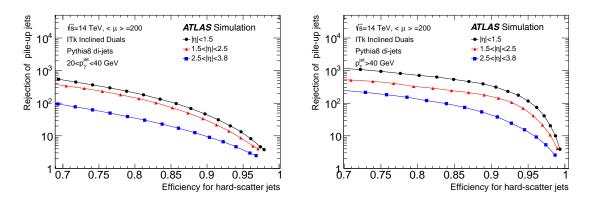

|    |       | 3.2.3   | Pile-up Jet Rejection and $E_{T}^{miss}$ Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65 |

|    |       | 3.2.4   | Electron and Muon Reconstruction and Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67 |

|    |       | 3.2.5   | Study of $	au$ Identification using the ITk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71 |

|    | 3.3   | Physic  | cs Benchmark Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72 |

|    |       | 3.3.1   | Higgs Boson Production in $\mu\mu$ and $4\mu$ Final States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75 |

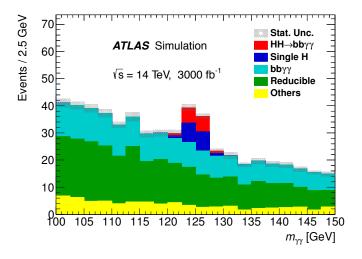

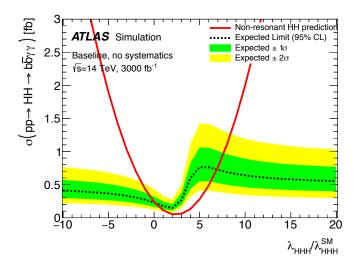

|    |       | 3.3.2   | Higgs Self-Coupling Measurement using the $HH \rightarrow b\bar{b}\gamma\gamma$ Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 76 |

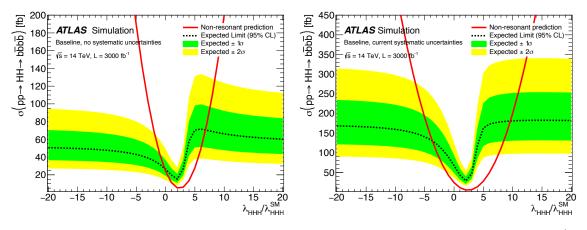

|   |      | 3.3.3 Higgs Self-Coupling Measurement using the $HH \rightarrow b\bar{b}b\bar{b}$ Channel | 78  |

|---|------|-------------------------------------------------------------------------------------------|-----|

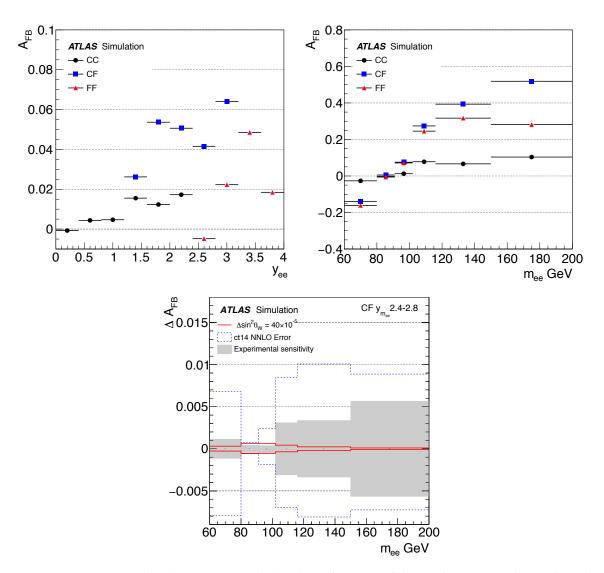

|   |      | 3.3.4 Prospects for a Precision Measurement of the Weak Mixing Angle                      | 80  |

|   |      | 3.3.5 Prospects for B-physics                                                             | 83  |

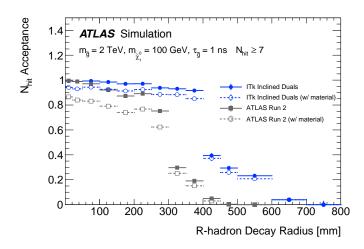

|   |      | 3.3.6 Prospects for SUSY Searches using the Disappearing Track Signature                  | 85  |

|   |      | 3.3.7 Prospects for SUSY Searches using the Displaced Vertex Signature                    | 87  |

| 4 | Tecl | nnical Overview                                                                           | 91  |

|   | 4.1  | Introduction                                                                              | 91  |

|   | 4.2  | Key requirements for the ITk design                                                       | 91  |

|   | 4.3  | Pixel Module                                                                              | 93  |

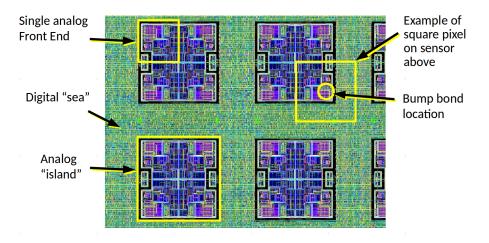

|   |      | 4.3.1 Front-end chip design in 65 nm technology                                           | 97  |

|   |      | 4.3.2 R&D on pixel sensors                                                                | 100 |

|   |      | 4.3.3 Hybridization                                                                       | 105 |

|   |      | 4.3.4 CMOS monolithic Pixel Detectors                                                     | 106 |

|   | 4.4  | Data Transmission                                                                         | 109 |

|   | 4.5  | Power Distribution                                                                        | 114 |

|   | 4.6  | Detector Control System                                                                   | 115 |

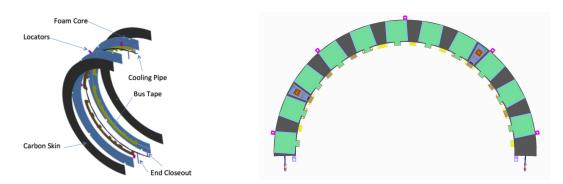

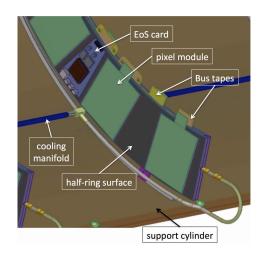

|   | 4.7  | Local supports                                                                            | 117 |

|   |      | 4.7.1 Constraints and Specifications                                                      | 117 |

|   |      | 4.7.2 Outer Barrel Local Supports                                                         | 119 |

|   |      | 4.7.3 Outer End-caps Local Supports                                                       | 120 |

|   |      | 4.7.4 Inner System Local Supports                                                         | 121 |

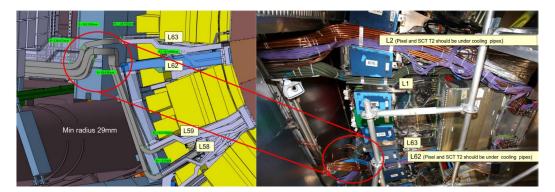

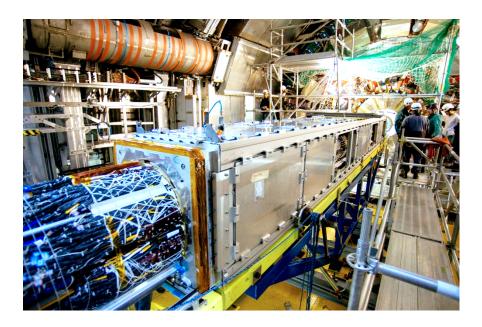

|   | 4.8  | Installation of the ITk into ATLAS                                                        | 122 |

|   | 4.9  | Decommissioning of the current Inner Tracking Detector                                    | 127 |

| 5 | Sen  | sors for the ITk Pixel Detector                                                           | 131 |

|   | 5.1  | Introduction and requirements for the ITk pixel sensors                                   | 131 |

|   | 5.2  | Overview of 3D pixel sensor technologies for ITk                                          | 131 |

|   | 5.3  | Overview of Planar pixel sensor technologies for the ITk Detector                         | 132 |

|   |      | 5.3.1 Passive CMOS sensors                                                                | 134 |

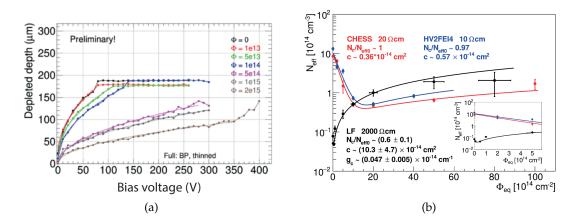

|   | 5.4  | 3D sensor characterization before and after irradiation                                   | 134 |

|   |      | 5.4.1 Electrical tests in the lab                                                         | 135 |

|   |      | 5.4.2 Test beam analysis                                                                  | 136 |

|   | 5.5  | Planar pixel sensor characterization before and after irradiation                         | 140 |

|   |      | 5.5.1 Electrical tests in the lab                                                         | 140 |

|   |      | 5.5.2 Test beam analysis                                                                  | 141 |

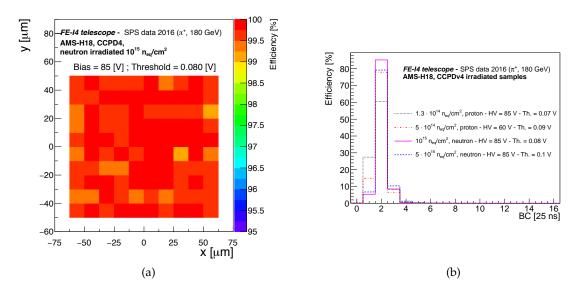

|   | 5.6  | Results with FE65-P2 and RD53A prototypes                                                 | 145 |

|   |      | 5.6.1 Planar pixel sensors characterization before and after irradiation                  | 145 |

|   |      | 5.6.2 Test beam analysis                                                                  | 146 |

|   | 5.7  | Discussion of open technological choices and production plans                             | 149 |

|   |      | 5.7.1 3D sensors options                                                                  | 149 |

|   |      | 5.7.2 3D Quality control and assurance                                                    | 149 |

|   |      | 5.7.3 Planar sensors options                                                              | 150 |

|   |      | 5.7.4 Planar Production plans                                         | 150 |

|---|------|-----------------------------------------------------------------------|-----|

|   |      | 5.7.5 Planar Quality control and assurance                            | 151 |

|   |      | 5.7.6 Path to the sensor decision in Layer 1                          | 151 |

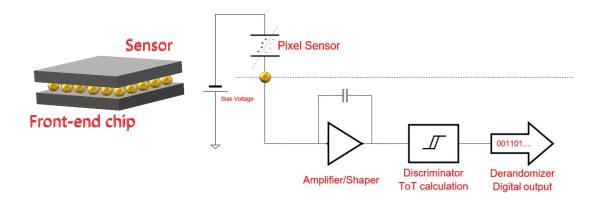

| 6 | From | nt-end Chips                                                          | 153 |

|   | 6.1  | Introduction and Requirements for the Front-end Chip                  | 153 |

|   |      | 6.1.1 Physical, Power, and Environmental Requirements for the FE chip | 153 |

|   |      | 6.1.2 Performance and Trigger Requirements for the FE chip            | 154 |

|   |      | 6.1.3 Electrical and Input/Output Requirements for the FE chip        | 155 |

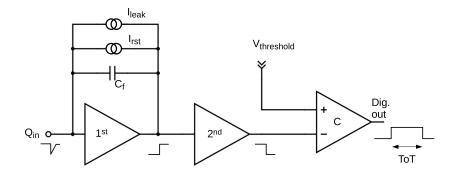

|   | 6.2  | Front-end Chip Description                                            | 156 |

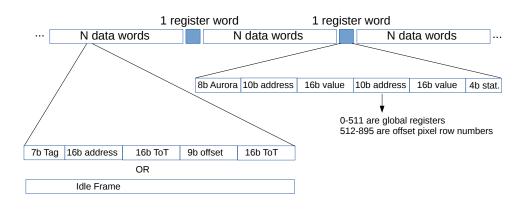

|   |      | 6.2.1 Command, Configuration, and Trigger                             | 158 |

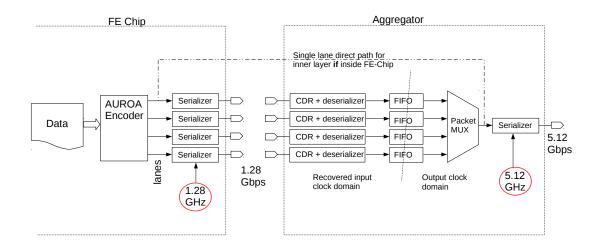

|   |      | 6.2.2 Output Data Transmission and Compression                        | 159 |

|   |      | 6.2.3 Serial powering                                                 | 163 |

|   | 6.3  | Development Status and Plan                                           | 164 |

|   |      | 6.3.1 The RD53 Collaboration and the RD53A Prototype                  | 164 |

|   |      | 6.3.2 Novel Features in RD53A                                         | 166 |

|   |      | 6.3.3 Changes from RD53A to Production                                | 167 |

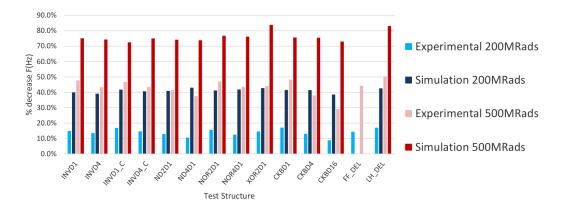

|   | 6.4  | Radiation Tolerance                                                   | 168 |

|   |      | 6.4.1 Total Dose Tolerance and Modeling                               | 169 |

|   |      | 6.4.2 Single Event Upsets                                             | 170 |

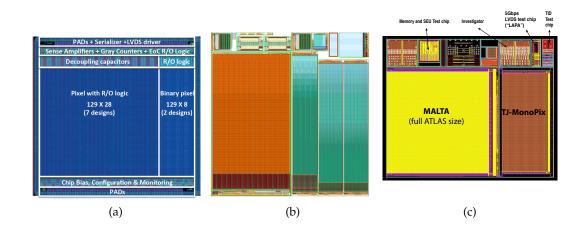

|   | 6.5  | Prototype Test Chips                                                  | 171 |

|   |      | 6.5.1 FE65-P2 and Chipix Test Chips                                   | 171 |

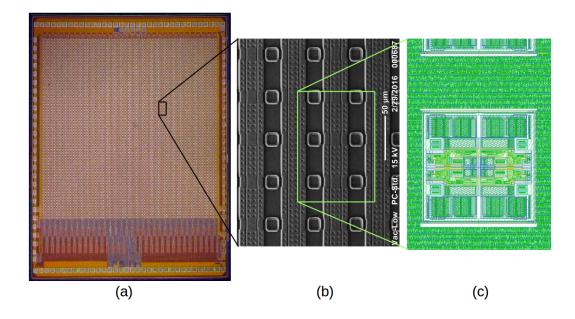

|   |      | 6.5.2 RD53A Chip                                                      | 176 |

| 7 | Pixe | el module Hybridization                                               | 177 |

|   | 7.1  | Introduction                                                          | 177 |

|   | 7.2  | Bare module assembly process                                          | 179 |

|   |      | 7.2.1 Front-end chip and sensor wafers                                | 179 |

|   |      | 7.2.2 Assembly process outline                                        | 179 |

|   |      | 7.2.3 Bump growth and flip-chip bonding                               | 181 |

|   |      | 7.2.4 Sensor UBM                                                      | 182 |

|   |      | 7.2.5 Front-end chip bow                                              | 182 |

|   |      | 7.2.6 High Voltage protection                                         | 183 |

|   | 7.3  | Hybridization specifications                                          | 183 |

|   | 7.4  | Planned quality control and quality assurance during production       | 184 |

|   |      | 7.4.1 At the vendors                                                  | 184 |

|   |      | 7.4.2 At the ITk institutes                                           | 185 |

|   | 7.5  | Vendor engagement                                                     | 186 |

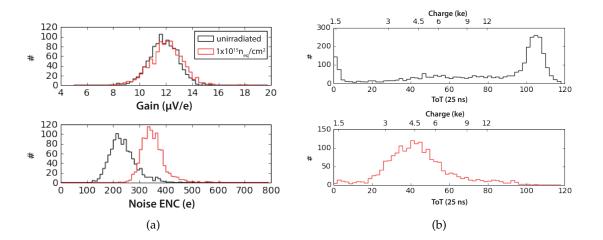

|   | 7.6  | Test results of thin FE-I4 prototype modules                          | 188 |

|   | 7.7  | Test results of ATLAS daisy chain prototype modules                   | 191 |

|   | 7.8  | Future hybridization development plans and production risks           | 193 |

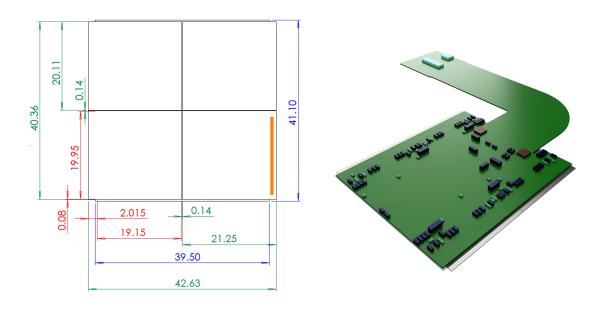

| 8 | Pixe | el Modules                                                            | 195 |

|    | 8.1  | Introduction and requirements for the ITk Pixel modules           | 195 |

|----|------|-------------------------------------------------------------------|-----|

|    | 8.2  | Components of ITk Pixel Modules                                   | 198 |

|    |      | 8.2.1 Bare Modules                                                | 198 |

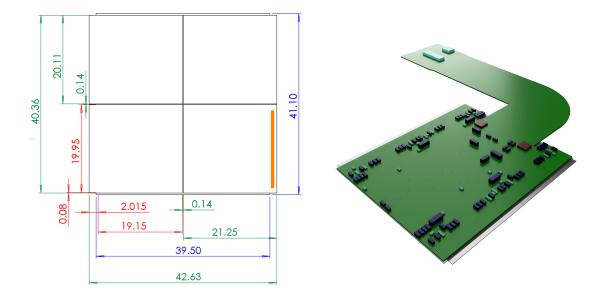

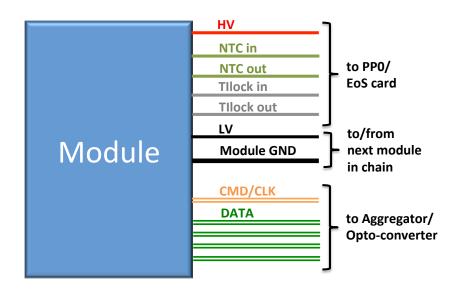

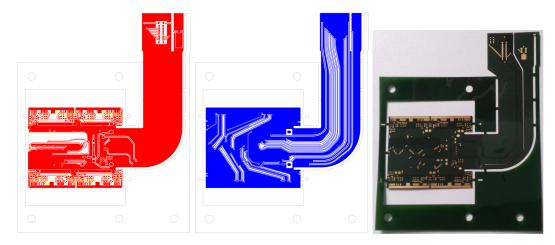

|    |      | 8.2.2 Module Flex                                                 | 199 |

|    |      | 8.2.3 DCS chip                                                    | 200 |

|    |      | 8.2.4 Aggregator Chip                                             | 201 |

|    |      | 8.2.5 Material budget of the ITk pixel module                     | 201 |

|    | 8.3  | Pixel Module Assembly and Quality Control                         | 202 |

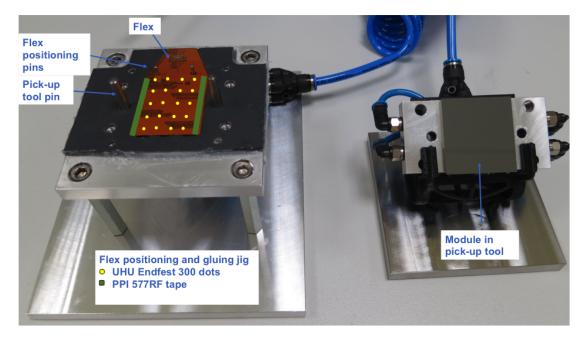

|    |      | 8.3.1 Module Assembly Steps                                       | 202 |

|    |      | 8.3.2 Planned Quality Control during Production                   | 206 |

| 9  | CM   | OS pixel                                                          | 211 |

|    | 9.1  | Motivation and R&D Overview                                       | 211 |

|    | 9.2  | CMOS sensors in the ITk                                           | 214 |

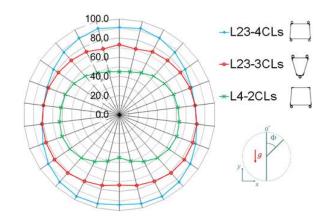

|    |      | 9.2.1 Tracking performance studies                                | 215 |

|    | 9.3  | CMOS pixel sensor developments: Designs and Performance           | 216 |

|    |      | 9.3.1 Large Fill-Factor CMOS sensors                              | 217 |

|    |      | 9.3.2 Small Fill-Factor CMOS sensors                              | 225 |

|    | 9.4  | Towards a CMOS Pixel Module and Stave                             | 230 |

|    |      | 9.4.1 ATLAS CMOS-1 sensor design and periphery                    | 232 |

|    |      | 9.4.2 Demonstration of CMOS technology for module design          | 233 |

|    | 9.5  | CMOS-pixel deployment plan for ATLAS ITk                          | 234 |

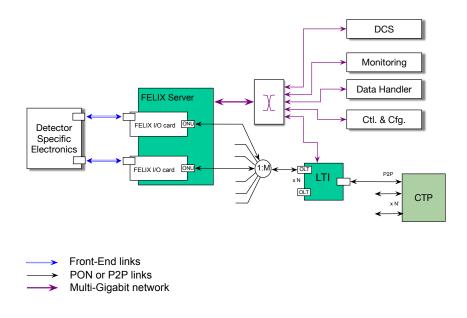

| 10 | Pixe | l Data Acquisition and Front End Control System                   | 237 |

|    | 10.1 | Introduction                                                      | 237 |

|    | 10.2 | Read-out Simulation Studies                                       | 239 |

|    | 10.3 | Link Architecture                                                 | 241 |

|    |      | 10.3.1 Downlinks                                                  | 241 |

|    |      | 10.3.2 Uplinks                                                    | 241 |

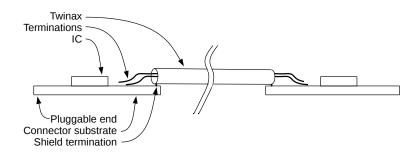

|    |      | 10.3.3 Electrical Links                                           | 244 |

|    |      | 10.3.4 Optical Components                                         | 247 |

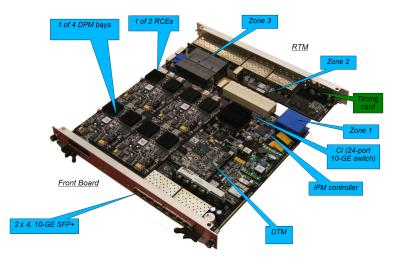

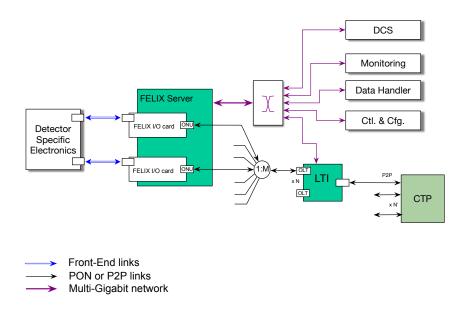

|    | 10.4 | Off-Detector Electronics                                          | 251 |

|    | 10.5 | System Test                                                       | 253 |

|    | 10.6 | Testing and DAQ Software                                          | 254 |

|    |      | 10.6.1 Software Design                                            | 254 |

|    |      | 10.6.2 Calibration Performance Requirements                       | 257 |

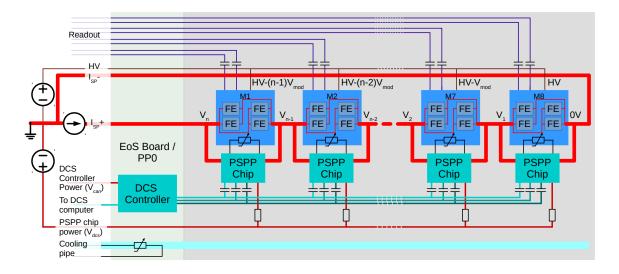

| 11 | Pow  | er Distribution, Grounding and Shielding, Detector Control System | 259 |

|    | 11.1 | ITk Pixel Powering                                                | 259 |

|    |      | 11.1.1 Serial Powering (LV)                                       | 259 |

|    |      | 11.1.2 Sensor Bias (HV) and Switch                                | 261 |

|    |      | 11.1.3 Cables and Patch Panels                                    | 262 |

|    |      | 11.1.4 Power Requirements and Dissipation                         | 263 |

|    | 11.1.5 The power supply system for the ITk Pixel Detector        | 264 |

|----|------------------------------------------------------------------|-----|

|    | 11.2 Grounding and Shielding                                     | 265 |

|    | 11.3 Detector Control System                                     | 267 |

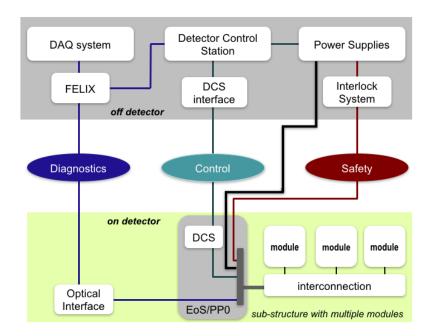

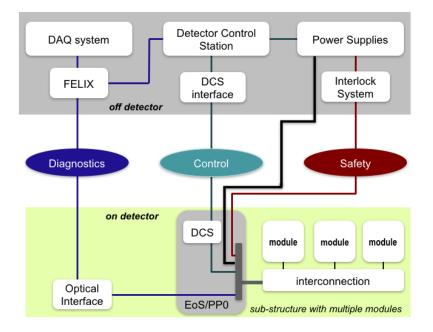

|    | 11.3.1 Overview of the DCS                                       | 267 |

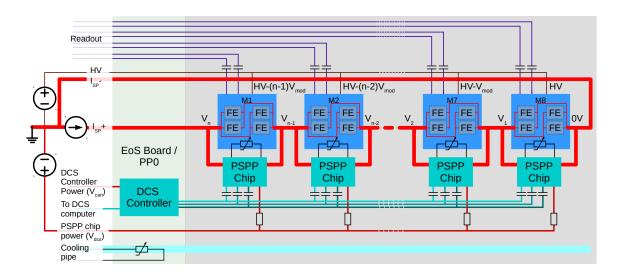

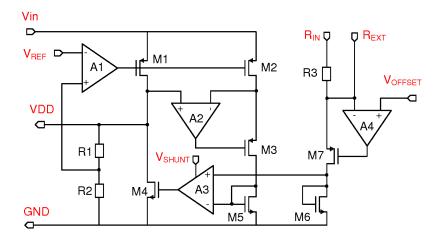

|    | 11.3.2 Pixel Serial Powering Protection Chip (PSPP)              | 269 |

|    | 11.4 Timescales                                                  | 269 |

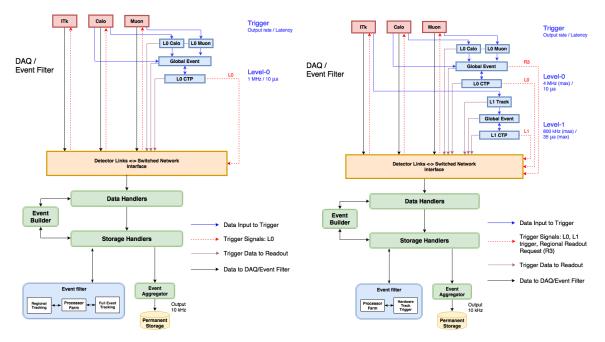

| 12 | Common Electronics                                               | 271 |

|    | 12.1 The ITk-TDAQ Interface and the ITk Read-out Group           | 271 |

|    | 12.2 Environmental Monitoring                                    | 273 |

|    | 12.3 Interlocks                                                  | 274 |

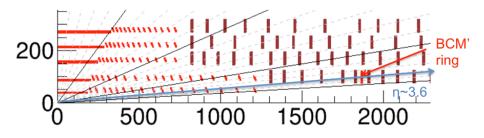

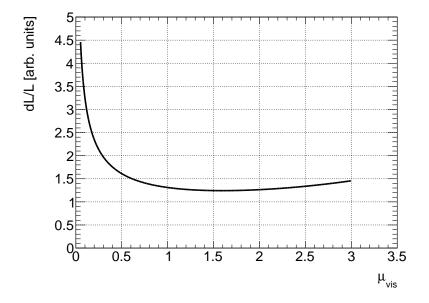

|    | 12.4 Beam Conditions monitoring and protection                   | 275 |

| 13 | Local Supports                                                   | 281 |

|    | 13.1 Local Supports Specifications                               | 281 |

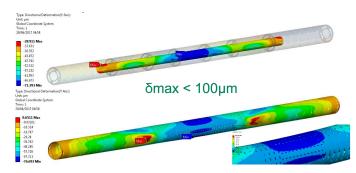

|    | 13.1.1 Geometrical Performance                                   | 282 |

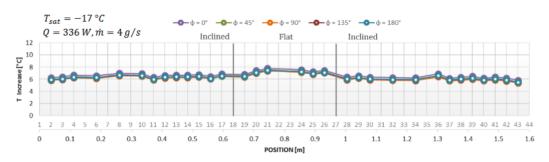

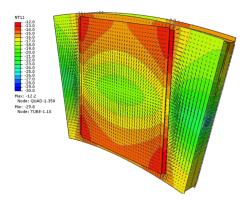

|    | 13.1.2 Thermal Performance                                       | 283 |

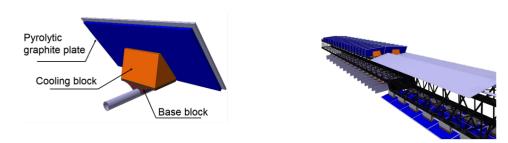

|    | 13.2 Thermo-Mechanical Design                                    | 286 |

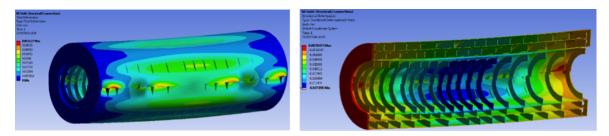

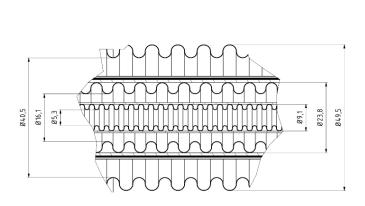

|    | 13.2.1 Cooling pipes for the Pixel Detector                      | 286 |

|    | 13.2.2 Local Supports for the Outer Barrel Layers                | 286 |

|    | 13.2.3 Local Supports for the Outer End-caps                     | 291 |

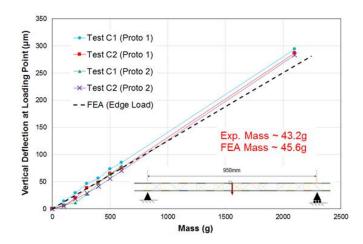

|    | 13.2.4 Local Supports for the Innermost Layers                   | 293 |

|    | 13.3 Local Support Qualification and Prototyping                 | 295 |

|    | 13.3.1 Outer Barrel and Baseline Inclined Inner Systems          | 295 |

|    | 13.3.2 Outer End-caps                                            | 298 |

|    | 13.4 Local Electrical Services                                   | 301 |

|    | 13.4.1 Outer Barrel                                              | 301 |

|    | 13.4.2 Outer End-caps                                            | 303 |

|    | 13.4.3 Innermost System                                          | 303 |

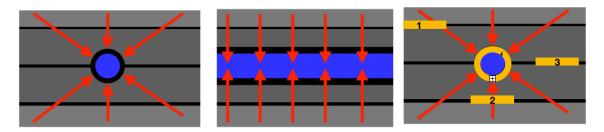

|    | 13.5 Module Loading and Replacement                              | 303 |

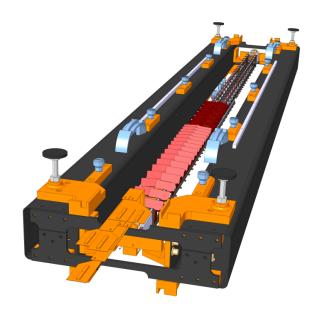

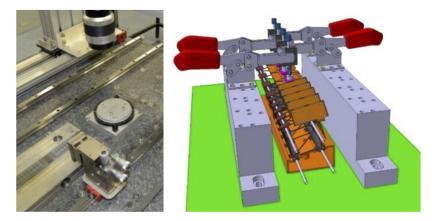

|    | 13.5.1 Module Loading for the Outer Barrel and Innermost Systems | 304 |

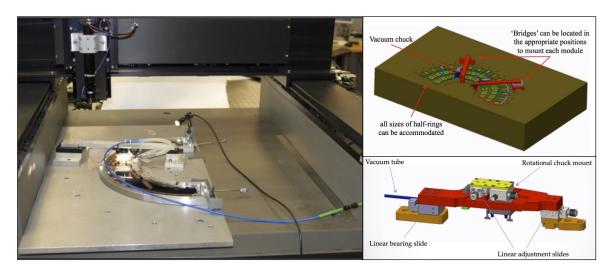

|    | 13.5.2 Module Loading for the Outer End-caps                     | 305 |

|    | 13.6 Local Support Quality Assurance and Quality Control         | 307 |

|    | 13.6.1 Thermal Quality Control                                   | 309 |

|    | 13.7 Decision path and timeline                                  | 311 |

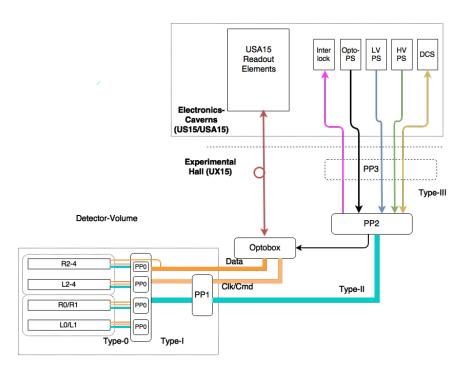

| 14 | Services                                                         | 313 |

|    | 14.1 Cable Inventory                                             | 313 |

|    | 14.2 Cooling                                                     | 315 |

|    | 14.2.1 Cooling Modularity and Mapping                            | 315 |

| 15 | Common Mechanics                                                 | 319 |

|    | 15.1 Common Structures                                           | 319 |

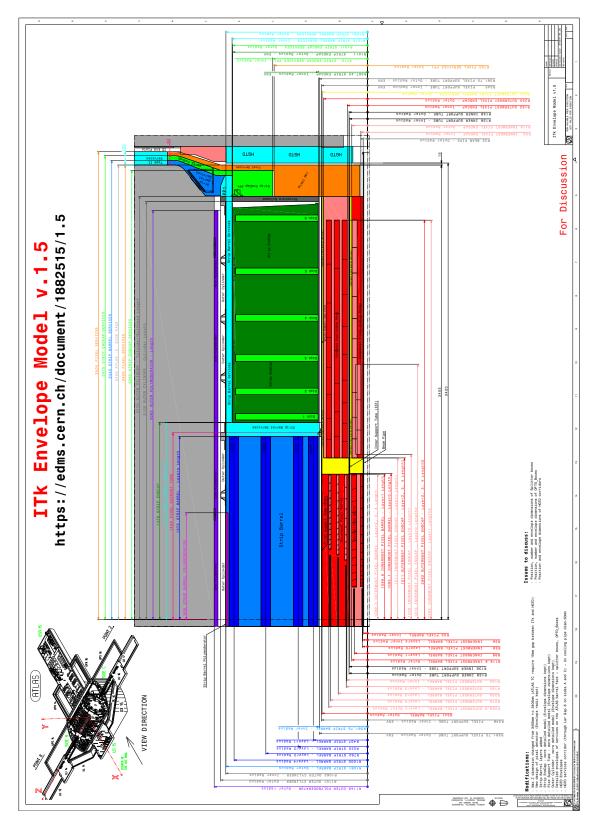

|    |      | 15.1.1 Envelopes and Interfaces                                      | 321 |

|----|------|----------------------------------------------------------------------|-----|

|    |      | 15.1.2 Support Hierarchy                                             | 323 |

|    | 15.2 | Global Mechanics                                                     | 324 |

|    |      | 15.2.1 Outer Cylinder and Structural Bulkhead                        | 324 |

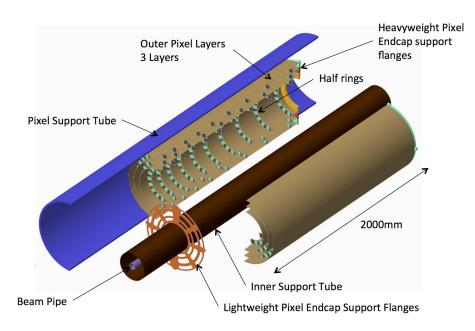

|    |      | 15.2.2 Pixel Support Tube                                            | 324 |

|    | 15.3 | External Mechanical Interfaces                                       | 326 |

|    |      | 15.3.1 External Envelopes for services                               | 326 |

|    |      | 15.3.2 Service Routing on Inner Detector End Plate                   | 327 |

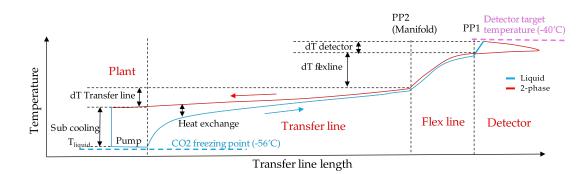

|    | 15.4 | Baby-DEMO low temperature CO <sub>2</sub> research                   | 327 |

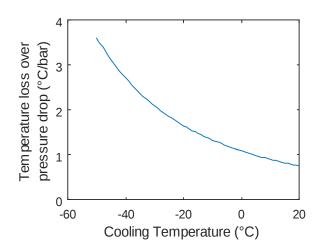

|    |      | 15.4.1 The challenges of CO <sub>2</sub> cooling at low temperatures | 327 |

|    |      | 15.4.2 Baby-DEMO cold temperature R&D system                         | 329 |

|    |      | 15.4.3 Real scale cooling distribution                               | 329 |

|    |      | 15.4.4 Baby-DEMO test results                                        | 331 |

|    |      | 15.4.5 Future aspects                                                | 332 |

| 16 | Surf | ace Integration, Commissioning and Associated Testing                | 335 |

|    | 16.1 | Commissioning activities and Schedule                                | 335 |

|    | 16.2 | Subsystem integration                                                | 336 |

|    |      | 16.2.1 Outer barrel pixel integration                                | 336 |

|    |      | 16.2.2 End-cap pixel integration, transport and reception            | 337 |

|    |      | 16.2.3 Inner pixel integration and reception                         | 339 |

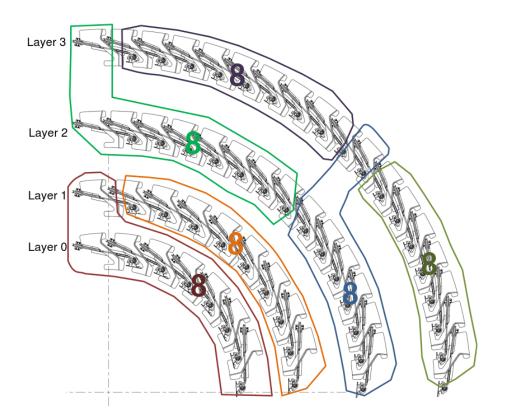

|    |      | 16.2.4 Barrel strip integration                                      | 339 |

|    |      | 16.2.5 End-cap strip integration and reception                       | 340 |

|    | 16.3 | ITk integration                                                      | 341 |

|    |      | 16.3.1 Strip EC insertion and cold test of strip systems             | 341 |

|    |      | 16.3.2 Insertion of the pixel systems and tests                      | 342 |

|    | 16.4 | Surface commissioning                                                | 343 |

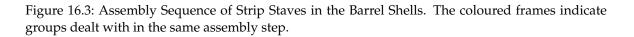

|    | 16.5 | SR1 preparations                                                     | 343 |

|    |      | 16.5.1 Cooling system requirements during integration                | 344 |

|    |      | 16.5.2 Long term use of SR1                                          | 346 |

| 17 | Inst | allation                                                             | 349 |

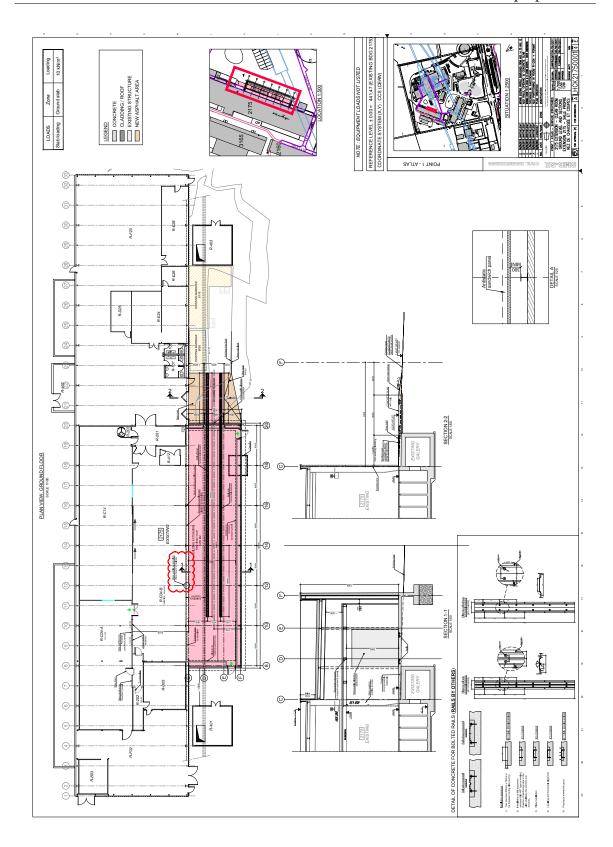

|    | 17.1 | Overview over the ATLAS Area                                         | 349 |

|    | 17.2 | ATLAS Opening Configuration and Infrastructure                       | 350 |

|    | 17.3 | Preparations of the Cryostat before the ITk Insertion                | 351 |

|    | 17.4 | ITk Transport                                                        | 354 |

|    |      | 17.4.1 Crane Operation                                               | 355 |

|    |      | 17.4.2 Rotation and Translation                                      | 358 |

|    |      | 17.4.3 Insertion of ITk into the Cryostat                            | 362 |

|    | 17.5 | Service Installation                                                 | 363 |

|    |      | 17.5.1 Type-II Service Installation on the Cryostat Wall             | 364 |

|    |      | 17.5.2 Patch Panel 2 Installation and Connection                     | 365 |

|    |      | 17.5.3 Type-III and -IV service installation                         | 369 |

|    |                                                                 | Contents |

|----|-----------------------------------------------------------------|----------|

|    | 17.6 Radioprotection and Personal Safety during Installation    | 369      |

| 18 | Inner Detector Decommissioning                                  | 371      |

| _  | 18.1 Introduction                                               | 371      |

|    | 18.2 Sequence of the Inner Detector Extraction                  | 371      |

|    | 18.2.1 Preparation Work & General Guidelines                    | 371      |

|    | 18.2.2 Proposed Sequence of Decommissioning                     | 372      |

|    | 18.2.3 End of Decommissioning Sequence                          | 375      |

|    | 18.2.4 Estimated Time Schedule                                  | 375      |

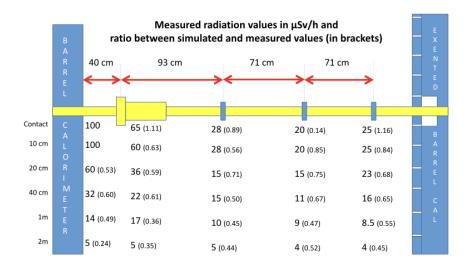

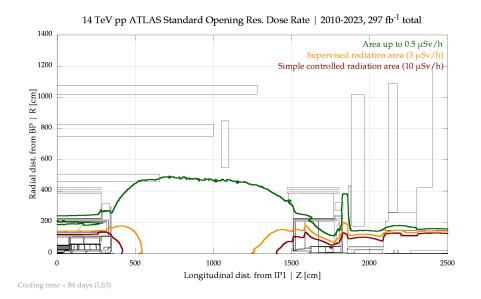

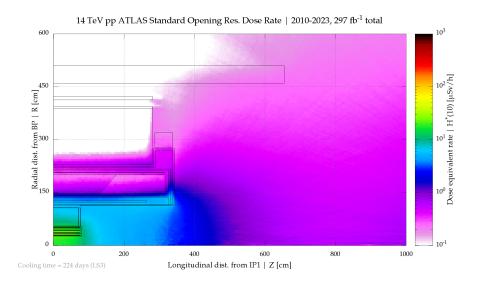

|    | 18.3 Radiation Protection Simulations and ALARA Considerations  | 375      |

|    | 18.3.1 Comparison of Simulated Radiation Levels to Measurements | 375      |

|    | 18.3.2 Radiation Simulations prepared for LS3                   | 377      |

|    | 18.3.3 Radioactive Waste Management                             | 378      |

|    | 18.3.4 ALARA Considerations                                     | 381      |

|    | 18.4 Training and Optimisation                                  | 381      |

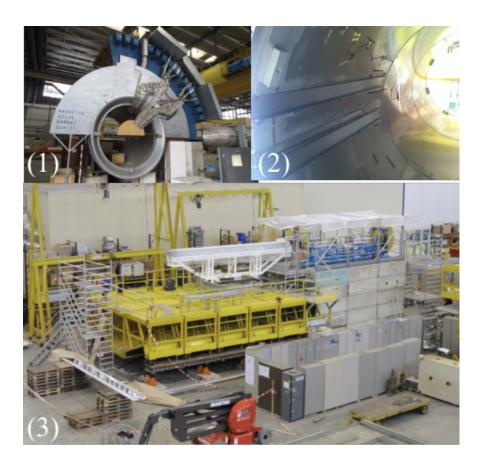

|    | 18.4.1 Upgrade to the ATLAS Mockups                             | 381      |

|    | 18.4.2 Dose Optimisation                                        | 383      |

|    | 18.4.3 Proposed Shielding                                       | 384      |

|    | 18.4.4 Conclusion                                               | 385      |

| 19 | Production Model and Schedule                                   | 387      |

|    | 19.1 Introduction                                               | 387      |

|    | 19.1.1 Work Breakdown Structure                                 | 388      |

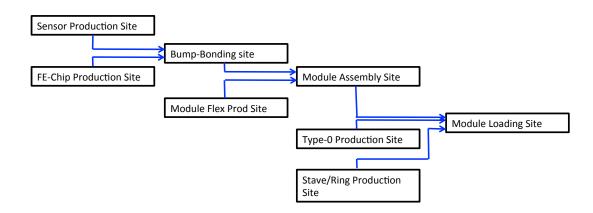

|    | 19.1.2 Production Responsibilities Flow                         | 390      |

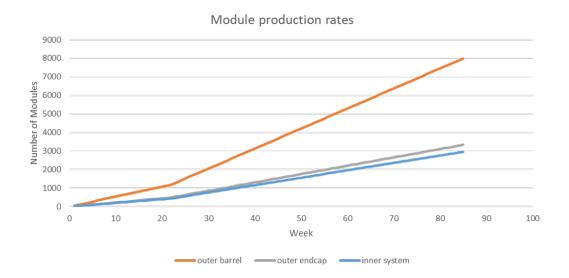

|    | 19.2 Global Production Plan                                     | 391      |

|    | 19.3 Module Loading on Local Supports                           | 395      |

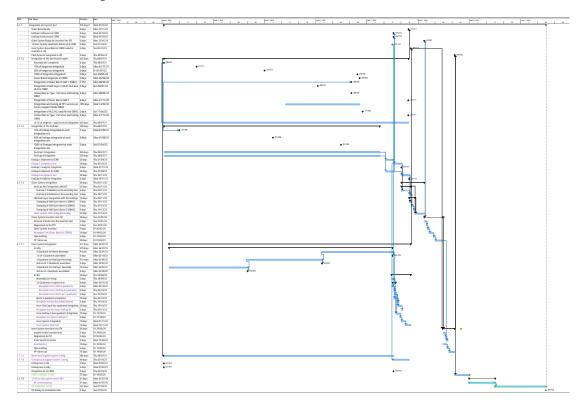

|    | 19.4 Production Schedule                                        | 396      |

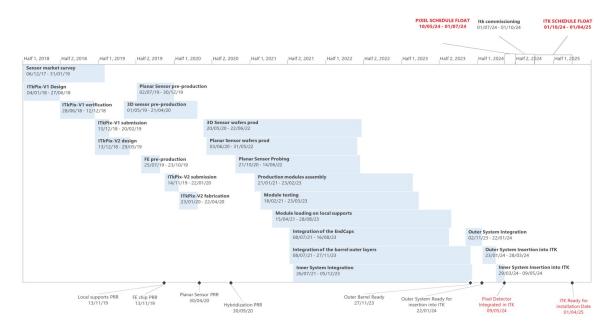

|    | 19.4.1 Overall Schedule                                         | 396      |

|    | 19.4.2 Market Surveys, Pre-production and Production            | 396      |

|    | 19.4.3 Preparation for the Installation of the ITk              | 397      |

|    | 19.4.4 The ITk Pixel Detector Schedule                          | 399      |

|    | 19.4.5 Production of the services for the ITk Pixel Detector    | 401      |

|    | 19.4.6 Local Supports                                           | 402      |

|    | 19.4.7 Integration of the ITk Pixel Detector                    | 403      |

|    | 19.4.8 Common Structures for the ITk                            | 403      |

|    | 19.4.9 Power supplies                                           | 404      |

|    | 19.4.10 ITk DAQ Schedule                                        | 404      |

| 20 | Costing                                                         | 407      |

|    | 20.1 Introduction                                               | 407      |

|    | 20.2 The Yield Model                                            | 408      |

|    | 20.3 Pre-production, NRE, Exchange rates and Quality Factors    | 408      |

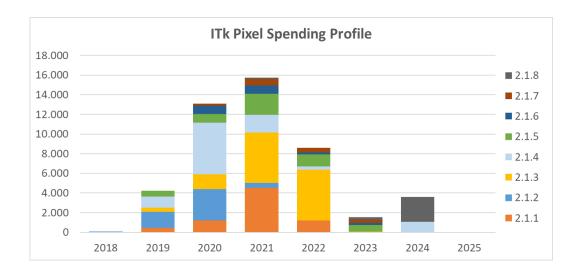

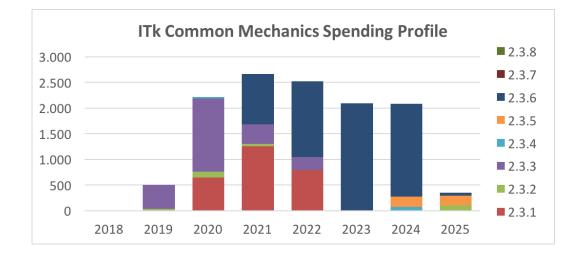

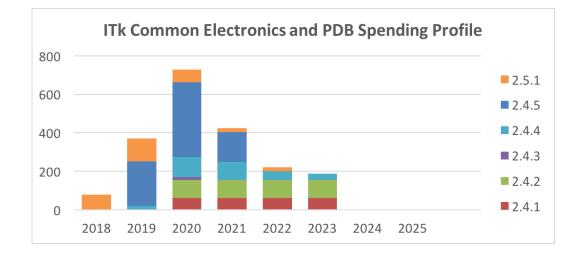

|    | 20.4 Current core cost estimates and the spend profile          | 410      |

| 20.5 The core cost of an ITk Pixel Module                        | 410 |

|------------------------------------------------------------------|-----|

| 20.6 The core cost of the local supports of the Pixel Detector   | 411 |

| 20.7 The core cost of the Pixel Read-out and associated services | 411 |

| 20.8 The core costs of Pixel loading and integration             | 412 |

| 20.9 The total core cost of the Pixel Detector                   | 412 |

| 20.10ITk Common Items                                            | 412 |

| 20.11Total Cost of the ITk Detector                              | 413 |

| 21 Risk Analysis and Risk Mitigation                             | 417 |

| 21.1 Introduction and overview                                   | 417 |

| 21.2 Risk Management Plan                                        | 418 |

| 21.3 Risk Register                                               | 418 |

| Bibliography                                                     | 432 |

| The ATLAS Collaboration                                          | 433 |

# 1 Introduction

This is the second of two Technical Design Reports that describe the upgrade of the central tracking system for the ATLAS experiment (Inner Tracker, ITk) as part of the preparation for the operation at the High Luminosity Large Hadron Collider (HL-LHC) that will start in the middle of 2026. In the first report, published in April 2017, the design, development and plans for the production of the ITk Strip Detector were presented [1]. In this document, the design, development, results of measurements on prototypes and plans for the production of the ITk Pixel Detector are presented, together with updates of the design of the common ITk mechanics and electronics systems.

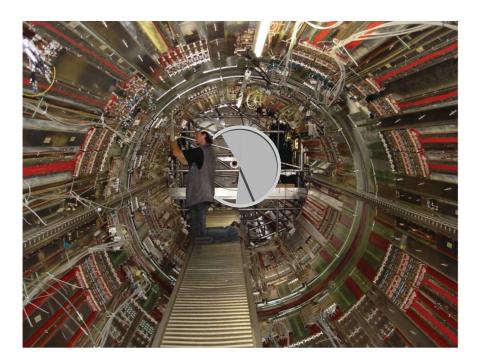

Meeting all of the requirements of a charged particle tracking detector close to the beamline at the HL-LHC presents a unique challenge for the design of an all-silicon system that consists of a Pixel Detector at small radius and a large area Strip Detector surrounding it. The design of the ITk benefits from the enormous amount of experience gained over more than two decades in the construction and operation of the existing inner tracking detector that has been highly successful for the exploitation of LHC physics up to and well beyond its original design requirements. This is particularly true of the existing Pixel system that was upgraded in 2015 during the first Long Shutdown (LS1) of the LHC with the insertion of an additional pixel layer within 3.4 cm of the beam line. This so called Insertable b-Layer (IBL) uses a combination of sensor technologies, including high-resistivity, planar and 3D, silicon detectors [2, 3]. These technologies are also proposed for the ITk Pixel Detector.

The design of the ITk Pixel Detector proposed in this document is based on the highly successful concept of "Hybrid Pixel Detector" developed for and implemented in the present ATLAS Pixel Detector [4] and in the IBL. However, it is clear that the very particular requirements imposed for a Pixel Detector operating at HL-LHC demand the development and implementation of new technical solutions. The HL-LHC will operate at an instantaneous luminosity up to  $\mathcal{L} = 7.5 \times 10^{34} \text{ cm}^{-2} \text{s}^{-1}$  which corresponds to an average of approximately 200 inelastic proton-proton collisions per beam crossing. The ITk will have to operate over the entire LHC Phase II program, delivering an integrated luminosity of 4000 fb<sup>-1</sup>. In order to cope with these requirements, and to maintain the same tracking performance as the present ATLAS Inner Detector, the layout of the ITk required a careful optimization that is described in detail in Chapters 2 and 3. Also the implementation of the Hybrid Pixel Detector concept required several adaptations and in some case the use of novel technologies to adapt to the HL-LHC conditions. The most significant improvements and novel solutions are summarized in Chapter 4 and analysed in detail in Chapters 5 to 18. Most of

#### 1 Introduction

relative merits of the different solutions are discussed and the decision making process and timeline for the decision are presented.

In designing the ITk, the aim has been to be able to reuse many of the existing services that are in place for the current Inner Detector. Many of the existing high and low voltage cables can be re-used over most of their length between the side-caverns and patch panels close to the detector. It will also be possible to reuse the cable cooling plant and the dry gas system which provides dry gas to the existing Inner Detector. The design of the services was illustrated in the Strip TDR and in this document only updates are given in Chapter 14.

The ITk will be installed as a single monolithic unit into the centre of ATLAS. Particular care has been taken to reduce the time on the beam line and rapid connection techniques are being prototyped so that the detector can be ready for operation a few months after installation. The safe decommissioning and disposal of the existing tracking detector and the plans for the insertion and connection of the ITk have been have been presented in the Strip TDR and will be updated here.

As well as the numerous technical challenges, the construction of a Pixel Detector of the scale that is proposed demands a new approach to the organization of the bulk component production. The active surface of the new tracker is more than 10 times larger than in the existing silicon Inner Detector and it will be constructed over just three years.

The infrastructure for tracking the production of parts of sufficiently high quality, on time and to agreed costs will require significant development and more oversight than was used in the past. A comprehensive set of quality assurance and quality control procedures will have to be developed and included from the beginning in the production plan. Particular attention will be devoted to the monitoring of the rate and quality of the module production.

The various aspects of the project management, in particular the details of the production model and the production schedule are outlined in Chapter 19. The management and internal organisation of the ITk, including its interaction with the rest of the experiment were discussed in the Strip TDR (Chapter 23) and will not be repeated here. Chapter 20 covers an analysis of the preliminary cost estimate of the Pixel Detector and of the ITk Common Electronics and Common Mechanics work packages. The assumptions that form the construction plan and the mitigation strategies that will aid successful delivery are captured in the Risk Management Plan and Risk Register (see Chapter 21).

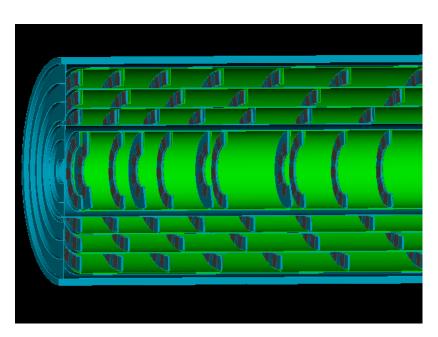

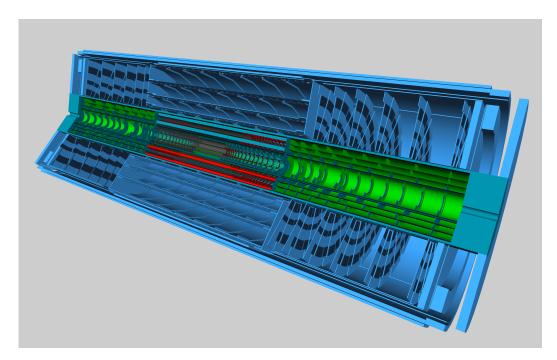

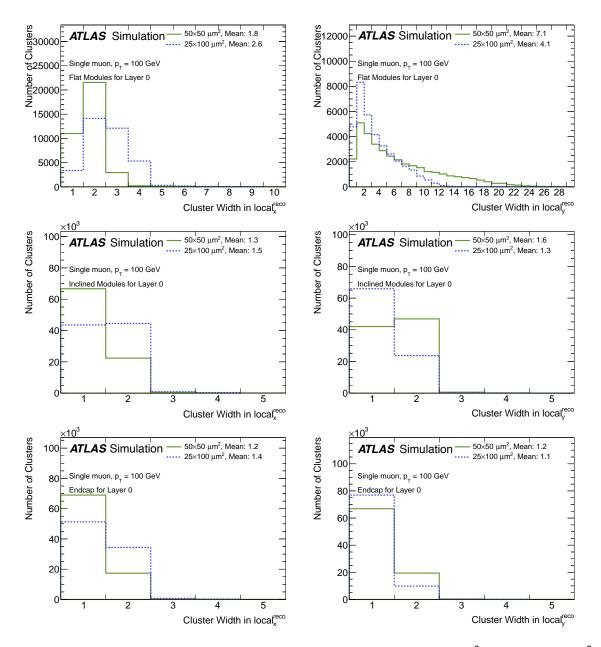

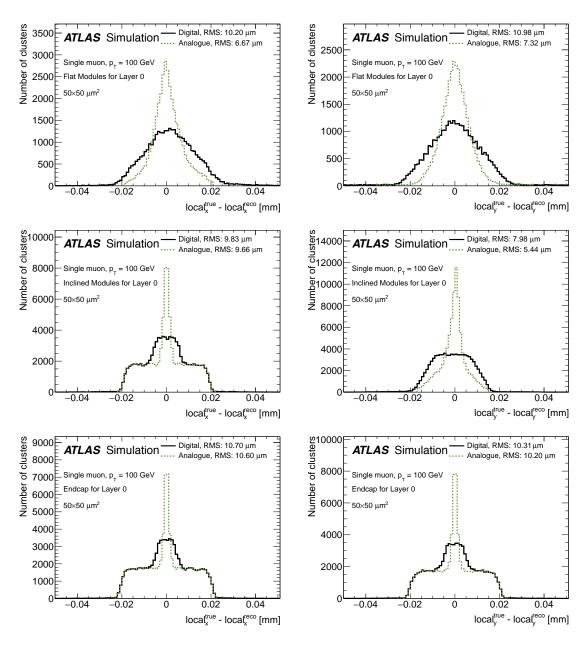

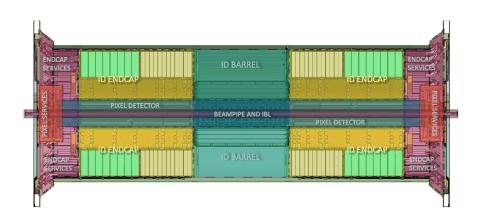

# **2** The Pixel Detector Layout and Simulation

The layout presented in this chapter is the baseline for the ITk Pixel Detector and is used as a reference throughout the rest of the document. The layout is an evolution of the concepts developed in the ITk Strip Technical Design Report [1] and follows the same guiding principles of an extended barrel stave with inclined sensors in the forward region of pseudorapidity<sup>1</sup>. It represents a major step towards a fully engineered detector design, taking into account the engineering constraints and benefiting from recent developments in pixel module design to achieve optimal detector performance for a fully efficient tracker covering  $|\eta| < 4$ , and simultaneously achieving all other performance goals as outlined in the Strip TDR. In the second part of this chapter the Geant4 simulation [5] of the ATLAS ITk is presented. The description of the Pixel Detector has been improved and, compared to the ITk Strip TDR, takes into account more of the engineering detail. In particular, the simulation results presented in this document are based on a more detailed description of the detector including stave supports and services. This allows for an improved description of the Pixel Detector material and a better understanding of how the material affects the tracking performance. Radiation dose and fluence results are also presented, using an equivalent ITk simulation model implemented in the FLUKA [6] framework.

#### 2.1 Description of the ITk Layout

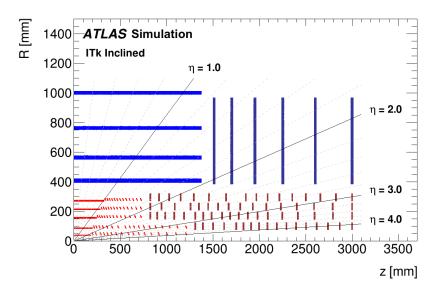

The layout presented in this chapter is based on one of the candidate layouts described in the Strip TDR called "Inclined Layout". This layout is shown in Figure 2.1 taken from Reference [1]. The Inclined Layout represents a significant evolution compared to the layouts discussed in the ATLAS Phase-II Upgrade Letter of Intent [7] and in the Phase-II Upgrade Scoping document [8]. Like the reference detector layout from the Phase-II Upgrade Scoping document, the detector design presented in the Strip TDR combines precision central tracking in the presence of an average of 200 pile-up events with the ability to extend the tracking coverage to a pseudorapidity of 4 while maintaining excellent tracking efficiency and performance. The ITk comprises two subsystems: a Strip Detector surrounding a Pixel Detector. The Strip Detector has four barrel layers and six end-cap petal-design

<sup>&</sup>lt;sup>1</sup> ATLAS uses a right-handed coordinate system with its origin at the nominal interaction point (IP) in the centre of the detector and the *z*-axis along the beam pipe. The *x*-axis points from the IP to the centre of the LHC ring, and the *y*-axis points upward. Cylindrical coordinates  $(r, \phi)$  are used in the transverse plane,  $\phi$  being the azimuthal angle around the *z*-axis. The pseudorapidity is defined in terms of the polar angle  $\theta$  as  $\eta = -\ln \tan(\theta/2)$ .

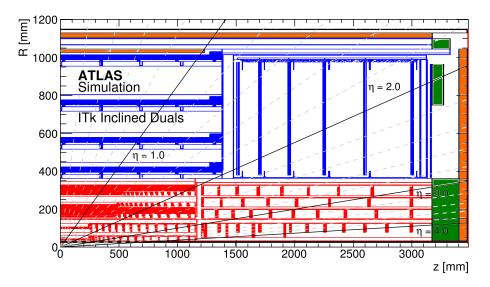

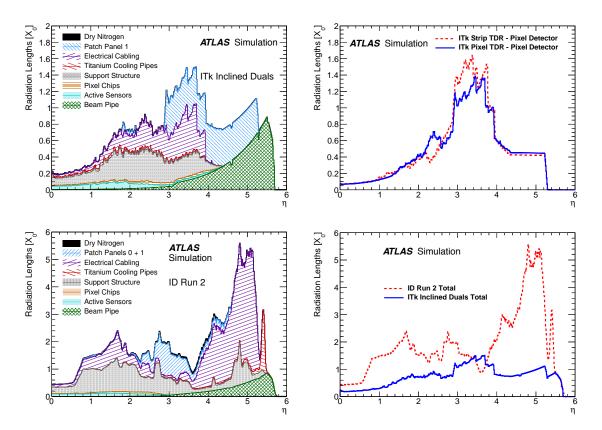

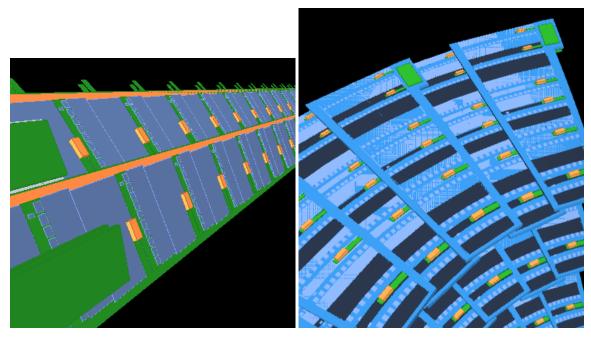

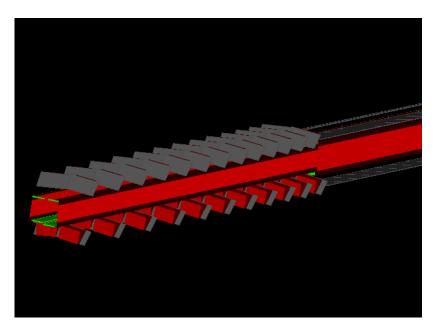

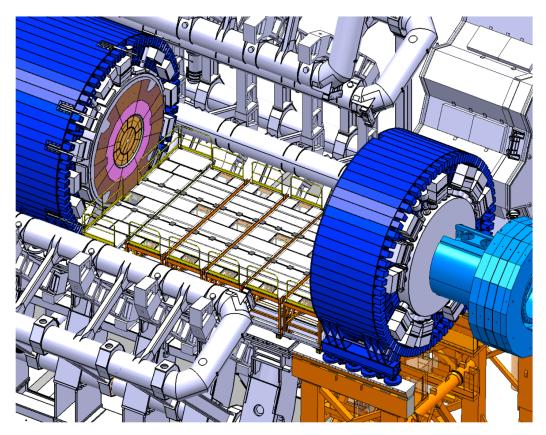

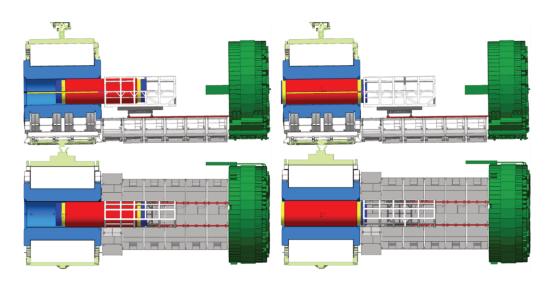

Figure 2.1: Schematic layout of the ITk for the HL-LHC phase of ATLAS as presented in the Strip TDR [1]. The active elements of the barrel and end-cap Strip Detector are shown in blue, for the Pixel Detector the sensors are shown in red for the barrel layers and in dark red for the end-cap rings. Here only one quadrant and only active detector elements are shown. The horizontal axis is the axis along the beam line with zero being the interaction point. The vertical axis is the radius measured from the interaction region. The outer radius is set by the inner radius of the barrel cryostat that houses the solenoid and the electromagnetic calorimeter.

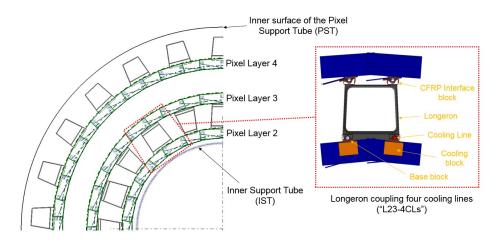

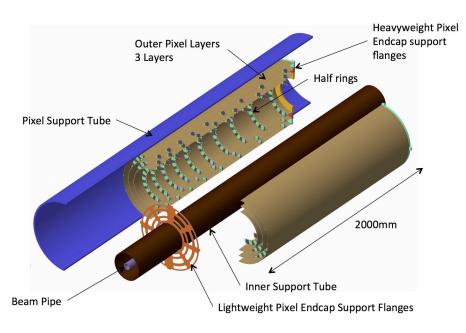

disks, both having double modules each with a small stereo angle to add z(R) resolution in the barrel (end-caps), respectively. The Strip Detector, covering  $|\eta| < 2.7$ , is complemented by a 5 layer Pixel Detector extending the coverage to  $|\eta| < 4$ . The Pixel and Strip Detector volumes are separated by a Pixel Support Tube (PST). In addition, and because of the harsh radiation environment expected for the HL-LHC, the inner two layers of the Pixel Detector are replaceable. The inner two pixel layers are separated from the outer three layers by an Inner Support Tube (IST), that facilitates a replacement of the inner layers. The combined Strip plus Pixel Detectors provide a total of 13 hits for  $|\eta| < 2.7$ , with the exception of the barrel/end-cap transition of the Strip Detector, where the hit count is 11 hits. The Pixel Detector presented in the Strip TDR [1] was designed to supply a minimum of at least 13 hits from the end of the strip coverage in pseudorapidity to  $|\eta|$  of 4. While the Strip Detector remains unchanged and is described in detail in Reference [1], the Pixel Detector layout has evolved to further improve the performance, reduce cost and incorporate engineering constraints. In the following, an overview is given on the methods used to optimise the detector layout, starting from the original Letter of Intent and Scoping Document studies, followed by a detailed description of the optimisations and changes to the Pixel Detector design since the Strip TDR.

#### 2.1.1 Methods used to optimised the ITk Detector Layout

Designing a tracking detector for the Phase-II upgrade of the ATLAS experiment is a challenging task. The detector will have to cope with the Phase-II operational conditions with an average of up to 200 pile-up events, the corresponding data rates and an unprecedented radiation environment. At the same time the ITk Detector will have to provide the required tracking performance to enable the physics programme as outlined in the ATLAS Phase-II Upgrade Letter of Intent [7]. The development of the ITk Detector layout is carried with the following set of goals:

- Design a tracking detector that provides the required tracking performance to the ATLAS Phase-II physics programme, in events with an average pile-up of up to 200 simultaneous interactions.

- The detector should provide robust tracking in presence of detector defects, like sensor inefficiencies due to expected radiation effects, as well as dead modules due to eventual component failures.

- Aim to minimise cost by reducing as much as possible the total silicon surface necessary to achieve the required hit coverage and by choosing less complex solutions whenever possible.

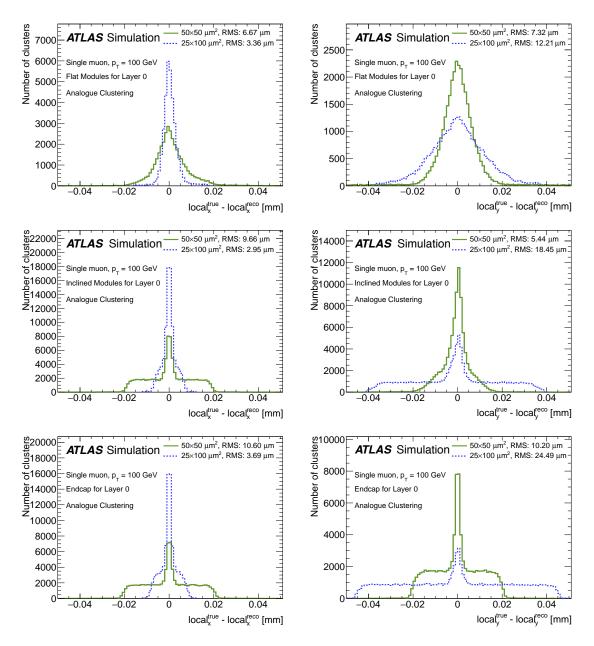

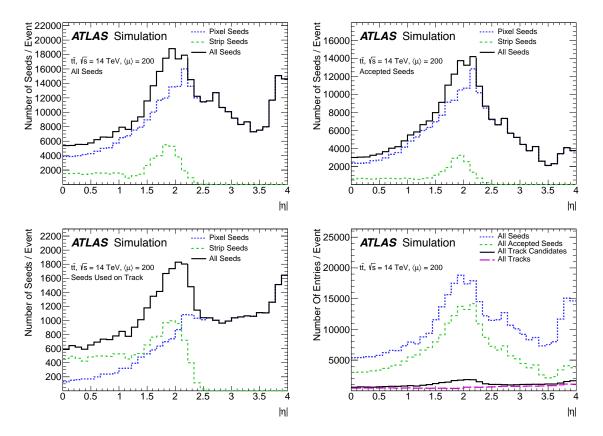

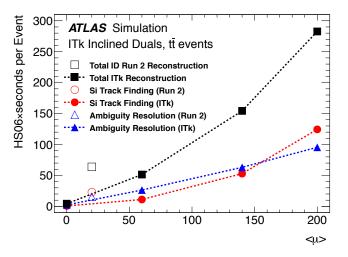

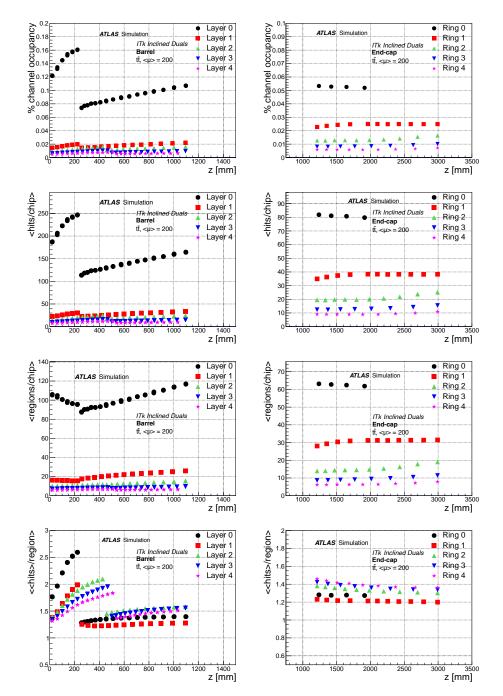

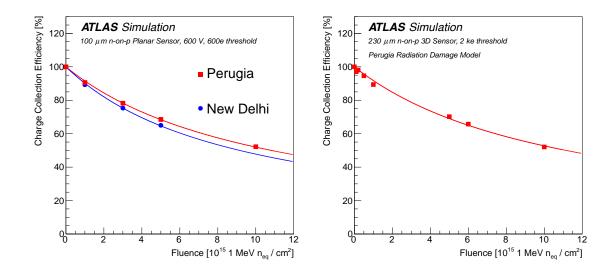

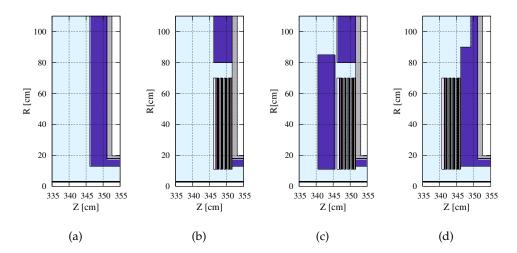

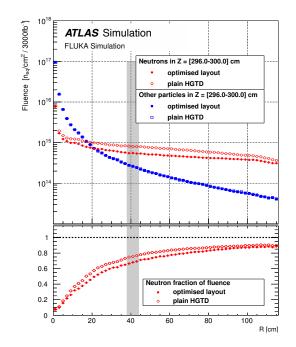

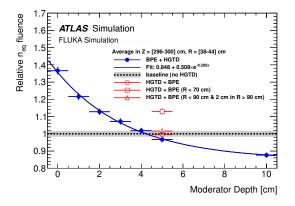

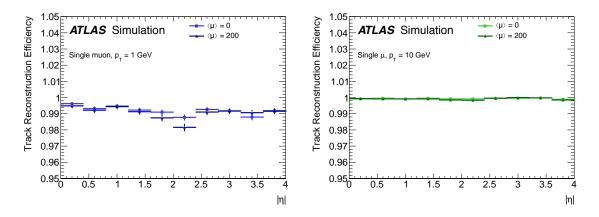

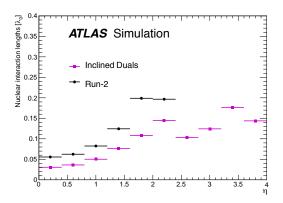

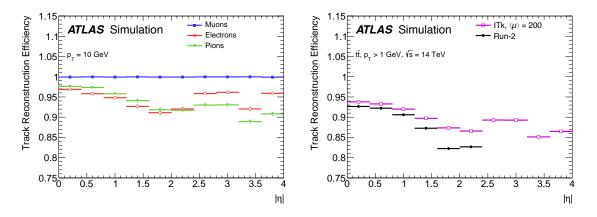

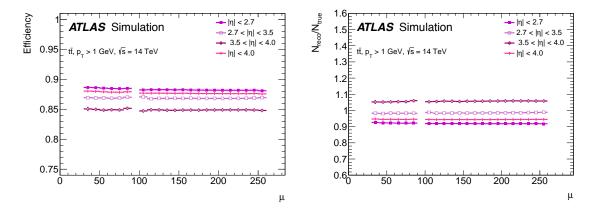

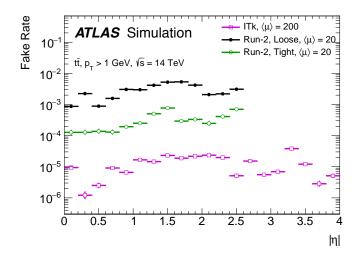

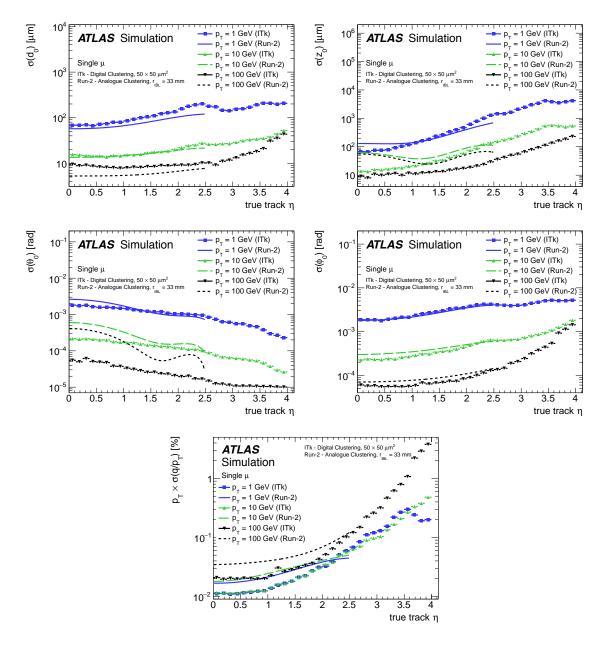

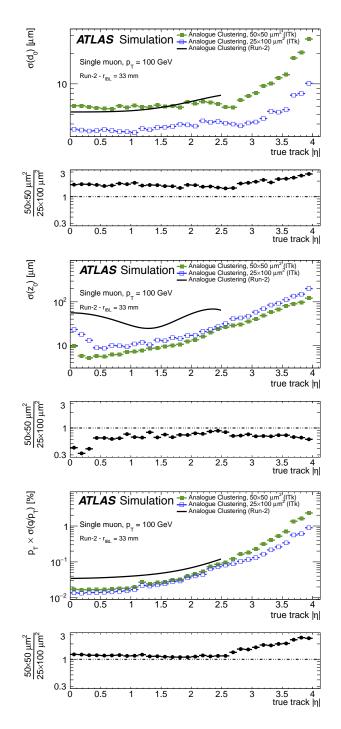

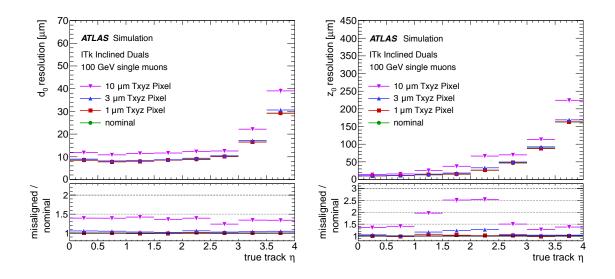

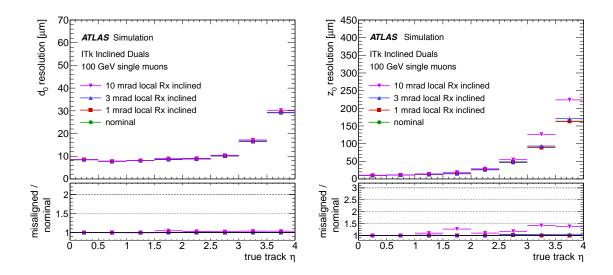

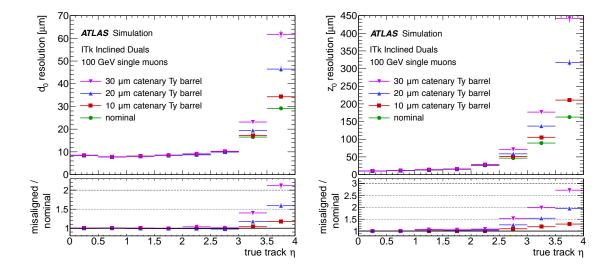

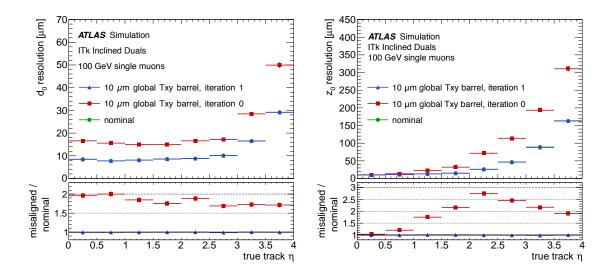

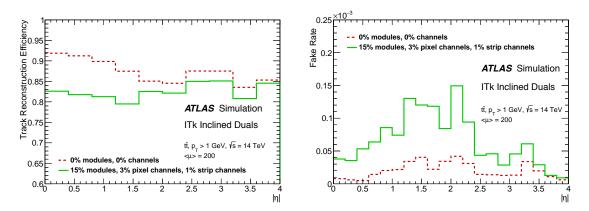

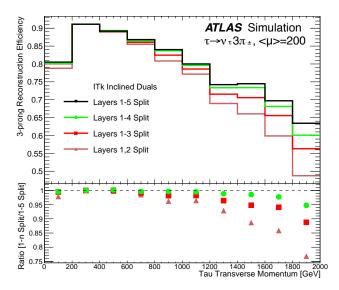

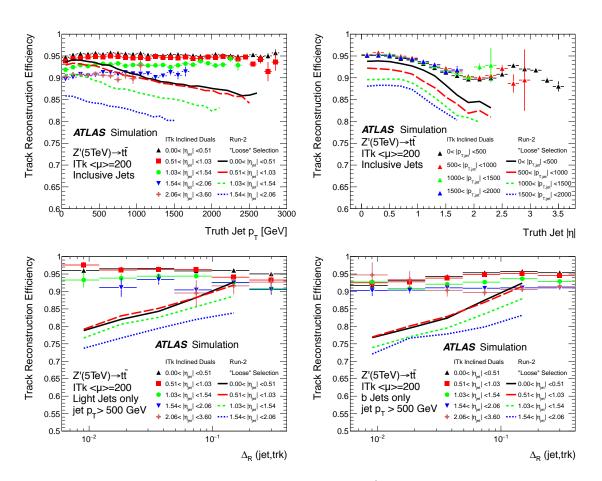

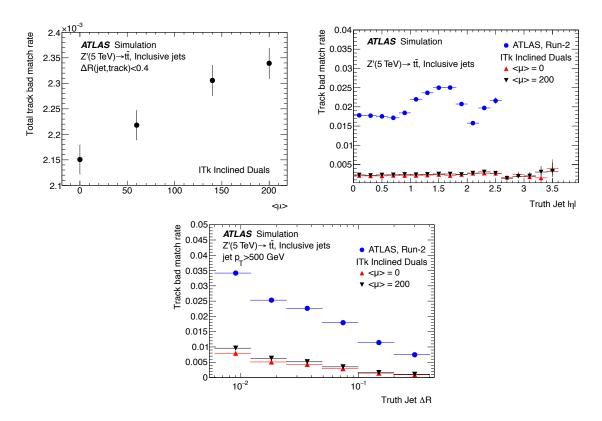

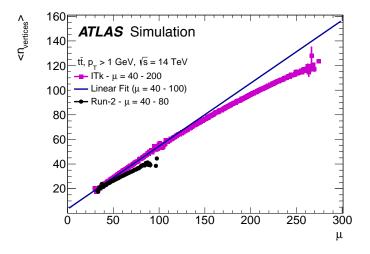

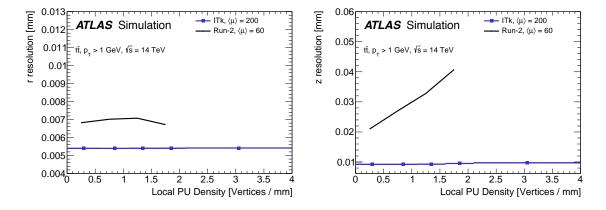

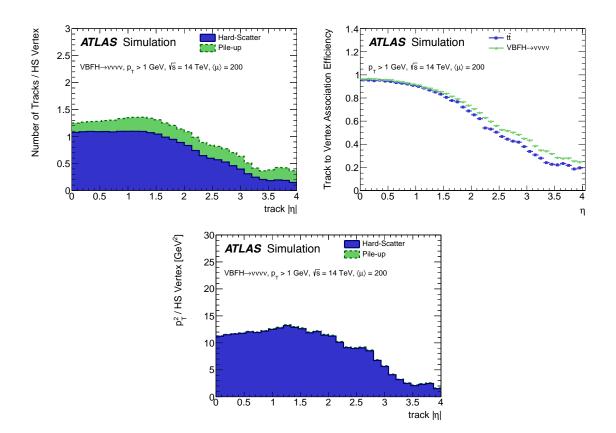

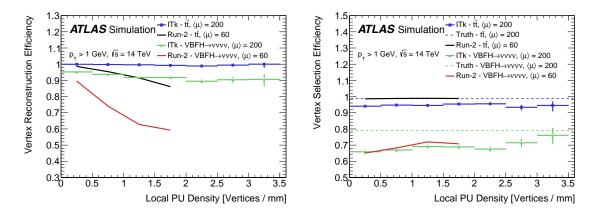

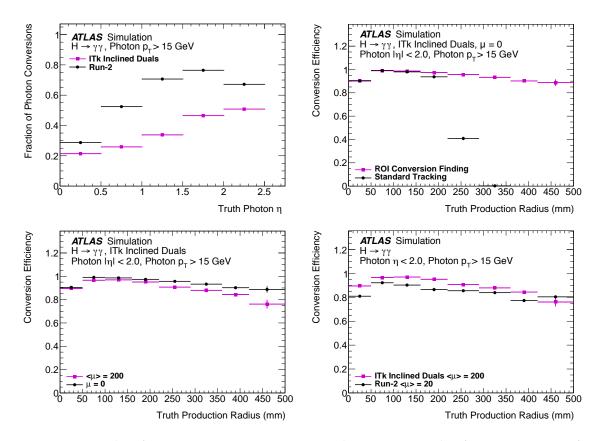

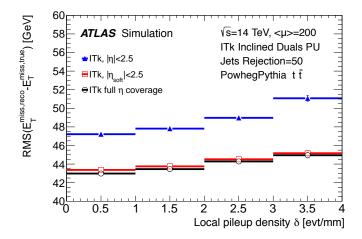

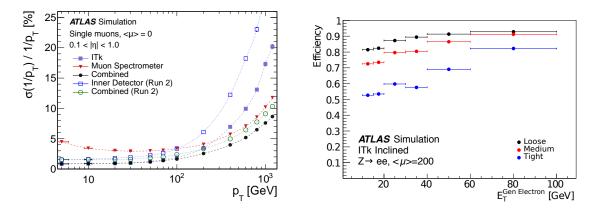

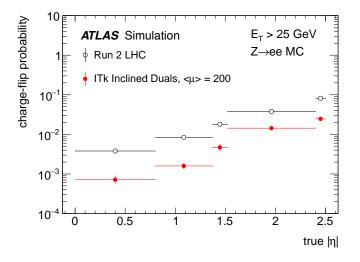

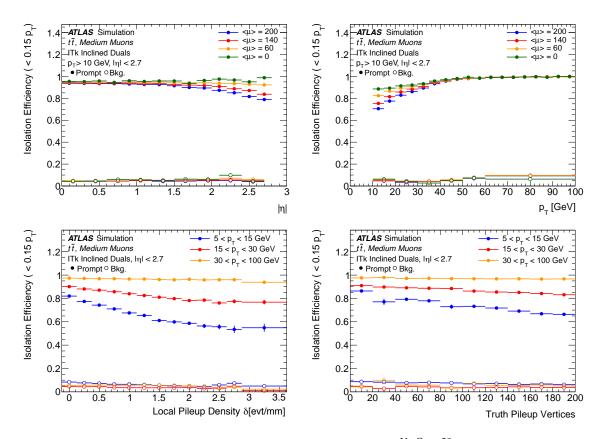

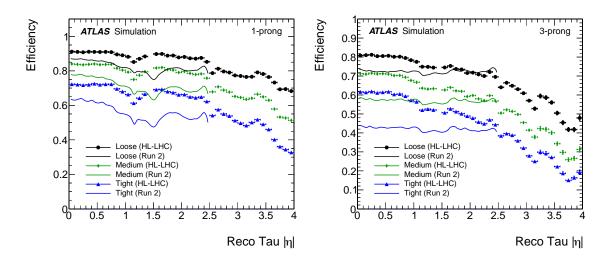

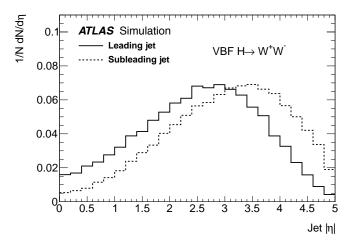

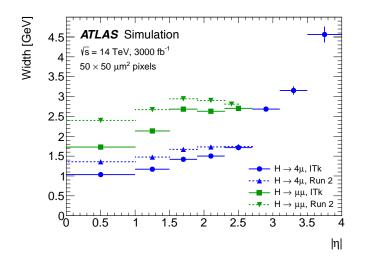

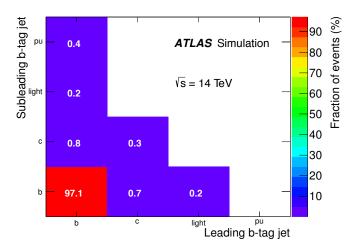

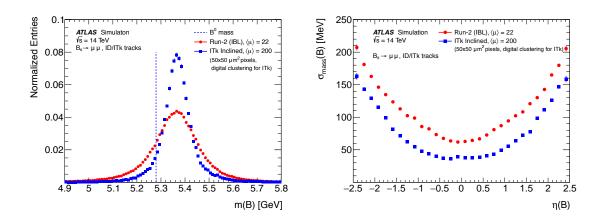

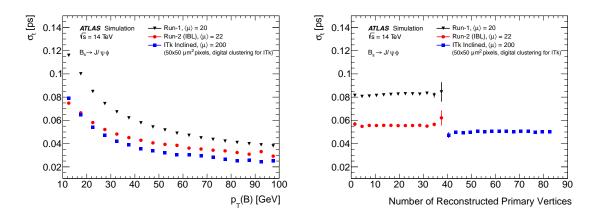

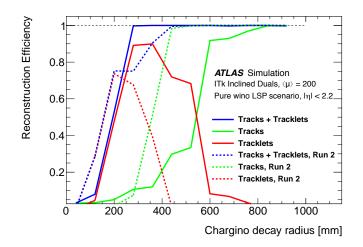

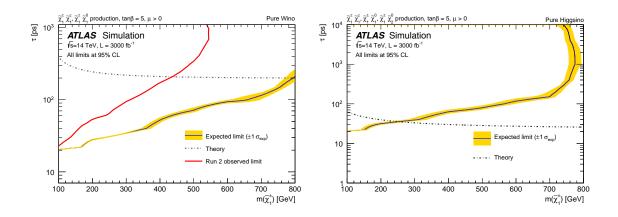

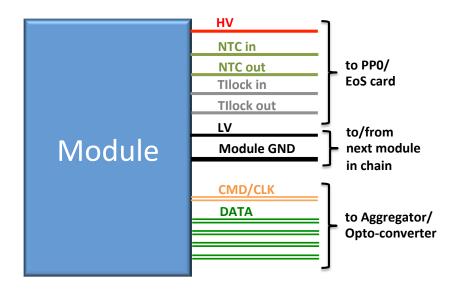

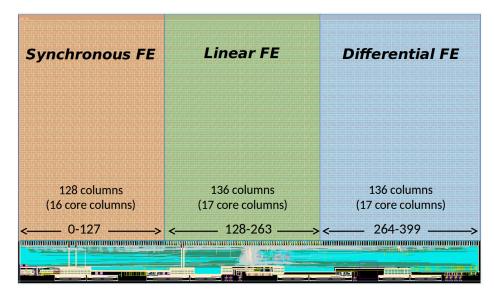

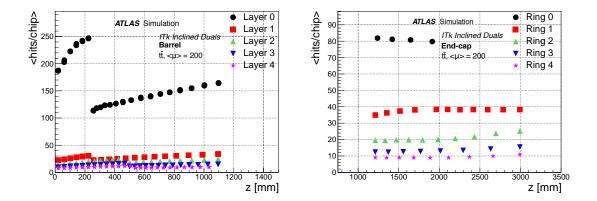

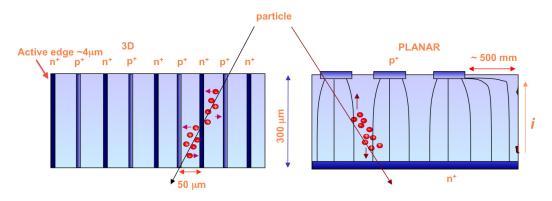

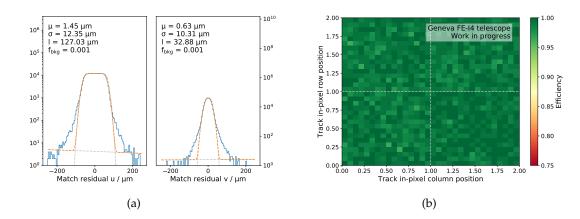

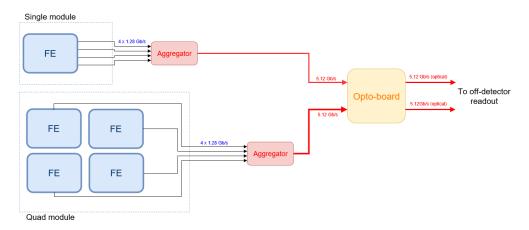

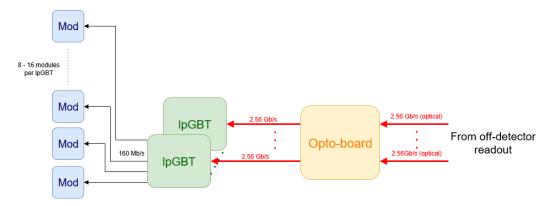

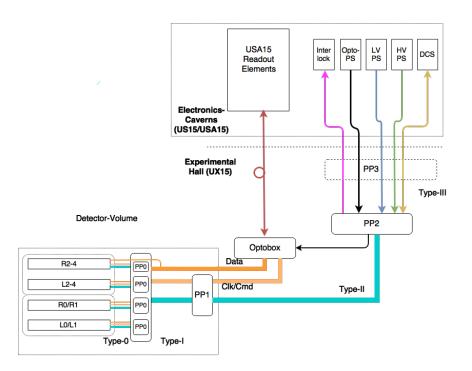

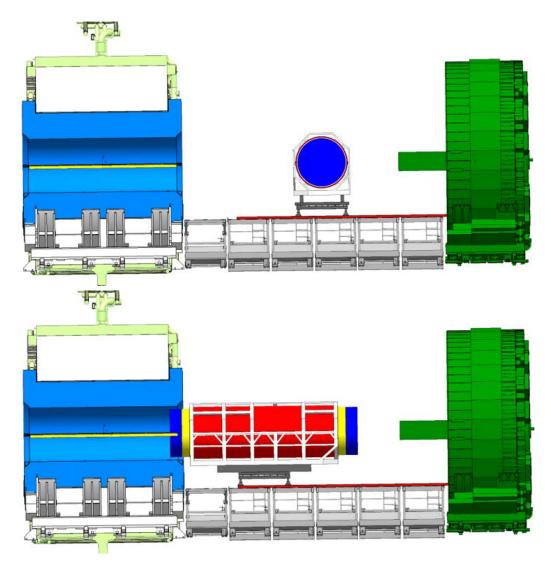

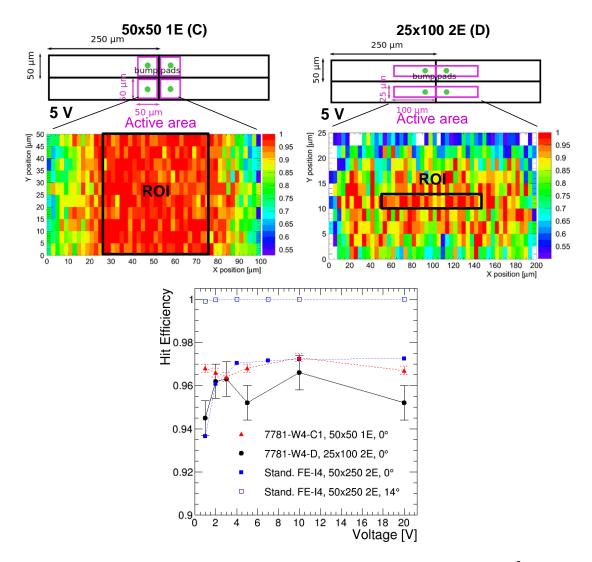

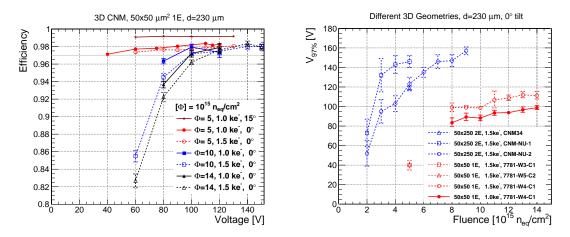

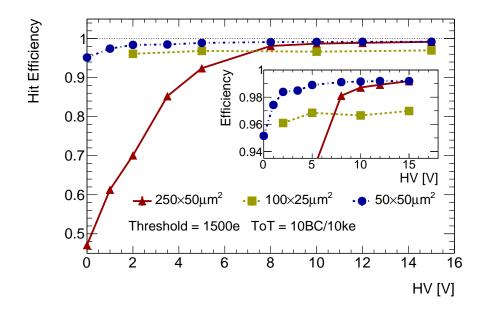

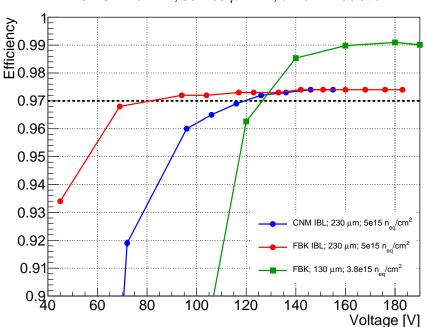

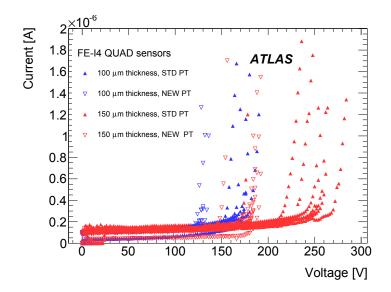

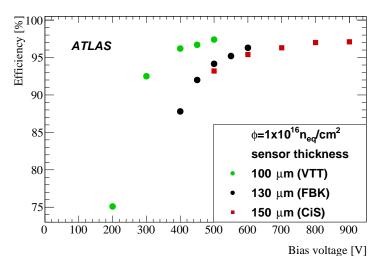

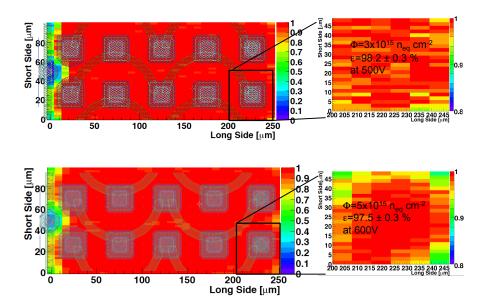

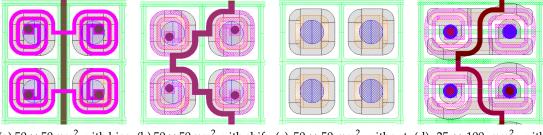

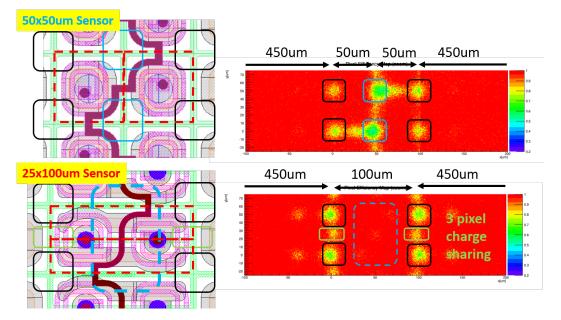

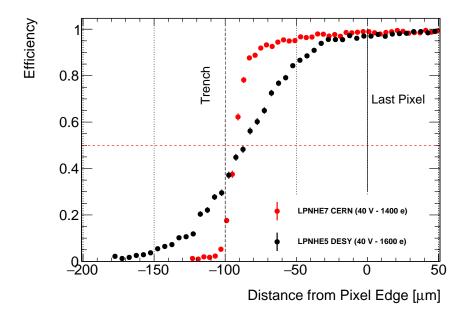

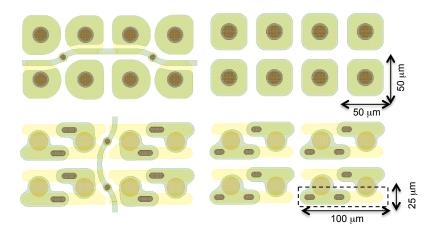

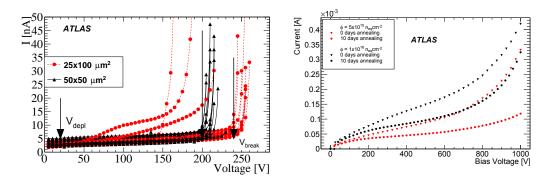

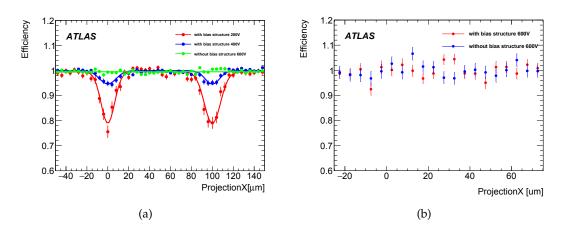

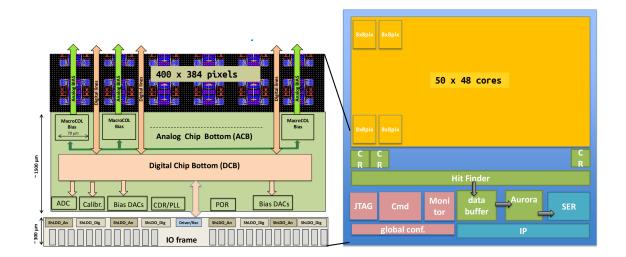

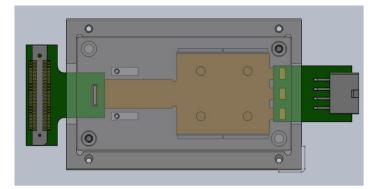

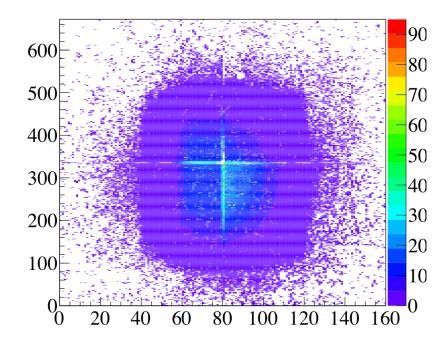

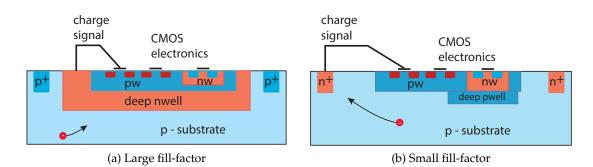

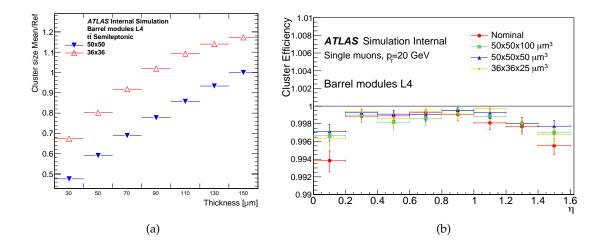

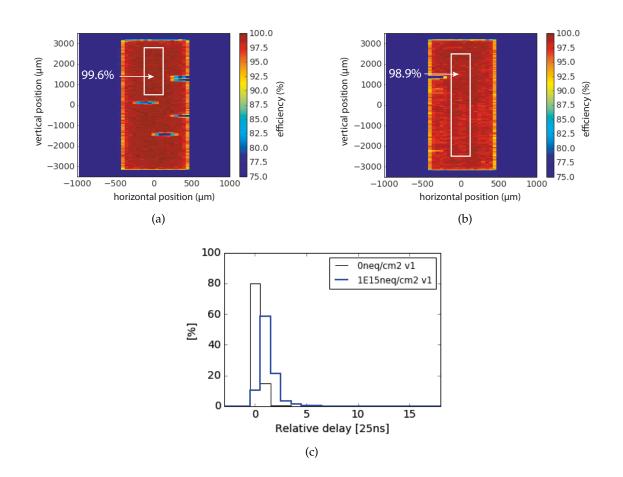

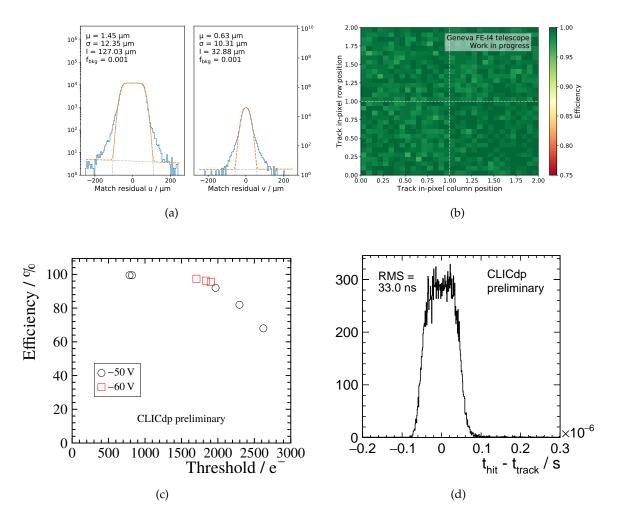

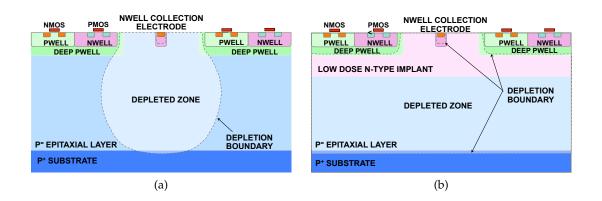

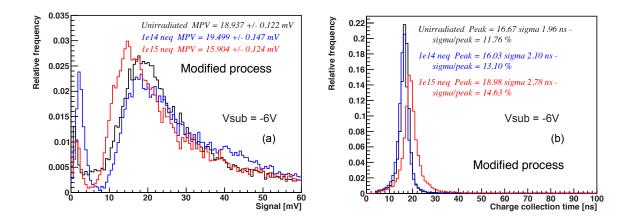

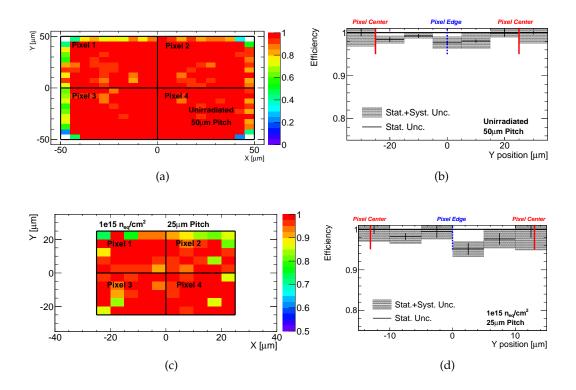

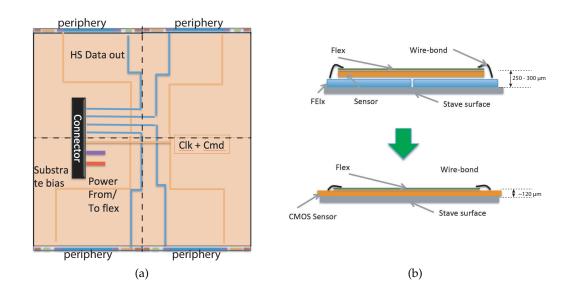

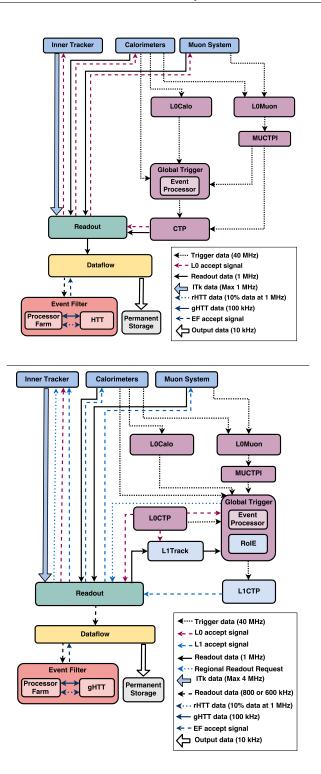

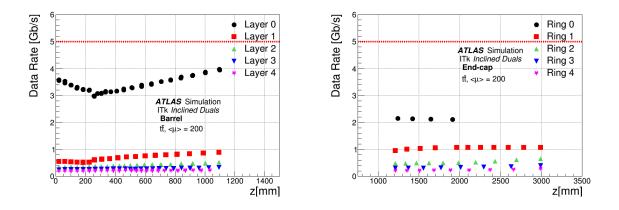

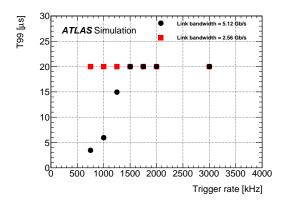

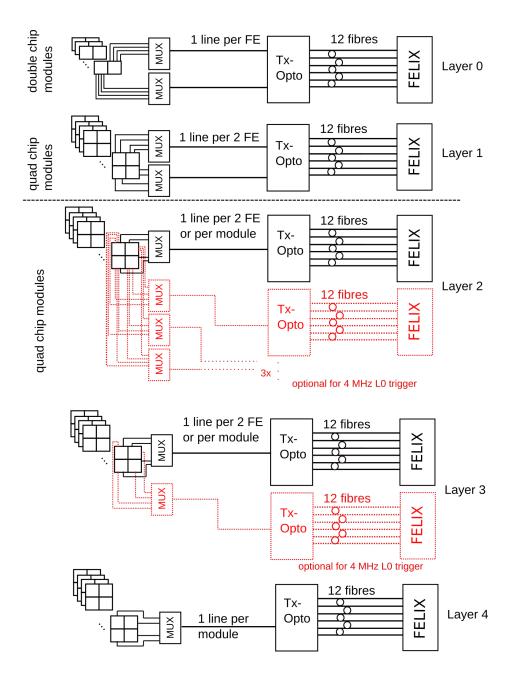

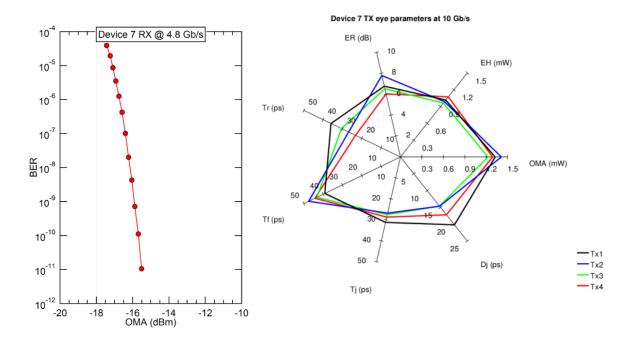

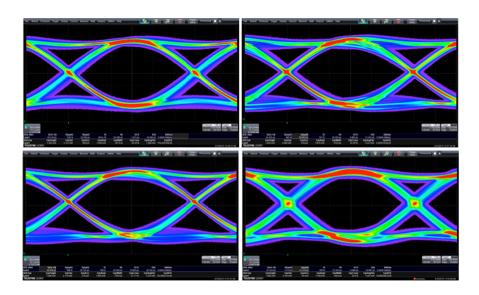

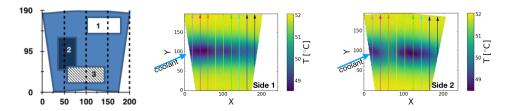

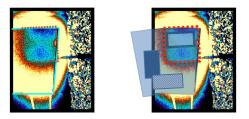

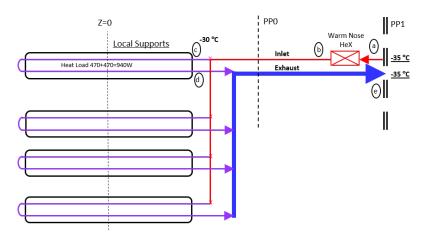

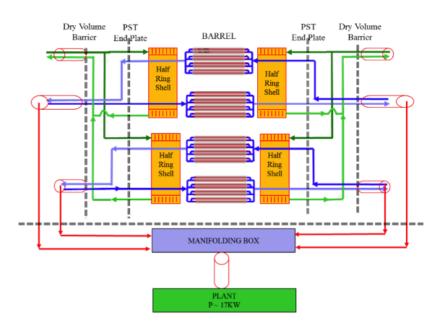

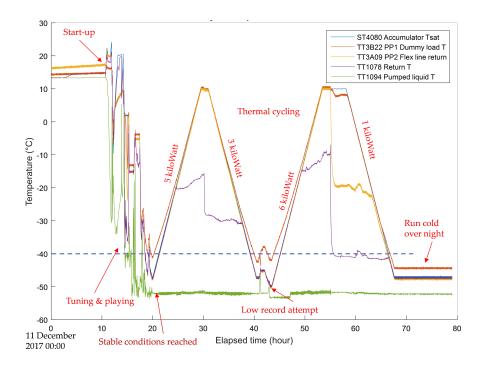

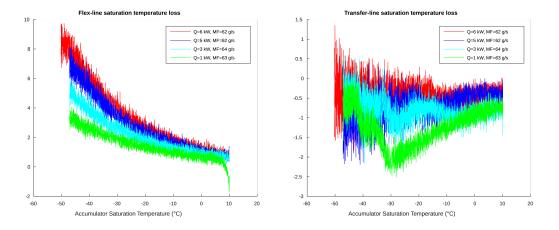

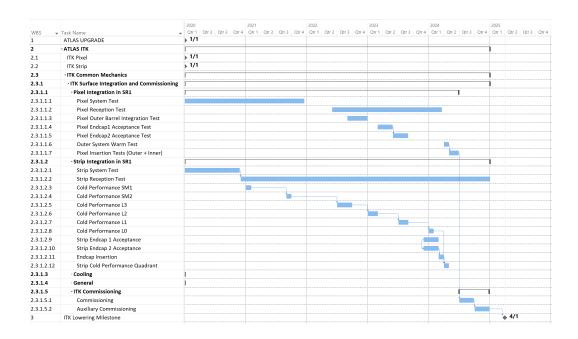

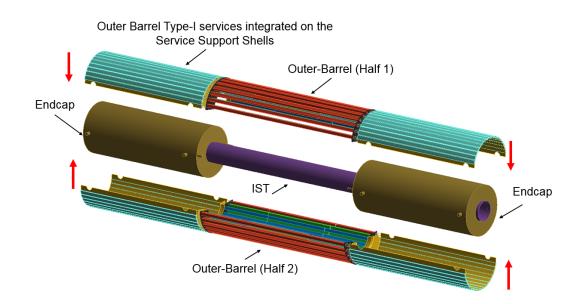

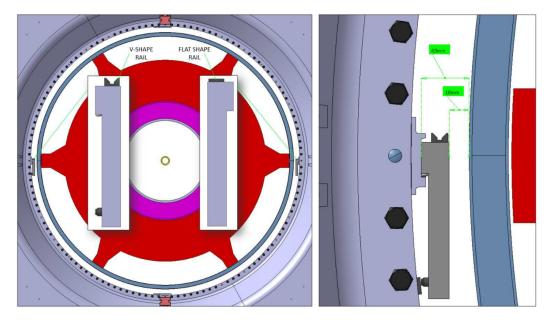

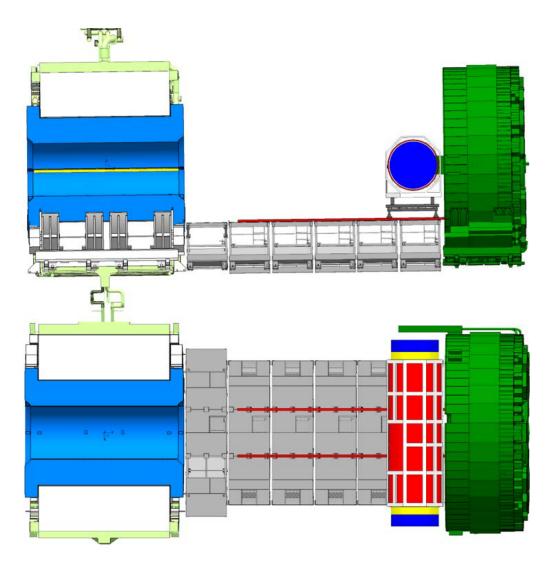

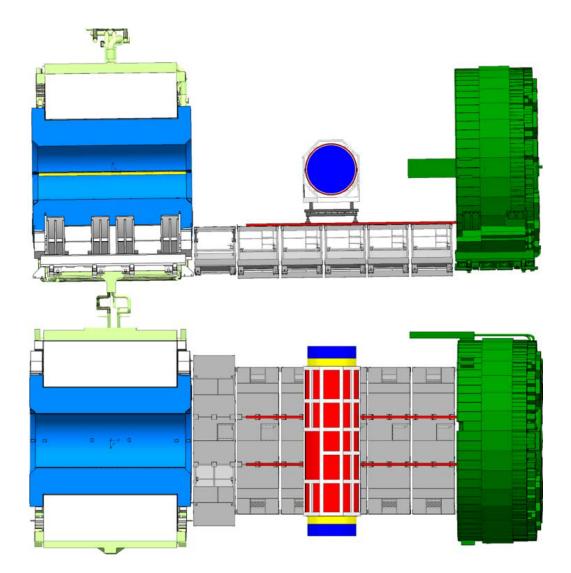

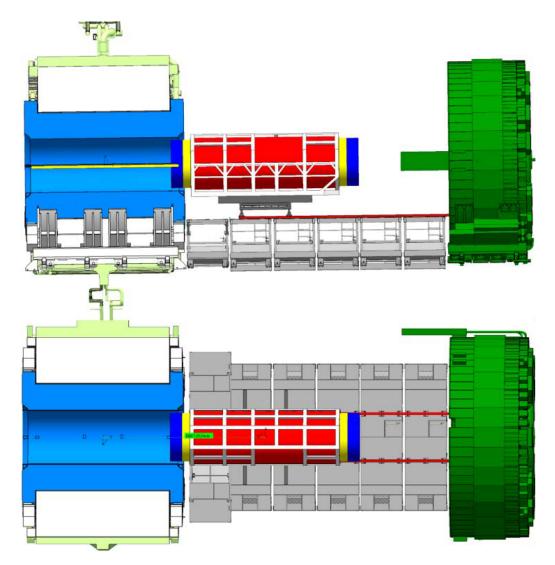

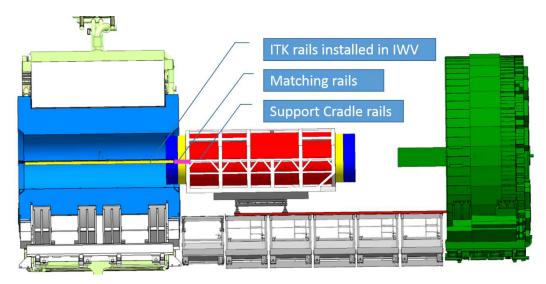

- At the same time, try to choose layout options that allow to minimise the CPU time needed for reconstruction, which is one of the cost drivers for the computing budget for the ATLAS Phase-II programme.