# Design Method of Constant Phase-Shifter Microwave Passive Integrated Circuit in 130-nm BiCMOS Technology With Bandpass-Type Negative Group Delay

Blaise Ravelo, Mathieu Guerin, Jaroslav Frnda, Frank Elliot Sahoa, Glauco Fontgalland, Hugerles S Silva, Samuel Ngoho, Fayrouz Haddad, Wenceslas Rahajandraibe

### ▶ To cite this version:

Blaise Ravelo, Mathieu Guerin, Jaroslav Fr<br/>nda, Frank Elliot Sahoa, Glauco Fontgalland, et al.. Design Method of Constant Phase-Shifter Microwave Passive Integrated Circuit in 130-nm BiCMOS Technology With Bandpass-Type Negative Group Delay. IEEE Access, 2022, 10, pp.93084-93103. 10.1109/ACCESS.2022.3201137 . hal-03968840

HAL Id: hal-03968840

https://hal.science/hal-03968840

Submitted on 7 Mar 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.Doi Number

# Design Method of Constant Phase-Shifter Microwave Passive Integrated Circuit in 130-nm BiCMOS Technology with Bandpass-Type Negative Group Delay

Blaise Ravelo<sup>1</sup>, Member, IEEE, Mathieu Guerin<sup>2</sup>, Member, IEEE, Jaroslav Frnda<sup>3,4</sup>, Senior Member, IEEE, Frank Elliot Sahoa<sup>5</sup>, Glauco Fontgalland<sup>6</sup>, Senior Member, IEEE, Hugerles S. Silva<sup>7,8</sup>, Member, IEEE, Samuel Ngoho<sup>9</sup>, Fayrouz Haddad<sup>2</sup>, Member, IEEE, and Wenceslas Rahajandraibe<sup>2</sup>, Member, IEEE

Email: blaise.ravelo@nuist.edu.cn, mathieu.guerin@im2np.fr, jfrnda@gmail.com, sfrankelliot@googlemail.com, fontgalland@dee.ufcg.edu.br, hugerles.silva@av.it.pt, samngoho@yahoo.fr, {fayrouz.haddad, wenceslas.rahajandraibe}@im2np.fr

Corresponding author: Mathieu Guerin (e-mail: mathieu.guerin@im2np.fr)

This research work was supported by the Ministry of Education, Youth and Sports of the Czech Republic under the grant SP2022/5 conducted by VSB - Technical University of Ostrava, Czechia. This research work was also supported in part by NSFC under Grant 61971230, and in part by the Jiangsu Specially Appointed Professor program and Six Major Talents Summit of Jiangsu Province (2019-DZXX-022), and in part by the Startup Foundation for Introducing Talent of NUIST.

**ABSTRACT** The miniaturization and application development are the expected challenges on the today engineering design research on bandpass (BP) type negative group delay (NGD) circuit. To overcome this technical limit, an innovative contribution on integrated circuit (IC) design method of BP-NGD application to design constant phase shifter (PS) in 130-nm BiCMOS technology is developed in the present paper. The BP-NGD PS microwave passive IC is topologically consisted of cascade of CLC- and RLC-resonant networks. After the S-matrix modelling, the synthesis design equations enabling to calculate each lumped component values constituting the BP-NGD PS BiCMOS are established. The design equations are expressed knowing the targeted specifications as phase shift and operating frequency. The BiCMOS design methodology including the key steps as design rule checking (DRC), layout versus schematic (LVS) and post-layout simulation (PLS) is described. The miniaturized BP-NGD PS design feasibility is verified with schematic and layout simulations with IC CMOS standard commercial software tool. A proof-of-concept (POC) of 130-nm BiCMOS BP-NGD PS operating at the center frequency f<sub>0</sub>=1.9 GHz and bandwidth  $\Delta f$ =0.1 GHz is designed and simulated. After DRC, the chip layout of miniaturized BP-NGD PS POC presents 0.407 mm<sup>2</sup> size. The BP-NGD PS POC exhibits constant phase shift notable value of about  $\varphi_0$ =- $90^{\circ}+/-0.4^{\circ}$  under  $S_{21}(f_0)=-6$  dB+/-1 dB transmission coefficient with good flatness and reflection coefficients ( $S_{21}(f_0)$  and  $S_{21}(f_0)$ ) widely better than -10 dB. The design robustness is confirmed by 1000-trial Monte Carlo uncertainty analyses with PLS results. Because of the potential integration in wireless sensor networks (WSNs), the BP-NGD PS under study is a promising candidate for the improvement of the future 5G and 6G transceiver design.

<sup>&</sup>lt;sup>1</sup> Nanjing University of Information Science & Technology (NUIST), School of Electronic & Information Engineering, Nanjing, Jiangsu, China 210044

<sup>&</sup>lt;sup>2</sup> Aix-Marseille University, CNRS, University of Toulon, IM2NP UMR7334, 13007 Marseille, France

<sup>&</sup>lt;sup>3</sup> Department of Quantitative Methods and Economic Informatics, Faculty of Operation and Economics of Transport and Communication, University of Zilina, 01026 Zilina, Slovakia

<sup>&</sup>lt;sup>4</sup> Department of Telecommunications, Faculty of Electrical Engineering and Computer Science, VSB-Technical University of Ostrava, 70800 Ostrava, Czech Republic

<sup>&</sup>lt;sup>5</sup> Laboratoire de Physique Nucléaire et Physique de l'Environnement (LPNPE), Université d'Antananarivo, Antananarivo 101, Madagascar

<sup>&</sup>lt;sup>6</sup> Federal University of Campina Grande, Applied Electromagnetic and Microwave Lab., Campina Grande/PB, 58429, Brazil

<sup>&</sup>lt;sup>7</sup> Instituto de Telecomunicações and Departamento de Eletrónica, Telecomunicações e Informática, Universidade de Aveiro, Campus Universitário de Santiago, 3810-193 Aveiro, Portugal

<sup>&</sup>lt;sup>8</sup> Department of Electric Engineering, University of Brasília (UnB), Federal District 70910-900, Brazil

<sup>9</sup> Association Française de Science des Systèmes (AFSCET), Paris 75013, France

**INDEX TERMS** 130-nm BiCMOS technology, Integrated circuit (IC), Design method, Microwave circuit, Passive topology, S-parameter model, Bandpass (BP) negative group delay (NGD), BP-NGD application, Microwave phase shifter (PS).

### I. INTRODUCTION

The technological and engineering evolution trends to enhance the quality of human life and to develop the modern society. To face up the challenging societal situation, new knowledge leading to natural progress of physical science is expected. Further understanding of non-vulgar phenomena can be the most efficient solutions against the societal problems. In other words, recent research works state the existence of abnormal physical phenomena which require further study. The negative group delay (NGD) phenomenon belongs among the most counterintuitive physical phenomena which is still not well-familiar to most of electronic and communication engineers.

# A. STATE OF THE ART ON THE NGD ELECTRONIC CIRCUIT DESIGN

The fascinating NGD phenomenon was experimented in dispersive optical media presenting negative refractive index (NRI) where the group velocity can also be negative [1-3]. The radio frequency (RF) and microwave NGD phenomenon was validated with split ring resonator (SRR) structure based NRI metamaterial circuits identified from 3-D and 2-D periodical bulk materials [4-5]. However, the metamaterial-based microwave NGD circuits operate with significant losses. For this reason, the NGD circuit applications are literally less developed and less investigated compared to other electronic communication functions as filter, antenna, amplifier, coupler and power combiner/divider. Last two decades, diverse topologies of NGD microwave circuits were designed and experimented [6-12]. It was demonstrated that the NGD circuits can be designed by using lumped R, L and C topologies and also microstrip topologies. In addition to the basic understanding of NGD phenomenon meaning, the main challenge at this stage was the design of low attenuation and compact NGD microwave circuit [10-12]. Moreover, despite the progressive research work from few groups around the world, the NGD engineering remains, so far, an unfamiliar concept for non-specialist RF and microwave design, manufacturing and test engineers.

An innovative fundamental theory of NGD circuit inspired from filter theory which is easy to understand for graduate students and non-specialist electronic design, fabrication, test and commercial engineers was initiated [13-14]. The NGD circuit theory is elaborated from transfer

function (TF) approach [13-14]. It is noteworthy that the main difference is the fact that the filter is characterized from TF magnitude and the NGD is characterized from the TF group delay (GD). Based on the NGD-filter analogy, the innovative classification of low-pass (LP) [13-17], high-pass (HP) [13-14,18-21], bandpass (BP) [4-14] and stop-band (SB) [13-14,21-23] NGD topologies are identified. These different NGD topology types are characterized from the frequency band(s) where the GD is susceptible to be negative. Behind the NGD theoretical development, there are curious questions about the application.

# B. STATE OF THE ART ON THE NGD CIRCUIT-BASED PHASE SHIFTER (PS) DESIGN

Tentative RF and microwave engineering applications of NGD circuits [24-36] were proposed. Ones of most remarkable applications are based on the NGD equalization technique which consists of cascading positive GD (PGD) and NGD circuits [24-36]. The NGD equalization approach enables naturally to compensate delay and electronic component undesirable effects [25-28]. By means of BP-NGD electronic function, the unfamiliar NGD equalization enables more importantly to design innovative microwave phase shifters (PSs) [29-34]. The solution of RF and microwave PS topology can be flexibly designed with both active [29-32] and passive [33-35] topologies. The main particularity of such PSs is the possibility to operate in broadband with constant value or independently with frequency [29-34]. This innovative PS topology can be exploited to design Hilbert filter [36] which is interesting to design higher performance transceivers (Tx-Rx). For example, the Hilbert filter is expected to be a good technological candidate to perform operation as FFT and iFFT and also to design analog and mixed modulators and demodulators for future communication front- and backend systems. More recent study [35] highlights that by using SB-NGD function, innovative design solution of stair PSs can be performed.

Compared to the metamaterial-based microwave PS design [37] and application for front- and back-end terminals [38-40], further understanding and applicative studies of BP-NGD circuits are needed. The technical challenge slowing down the development of constant phase BP-NGD PS is the integration feasibility in miniaturized Tx-Rx system. The prominent solution is the design in CMOS integrated circuit (IC) technology whose the feasibility for LP- [41-42] and HP- [43] NGD circuits were

VOLUME XX, 2022

recently theoretically investigated.

### C. ORIGINALITY AND OUTLINE OF THE PAPER

The originality of the present research work is claimed as follows:

- On the IC-based design methodology of BP-NGD PS constituted by CLC and BP-NGD passive circuits combined in cascade by considering 130-nm BiCMOS technology.

- On the synthesis and design formulation for calculating the lumped passive topology in function of the targeted operation frequency.

The present paper is organized in seven main sections as follows:

- Section II recalls the general specifications of the unfamiliar BP-NGD and positive group delay (PGD) ideal circuits.

- Section III defines the ideal analysis and also the key specifications of the behavior of the proposed BP-NGD PS from the S-matrix modelling.

- Section IV examines theoretically the analytical Smatrix models of the PGD, BP-NGD and PS lumped topologies.

- Section V reveals the synthesis equations enabling to determine the R, L and C component values from the expected specifications of the PS under study.

- Section VI is focused on the CMOS IC design methodology of the BP-NGD PS by using IC simulator Cadence® VIRTUOSO. A miniaturized BP-NGD PS proof-of-concept (POC) will be designed and studied.

- Section VII examines the verification results from calculation and simulations. Monte Carlo (MC) uncertainty analyses (UAs) are also performed to highlight the CMOS BP-NGD PS design.

- Section VIII finalizes the paper with conclusion.

# II. GENERAL DESCRIPTION OF BP-NGD AND PGD FUNCTIONS

The general theoretical approach to analyze the BP-NGD PS is introduced in the present section. The introduced theory is based on S-parameter representation. The specifications of BP-NGD and also the PS are defined.

### A. S-MATRIX MODELLING GENERAL DESCRIPTION

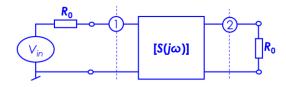

Acting as a microwave circuit, the analysis of the PS studied in this paper is essentially based on S-matrix approach. Fig. 1 represents a general configuration of two-port black box modelled by S-matrix:

$$[S(s)] = \begin{bmatrix} S_{11}(s) & S_{21}(s) \\ S_{21}(s) & S_{11}(s) \end{bmatrix}.$$

(1)

with  $s=j\omega$  is the Laplace variable expressed in function of angular frequency  $\omega=2\pi f$ . The S-model elaborated in the along paper is referred to the impedance  $R_0=50~\Omega$ .

FIGURE 1. Two-port S-parameter black box.

Acting as a symmetric circuit, we have the magnitudes of the reflection and transmission coefficients expressed as, respectively:

$$S_{11}(\omega) = |S_{11}(j\omega)| \tag{2}$$

$$S_{21}(\omega) = \left| S_{21}(j\omega) \right|. \tag{3}$$

In addition to the magnitudes, the present study will also consider:

the phase of the transmission coefficient which is defined by:

$$\varphi(\omega) = \arg \left[ S_{21}(j\omega) \right] \tag{4}$$

the frequency dependent GD response which is defined by:

$$GD(\omega) = -\frac{\partial \varphi(\omega)}{\partial \omega} \,. \tag{5}$$

When the last quantity is negative, the S-parameter presents an unfamiliar NGD behavior. The next subsection recalls the main specifications of BP-NGD type circuits.

### B. SPECIFICATIONS OF TYPICAL BP-NGD FUNCTION

A circuit can be classified as typical BP-NGD function if we can find an angular frequency,  $\omega$ , from the transmission coefficient GD respecting the condition:

$$GD(\omega) < 0$$

. (6)

An ideal response of BP-NGD function can be represented by:

• The cut-off angular frequencies,  $\omega_1$  and  $\omega_2$ , as depicted by Fig. 2(a), as roots of equation:

$$GD(\omega) = 0$$

. (7)

• By taking a real negative parameter  $t_n$ , the ideal GD response can be negative as defined by:

$$GD(\omega_1 \le \omega \le \omega_2) = t_n < 0.$$

(8)

• By taking the maximal reflection coefficient  $0 < A_{max} < 1$ , we have the ideal response displayed as plotted in Fig. 2(b):

$$S_{11}(\omega_1 \le \omega \le \omega_2) = A_n \le A_{\text{max}}. \tag{9}$$

• And by taking the minimal transmission coefficient  $0 < B_{min} < 1$ , we have the ideal response as shown in Fig. 2(c):

$$S_{21}(\omega_1 \le \omega \le \omega_2) = B_n \ge B_{\min}. \tag{10}$$

For the case of BP-NGD circuit, the bandwidth is defined by:

$$\Delta \omega = \omega_2 - \omega_1 \ . \tag{11}$$

FIGURE 2. (a) GD, (b) refection and (c) transmission coefficient responses of typical BP-NGD function.

To design an ideal PS, the ideal S-matrix model of BP-NGD in frequency band  $[\omega_1, \omega_2]$  with:

$$\left| S_{11,NGD}(j\omega) \right| = \left| S_{22,NGD}(j\omega) \right| \approx 0. \tag{12}$$

Therefore, the BP-NGD S-matrix can be formulated by:

$$[S_{NGD}(j\omega)] = \begin{bmatrix} 0 & S_{21,NGD}(j\omega) \\ S_{21,NGD}(j\omega) & 0 \end{bmatrix}.$$

(13)

The S-matrix presents the associated transmission coefficient expressed as:

$$S_{21,NGD}(j\omega) = B_n \cdot \exp[j(\varphi_n - \omega \cdot t_n)]$$

(14)

with  $0 < B_n < 1$  and initial phase shift:

$$\varphi_n = \varphi_{NGD}(\omega_1) . \tag{15}$$

In opposite to the present case, the PGD circuit specifications will be elaborated in the next section.

# C. SPECIFICATIONS OF THE PGD FUNCTION BEHAVIOR

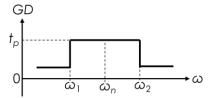

The PGD function operates as typical true time delay (TTD) circuit assumed to work in the frequency band defined by limits  $\omega_1$  and  $\omega_2$  with  $\omega_1 < \omega_2$  which is the same as the frequency band of the previously described BP-NGD function. By taking real positive  $t_p$ , the ideal GD diagram can be represented by Fig. 3 specified by:

$$GD(\omega_1 \le \omega \le \omega_2) = t_p > 0.$$

(16)

The PGD is expected to present the same specifications in terms of reflection and transmission coefficients as the BP-NGD ones plotted in Fig. 2(b) and Fig. 2(c), with  $A_p=A_n$  and  $B_p=B_n^2$ , respectively. The GD diagram shown by Fig. 3 enables to express the phase shift associated to the PGD

that within frequency band  $[\omega_1, \omega_2]$ . Accordingly, the ideal S-matrix model of PGD under ideal condition:

$$\left| S_{11,PGD}(j\omega) \right| = \left| S_{22,PGD}(j\omega) \right| \approx 0. \tag{17}$$

FIGURE 3. GD diagram of PGD function constituting the PS.

The associated S-matrix should be:

$$[S_{PGD}(j\omega)] = \begin{bmatrix} 0 & S_{21,PGD}(j\omega) \\ S_{21,PGD}(j\omega) & 0 \end{bmatrix}$$

(18)

which presents the associated transmission coefficient expressed as:

$$S_{21,PGD}(j\omega) = B_p \cdot \exp\left[j(\varphi_p - \omega \cdot t_p)\right]$$

(19)

with  $0 < B_p < 1$  and initial phase shift:

$$\varphi_{p} = \varphi_{PGD}(\omega_{1}). \tag{20}$$

The next section describes the proposed PS theorization from the previously defined BP-NGD and PGD characterization.

# III. GENERAL DESCRIPTION OF THE BP-NGD BASED CONSTANT PS

The fundamental theory of the constant or independent of frequency PS is described in the present subsection. The ideal representation of the constituting PGD and NGD circuit is introduced. The ideal main specifications and the analytical approach from the S-parameter operation are defined.

### A. S-PARAMETER IDEAL ANALYSIS OF THE BP-NGD FUNCTION BASED PS

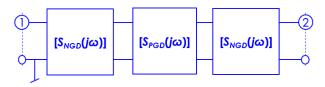

The BP-NGD PS under study is composed cascaded PGD and NGD circuits. The analysis is elaborated based on the frequency domain representation. The two identical NGD circuits are intercalated by PGD one. The topological solution to design this PS, we proposed the two-port topology introduced by Fig. 4. Since the reflection coefficients are negligible under conditions (12) and (17), the S-matrix modelling of this synoptic diagram is the product:

$$[S(j\omega)] = [S_{NGD}(j\omega)] \times [S_{PGD}(j\omega)] \times [S_{NGD}(j\omega)].$$

(21)

FIGURE 4. Two-port black box of frequency-independent PS constituted by PGD and NGD circuits in cascade.

Substituting the S-matrix of equation (13) and equation (18) into the previous relation, it yields the PS following ideal model:

$$[S(j\omega)] = \begin{bmatrix} 0 & S_{21}(j\omega) \\ S_{21}(j\omega) & 0 \end{bmatrix}$$

(22)

where the overall transmission coefficient ideally expressed as follows:

$$S_{21}(j\omega) = S_{21,NGD}(j\omega) \cdot S_{21,PGD}(j\omega) \cdot S_{21,NGD}(j\omega). \tag{23}$$

It yields the phase shift analytical expression of the next subsection.

### B. PHASE SHIFT ANALYTICAL EXPRESSION

Substituting the transmission coefficients given by equation (14) and equation (19) into the previous one, we have:

$$S_{21}(j\omega) = B_n^2 B_p \exp\left\{j\left[2\varphi_n + \varphi_p - \omega(2t_n + t_p)\right]\right\}. (24)$$

It means that the associated phase shift  $\varphi_{PS}(\omega) = \arg[S_{21}(j\omega)]$  is given by:

$$\varphi_{PS}(\omega) = 2\varphi_n + \varphi_n - \omega(2t_n + t_n). \tag{25}$$

To generate a frequency independent PS within frequency band  $[\omega_1, \omega_2]$ , the phase shift must be expressed as:

$$\varphi_{PS}(\omega) = \varphi_0 = \text{Constant}$$

(26)

By identification coefficients of equations (25) and (26), we have:

• The PS GD  $GD_{PS}(\omega) = -\partial \varphi_{PS}(\omega)/\partial \omega$  as defined in equation (5) becomes:

$$GD_{PS}(\omega) = t_p + 2t_n = 0$$

. (27)

which implies:

$$t_p = -2t_n \,. \tag{28}$$

• The independent frequency phase value:

$$\varphi_0 = 2\varphi_n + \varphi_p. \tag{29}$$

More illustrative comprehension about the constant phase shift aspect can be reached with graphical representation of phase diagram.

# C. PHASE DIAGRAM ANALYSIS OF THE BP-NGD BASED PS

The previous analytical approach enables to plot the ideal behavior of the BP-NGD PS understudy. We also recall that

the PS is expected to operate within frequency band  $[\omega_1,\omega_2]$ . We can denote  $\omega_0\in[\omega_1,\omega_2]$  a particular operating angular frequency. According to such particular characteristics, we can realize a frequency independent PS illustrated from algebraic operation based on PGD and NGD phase plot shown by Fig. 5(a). Following the ideal case behavior, it is noteworthy that the BP-NGD PS should present:

- A phase shift equal to constant  $\varphi_{PS}(\omega) = \varphi_0$  which is equal to constant or does not depend to the frequency as stated by equation (26) and depicted by Fig. 5(a).

- A zero delay in the working frequency band of the study as stated by equation (27) and highlighted by Fig. 5(b).

Before the investigation of POC, a concrete design of the proposed PS with RLC-network based lumped circuit is investigated in the next subsection.

FIGURE 5. (a) Phase and (b) GD responses of PGD, NGD, and frequency-independent PS ideal function.

# IV. S-PARAMETER MODEL OF PGD AND NGD PASSIVE CIRCUITS UNDER CONSIDERATION

The S-parameter models of the elementary circuits constituting the PGD, NGD and constant PS circuits are developed in this section.

### A. S-PARAMETER MODELLING OF PGD TOPOLOGY

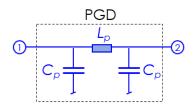

Fig. 6 represents the schematic of the PGD passive two-port circuit. It acts as a  $\pi$ -topology composed of two identical  $C_p$ -parallel capacitors connected at the input/output accesses and  $L_p$ -series inductor. This passive cell can be named CLC-circuit also in the rest of the paper.

FIGURE 6. Schematic of two-port PGD circuit constituting the BP-NGD PS under study.

The PGD-topology equivalent impedance matrix is given by:

$$[Z_{PGD}(s)] = \frac{\begin{bmatrix} 1 + L_p C_p s^2 & 1\\ 1 & 1 + L_p C_p s^2 \end{bmatrix}}{2 + C_p s (2 + L_p C_p s^2)}.$$

(30)

The S-matrix model is calculated from Z-to-S transform relationship:

$$[S_{PGD}(s)] = \begin{cases} \{ [Z_{PGD}(s)] - R_0 [I_{2-D}] \} \times \\ \{ [Z_{PGD}(s)] + R_0 [I_{2-D}] \}^{-1} \end{cases}$$

(31)

with 2-D identity matrix:

$$\begin{bmatrix} I_{2-D} \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} \tag{32}$$

Accordingly, we have the reflection and transmission coefficient expressions of the following PGD S-matrix:

$$S_{11,PGD}(s) = \frac{s \left[ L_p - R_0^2 C_p (2 + L_p C_p s^2) \right]}{D_{PGD}(s)}$$

(33)

$$S_{21,PGD}(s) = \frac{2R_0}{D_{PGD}(s)}$$

(34)

where:

$$D_{PGD}(s) = (1 + R_0 C_p s) \left[ R_0 (2 + L_p C_p s^2) + L_p s \right].$$

(35)

These analytical relations will be exploited to elaborate the analysis and design method in the following subsection.

# B. BP-NGD S-PARAMETER MODELLING AND ANALYSIS

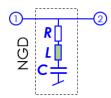

The BP-NGD topology is comprised of simple RLC-series network as parallel impedance. The two-port cell is presented by Fig. 7.

FIGURE 7. BP-NGD passive cell employed in this paper to design the constant PS.

The equivalent matrix impedance associated to the NGD passive topology is written as:

with:

$$Z(s) = R + Ls + \frac{1}{Cs}. (37)$$

The associated S-matrix model is established from Z-to-S matrix transform from relationship as expressed in equation (31). Accordingly, we have the reflection and transmission coefficient expressions of the following S-matrix of the NGD passive cell:

$$S_{11,NGD}(s) = \frac{-R_0}{R_0 + 2Z(s)}$$

(38)

$$S_{21,NGD}(s) = \frac{2Z(s)}{R_0 + 2Z(s)}$$

(39)

The model of the PGD and NGD combined cells is elaborated in the next subsection.

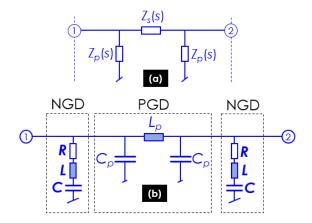

### C. II-TOPOLOGY S-PARAMETER MODELLING OF PS CIRCUIT

Figs. 8 represent the concrete circuit for designing PS passive topology. It is constituted by the combined PGD and NGD circuits schematized by the general  $\pi$ -topology shown by Fig. 8(a). The detailed configuration of the BP-NGD PS circuit including all the lumped components is depicted by Fig. 8(b).

FIGURE 8. (a) Equivalent impedance based  $\pi$ -topology and (b) two-port black box of frequency-independent PS constituted by PGD and NGD circuits in cascade.

The passive topology of the PS is composed of two identical  $Z_p$ -parallel impedances connected at the input/output accesses and  $Z_s$ -series impedance analytically given by:

$$\begin{cases}

Z_s(s) = L_s s \\

Z_p(s) = \frac{Z(s)}{1 + C s Z(s)}

\end{cases}$$

(40)

The BP-NGD PS-topology equivalent impedance matrix is given by:

$$[Z_{ps}(s)] = \Xi(s) \begin{bmatrix} Z_{s}(s) + Z_{p}(s) & Z_{p}(s) \\ Z_{p}(s) & Z_{s}(s) + Z_{p}(s) \end{bmatrix}$$

(41)

with:

$$\Xi(s) = \frac{Z_{p}(s)}{Z_{s}(s) + 2Z_{p}(s)}.$$

(42)

By means of Z-to-S matrix transform, we have the reflection and transmission coefficient expressions of the following S-matrix of the BP-NGD PS passive cell:

$$S_{11,PS}(s) = \frac{Z_s(s)Z_p^2(s) - R_0^2 \left[ Z_s(s) + Z_p(s) \right]}{D_{PS}(s)}$$

(43)

$$S_{21,PS}(s) = \frac{2R_0 Z_p^2(s)}{D_{PS}(s)}$$

(44)

with:

$$D_{PS}(s) = \left\{ \begin{bmatrix} R_0 + 2Z_p(s) \\ R_0 \left[ Z_s(s) + Z_p(s) \right] + Z_s(s) Z_p(s) \end{bmatrix} \right\}.$$

(45)

Before the design methodology of BP-NGD PS in CMOS technology, the synthesis formulas of lumped components will be investigated in the following section.

# V. SYNTHESIS FORMULAS OF THE BP-NGD CONSTANT PS

This section describes the main design formulas established from the previous analyses. The values of resistor, inductor and capacitor components constituting the BP-NGD PS are addressed in function of the targeted specifications.

# A. HYPOTHESES FOR THE PRESENT BP-NGD PS ANALYSES

For the sake of the mathematical complexity, let us take a real positive parameter  $A \ll 1$  as the hypothetical reflection loss. The synthesis of the proposed PS in the present paper is performed under matching conditions of PGD and NGD reflection coefficients:

$$\begin{cases} \left| S_{11,PGD}(j\omega) \right| = \left| S_{22,PGD}(j\omega) \right| = A \\ \left| S_{11,NGD}(j\omega) \right| = \left| S_{22,NGD}(j\omega) \right| = A \end{cases}$$

$$(46)$$

Consequently, we expect to have the PS access matching with respect to equation:

$$|S_{11,PS}(j\omega)| = |S_{22,PS}(j\omega)| = A.$$

(47)

Based on such hypothesis, the BP-NGD PS transmission coefficient can be simply approximated by the following product:

$$S_{21,PS}(j\omega) \approx S_{21,NGD}(j\omega) \cdot S_{21,PGD}(j\omega) \cdot S_{21,NGD}(j\omega)$$

. (48)

Based on such assumption, the syntheses of our PS consist in determining lumped component with respect to the targeted

specifications. The design approach can be explored from analyses from PGD and NGD circuits. The analytical elaboration of the last two ones are examined in the two next subsections.

# B. DESIGN EQUATIONS OF THE PGD CIRCUIT CONSTITUTING COMPONENTS

The analysis and synthesis of the PGD circuit is elaborated in the present subsection.

# 1) PGD CIRCUIT ANALYSIS AT THE WORKING FREQUENCY

First of all, the PGD circuit can be analyzed by the examination of magnitude of reflection coefficient expressed in equation (33) and the phase of transmission coefficient expressed in equation (34). We can choose as particular angular frequency:

$$\omega = \frac{1}{\sqrt{L_p C_p}} \,. \tag{49}$$

Secondly, it is important to underline that at this angular frequency, the PGD circuit shown by Fig. 6 is in phase quadrature:

$$\varphi_{PGD}(\omega_0) = -\pi/2. \tag{50}$$

The PGD circuit synthesis consists practically in determining the constituting components inductor  $L_p$  and capacitor  $C_p$  to target the particular operation angular frequency and reflection coefficient A << 1 by solving equations:

$$\omega = \omega_0 \tag{51}$$

$$\left| S_{11,PGD}(j\omega_0) \right| = A. \tag{52}$$

In this case, we have:

The transmission coefficient written in equation (34) becomes:

$$|S_{21,PGD}(j\omega_0)| = \sqrt{1 - A^2}$$

(53)

• The GD defined in equation (5) applied to equation (34) becomes:

$$GD_{PGD}(\omega_0) = t_{p} \tag{54}$$

which is given by:

$$t_p = \frac{2\sqrt{1 - A^2}}{\omega_0} \,. \tag{55}$$

These analytical equations serve to characterize our PGD circuit as described in the following paragraph.

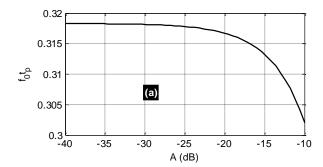

### 2) GRAPHICAL ANALYSIS

By using equation (55), the variation of the PGD GD and working frequency product versus reflection coefficient *A* is plotted in Fig. 9(a). We can see that the product variation is not significant when *A* increases to -40 dB to -10 dB. Consequently, based on such increase of reflection coefficient, we see that the GD-working frequency product decreases from 0.318 to 0.302.

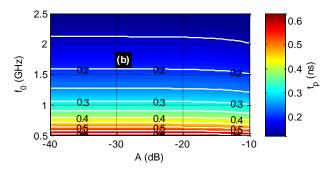

The cartographies of the PGD GD  $t_p$  versus pair working frequency varying from  $f_{min}$ =0.5 GHz and  $f_{max}$ =2.5 GHz and reflection coefficient A is displayed in Fig. 9(b). In the considered range of pair  $(A, f_0)$ , we emphasized that  $t_p$  is decreasing from 0.637 ps to 120 ps inversely to  $f_0$  and A.

FIGURE 9. Plots of PGD (a) GD-working frequency and (c) GD cartography versus pair  $(A, f_0)$ .

### 3) SYNTHESIS FORMULAS

The design equations of the PGD circuit are established by inversing the equation of reflection coefficient and GD. Accordingly, the PGD-circuit synthesis formulas derived from the previous equations are:

$$L_p = \frac{R_0}{\omega_0} \sqrt{\frac{1+A}{1-A}} \tag{56}$$

$$C_{p} = \frac{\sqrt{\frac{1-A}{1+A}}}{R_{0}\omega_{0}} \,. \tag{57}$$

The other formulas for calculating the other components of the PS are established from the analysis of the BP-NGD circuit and the PS shown by Fig. 7 and Fig. 8, respectively. The BP-NGD circuit analysis are introduced in the following subsection.

# C. ANALYSIS AND SYNTHESIS OF BP-NGD CIRCUIT CONSTITUTING COMPONENTS

As stated in [29-36], the BP-NGD circuit must operate in opposite phase of the PGD one. The NGD block ideal specification will be defined in the following paragraph.

The BP-NGD circuit shown in Fig. 7 was analyzed by the examination of magnitude of reflection coefficient

expressed in equation (38) and the GD associated to the transmission coefficient expressed in equation (39) at the particular angular frequency:

$$\omega = \frac{1}{\sqrt{LC}} \,. \tag{58}$$

It should be pointed out that at this angular frequency, the NGD circuit presents the phase from equation (39) equal to:

$$\varphi_{NGD}(\omega_0) = 0. (59)$$

In this case, we have:

The reflection coefficient written in equation (38) becomes:

$$\left| S_{11,NGD}(j\omega_0) \right| = \frac{R_0}{R_0 + 2R} \,.$$

(60)

• The transmission coefficient written in equation (39) becomes:

$$\left| S_{11,NGD}(j\omega_0) \right| = \frac{R_0}{R_0 + 2R} \,.$$

(61)

• The GD defined in equation (5) applied to equation (39) becomes:

$$GD_{NGD}(\omega_0) = t_n . (62)$$

which is given by:

$$t_n = \frac{-2R_0L}{R(R_0 + 2R)}. (63)$$

The BP-NGD circuit synthesis equations are established in the following subsection.

# D. ELABORATION OF NGD CIRCUIT COMPONENT SYNTHESIS

The NGD circuit synthesis is naturally the calculations of the constituting components resistor R, inductor L and capacitor C to target:

- The particular operation angular frequency as stated in equation (51).

- The reflection coefficient verifying:

$$\left| S_{11,NGD}(j\omega_0) \right| = A \tag{64}$$

• The GD equalized from equation (28) which leads to the equation:

$$\frac{2R_0L}{R(R_0 + 2R)} = \frac{t_p}{4} \tag{65}$$

Lastly, the NGD-circuit synthesis formulas derived from the previous equations are:

$$R = \frac{R_0(1-A)}{2A} \tag{66}$$

$$L = \frac{R_0}{8A^2\omega_0} \sqrt{\frac{1+A}{1-A}} \tag{67}$$

$$C = \frac{8A^2}{R_0 \rho_0} \sqrt{\frac{1-A}{1+A}} \,. \tag{68}$$

Knowing the resistor synthesis equation, the transmission coefficient written in equation (34) becomes:

$$|S_{21.NGD}(j\omega_0)| = 1 - A$$

. (69)

Further insight on the BP-NGD characteristics can be established from these R, L and C component synthesis equations.

### E. **BP-NGD BANDWITH CIRCUIT VERSUS** REFLECTION COEFFICIENT

The analysis of the BP-NGD bandwidth is described in the present subsection.

### 1) ANALYTICAL EXPRESSION

The GD of the BP-NGD circuit shown in Fig. 7 can be expressed from the transmission coefficient introduced in equation (39) and definition (5). The NGD cut-off angular frequencies are determined by solving equation (7). Following these analytical actions, it can be derived from synthesis equations (66), (67) and (68), the NGD cut-off frequencies versus reflection coefficient and center frequency given by:

$$\omega_{1} = \omega_{0} \sqrt{\frac{1 + 8A^{3}(A - 2) + A\left[1 + 4(a - 1)\sqrt{\lambda}\right]}{A + 1}}$$

$$\omega_{2} = \sqrt{\frac{1 + 8A^{3}(A - 2) + A\left[1 + 4(1 - a)\sqrt{\lambda}\right]}{A + 1}}$$

(70)

$$\omega_2 = \sqrt{\frac{1 + 8A^3(A - 2) + A\left[1 + 4(1 - a)\sqrt{\lambda}\right]}{A + 1}}$$

(71)

$$\lambda = 1 + A + 4A^{2}(A - 1)^{2}. \tag{72}$$

It implies the NGD relative BW which is defined  $\Delta \omega / \omega_0 = \Delta f / f_0$  by formula:

$$\frac{\Delta f}{f_0} = \frac{4A(1-A)\left[2A(A-1) + \sqrt{\lambda}\right]}{\sqrt{(1+A)\left\{1 + A\left[1 + 4(A-1)\left[2A^2(A-1) + \sqrt{\lambda}\right]\right]\right\}}} . (73)$$

### 2) GRAPHICAL ANALYSIS

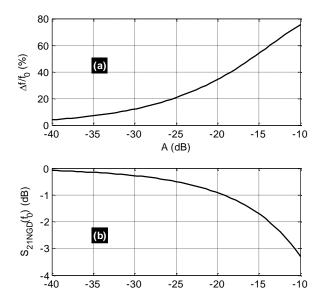

For further insight about the variation of previously expressed parameters, graphical analyses of the NGD relative bandwidth and transmission coefficient are performed in the present paragraph when A increases from -40 dB to -10 dB. Accordingly, Fig. 10(a) represents the monotonic variation of the NGD BW expressed by equation (70). We find that this relative frequency increases almost linearly from about 4% to 75.4%. However, the transmission coefficient variation decreases from -3.3 dB to -0.09 dB as witnessed by in Fig. 10(b).

Before the numerical verification of the established microwave theory feasibility, the next subsection describes the design of POC to be investigated and also the associated methodology for 130-nm BiCMOS BP-NGD PS.

FIGURE 10. Variations of (a) NGD BW and (b) transmission coefficient versus reflection coefficient at the operation frequency.

A (dB)

### VI. METHODOLOGY AND DESCRIPTION OF 130-nm **BICMOS BP-NGD PS DESIGN**

The present section describes the CMOS methodology of the BP-NGD PS topology. A POC designed in 130-nm BiCMOS technology by using an IC design and simulation commercial tool will be introduced.

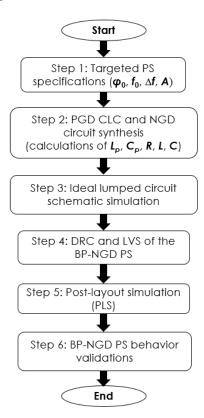

### A. DESIGN METHODOLOGY OF THE BP-NGD PS IN **CMOS TECHNOLOGY**

Similar to the CMOS design method of NGD ICs introduced in [41-43], the proposed BP-NGD PS one should start from the targeted specifications to the final layout design. The main actions behind the design methodology of BP-NGD PS ICs are indicated by the design flow depicted by Fig. 11. The proposed six principal steps of the CMOS IC design can be described as follows:

- **Step 1**: The choice of the BP-NGD PS specifications as phase shift (fixed to  $\varphi_0$ =-90° for the present study) working frequency and reflection loss which is linked to the attenuation. The designer can refer to the specifications plotted by Figs. 5.

- Step 2: The ideal values of resistor, inductor and capacitor constituting the BP-NGD PS IC should be calculated. For this step, the design engineers can use formulas (56), (57), (66), (67) and (68).

- Step 3: The previously calculated values must be verified in the component library of the simulation software (for the present study, Cadence-VURTUOSO®). Then, the feasibility of the BP-NGD PS CMOS IC design should be investigated by the

VOLUME XX 2022 1

- comparison between the calculated results of S-parameter simulations.

- Step 4: The layout design should begin in the present step after schematic ideal simulation. The BP-NGD PS CMOS IC must respect the design rule check (DRC) with high Ohmic unsalicided N+poly resistor and symmetrical high current spiral inductor. The DRC ensures that the design can be manufactured within the limits of production process. The layout versus schematic (LVS) of BP-NGD PS CMOS IC must be performed. The LVS consists in evaluating the differences by comparing the results of circuit diagram with its layout.

- Step 5: The effects of parasitic capacitances and resistors on the BP-NGD PS CMOS IC performances can be investigated in this present step. In all, the simulations should focus on the circuit layout. Further modifications on the IC design maybe proposed in order to meet the expected constant PS performances.

- Step 6: The final action of the BP-NGD PS CMOS IC design is the post-layout simulation (PLS). Any modifications can be made, in particular at the layout level, to improve the results All the rules of DRC should be validated and the result acceptability can be assessed following the targeted specifications defined in Step 1.

FIGURE 11. Design flow of BP-NGD PS CMOS IC.

Following the elaborated design methodology, the BP-NGD PS POC is designed in 130-nm BiCMOS technology in the following section.

### B. DESCRIPTION OF THE BP-NGD PS POC DESIGN

The POC design of the BP-NGD PS under study in 130-nm BiCMOS technology is investigated in the present subsection. The different steps of work flow indicated by Fig. 11 were followed during the design.

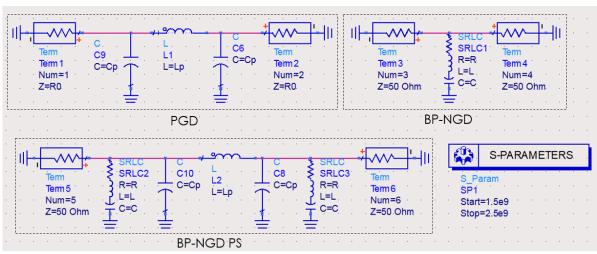

The BP-NGD PS specifications are arbitrarily chosen in order to highlight the microwave CMOS IC design feasibility study. The main specifications including the consideration of the investigation frequency band are indicated in Table I. The IC design focuses first on the BP-NGD and PGD circuits. Then, the combined circuit is designed to analyze the PS behavior. As result, Fig. 12 represents the schematics of the PGD, NGD and PS POC designed in the environment of the ADS® electronic and RF/microwave simulation tools from Keysight technologies®.

TABLE I SPECIFICATIONS OF THE BP-NGD PS CIRCUIT POC

| Circuit | Parameter                | Arbitrary chosen value     |

|---------|--------------------------|----------------------------|

|         | Center frequency         | $f_0 = 1.9 \text{ GHz}$    |

| PS      | Phase shift              | $\varphi_0=90^\circ$       |

| P3      | Bandwidth                | $\Delta f=0.2 \text{ GHz}$ |

|         | Reflection coefficient   | -25 dB                     |

|         | Center frequency         | $f_p = f_0$                |

| DCD     | PGD value                | $t_p = -156 \text{ ps}$    |

| PGD     | Reflection coefficient   | $A_p=-15 \text{ dB}$       |

|         | Transmission coefficient | $B_p$ =-1 dB               |

| NGD     | Center frequency         | $f_n = f_0$                |

|         | NGD value                | $t_n$ =-78 ps              |

|         | Reflection coefficient   | $A_n=-15 \text{ dB}$       |

|         | Transmission coefficient | $B_n$ =-6 dB               |

The component values of resistor, inductor and capacitor constituting the constant phase BP-NGD PS were calculated from formulas (56), (57), (66), (67) and (68). The calculated results of POC PGD and NGD R, L and C parameters are addressed in Table II.

$\label{eq:Table II} \mbox{Parameters of the PGD and NGD Circuits Constituting the PS}$

| Circuit | Parameter | Calculated components |  |  |

|---------|-----------|-----------------------|--|--|

| PGD     | Inductor  | $L_p=5 \text{ nH}$    |  |  |

| - TOD   | Capacitor | $C_p=1.4 \text{ pF}$  |  |  |

|         | Resistor  | R=116 Ω               |  |  |

| NGD     | Inductor  | <i>L</i> =20 nH       |  |  |

|         | Capacitor | <i>C</i> =0.35 pF     |  |  |

The BiCMOS BP-NGD PS design is described in the following subsection.

# C. DESCRIPTION OF THE BP-NGD PS LAYOUT OF CMOS IC DESIGN

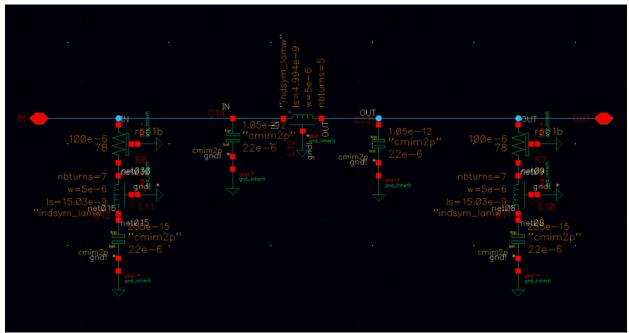

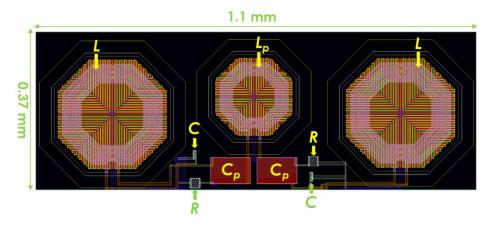

The CADENCE VIRTUOSO® design of the PS schematic is displayed in Fig. 13. The STMicroelectronics 130-nm BiCMOS manufacturing process was chosen as main reference for the present microwave PS design because of its component integration potential in the range of desired specification values.

Due to the relatively large size of the components, expensive manufacturing processes such as 28 nm-FDSOI are not needed. Fig. 14 displays the layout of the designed CMOS IC PS chipset. This PS POC layout is designed with  $1.1 \text{ mm} \times 0.37 \text{ mm}$  size. The resistors and inductor were expected to be implemented under the manufacturing process minimum square area. The SISO circuit whole layout area is occupied by the two resistors in left and the

large spiral inductor. The  $100~\mu m \times 4.9~\mu m$  size resistors are implemented in 100-nm thickness poly-Si on 4.5-relative permittivity dielectric insulator. Each resistor is guard-ring surrounded in order to ensure their polarization and the ground plane connection through the dielectric substrate.

The inductor is implemented in Al-metal spiral octagon with 0.0145 mm² surface over 1  $\mu m$  thickness. All the layout component interconnections are Cu-based interconnect metallization with 0.1  $\mu m$  thickness.

The range of the geometrical parameters (width, length, number of turns, diameter, Silicium area) of the considered resistor and inductor layouts in function of the constituting materials are addressed in Table III and Table IV, respectively. The minimal resonance frequency is also indicated.

FIGURE 12. ADS® schematic of the BP-NGD PS POC.

| Description | Type of resistor design       | Width, w  |           | Length, d |           | Resistor value |           |

|-------------|-------------------------------|-----------|-----------|-----------|-----------|----------------|-----------|

| Parameter   | Unsalicided N+active resistor | $w_{min}$ | $W_{max}$ | $d_{min}$ | $d_{max}$ | $R_{min}$      | $R_{max}$ |

| Value       | rpo1b                         | 1 μm      | 100 μm    | 3 µm      | 100 µm    | 4 Ω            | 13 kΩ     |

$\label{thm:table III} \textbf{Ranges of Geometrical Parameters of the Used Designed Inductor}$

| Description | Type of inductor                  | Wi               | Ith, w Diameter, $\phi$ |                         | Number of turns, N |           | Inductor value |                     |           |  |

|-------------|-----------------------------------|------------------|-------------------------|-------------------------|--------------------|-----------|----------------|---------------------|-----------|--|

| Parameter   | Inductor symmetrical high current | $W_{min}$        | $W_{max}$               | $\phi_{min}$            | $\phi_{max}$       | $N_{min}$ | $N_{max}$      | $L_{min}$           | $L_{max}$ |  |

| Value       | indsym_lamw                       | 5 μm             | 12 µm                   | 53 µm                   | 163 µm             | 2         | 9              | 3.8 nH              | 25.8 nH   |  |

| Description | Type of inductor                  | Type of inductor |                         |                         | Si area, S         |           |                | Resonance frequency |           |  |

| Parameter   | Inductor symmetrical high         | h current $S_n$  |                         | $S_{max}$               |                    | $f_{min}$ | $f_{max}$      |                     |           |  |

| Value       | indsym_lamw                       | 0.               |                         | 4 mm <sup>2</sup> 0.096 |                    | 1 mm²     | 3.33 GHz       | 91.4 GHz            |           |  |

FIGURE 13. Cadence® schematic of the BP-NGD PS POC.

FIGURE 14. Chip Cadence-VIRTUOSO® layout (1.1 mm x 0.37 mm=0.407 mm²) of BP-NGD PS POC.

# VII. VERIFICATION RESULTS AND MC UNCERTAINTY ANALYSES OF THE DESIGNED 130-nm BiCMOS POC

The present section deals with the numerical verification of the BP-NGD PS topology. The frequency dependent BP-NGD PS behavior will be discussed. The compared and obtained results are from:

- Calculations computed ideal circuit models from MATLAB®,

- Simulation of ideal schematic circuits with the ADS® electronic and RF/microwave simulation tool from Keysight technologies®,

and IC design and simulation of CMOS IC BP-NGD PS having schematic shown in Fig. 13 and layout shown in Fig. 14 with CADENCE VIRUTOSO®.

The presented results are generated in the frequency band delimited by  $f_{min}$ =1.5 GHz and  $f_{max}$ =2.3 GHz which contains intentionally the expected working frequency  $f_0$ =1.9 GHz. The CADENCE VIRTUOSO® MC uncertainty analyses in function of IC BP-NGD PS physical parameters will be performed.

### A. PGD AND NGD CHARACTERISATION

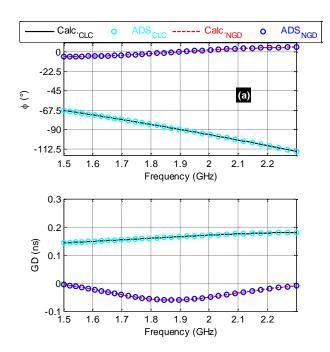

The synthesized CLC (which represents the PGD circuit) or and NGD circuits are characterized from the phase,  $GD_{CLC,NGD}$ ,  $S_{11CLC,NGD}$  and  $S_{21CLC,NGD}$  analyses. As

depicted by Figs. 15 and Figs. 16, the calculated and simulated results are in excellent correlation. Fig. 15(a) shows the comparison between:

- The calculated ("Calc.<sub>CLC</sub>" plotted in black solid line) and ADS® simulated ("ADS<sub>CLC</sub>" plotted in dotted blue-sky line) of the CLC-circuit alone. The phase presents a clear negative slope with phase shift  $\varphi_{CLC}(f_0)\approx -90^{\circ}$ .

- The calculated ("Calc.<sub>CLC</sub>" plotted in dashed red line) and ADS® simulated ("ADS<sub>CLC</sub>" plotted in dotted navy-blue line) of the CLC-circuit alone. The phase presents a clear negative slope with phase shift  $\varphi_{NGD}(f_0)\approx 0^{\circ}$ .

FIGURE 15. Comparison of calculated and simulated (a) phases and (b) GDs of the PGD and NGD circuits.

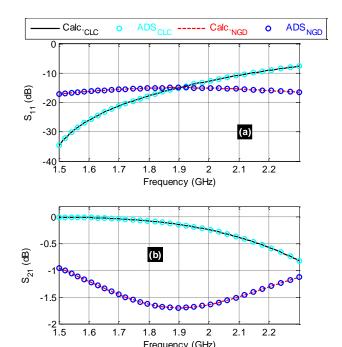

The corresponding GDs are displayed by Fig. 15(b) which shows NGD from  $f_1$ =1.456 GHz to  $f_2$ =2.48 GHz with  $GD_{NGD}(f_0)\approx$ -61 ps. The NGD effect compensates the PGD which presents  $GD_{CLC}(f_0)\approx$ 165 ps. Fig. 16(a) confirms that the CLC and NGD circuits are matched to  $S_{11CLC,NGD}(f_0)\approx$ -13 dB around the expected working frequency. Both circuits present transmission coefficients better than  $S_{21CLC,NGD}(f_0)>$ -2 dB as illustrated by Fig. 16(b) confirms that the CLC and NGD circuits. The results of the combined CLC and NGD circuits designed in 130-nm BiCMOS IC technology with parameters indicated by Table II and Table III are examined in the next subsection.

FIGURE 16. Comparison of calculated and simulated (a)  $S_{11}$  and (b)  $S_{21}$  of the PGD and NGD circuits.

### B. BICMOS IC DESIGNED BP-NGD CONSTANT PS VERICATION RESULT

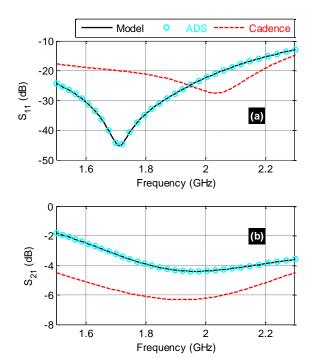

The verification of the IC design feasibility was performed based on comparisons between:

- Calculated ("Model" plotted in black solid line) results from ideal model,

- ADS® simulated ("ADS" dotted in blue-sky dotted line) results from ideal schematic.

- CADENCE VIRTUOSO® simulated ("Cadence" dotted in blue-sky dotted line) results from BiCMOS IC layout.

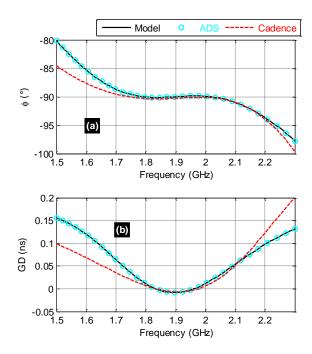

Fig. 17(a) displays the BP-NGD PS phase and the associated GDs are plotted in Fig. 17(b). A good agreement between the 130-nm BiCMOS designed BP-NGD PS POC and ideal ones (MATLAB® calculation and ADS® simulation) PSs and GDs are obtained.

As expected, they confirm undeniably the constant PS behavior with GD less than 10 ps around the working frequency. A good correlation of the behavior of the independent frequency phase shift around the working frequency  $f_0$ =1.9 GHz is shown in Fig. 17(a). Table IV summarizes the BP-NGD PS specifications from the POCs of ideal and BiCMOS IC BP-NGD PS circuits shown in Figs. 12 and 14.

FIGURE 17. Comparison of calculated and simulated (a) phases and (b) GDs of the BP-NGD PS POC.

FIGURE 18. Comparison of calculated and simulated (a)  $S_{11}$  and (b)  $S_{21}$  of the BP-NGD PS POC.

As results, we have the remarkable phase variations:

- $\Delta \varphi(f_0+/-\Delta f/2)=-90^{\circ}\pm 1^{\circ}$  in the bandwidth delimited by  $f_{low-PS}=1.75$  GHz and  $f_{high-PS}=2.1$  GHz from ideal circuit,

- against  $\Delta \varphi(f_0+/-\Delta f/2)=-90^{\circ}\pm 0.4^{\circ}$  in the bandwidth delimited by  $f_{low-PS}=1.7$  GHz and  $f_{high-PS}=2.05$  GHz from the BiCMOS POC.

TABLE IV

SPECIFICATIONS OF THE CONSIDERED IDEAL CIRCUIT AND BICMOS

LAYOUT BP-NGD PS

| Parameters                       | Calculated    | ADS®          | Cadence®      |  |

|----------------------------------|---------------|---------------|---------------|--|

| $f_{low-PS}$                     | 1.75 GHz      | 1.75 GHz      | 1.7 GHz       |  |

| $f_{high-PS}$                    | 2.1 GHz       | 2.1 GHz       | 2.05 GHz      |  |

| $(f_{high-PS} - f_{low-PS})/f_0$ | 18.4%         | 18.4%         | 18.4%         |  |

| $\varphi(f_0)$                   | -90°          | -90°          | -90.3°        |  |

| Δφ (°)                           | -90+/-1°      | -90+/-1°      | -90+/-0.4°    |  |

| $\Delta S_{21}(f_0)$             | -2.8+/-0.5 dB | -2.8+/-0.5 dB | -5.3+/-0.7 dB |  |

In addition, the associated reflection and transmission coefficients of the BP-NGD PS are plotted in Figs. 18. They show a good access matching better than  $S_{11}(f_0)$ <-15 dB in the considered frequency band PS BW. Moreover, the PS flatness transmission coefficient is less than 1 dB. The main differences between  $S_{11}$  and  $S_{21}$  observed in Figs. 17 are due to the CMOS distributed component designed.

To highlight the proposed design robustness of the 130-nm BiCMOS PS, MC UAs were run and the results are discussed in the following subsection.

### C. MC UAS OF THE BICMOS IC BP-NGD PS

The carried-out UAs were performed by considering the geometrical parameters of the implemented resistor and inductor by means of the PLS of BiCMOS IC PS. Based on statistical approach, all parameters are simultaneously changed under +/-5% variations. The references values of the resistor and inductor parameters are indicated by Table II and Table III, respectively.

The following paragraphs are discussing the obtained CADENCE VIRTUOSO® based simulation results following the MC UAs with n=1000-trials via Gaussian distribution statistical probability (DSP).

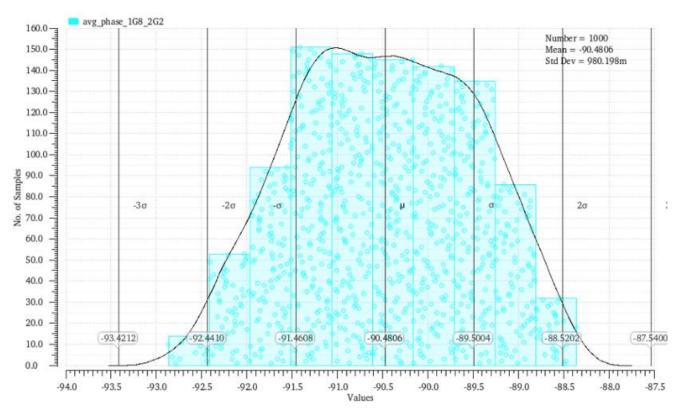

# 1) MC UA OF IC BP-NGD PS PHASE SHIFT AVERAGE IN THE CONSIDERED BW

In this first case of study, the UAs were based on the CADENCE-VIRTUOSO® simulations by considering +/-5% variations of the BP-NGD PS POCs initial parameters (through standard deviations). The obtained average phase shift denoted  $\varphi_{ave}$  from  $f_{low\text{-}PS}$ =1.7 GHz and  $f_{high\text{-}PS}$ =2.05 GHz was considered for the statistical analyses of the samples in the intervals delimited by the one, two and three times multiple of standard deviation. The statistical analyses from the computed results lead to the flat typical Gaussian variations with assessed values. Fig. 19 presents the histogram and DSP of  $\varphi_{ave}$  from BP-NGD PS chip POC. Significant probability of phase variation is observed from -91.5° to -89.5°.

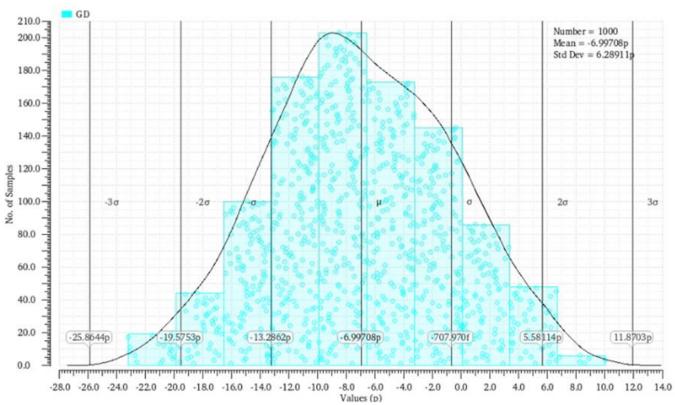

### 2) PS GD AVERAGE

Like the previous case, the statistical analyses of GD were performed from the CADENCE® simulated results. All the physical parameters of the BiCMOS IC BP-NGD

VOLUME XX. 2022

GD were varied in the same frequency band. The average value of the GD results from  $f_{low-PS}$ =1.7 GHz and  $f_{high-PS}$ =2.05 GHz enables to establish the accentuated Gaussian variations with assessed values. Fig. 20 presents the histogram of average value  $GD_{ave}$ . The GD mean value is of about 7 ps with high DSP over standard deviation 6.3 ps.

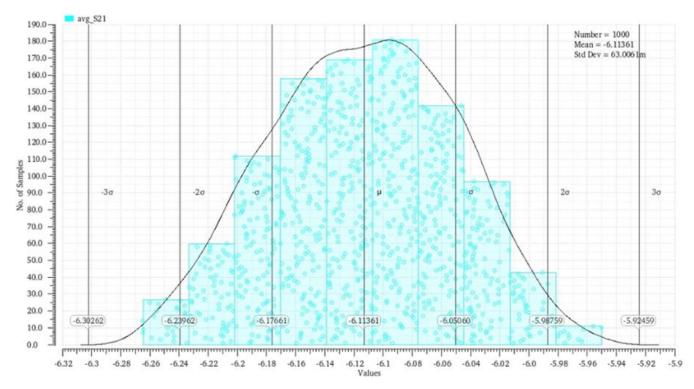

### 3) PS S21 AVERAGE

By means of the same MC UAs, the transmitted coefficient of the BP-NGD IC POS was analyzed. We assess then the average value if the transmission coefficient in the same previous bandwidth from  $f_{low-PS}$  and  $f_{high-PS}$ . Fig. 21 displays the histogram and DSP of  $S_{21ave}$ . The mean statistical value is of about -6.11 dB over standard deviation of about 0.6 dB.

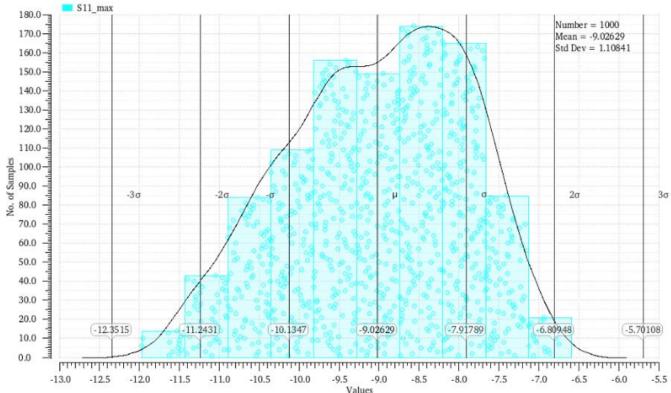

### 4) PS S<sub>11</sub> MAXIMUM

The last case MC UA of BP-NGD PS POC UA is focused on the reflection coefficient. The analysis is based on the assessment of maximum  $S_{11\text{max}} = \max[S_{11}(f)]$ . Fig. 22 depicts the histogram and DSP of  $S_{11ave}$ . We can emphasize that mean value is of about -9.1 dB over the standard deviation of about 1.1 dB. This result enables to state that our BiCMOS PS presents a risk of unmatching

if the physical parameters varied over +/-5% relative variation.

5) SUMMARY OF MEAN AND STANDART DEVIATION Based on the previous results, Table V addresses the summary of the MC UAs. We recall that the statistical run was repeated with 1000 trials.

TABLE V IC BP-NGD PS MEAN AND STANDARD DEVIATIONS FROM n=1000 TRIAL UAS

| PS characteristics | Statistical parameter | Value    |  |

|--------------------|-----------------------|----------|--|

|                    | Mean                  | -90.48°  |  |

| $arphi_{ave}$      | Standard deviation    | 0.98°    |  |

| CD                 | Mean                  | 7 ps     |  |

| $GD_{ave}$         | Standard deviation    | 6.3 ps   |  |

| C                  | Mean                  | -6.11 dB |  |

| $S_{21ave}$        | Standard deviation    | 0.63 dB  |  |

| C                  | Mean                  | -9.1 dB  |  |

| $S_{11max}$        | Standard deviation    | 1.1 dB   |  |

The last explored table indicates the mean values and standard deviations of the four previously discussed specific characteristics analyzed. Less relative variation of physical parameters should be expected to ensure BP-NGD phase shift respecting the criteria of microwave circuits in  $f_{low-PS}$ =1.7 GHz and  $f_{high-PS}$ =2.05 GHz.

FIGURE 19. Histogram of  $\phi_{ave}(f)$  average from the BP-NGD PS MC UA.

FIGURE 20. Histogram of GDPS average from the BP-NGD PS MC UA.

FIGURE 21. Histogram of S<sub>21ave</sub>(f) average from the BP-NGD PS MC UA.

VOLUME XX, 2022

FIGURE 22. S<sub>11max</sub>(f<sub>0</sub>) histogram from the BP-NGD PS MC UA

### VIII. CONCLUSION

An original research work on BP-NGD microwave engineering application for designing miniature quadrature passive PS operating independently to the frequency is developed. The investigated PS IC using unfamiliar BP-NGD function is innovatively designed in 130-nm BiCMOS technology.

The theoretical approach based on the S-matrix modelling is elaborated. The main principle of the BP-NGD PS topology is implemented from the cascade of PGD and NGD circuits. The PGD circuit is constituted by inductor and capacitor which named CLC reactive network. The NGD one is composed of RLC-resonant network. The modelling, analysis and synthesis of BP-NGD and CLC PGD are introduced. The synthesis equations enabling to determine the lumped circuit parameters in function of the targeted working frequency, phase shift, GD and reflection coefficient are established.

To generalize the BP-NGD PS concept in BiCMOS technology, the design methodology of IC including the DRC, LVS and PLS is described. The design feasibility of the miniaturized BP-NGD PS is verified in 130-nm BiCMOS technology by using a standard commercial tool.

The obtained results confirm the IC designability of the BP-NGD PS. As expected, the constant phase shift of about -90+/-1° with outstanding challenging flatness is obtained. Moreover, the PS flatness is verified over 18.4% relative bandwidth. Furthermore, interesting flatness's of transmission coefficient phase and magnitude is verified. The robustness of the PS expected during the fabrication process is expected with 1000-trial MC UAs. The sensitivities of the constant PS characteristics are pointed out in function of the relative variations of layout IC physical parameters.

As ongoing research in continuation of the present study, we are currently working on:

- The fabrication and test of BiCMOS BP-NGD PS prototypes,

- The feasibility of BP-NGD PS at higher frequencies as W-band,

- The integration and test of multi-band BP-NGD PS in for phased array antenna design [40-43],

- And the real environment characterization test of miniaturized CMOS and MMIC PS for the future 5G and 6G TxRx microwave system.

### **REFERENCES**

- B. Ségard and B. Macke, "Observation of Negative Velocity Pulse Propagation," Phys. Lett. A, Vol. 109, 1985, pp. 213-216.

- [2] J. N. Munday and W. M. Robertson, "Observation of Negative Group Delays within a Coaxial Photonic Crystal Using an Impulse Response Method," Optics Communications, Vol. 273, No. 1, 2007, pp. 32-36.

- [3] B. Ségard and B. Macke, "Two-pulse interference and superluminality," Optics Communications, Vol. 281, No. Jan. 2008, pp. 12–17.

- [4] G. V. Eleftheriades, O. Siddiqui, and A. K. Iyer, "Transmission Line for Negative Refractive Index Media and Associated Implementations without Excess Resonators," IEEE Microw. Wireless Compon. Lett., Vol. 13, No. 2, pp. 51-53, Feb. 2003.

- [5] O. F. Siddiqui, M. Mojahedi and G. V. Eleftheriades, "Periodically Loaded Transmission Line With Effective Negative Refractive Index and Negative Group Velocity," IEEE Trans. Antennas Propagat., Vol. 51, No. 10, Oct. 2003, pp. 2619-2625.

- [6] Z. Wang, Y. Cao, T. Shao, S. Fang and Y. Liu, "A Negative Group Delay Microwave Circuit Based on Signal Interference Techniques," IEEE Microw. Wireless Compon. Lett., vol. 28, no. 4, pp. 290-292, Apr. 2018.

- [7] B. Ravelo and S. De Blasi, "An FET-Based Microwave Active Circuit with Dual-Band Negative Group Delay", JMOe, Vol. 10, No. 2, Dec. 2011, pp. 355-366.

- [8] B. Ravelo, "Innovative Theory on Multiband Negative Group Delay Topology Based on Feedback Loop Power Combiner", IEEE Tran. CAS II: Express Briefs, Vol. 63, No. 8, Aug. 2016, pp. 738-742.

- [9] X. Zhou, B. Li, N. Li, B. Ravelo, X. Hu, Q. Ji, F. Wan, and G. Fontgalland, "Analytical Design of Dual-Band Negative Group Delay Circuit with Multi-Coupled Lines," IEEE Access, Vol. 8, No. 1, Apr. 2020, pp. 72749-72756.

- [10] G. Liu and J. Xu, "Compact transmission-type negative group delay circuit with low attenuation," Electron. Lett., vol. 53, no. 7, pp. 476-478. Mar. 2017.

- [11] T. Shao, Z. Wang, S. Fang, H. Liu, and S. Fu, "A compact transmission line self-matched negative group delay microwave circuit," IEEE Access, vol. 5. pp. 22836-22843, Oct. 2017.

- [12] T. Shao, S. Fang, Z. Wang and H. Liu, "A Compact Dual-Band Negative Group Delay Microwave Circuit," Radio Engineering, vol. 27, no. 4, pp. 1070-1076, Dec. 2018.

- [13] B. Ravelo, "Similitude between the NGD function and filter gain behaviours," Int. J. Circ. Theor. Appl., Vol. 42, No. 10, Oct. 2014, pp. 1016–1032.

- [14] B. Ravelo, "On the low-pass, high-pass, bandpass and stop-band NGD RF passive circuits," URSI Radio Science Bulletin, Vol. 2017, No. 363, Dec. 2017, pp. 10-27.

- [15] B. Ravelo, "First-order low-pass negative group delay passive topology," Electronics Letters, Vol. 52, No. 2, Jan. 2016, pp. 124– 126.

- [16] R. Randriatsiferana, Y. Gan, F. Wan, W. Rahajandraibe, R. Vauché, N. M. Murad and B. Ravelo, "Study and Experimentation of a 6-dB Attenuation Low-Pass NGD Circuit," Analog. Integr. Circ. Sig. Process., vol. 110, pp. 105–114, Jan. 2022.

- [17] E. J. R. Sambatra, A. Jaomiary, S. Ngoho, S. S. Yazdani, N. M. Murad, G. Chan and B. Ravelo, "Low-pass negative group delay modelling and experimentation with tri-port resistorless passive cross-circuit," Progress In Electromagnetics Research (PIER) M, Vol. 108, pp. 39-51, 2022.

- [18] F. Wan, X. Huang, K. Gorshkov, B. Tishchuk, X. Hu, G. Chan, F. E. Sahoa, S. Baccar, M. Guerin, W. Rahajandraibe and B. Ravelo, "High-pass NGD characterization of resistive-inductive network based low-frequency circuit," COMPEL The International Journal for Computation and Mathematics in Electrical and Electronic Engineering, Vol. 40, No. 5, pp. 1032-1049, 2021.

- [19] R. Yang, X. Zhou, S. S. Yazdani, E. Sambatra, F. Wan, S. Lalléchère and B. Ravelo, "Analysis, design and experimentation of high-pass negative group delay lumped circuit," Circuit World, 2021, pp. 1-25.

- [20] S. Fenni, F. Haddad, A. Jaomiary, S. S. Yazdani, F. E. Sahoa, L. Ramifidisoa, M. Guerin, W. Rahajandraibe, and B. Ravelo, "Investigation on four-port mono-capacitor circuit with high-pass negative group delay behavior", Int. J. Circ. Theor. Appl., Vol. 50, No. 2, Feb. 2022, pp. 478-495.

- [21] H. Jia, F. Wan, J. Frnda, M. Guerin, W. Rahajandraibe, P. Thakur, A. Thakur, B. Agnus and B. Ravelo, "Novel Tee-Shaped Topology Theory of Low- and High-Pass NGD Double-Type Function," IEEE Access, Vol. 10, No. 1, 2022, pp. 28445 28460.

- [22] M. Guerin, Y. Liu, A. Douyère, G. Chan, F. Wan, S. Lalléchère, W. Rahajandraibe, and B. Ravelo, "Design and Synthesis of Inductorless Passive Cell Operating as Stop-Band Negative Group Delay Function," IEEE Access, Vol. 9, No. 1, July 2021, pp. 100141–100153

- [23] S. Fenni, F. Haddad, K. Gorshkov, B. Tishchuk, A. Jaomiary, F. Marty, G. Chan, M. Guerin, W. Rahajandraibe and B. Ravelo, "AC low-frequency characterization of stop-band negative group delay circuit," Progress In Electromagnetics Research C (PIER C), Vol. 115, pp. 261-276, 2021.

- [24] J. -K. Xiao, Q. -F. Wang and J. -G. Ma, "Negative Group Delay Circuits and Applications: Feedforward Amplifiers, Phased-Array Antennas, Constant Phase Shifters, Non-Foster Elements, Interconnection Equalization, and Power Dividers," IEEE Microwave Magazine, vol. 22, no. 2, pp. 16-32, Feb. 2021.

- [25] C. D. Broomfield and J. K. A. Everard, "Broadband Negative Group Delay Networks for Compensation of Oscillators, Filters and Communication Systems," Electron. Lett., Vol. 36, No. 23, pp. 1931-1933, Nov. 2000.

- [26] K.-P. Ahn, R. Ishikawa and K. Honjo, "Group Delay Equalized UWB InGaP/GaAs HBT MMIC Amplifier using Negative Group Delay Circuits," IEEE Trans. Microw. Theory Techn., Vol. 57, No. 9, Sept. 2009, pp. 2139-2147.

- [27] B. Ravelo, S. Lalléchère, A. Thakur, A. Saini and P. Thakur, "Theory and circuit modelling of baseband and modulated signal delay compensations with low- and band-pass NGD effects," Int. J. Electron. Commun., Vol. 70, No. 9, Sept. 2016, pp. 1122–1127.

- [28] T. Shao, Z. Wang, S. Fang, H. Liu and Z. Chen, "A Full-Passband Linear-Phase Band-Pass Filter Equalized with Negative Group Delay Circuits," IEEE Access, vol. 8, Feb. 2020, pp. 43336-43343.

- [29] B. Ravelo, M. Le Roy and A. Perennec, "Application of negative group delay active circuits to the design of broadband and constant phase shifters," Microwave and Optical Technology Letters, Vol. 50, No. 12, Dec. 2008, pp. 3077-3080.

- [30] B. Ravelo, A. Perennec and M. Le Roy, "Synthesis of frequencyindependent phase shifters using negative group delay active circuit," Int. J. RFMiCAE, Vol. 21, No. 1, Jan. 2011, pp. 17-24.

- [31] B. Ravelo, M. Le Roy and A. Pérennec, "Frequency-Independent Active Phase Shifters for UWB applications," Proc. of the 40th European Microwave Conference, Paris, France, 28-30 Sept. 2010, pp. 1774-1777.

- [32] B. Ravelo, "Distributed NGD active circuit for RF-microwave communication," Int. J. Electron. Commun., Vol. 68, No. 4, Apr. 2014, pp. 282-290.

- [33] Y. Meng, Z. Wang, S.-J. Fang, and H. Liu, "Broadband Phase Shifter with Constant Phase Based on Negative Group Delay Circuit," Progress In Electromagnetics Research Letters, Vol. 103, 161-169, 2022.

- [34] J. Nebhen and B. Ravelo, "Innovative microwave design of frequency-independent passive phase shifter with LCL-network and bandpass NGD circuit," PIER C, Vol. 109, pp. 187–203, 2021.

- [35] B. Ravelo, G. Fontgalland, H. S. Silva, J. Nebhen, W. Rahajandraibe, M. Guerin, G. Chan, and F. Wan, "Original Application of Stop-Band Negative Group Delay Microwave Passive Circuit for Two-Step Stair Phase Shifter Designing," IEEE Access, Vol. 10, No. 1, 2022, pp. 1493-1508.

- [36] B. Ravelo, "Negative group delay based Hilbert filter", Negative Group Delay Devices: From Concept to Applications, Chap. 7, From concept to applications, IET Materials, Circuit and Devices Series 43, Publisher Michael Faraday House, Six Hills Way, Stevenage, Hertfordshire, UK, ISBN 978-1-78561-640-2 / 978-1-78561-641-9, 2018, pp. 173-198.

- [37] M. A. Antoniades and G. V. Eleftheriades, "Compact linear lead/lag metamaterial phase shifters for broadband applications", IEEE Antennas Wireless Propag. Lett., vol. 2, pp. 103-106, 2003.

- [38] Y. Li, M. F. Iskander, Z. Zhang and Z. Feng, "A New Low Cost Leaky Wave Coplanar Waveguide Continuous Transverse Stub Antenna Array Using Metamaterial-Based Phase Shifters for Beam

1

VOLUME XX, 2022

- Steering," IEEE Trans. Antennas Propag., Vol. 61, No. 7, pp. 2619-2625, July 2013.

- [39] S. S. Oh and L. Shafai, "Compensated circuit with characteristics of lossless double negative materials and its application to array antennas," IET Microw. Antennas Propag., vol. 1, no. 1, 2007, pp. 29–38.

- [40] H. Liu, S. Gao and T. H. Loh, "Compact Dual-Band Antenna With Electronic Beam-Steering and Beamforming Capability," IEEE Antennas and Wireless Propagation Letters, vol. 10, 2011, pp. 1349-1352.

- [41] B. Ravelo, W. Rahajandraibe, M. Guerin, B. Agnus, P. Thakur and A. Thakur, "130-nm BiCMOS design of low-pass negative group delay integrated RL-circuit", Int. J. Circ. Theor. Appl., Early view, Feb. 2022, pp. 1-17.

- [42] F. Wan et al., "Design and Experimentation of Inductorless Low-Pass NGD Integrated Circuit in 180-nm CMOS Technology," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (Early Access), doi: 10.1109/TCAD.2021.3136982

- [43] M. Guerin, W. Rahajandraibe, G. Fontgalland, H. S. Silva, G. Chan, F. Wan, P. Thakur, A. Thakur, J. Frnda and B. Ravelo, "Theory and Original Design of Resistive-Inductive Network High-Pass Negative Group Delay Integrated Circuit in 130-nm CMOS Technology," IEEE Access, Vol. 10, No. 1, 2022, pp. 27147-27161.

Prof. Dr. Blaise RAVELO (M'09)

is currently University Full Professor at NUIST, Nanjing, China. His research interest is on Multiphysics and electronics engineering. He is a pioneer of the negative group delay (NGD) concept about t<0 signal travelling physical space. This extraordinary concept is potentially useful for anticipating and prediction all kind of information. He was research director of 11 PhD students (10 defended), postdocs, research engineers and Master internships. With US, Chinese, Indian, European and African partners, he is actively involved and contributes on several international research projects (ANR, FUI, FP7, INTERREG, H2020, Euripides², Eurostars...). He is member of IET Electronics Letters editorial board as circuit & system subject editor. He is member of scientific technical committee of Advanced Electromagnetic Symposium (AES) 2013 to now. He is ranked in Top 2% world's scientists based on years (2020-2021) by Stanford

University,

US

(https://elsevier.digitalcommonsdata.com/datasets/btchxktzyw/3). He has Google scholar h-index(2022)=25 and i10-index(2022)=80. He is member of research groups: IEEE, URSI, GDR Ondes, Radio Society and (co-) authors of more than 360 scientific research papers in new technologies published in int. conf. and journals. He is lecturer on circuit & system theory, STEM (science, technology, engineering and maths) and applied physics. Dr. Ravelo is IEEE member since 2007 and regularly invited to review papers submitted for publication to international journals (IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS, IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY, IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, IEEE ACCESS, IET CDS, IET MAP ...) and books (Wiley, Intech Science...).

degree in Microelectronics and Telecommunications from Polytech Marseille in 2010 and at the same time a Research Master in Integrated Circuits Design from the University of Aix-Marseille. He obtained his doctorate from the same institution in 2010. He worked as technical leader of the analog and radio-frequency design team of IDEMIA-StarChip for five years and designed chips embedded in SIM cards and contactless bank cards with biometric recognition. He joined Aix-Marseille University as an Assistant Professor in 2020 and joined the CCSI team of the IM2NP laboratory. His research focuses mainly on the design and synthesis of circuits in digital electronics. He is also working on methods of modeling and characterizing circuits in analog electronics.

born in Slovakia, in 1989. He received the M.Sc. and Ph.D. degrees from the Department of Telecommunications, VSB—Technical University of Ostrava, Czechia, in 2013 and 2018, respectively. He is currently working as an Assistant Professor at the University of Zilina, Slovakia. He has authored and coauthored 32 SCI-E and nine ESCI papers in WoS. His research interests include quality of multimedia services in IP networks, data analysis, and machine learning algorithms.

Dr. Frank Elliot SAHOA has received his Master degree in electrical engineering from the University of Antsiranana, Madagascar in 2004. He got his Master degree in Nuclear Physics, Theoretical Physics and Applied Physics at the University of Antananarivo in 2007. From 2008 to 2010, he was a DAAD doctorate fellow in Institüt für Nukleare Entsorgung (I.N.E.) at Karlsruhe Institute of Technology – Germany. He defended his Ph. D thesis at the University of Antananarivo in 2015. He is currently assistant professor at the Physics Department in the same university. His main research interests include environmental radioactivity monitoring using nuclear techniques and negative group delay (NGD) circuits. He is regularly involved to participate in international technical cooperation projects supported by IAEA such as MAG/7/002, MAG/5/014, RAF/5/063, MAG/5/019...

Glauco Fontgalland (S'97–A'99–M'00–SM'07) was born in Fortaleza, CE, Brazil, on March 2, 1966. Graduated (1990) and M.S. degree (1993) in Electrical Engineering from the Universidade Federal de Campina Grande (UFCG), Campina Grande - PB, Brazil. He has a

PhD in Electronics from Toulouse Institut National Polytechnique - ENSEEIHT (1999), Toulouse, France, where his Thesis work was nominated for the Leopold Escande Award 1999. From 2010 to 2012 he was visiting scholar at ElectroScience Laboratory at the Ohio State University - OSU, USA.

Currently, He is a Full Professor at the Universidade Federal de Campina Grande (UFCG), Campina Grande-PB, Brazil, where he develops research on: electromagnetic modeling, EMC, EMI, ESD, RFID, UWB, propagation, and antennas for various applications. He has published more than 200 papers in journal and conferences. He is past IEEE AP-S chapter chair and member of the 2020 IEEE AP-S student design contest and 2020 IEEE AP-S Field Awards Evaluation. Since 2019, he is an Associate Editor at IEEE Latin America Transactions.

Prof. Dr. Fontgalland is a member of the Sociedade Brasileira de Microondas e Optoeletrônica (SBMO), Sociedade Brasileira de Eletromagnetismo (SBMag), Sociedade Brasileira de Microeletrônica (SBMicro), and The applied Computacional Eletromagnetics Society (ACES).

Dr. Hugerles S. Silva received his B.Sc., M.Sc. and Ph.D. degrees in Electrical Engineering from UFCG, Brazil, in 2014, 2016 and 2019, respectively. Currently, Dr. Silva is a postdoc student at the Telecommunications Institute, University of Aveiro, Portugal. His main research interests include wireless communication, digital signal processing and wireless channel modeling.

Dr. Samuel Ngoho is graduated from ESIGELEC in Rouen, France, in 2012. He received his PhD degree in the thematic of High Frequency Electronics, Photonics and Systems from the University of Limoges, XLIM Laboratory, Limoges, France. The PhD subject concerned was based on the design and production of integrated optoelectronic components for high speed telecommunications systems. He worked as an integration,

verification, validation and qualification engineer of RF / HF products and systems for civil and military applications. He is currently working as a system engineer at THALES SIX, Gennevilliers, France. He is interested in the progress of microelectronics, in particular in the development of innovative functions integrated in microwave devices to meet the need for densification and evolution of spectra for future communications systems. He also takes part within research groups in the use of unfamiliar methods for resolving complex system as Kron's method.

degree in electronic engineering from the ENSEIRB, Bordeaux, France in 2006, and her Ph.D degree in Microelectronics from Aix-Marseille University, France in 2009. Since 2010, she joined the Integrated Circuits Design team at the Institute of Materials, Microelectronics and Nanosciences of Provence (IM2NP), Marseille, France.

She is currently assistant professor at Aix-Marseille University (AMU). Her research interests include CMOS analog and RF integrated circuits design, ultra-low power (ULP) and multi-standards applications. She coorganized the International Conferences ICECS 2014 and NEWCAS 2021, and also was member of the technical program committee of several IEEE international conferences. She is reviewer for IEEE Transactions on circuits and systems (TCAS), International Journal of Electronics and Communications (AEUE), Applied sciences journal, Electronics letters (IET), etc., as well as for many IEEE conferences dedicated to integrated circuits (ISCAS, NEWCAS, ICECS, MWSCAS, ICMCS, SBCCI...). She co-supervised 5 Ph.D and 8 Master students. She is author or co-author of more than 70 papers published in referred journals and conferences.

Prof. Dr. Wenceslas RAHAJANDRAIBE is

currently full professor at the University of Aix-Marseille. He received the B. Sc. degree in electrical engineering from Nice Sophia-Antipolis University, France, in 1996 and the M. Sc. (with distinction) in electrical engineering from the University of Montpellier, Science department, France, in 1998. Since 1998, he joined the microelectronics department of Informatics, Robotics and Microelectronics Laboratory of Montpellier (LIRMM) and received the Ph. D. on Microelectronics form the University of Montpellier. Since 2003, he joined the microelectronic department of Materials, Microelectronics and Nanoscience Laboratory of Provence (IM2NP) in Marseille, France where he was an Associate Professor, Since 2014, he is Professor at Aix Marseille University where he heads the Integrated Circuit Design group of the IM2NP laboratory. He is regularly involved to participate and to lead national and international research projects (ANR, H2020, FP7 KIC-InnoEnergy...). He directed and cosupervised 18 PhD and 15 Master students. His research interests involve AMS and RF circuit design from transistor to architectural level. His present research activity is focused on ultralow power circuit design for smart sensor interface and embedded electronic in bioelectronic and ehealth applications, wireless systems, design technique and architecture for multi-standard transceiver. He is author or co-author of 11 patents and more than 150 papers published in refereed journals and conferences. He is an expert for the ANR, the French Agency for Research. He has served on program committees of IEEE NEWCAS and ICECS. He has been and is a reviewer of contributions submitted to several IEEE conferences and journals such as ISCAS, NEWCAS, MWSCAS, ESSCIRC, ESSDERC, RFIC, IEEE Transactions on Circuits and Systems I and II, IET Electronics Letters.